Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                |                                                                             |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24j11-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.1.4 EXTENDED INSTRUCTION SET

The PIC18F46J11 family implements the optional extension to the PIC18 instruction set, adding eight new instructions and an Indexed Addressing mode. Enabled as a device configuration option, the extension has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as C.

## 1.1.5 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also aids in migrating to the next larger device.

The PIC18F46J11 family is also pin compatible with other PIC18 families, such as the PIC18F4620, PIC18F4520 and PIC18F45J10. This allows a new dimension to the evolution of applications, allowing developers to select different price points within Microchip's PIC18 portfolio, while maintaining the same feature set.

## 1.2 Other Special Features

- Communications: The PIC18F46J11 family incorporates a range of serial and parallel communication peripherals. This device also includes two independent Enhanced USARTs and two Master Synchronous Serial Port (MSSP) modules, capable of both Serial Peripheral Interface (SPI) and I<sup>2</sup>C™ (Master and Slave) modes of operation. The device also has a parallel port and can be configured to serve as either a Parallel Master Port (PMP) or as a Parallel Slave Port (PSP).

- ECCP Modules: All devices in the family incorporate three Enhanced Capture/Compare/PWM (ECCP) modules to maximize flexibility in control applications. Up to four different time bases may be used to perform several different operations at once. Each of the ECCPs offers up to four PWM outputs, allowing for a total of eight PWMs. The ECCPs also offer many beneficial features, including polarity selection, programmable dead time, auto-shutdown and restart and Half-Bridge and Full-Bridge Output modes.

- **10-Bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, and thus, reducing code overhead.

- Extended Watchdog Timer (WDT): This enhanced version incorporates a 16-bit prescaler, allowing an extended time-out range that is stable across operating voltage and temperature. See Section 29.0 "Electrical Characteristics" for time-out periods.

## 1.3 Details on Individual Family Devices

Devices in the PIC18F46J11 family are available in 28-pin and 44-pin packages. Block diagrams for the two groups are shown in Figure 1-1 and Figure 1-2. The devices are differentiated from each other in two ways:

- Flash program memory (three sizes: 16 Kbytes for the PIC18FX4J11, 32 Kbytes for PIC18FX5J11 devices and 64 Kbytes for PIC18FX6J11)

- I/O ports (three bidirectional ports on 28-pin devices, five bidirectional ports on 44-pin devices)

All other features for devices in this family are identical. These are summarized in Table 1-1 and Table 1-2.

The pinouts for the PIC18F2XJ11 devices are listed in Table 1-3 and the pinouts for the PIC18F4XJ11 devices are listed in Table 1-4.

The PIC18F46J11 family of devices provides an on-chip voltage regulator to supply the correct voltage levels to the core. Parts designated with an "F" part number (such as PIC18F46J11) have the voltage regulator enabled.

These parts can run from 2.15V-3.6V on VDD, but should have the VDDCORE pin connected to VSs through a low-ESR capacitor. Parts designated with an "LF" part number (such as PIC18**LF**46J11) do not enable the voltage regulator. For "LF" parts, an external supply of 2.0V-2.7V has to be supplied to the VDDCORE pin with 2.0V-3.6V supplied to VDD (VDDCORE should never exceed VDD).

For more details about the internal voltage regulator, see **Section 26.3 "On-Chip Voltage Regulator"**.

#### REGISTER 4-3: DSGPR0: DEEP SLEEP PERSISTENT GENERAL PURPOSE REGISTER 0 (BANKED F4Eh)

| R/W-xxxx <sup>(1)</sup> |                                            |                        |                    |  |  |  |

|-------------------------|--------------------------------------------|------------------------|--------------------|--|--|--|

|                         | Deep Sleep Persistent General Purpose bits |                        |                    |  |  |  |

| bit 7                   |                                            |                        |                    |  |  |  |

|                         |                                            |                        |                    |  |  |  |

| Legend:                 |                                            |                        |                    |  |  |  |

| R = Readable bit        | W = Writable bit                           | U = Unimplemented bit, | read as '0'        |  |  |  |

| -n = Value at POR       | '1' = Bit is set                           | '0' = Bit is cleared   | x = Bit is unknown |  |  |  |

bit 7-0 Deep Sleep Persistent General Purpose bits Contents are retained even in Deep Sleep mode.

## REGISTER 4-4: DSGPR1: DEEP SLEEP PERSISTENT GENERAL PURPOSE REGISTER 1 (BANKED F4Fh)

|                 |                | R/W-xxxx <sup>(1)</sup>      |       |

|-----------------|----------------|------------------------------|-------|

|                 | Deep Sleep Per | sistent General Purpose bits |       |

| bit 7           |                |                              | bit 0 |

|                 |                |                              |       |

| Legend:         |                |                              |       |

| D D L L L L L L |                |                              |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-0 Deep Sleep Persistent General Purpose bits Contents are retained even in Deep Sleep mode.

**Note 1:** All register bits are maintained unless: VDDCORE drops below the normal BOR threshold outside of Deep Sleep, or, the device is in Deep Sleep and the dedicated DSBOR is enabled and VDD drops below the DSBOR threshold, or DSBOR is enabled or disabled, but VDD is hard cycled to near VSS.

**Note 1:** All register bits are maintained unless: VDDCORE drops below the normal BOR threshold outside of Deep Sleep, or the device is in Deep Sleep and the dedicated DSBOR is enabled and VDD drops below the DSBOR threshold, or DSBOR is enabled or disabled, but VDD is hard cycled to near VSS.

| TABLE 5-2:          | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |             |                                                                |                                                                            |                                 |  |  |  |  |

|---------------------|---------------------------------------------------------|-------------|----------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------|--|--|--|--|

| Register            | Applicable Devices                                      |             | Power-on Reset,<br>Brown-out Reset,<br>Wake From<br>Deep Sleep | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |  |  |  |

| INDF2               | PIC18F2XJ11                                             | PIC18F4XJ11 | N/A                                                            | N/A                                                                        | N/A                             |  |  |  |  |

| POSTINC2            | PIC18F2XJ11                                             | PIC18F4XJ11 | N/A                                                            | N/A                                                                        | N/A                             |  |  |  |  |

| POSTDEC2            | PIC18F2XJ11                                             | PIC18F4XJ11 | N/A                                                            | N/A                                                                        | N/A                             |  |  |  |  |

| PREINC2             | PIC18F2XJ11                                             | PIC18F4XJ11 | N/A                                                            | N/A                                                                        | N/A                             |  |  |  |  |

| PLUSW2              | PIC18F2XJ11                                             | PIC18F4XJ11 | N/A                                                            | N/A                                                                        | N/A                             |  |  |  |  |

| FSR2H               | PIC18F2XJ11                                             | PIC18F4XJ11 | 0000                                                           | 0000                                                                       | uuuu                            |  |  |  |  |

| FSR2L               | PIC18F2XJ11                                             | PIC18F4XJ11 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| STATUS              | PIC18F2XJ11                                             | PIC18F4XJ11 | x xxxx                                                         | u uuuu                                                                     | u uuuu                          |  |  |  |  |

| TMR0H               | PIC18F2XJ11                                             | PIC18F4XJ11 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |

| TMR0L               | PIC18F2XJ11                                             | PIC18F4XJ11 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| T0CON               | PIC18F2XJ11                                             | PIC18F4XJ11 | 1111 1111                                                      | 1111 1111                                                                  | uuuu uuuu                       |  |  |  |  |

| OSCCON              | PIC18F2XJ11                                             | PIC18F4XJ11 | 0110 q100                                                      | 0110 q100                                                                  | 0110 qluu                       |  |  |  |  |

| CM1CON              | PIC18F2XJ11                                             | PIC18F4XJ11 | 0001 1111                                                      | 0001 1111                                                                  | uuuu uuuu                       |  |  |  |  |

| CM2CON              | PIC18F2XJ11                                             | PIC18F4XJ11 | 0001 1111                                                      | 0001 1111                                                                  | uuuu uuuu                       |  |  |  |  |

| RCON <sup>(4)</sup> | PIC18F2XJ11                                             | PIC18F4XJ11 | 0-11 11qq                                                      | 0-qq qquu                                                                  | u-qq qquu                       |  |  |  |  |

| TMR1H               | PIC18F2XJ11                                             | PIC18F4XJ11 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| TMR1L               | PIC18F2XJ11                                             | PIC18F4XJ11 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| T1CON               | PIC18F2XJ11                                             | PIC18F4XJ11 | 0000 0000                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| TMR2                | PIC18F2XJ11                                             | PIC18F4XJ11 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |

| PR2                 | PIC18F2XJ11                                             | PIC18F4XJ11 | 1111 1111                                                      | 1111 1111                                                                  | uuuu uuuu                       |  |  |  |  |

| T2CON               | PIC18F2XJ11                                             | PIC18F4XJ11 | -000 0000                                                      | -000 0000                                                                  | -uuu uuuu                       |  |  |  |  |

| SSP1BUF             | PIC18F2XJ11                                             | PIC18F4XJ11 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| SSP1ADD             | PIC18F2XJ11                                             | PIC18F4XJ11 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |

| SSP1MSK             | PIC18F2XJ11                                             | PIC18F4XJ11 | 1111 1111                                                      | 1111 1111                                                                  | uuuu uuuu                       |  |  |  |  |

| SSP1STAT            | PIC18F2XJ11                                             | PIC18F4XJ11 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |

| SSP1CON1            | PIC18F2XJ11                                             | PIC18F4XJ11 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |

| SSP1CON2            | PIC18F2XJ11                                             | PIC18F4XJ11 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |

| ADRESH              | PIC18F2XJ11                                             | PIC18F4XJ11 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| ADRESL              | PIC18F2XJ11                                             | PIC18F4XJ11 | xxxx xxxx                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |

| ADCON0              | PIC18F2XJ11                                             | PIC18F4XJ11 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |

| ADCON1              | PIC18F2XJ11                                             | PIC18F4XJ11 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |

| WDTCON              | PIC18F2XJ11                                             | PIC18F4XJ11 | 1qq- q000                                                      | 1qq- 0000                                                                  | uqq- uuuu                       |  |  |  |  |

## TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

**2:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 4: See Table 5-1 for Reset value for specific condition.

- 5: Not implemented for PIC18F2XJ11 devices.

- 6: Not implemented on "LF" devices.

| Pin       | Function | TRIS<br>Setting | I/O | I/O<br>Type                          | Description                          |

|-----------|----------|-----------------|-----|--------------------------------------|--------------------------------------|

| RD6/PMD6/ |          |                 | Ι   | ST                                   | PORTD<6> data input.                 |

| RP23      |          | 0               | 0   | DIG                                  | LATD<6> data output.                 |

|           | PMD6     | 1               | Ι   | ST/TTL                               | Parallel Master Port data in.        |

|           |          | 0               | 0   | DIG                                  | Parallel Master Port data out.       |

|           | RP23     | 1               | I   | ST                                   | Remappable peripheral pin 23 input.  |

|           | 0        | 0               | DIG | Remappable peripheral pin 23 output. |                                      |

| RD7/PMD7/ | RD7      | 1               | Ι   | ST                                   | PORTD<7> data input.                 |

| RP24      |          | 0               | 0   | DIG                                  | LATD<7> data output.                 |

|           | PMD7     | 1               | Ι   | ST/TTL                               | Parallel Master Port data in.        |

|           |          | 0               | 0   | DIG                                  | Parallel Master Port data out.       |

|           | RP24     | 1               | Ι   | ST                                   | Remappable peripheral pin 24 input.  |

|           |          | 0               | 0   | DIG                                  | Remappable peripheral pin 24 output. |

TABLE 10-9: PORTD I/O SUMMARY (CONTINUED)

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer;  $I^2C/SMB = I^2C/SMB$ us input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

| Name                 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|----------------------|--------|--------|--------|--------|--------|--------|--------|--------|----------------------------|

| PORTD <sup>(1)</sup> | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | 93                         |

| LATD <sup>(1)</sup>  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | 92                         |

| TRISD <sup>(1)</sup> | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | 92                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTD.

Note 1: These registers are not available in 28-pin devices.

| REGISTER 10-6: | <b>RPINR1: PERIPHERAL</b> | <b>PIN SELECT INPUT</b> | <b>REGISTER 1</b> | (BANKED EE7h) |

|----------------|---------------------------|-------------------------|-------------------|---------------|

|----------------|---------------------------|-------------------------|-------------------|---------------|

| U-0   | U-0 | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|-------|-----|-----|---------|---------|---------|---------|---------|

| —     | —   | —   | INTR1R4 | INTR1R3 | INTR1R2 | INTR1R1 | INTR1R0 |

| bit 7 |     |     |         |         |         |         | bit 0   |

| Legend:           | R/W = Readable, Writable | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                    |  |  |  |  |

|-------------------|--------------------------|-----------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read as '0'                  |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 INTR1R<4:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits

#### REGISTER 10-7: RPINR2: PERIPHERAL PIN SELECT INPUT REGISTER 2 (BANKED EE8h)

| U-0   | U-0 | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|-------|-----|-----|---------|---------|---------|---------|---------|

| —     | —   | —   | INTR2R4 | INTR2R3 | INTR2R2 | INTR2R1 | INTR2R0 |

| bit 7 |     |     |         |         |         |         | bit 0   |

| Legend:           | R/W = Readable, Writable | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                    |  |  |  |  |

|-------------------|--------------------------|-----------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, rea                          | d as '0'           |  |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 INTR2R<4:0>: Assign External Interrupt 2 (INT2) to the Corresponding RPn pin bits

#### REGISTER 10-8: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3 (BANKED EE9h)

| U-0   | U-0 | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|-------|-----|-----|---------|---------|---------|---------|---------|

| —     | —   | —   | INTR3R4 | INTR3R3 | INTR3R2 | INTR3R1 | INTR3R0 |

| bit 7 |     |     |         |         |         |         | bit 0   |

| Legend:           | $R/\overline{W}$ = Readable, Writable i | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                    |  |  |  |  |

|-------------------|-----------------------------------------|-----------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit                        | U = Unimplemented bit, read                         | as '0'             |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                        | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 INTR3R<4:0>: Assign External Interrupt 3 (INT3) to the Corresponding RPn Pin bits

## 17.6 Register Maps

Table 17-5, Table 17-6 and Table 17-7 summarize the registers associated with the RTCC module.

| File Name | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2     | Bit 1     | Bit 0    | All<br>Resets |

|-----------|--------|--------|---------|---------|---------|-----------|-----------|----------|---------------|

| RTCCFG    | RTCEN  | _      | RTCWREN | RTCSYNC | HALFSEC | RTCOE     | RTCPTR1   | RTCPTR0  | 0000          |

| RTCCAL    | CAL7   | CAL6   | CAL5    | CAL4    | CAL3    | CAL2      | CAL1      | CAL0     | 0000          |

| PADCFG1   | _      |        | _       | —       | _       | RTSECSEL1 | RTSECSEL0 | PMPTTL   | 0000          |

| ALRMCFG   | ALRMEN | CHIME  | AMASK3  | AMASK2  | AMASK1  | AMASK0    | ALRMPTR1  | ALRMPTR0 | 0000          |

| ALRMRPT   | ARPT7  | ARPT6  | ARPT5   | ARPT4   | ARPT3   | ARPT2     | ARPT1     | ARPT0    | 0000          |

| IPR3      | SSP2IP | BCL2IP | RC2IP   | TX2IP   | TMR4IP  | CTMUIP    | TMR3GIP   | RTCCIP   | 1111          |

| PIR3      | SSP2IF | BCL2IF | RC2IF   | TX2IF   | TMR4IF  | CTMUIF    | TMR3GIF   | RTCCIF   | 0000          |

| PIE3      | SSP2IE | BCL2IE | RC2IE   | TX2IE   | TMR4IE  | CTMUIE    | TMR3GIE   | RTCCIE   | 0000          |

#### TABLE 17-5: RTCC CONTROL REGISTERS

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal for 44-pin devices.

#### TABLE 17-6: RTCC VALUE REGISTERS

| File Name | Bit 7       | Bit 6                                                        | Bit 5        | Bit 4        | Bit 3     | Bit 2  | Bit 1    | Bit 0    | All Resets |

|-----------|-------------|--------------------------------------------------------------|--------------|--------------|-----------|--------|----------|----------|------------|

| RTCVALH   | RTCC Value  | Register W                                                   | indow High B | yte, Based o | n RTCPTR< | 1:0>   |          |          | xxxx       |

| RTCVALL   | RTCC Value  | RTCC Value Register Window Low Byte, Based on RTCPTR<1:0>    |              |              |           |        |          |          | xxxx       |

| RTCCFG    | RTCEN       | _                                                            | RTCWREN      | RTCSYNC      | HALFSEC   | RTCOE  | RTCPTR1  | RTCPTR0  | 0000       |

| ALRMCFG   | ALRMEN      | CHIME                                                        | AMASK3       | AMASK2       | AMASK1    | AMASK0 | ALRMPTR1 | ALRMPTR0 | 0000       |

| ALRMVALH  | Alarm Value | Alarm Value Register Window High Byte, Based on ALRMPTR<1:0> |              |              |           |        |          |          | xxxx       |

| ALRMVALL  | Alarm Value | Register Wi                                                  | ndow Low By  | te, Based on | ALRMPTR<  | <1:0>  |          |          | xxxx       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal for 44-pin devices.

## TABLE 17-7: ALARM VALUE REGISTERS

| File Name | Bit 7         | Bit 6                                                      | Bit 5         | Bit 4        | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|---------------|------------------------------------------------------------|---------------|--------------|------------|-------|-------|-------|---------------|

| ALRMRPT   | ARPT7         | ARPT6                                                      | ARPT5         | ARPT4        | ARPT3      | ARPT2 | ARPT1 | ARPT0 | 0000          |

| ALRMVALH  | Alarm Value R | arm Value Register Window High Byte, Based on ALRMPTR<1:0> |               |              |            |       |       |       |               |

| ALRMVALL  | Alarm Value R | egister Windo                                              | w Low Byte, E | Based on ALF | RMPTR<1:0> |       |       |       | xxxx          |

| RTCCAL    | CAL7          | CAL6                                                       | CAL5          | CAL4         | CAL3       | CAL2  | CAL1  | CAL0  | 0000          |

| RTCVALH   | RTCC Value R  | TCC Value Register Window High Byte, Based on RTCPTR<1:0>  |               |              |            |       |       |       | xxxx          |

| RTCVALL   | RTCC Value R  | TCC Value Register Window Low Byte, Based on RTCPTR<1:0>   |               |              |            |       |       |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal for 44-pin devices.

## REGISTER 19-7: SSPxCON2: MSSPx CONTROL REGISTER 2 –I<sup>2</sup>C<sup>™</sup> MASTER MODE (ACCESS FC5h/F71h)

|                     | (700                              |                                    | ,                              |                                       |                    |                     |                    |

|---------------------|-----------------------------------|------------------------------------|--------------------------------|---------------------------------------|--------------------|---------------------|--------------------|

| R/W-0               | R-0                               | R/W-0                              | R/W-0                          | R/W-0                                 | R/W-0              | R/W-0               | R/W-0              |

| GCEN <sup>(3)</sup> | ACKSTAT                           | ACKDT <sup>(1)</sup>               | ACKEN <sup>(2)</sup>           | RCEN <sup>(2)</sup>                   | PEN <sup>(2)</sup> | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup> |

| bit 7               |                                   |                                    |                                |                                       |                    |                     | bit (              |

| Legend:             |                                   |                                    |                                |                                       |                    |                     |                    |

| R = Readabl         | e bit                             | W = Writable                       | bit                            | U = Unimplem                          | nented bit, rea    | d as '0'            |                    |

| -n = Value at       | POR                               | '1' = Bit is set                   |                                | '0' = Bit is clea                     | ared               | x = Bit is unkn     | own                |

| bit 7               |                                   |                                    | bit (Slave mod general call ad |                                       | is received in     | the SSPxSR          |                    |

|                     |                                   | all address dis                    | •                              | , , , , , , , , , , , , , , , , , , , |                    |                     |                    |

| bit 6               | ACKSTAT: A                        | cknowledge Sta                     | atus bit (Master               | Transmit mode                         | e only)            |                     |                    |

|                     |                                   |                                    | ceived from sla                | ive                                   |                    |                     |                    |

| 6:4 F               |                                   | dge was receiv                     |                                |                                       | <b>(1)</b>         |                     |                    |

| bit 5               | 1 = Not Ackn                      |                                    | bit (Master Red                | ceive mode oni                        | y)(''              |                     |                    |

|                     | 0 = Acknowle                      |                                    |                                |                                       |                    |                     |                    |

| bit 4               |                                   | •                                  | lence Enable b                 | it <sup>(2)</sup>                     |                    |                     |                    |

|                     | automati                          | Acknowledge<br>cally cleared by    | / hardware                     | SDAx and SC                           | CLx pins and       | transmits AC        | KDT data bi        |

| bit 3               |                                   |                                    | Master Receive                 | mode only) <sup>(2)</sup>             |                    |                     |                    |

|                     |                                   | Receive mode t                     |                                |                                       |                    |                     |                    |

| bit 2               | PEN: Stop Co                      | ondition Enable                    | e bit <sup>(2)</sup>           |                                       |                    |                     |                    |

|                     | 1 = Initiates S<br>0 = Stop cond  |                                    | on SDAx and SO                 | CLx pins; auton                       | natically clear    | ed by hardware      |                    |

| bit 1               | RSEN: Repe                        | ated Start Cond                    | dition Enable bit              | (2)                                   |                    |                     |                    |

|                     |                                   | Repeated Start<br>d Start conditio |                                | DAx and SCLx                          | pins; automat      | tically cleared by  | / hardware         |

| bit 0               | SEN: Start Co                     | ondition Enable                    | e bit <sup>(2)</sup>           |                                       |                    |                     |                    |

|                     | 1 = Initiates S<br>0 = Start cond |                                    | on SDAx and S                  | CLx pins; autor                       | natically clear    | ed by hardware      |                    |

|                     | -                                 |                                    |                                |                                       |                    | ence at the end o   |                    |

| <b>2:</b> If        | the I <sup>-</sup> C module       | is active, these                   | e bits may not b               | e set (no spool                       | ling) and the S    | SPxBUF may n        | ot be written      |

(or writes to the SSPxBUF are disabled).

**3:** This bit is not implemented in  $I^2C$  Master mode.

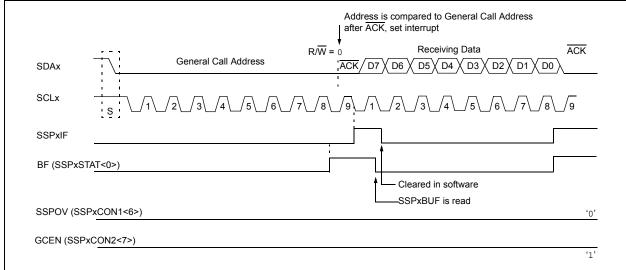

#### 19.5.5 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an Acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all '0's with R/W = 0.

The general call address is recognized when the General Call Enable bit, GCEN, is enabled (SSPxCON2<7> set). Following a Start bit detect, 8 bits are shifted into the SSPxSR and the address is compared against the SSPxADD. It is also compared to the general call address and fixed in hardware.

If the general call address matches, the SSPxSR is transferred to the SSPxBUF, the BF flag bit is set (eighth bit), and on the falling edge of the ninth bit (ACK bit), the SSPxIF interrupt flag bit is set.

When the interrupt is serviced, the source for the interrupt can be checked by reading the contents of the SSPxBUF. The value can be used to determine if the address was device-specific or a general call address.

In 10-bit mode, the SSPxADD is required to be updated for the second half of the address to match and the UA bit is set (SSPxSTAT<1>). If the general call address is sampled when the GCEN bit is set, while the slave is configured in 10-Bit Addressing mode, then the second half of the address is not necessary, the UA bit will not be set and the slave will begin receiving data after the Acknowledge (Figure 19-17).

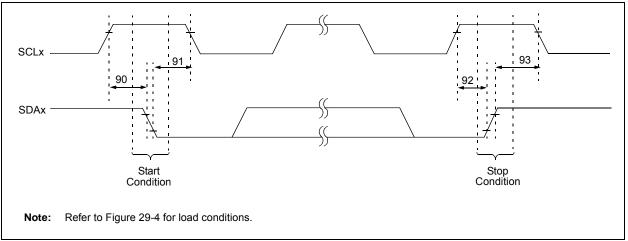

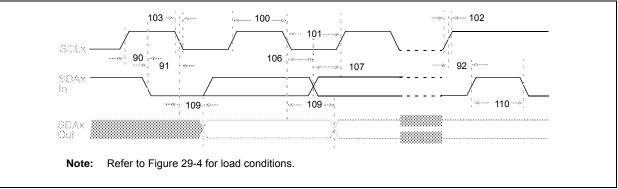

## 19.5.6 MASTER MODE

Master mode is enabled by setting and clearing the appropriate SSPM bits in SSPxCON1 and by setting the SSPEN bit. In Master mode, the SCLx and SDAx lines are manipulated by the MSSP hardware if the TRIS bits are set.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Start (S) and Stop (P) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the Stop bit is set, or the bus is Idle, with both the Start and Stop bits clear.

In Firmware Controlled Master mode, user code conducts all  ${\rm I}^2{\rm C}$  bus operations based on Start and Stop bit conditions.

Once Master mode is enabled, the user has six options.

- 1. Assert a Start condition on SDAx and SCLx.

- 2. Assert a Repeated Start condition on SDAx and SCLx.

- 3. Write to the SSPxBUF register initiating transmission of data/address.

- 4. Configure the  $I^2C$  port to receive data.

- 5. Generate an Acknowledge condition at the end of a received byte of data.

- 6. Generate a Stop condition on SDAx and SCLx.

## 20.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is one of two serial I/O modules. (Generically, the EUSART is also known as a Serial Communications Interface or SCI.) The EUSART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs and so on.

The Enhanced USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These make it ideally suited for use in Local Interconnect Network bus (LIN/J2602 bus) systems.

All members of the PIC18F46J11 family are equipped with two independent EUSART modules, referred to as EUSART1 and EUSART2. They can be configured in the following modes:

- Asynchronous (full-duplex) with:

- Auto-wake-up on character reception

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half-duplex) with selectable clock polarity

- Synchronous Slave (half-duplex) with selectable clock polarity

The pins of EUSART1 and EUSART2 are multiplexed with the functions of PORTC (RC6/PMA5/TX1/CK1/RP17 and RC7/PMA4/RX1/DT1/RP18) and remapped (RPn1/TX2/CK2 and RPn2/RX2/DT2), respectively. In order to configure these pins as an EUSART:

- For EUSART1:

- SPEN bit (RCSTA1<7>) must be set (= 1)

- TRISC<7> bit must be set (= 1)

- TRISC<6> bit must be cleared (= 0) for Asynchronous and Synchronous Master modes

- TRISC<6> bit must be set (= 1) for Synchronous Slave mode

- For EUSART2:

- SPEN bit (RCSTA2<7>) must be set (= 1)

- TRIS bit for RPn2/RX2/DT2 = 1

- TRIS bit for RPn1/TX2/CK2 = 0 for Asynchronous and Synchronous Master modes

- TRISC<6> bit must be set (= 1) for Synchronous Slave mode

Note: The EUSART control will automatically reconfigure the pin from input to output as needed.

The TXx/CKx I/O pins have an optional open-drain output capability. By default, when this pin is used by the EUSART as an output, it will function as a standard push-pull CMOS output. The TXx/CKx I/O pins' open-drain, output feature can be enabled by setting the corresponding UxOD bit in the ODCON2 register. For more details, see **Section 19.3.3 "Open-Drain Output Option"**.

The operation of each Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTAx)

- Receive Status and Control (RCSTAx)

- Baud Rate Control (BAUDCONx)

These are covered in detail in Register 20-1, Register 20-2 and Register 20-3, respectively.

Note: Throughout this section, references to register and bit names that may be associated with a specific EUSART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "RCSTAx" might refer to the Receive Status register for either EUSART1 or EUSART2.

|       |                       |            |                             |                       | SYNC       | = 0, BRGH                   | <b>i =</b> 0, BRG     | 16 = 1     |                             |                       |            |                             |

|-------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD  | Fosc                  | = 40.000   | ) MHz                       | Fosc                  | = 20.000   | ) MHz                       | Fosc                  | = 10.000   | ) MHz                       | Fosc = 8.000 MHz      |            |                             |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3   | 0.300                 | 0.00       | 8332                        | 0.300                 | 0.02       | 4165                        | 0.300                 | 0.02       | 2082                        | 0.300                 | -0.04      | 1665                        |

| 1.2   | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.03      | 1041                        | 1.200                 | -0.03      | 520                         | 1.201                 | -0.16      | 415                         |

| 2.4   | 2.402                 | 0.06       | 1040                        | 2.399                 | -0.03      | 520                         | 2.404                 | 0.16       | 259                         | 2.403                 | -0.16      | 207                         |

| 9.6   | 9.615                 | 0.16       | 259                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |

| 19.2  | 19.231                | 0.16       | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |

| 57.6  | 58.140                | 0.94       | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |

| 115.2 | 113.636               | -1.36      | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           | —                     |            | —                           |

## TABLE 20-3: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|       |                       |            | S                           | YNC = 0, E            | BRGH = (   | ), BRG16 =                  | 1                     |            |                             |

|-------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD  | Foso                  | c = 4.000  | MHz                         | Fosc = 2.000 MHz      |            |                             | Fosc = 1.000 MHz      |            |                             |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3   | 0.300                 | 0.04       | 832                         | 0.300                 | -0.16      | 415                         | 0.300                 | -0.16      | 207                         |

| 1.2   | 1.202                 | 0.16       | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |

| 2.4   | 2.404                 | 0.16       | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |

| 9.6   | 9.615                 | 0.16       | 25                          | 9.615                 | -0.16      | 12                          | —                     | _          | _                           |

| 19.2  | 19.231                | 0.16       | 12                          | —                     | _          | _                           | —                     | _          | _                           |

| 57.6  | 62.500                | 8.51       | 3                           | —                     | _          | _                           | —                     | _          | _                           |

| 115.2 | 125.000               | 8.51       | 1                           | _                     | _          | —                           | _                     | _          | _                           |

|              |                       |            |                             | <b>SYNC</b> = 0,      | BRGH =     | = 1, BRG16                  | = 1 or SY             | NC = 1, I  | BRG16 = 1                   |                       |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc                  | = 40.000   | ) MHz                       | Fosc                  | = 20.000   | ) MHz                       | Fosc = 10.000 MHz Fos |            |                             | c = 8.000 MHz         |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                 | 0.00       | 33332                       | 0.300                 | 0.00       | 16665                       | 0.300                 | 0.00       | 8332                        | 0.300                 | -0.01      | 6665                        |

| 1.2          | 1.200                 | 0.00       | 8332                        | 1.200                 | 0.02       | 4165                        | 1.200                 | 0.02       | 2082                        | 1.200                 | -0.04      | 1665                        |

| 2.4          | 2.400                 | 0.02       | 4165                        | 2.400                 | 0.02       | 2082                        | 2.402                 | 0.06       | 1040                        | 2.400                 | -0.04      | 832                         |

| 9.6          | 9.606                 | 0.06       | 1040                        | 9.596                 | -0.03      | 520                         | 9.615                 | 0.16       | 259                         | 9.615                 | -0.16      | 207                         |

| 19.2         | 19.193                | -0.03      | 520                         | 19.231                | 0.16       | 259                         | 19.231                | 0.16       | 129                         | 19.230                | -0.16      | 103                         |

| 57.6         | 57.803                | 0.35       | 172                         | 57.471                | -0.22      | 86                          | 58.140                | 0.94       | 42                          | 57.142                | 0.79       | 34                          |

| 115.2        | 114.943               | -0.22      | 86                          | 116.279               | 0.94       | 42                          | 113.636               | -1.36      | 21                          | 117.647               | -2.12      | 16                          |

|       |                       | SYN        | IC = 0, BR(                 | GH = 1, BF            | <b>RG16 =</b> 1 | or SYNC =                   | = 1, BRG1             | 6 = 1      |                             |

|-------|-----------------------|------------|-----------------------------|-----------------------|-----------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD  | Fost                  | c = 4.000  | MHz                         | Fos                   | c = 2.000       | MHz                         | Fosc = 1.000 MHz      |            |                             |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error      | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3   | 0.300                 | 0.01       | 3332                        | 0.300                 | -0.04           | 1665                        | 0.300                 | -0.04      | 832                         |

| 1.2   | 1.200                 | 0.04       | 832                         | 1.201                 | -0.16           | 415                         | 1.201                 | -0.16      | 207                         |

| 2.4   | 2.404                 | 0.16       | 415                         | 2.403                 | -0.16           | 207                         | 2.403                 | -0.16      | 103                         |

| 9.6   | 9.615                 | 0.16       | 103                         | 9.615                 | -0.16           | 51                          | 9.615                 | -0.16      | 25                          |

| 19.2  | 19.231                | 0.16       | 51                          | 19.230                | -0.16           | 25                          | 19.230                | -0.16      | 12                          |

| 57.6  | 58.824                | 2.12       | 16                          | 55.555                | 3.55            | 8                           | —                     | _          | —                           |

| 115.2 | 111.111               | -3.55      | 8                           | —                     | _               | —                           | —                     | _          | —                           |

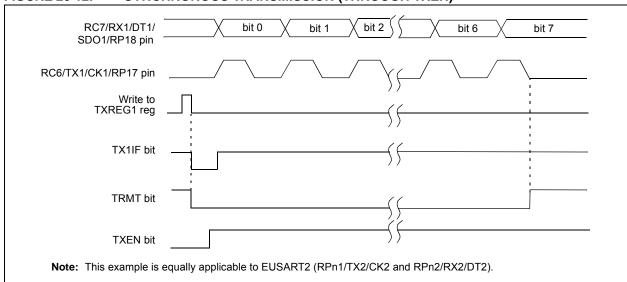

## FIGURE 20-12: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

| TABLE 20-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION | TABLE 20-7: | 20-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION |

|-----------------------------------------------------------------------|-------------|-----------------------------------------------------------------|

|-----------------------------------------------------------------------|-------------|-----------------------------------------------------------------|

| Name     | Bit 7                                          | Bit 6       | Bit 5       | Bit 4       | Bit 3             | Bit 2  | Bit 1   | Bit 0  | Reset<br>Values<br>on Page: |

|----------|------------------------------------------------|-------------|-------------|-------------|-------------------|--------|---------|--------|-----------------------------|

| INTCON   | <b>GIE/GIEH</b>                                | PEIE/GIEL   | TMR0IE      | INT0IE      | RBIE              | TMR0IF | INT0IF  | RBIF   | 69                          |

| PIR1     | PMPIF <sup>(1)</sup>                           | ADIF        | RC1IF       | TX1IF       | SSP1IF            | CCP1IF | TMR2IF  | TMR1IF | 72                          |

| PIE1     | PMPIE <sup>(1)</sup>                           | ADIE        | RC1IE       | TX1IE       | SSP1IE            | CCP1IE | TMR2IE  | TMR1IE | 72                          |

| IPR1     | PMPIP <sup>(1)</sup>                           | ADIP        | RC1IP       | TX1IP       | SSP1IP            | CCP1IP | TMR2IP  | TMR1IP | 72                          |

| PIR3     | SSP2IF                                         | BCL2IF      | RC2IF       | TX2IF       | TMR4IF            | CTMUIF | TMR3GIF | RTCCIF | 72                          |

| PIE3     | SSP2IE                                         | BCL2IE      | RC2IE       | TX2IE       | TMR4IE            | CTMUIE | TMR3GIE | RTCCIE | 72                          |

| IPR3     | SSP2IP                                         | BCL2IP      | RC2IP       | TX2IP       | TMR4IP            | CTMUIP | TMR3GIP | RTCCIP | 72                          |

| RCSTAx   | SPEN                                           | RX9         | SREN        | CREN        | ADDEN             | FERR   | OERR    | RX9D   | 72                          |

| TXREGx   | EUSARTx                                        | Transmit Re | gister      |             |                   |        |         |        | 72                          |

| TXSTAx   | CSRC                                           | TX9         | TXEN        | SYNC        | SENDB             | BRGH   | TRMT    | TX9D   | 72                          |

| BAUDCONx | ABDOVF                                         | RCIDL       | RXDTP       | TXCKP       | BRG16             | _      | WUE     | ABDEN  | 73                          |

| SPBRGHx  | EUSARTx Baud Rate Generator Register High Byte |             |             |             |                   |        |         |        | 72                          |

| SPBRGx   | EUSARTx                                        | Baud Rate C | Generator R | egister Low | <sup>,</sup> Byte |        |         |        | 72                          |

| ODCON2   | _                                              |             |             |             |                   |        | U2OD    | U10D   | 74                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: These pins are only available on 44-pin devices.

## 20.4 EUSART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTAx<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the CKx pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

#### 20.4.1 EUSART SYNCHRONOUS SLAVE TRANSMISSION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep mode.

If two words are written to the TXREGx and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREGx register.

- c) Flag bit, TXxIF, will not be set.

- d) When the first word has been shifted out of TSR, the TXREGx register will transfer the second word to the TSR and flag bit, TXxIF, will now be set.

- e) If enable bit, TXxIE, is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. Clear bits, CREN and SREN.

- 3. If interrupts are desired, set enable bit, TXxIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting enable bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| R/W-0                                       | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ADCAL                                       | ACQT2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ACQT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ACQT0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ADCS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ADCS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ADCS0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |