Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 48MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 16                                                                           |

| Program Memory Size        | 16KB (8K x 16)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 3.8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24j11t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### REGISTER 4-3: DSGPR0: DEEP SLEEP PERSISTENT GENERAL PURPOSE REGISTER 0 (BANKED F4Eh)

| R/W-xxxx <sup>(1)</sup>                    |                  |                        |                    |       |  |  |

|--------------------------------------------|------------------|------------------------|--------------------|-------|--|--|

| Deep Sleep Persistent General Purpose bits |                  |                        |                    |       |  |  |

| bit 7                                      |                  |                        |                    | bit 0 |  |  |

|                                            |                  |                        |                    |       |  |  |

| Legend:                                    |                  |                        |                    |       |  |  |

| R = Readable bit                           | W = Writable bit | U = Unimplemented bit, | read as '0'        |       |  |  |

| -n = Value at POR                          | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |       |  |  |

bit 7-0 Deep Sleep Persistent General Purpose bits Contents are retained even in Deep Sleep mode.

### REGISTER 4-4: DSGPR1: DEEP SLEEP PERSISTENT GENERAL PURPOSE REGISTER 1 (BANKED F4Fh)

|                 |                | R/W-xxxx <sup>(1)</sup>      |       |

|-----------------|----------------|------------------------------|-------|

|                 | Deep Sleep Per | sistent General Purpose bits |       |

| bit 7           |                |                              | bit 0 |

|                 |                |                              |       |

| Legend:         |                |                              |       |

| D D L L L L L L |                |                              |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-0 Deep Sleep Persistent General Purpose bits Contents are retained even in Deep Sleep mode.

**Note 1:** All register bits are maintained unless: VDDCORE drops below the normal BOR threshold outside of Deep Sleep, or, the device is in Deep Sleep and the dedicated DSBOR is enabled and VDD drops below the DSBOR threshold, or DSBOR is enabled or disabled, but VDD is hard cycled to near VSS.

**Note 1:** All register bits are maintained unless: VDDCORE drops below the normal BOR threshold outside of Deep Sleep, or the device is in Deep Sleep and the dedicated DSBOR is enabled and VDD drops below the DSBOR threshold, or DSBOR is enabled or disabled, but VDD is hard cycled to near VSS.

#### EXAMPLE 4-1: ULTRA LOW-POWER WAKE-UP INITIALIZATION

```

//Configure a remappable output pin with interrupt capability

//for ULPWU function (RP21 => RD4/INT1 in this example)

RPOR21 = 13;// ULPWU function mapped to RP21/RD4

RPINR1 = 21;// INT1 mapped to RP21 (RD4)

//*********

//Charge the capacitor on RAO

TRISAbits.TRISA0 = 0;

LATAbits.LATA0 = 1;

for(i = 0; i < 10000; i++) Nop();</pre>

//Stop Charging the capacitor on RAO

TRISAbits.TRISA0 = 1;

//Enable the Ultra Low Power Wakeup module

//and allow capacitor discharge

WDTCONbits.ULPEN = 1;

WDTCONbits.ULPSINK = 1;

//For Sleep, Enable Interrupt for ULPW.

INTCON3bits.INT1IF = 0;

INTCON3bits.INT1IE = 1;

//***************

//Configure Sleep Mode

//********************

//For Sleep

OSCCONbits.IDLEN = 0;

//For Deep Sleep

OSCCONDits.IDLEN = 0i// enable deep sleep

DSCONHbits.DSEN = 1;// Note: must be set just before executing Sleep();

/ / * * * * * * * * * * * * * * * *

//Enter Sleep Mode

/ / * * * * * * * * * * * * * * * *

Sleep();

// for sleep, execution will resume here

// for deep sleep, execution will restart at reset vector (use WDTCONbits.DS to detect)

```

# PIC18F46J11 FAMILY

| TABLE 5-2:              | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |                                |           |                                                                            |                                 |  |  |

|-------------------------|---------------------------------------------------------|--------------------------------|-----------|----------------------------------------------------------------------------|---------------------------------|--|--|

| Register                | Applicabl                                               | Applicable Devices<br>Wa<br>De |           | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |  |

| BAUDCON1                | PIC18F2XJ11                                             | PIC18F4XJ11                    | 0100 0-00 | 0100 0-00                                                                  | uuuu u-uu                       |  |  |

| SPBRGH2                 | PIC18F2XJ11                                             | PIC18F4XJ11                    | 0000 0000 | 0000 0000                                                                  | սսսս սսսս                       |  |  |

| BAUDCON2                | PIC18F2XJ11                                             | PIC18F4XJ11                    | 0100 0-00 | 0100 0-00                                                                  | uuuu u-uu                       |  |  |

| TMR3H                   | PIC18F2XJ11                                             | PIC18F4XJ11                    | xxxx xxxx | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| TMR3L                   | PIC18F2XJ11                                             | PIC18F4XJ11                    | xxxx xxxx | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| T3CON                   | PIC18F2XJ11                                             | PIC18F4XJ11                    | 0000 -000 | uuuu -uuu                                                                  | uuuu –uuu                       |  |  |

| TMR4                    | PIC18F2XJ11                                             | PIC18F4XJ11                    | 0000 0000 | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| PR4                     | PIC18F2XJ11                                             | PIC18F4XJ11                    | 1111 1111 | 1111 1111                                                                  | uuuu uuuu                       |  |  |

| T4CON                   | PIC18F2XJ11                                             | PIC18F4XJ11                    | -000 0000 | -000 0000                                                                  | -uuu uuuu                       |  |  |

| SSP2BUF                 | PIC18F2XJ11                                             | PIC18F4XJ11                    | xxxx xxxx | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |

| SSP2ADD                 | PIC18F2XJ11                                             | PIC18F4XJ11                    | 0000 0000 | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| SSP2MSK                 | PIC18F2XJ11                                             | PIC18F4XJ11                    | 0000 0000 | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| SSP2STAT                | PIC18F2XJ11                                             | PIC18F4XJ11                    | 1111 1111 | 1111 1111                                                                  | uuuu uuuu                       |  |  |

| SSP2CON1                | PIC18F2XJ11                                             | PIC18F4XJ11                    | 0000 0000 | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| SSP2CON2                | PIC18F2XJ11                                             | PIC18F4XJ11                    | 0000 0000 | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| CMSTAT                  | PIC18F2XJ11                                             | PIC18F4XJ11                    | 11        | 11                                                                         | uu                              |  |  |

| PMADDRH <sup>(5)</sup>  | _                                                       | PIC18F4XJ11                    | -000 0000 | -000 0000                                                                  | -uuu uuuu                       |  |  |

| PMDOUT1H <sup>(5)</sup> | _                                                       | PIC18F4XJ11                    | 0000 0000 | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| PMADDRL <sup>(5)</sup>  | _                                                       | PIC18F4XJ11                    | 0000 0000 | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| PMDOUT1L <sup>(5)</sup> | _                                                       | PIC18F4XJ11                    | 0000 0000 | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| PMDIN1H <sup>(5)</sup>  | _                                                       | PIC18F4XJ11                    | 0000 0000 | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| PMDIN1L <sup>(5)</sup>  | _                                                       | PIC18F4XJ11                    | 0000 0000 | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| TXADDRL                 | PIC18F2XJ11                                             | PIC18F4XJ11                    | 0000 0000 | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| TXADDRH                 | PIC18F2XJ11                                             | PIC18F4XJ11                    | 0000      | 0000                                                                       | uuuu                            |  |  |

| RXADDRL                 | PIC18F2XJ11                                             | PIC18F4XJ11                    | 0000 0000 | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| RXADDRH                 | PIC18F2XJ11                                             | PIC18F4XJ11                    | 0000      | 0000                                                                       | uuuu                            |  |  |

| DMABCL                  | PIC18F2XJ11                                             | PIC18F4XJ11                    | 0000 0000 | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| DMABCH                  | PIC18F2XJ11                                             | PIC18F4XJ11                    | 00        | 00                                                                         | uu                              |  |  |

| PMCONH <sup>(5)</sup>   |                                                         | PIC18F4XJ11                    | 00 0000   | 00 0000                                                                    | uu uuuu                         |  |  |

| PMCONL <sup>(5)</sup>   |                                                         | PIC18F4XJ11                    | 000- 0000 | 000- 0000                                                                  | uuu- uuuu                       |  |  |

| PMMODEH <sup>(5)</sup>  | _                                                       | PIC18F4XJ11                    | 0000 0000 | 0000 0000                                                                  | uuuu uuuu                       |  |  |

| PMMODEL <sup>(5)</sup>  | _                                                       | PIC18F4XJ11                    | 0000 0000 | 0000 0000                                                                  | uuuu uuuu                       |  |  |

## TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

- **2:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- **4:** See Table 5-1 for Reset value for specific condition.

- 5: Not implemented for PIC18F2XJ11 devices.

- 6: Not implemented on "LF" devices.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

## 6.2 PIC18 Instruction Cycle

#### 6.2.1 CLOCKING SCHEME

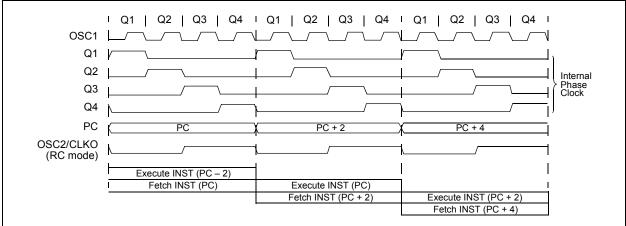

The microcontroller clock input, whether from an internal or external source, is internally divided by '4' to generate four non-overlapping quadrature clocks (Q1, Q2, Q3 and Q4). Internally, the PC is incremented on every Q1; the instruction is fetched from the program memory and latched into the Instruction Register (IR) during Q4. The instruction is decoded and executed during the following Q1 through Q4. Figure 6-4 illustrates the clocks and instruction execution flow.

## 6.2.2 INSTRUCTION FLOW/PIPELINING

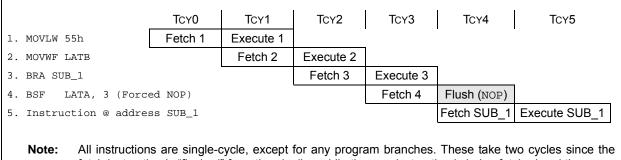

An "Instruction Cycle" consists of four Q cycles, Q1 through Q4. The instruction fetch and execute are pipelined in such a manner that a fetch takes one instruction cycle, while the decode and execute take another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the PC to change (e.g., GOTO), then two cycles are required to complete the instruction (Example 6-3).

A fetch cycle begins with the PC incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the IR in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### EXAMPLE 6-3: INSTRUCTION PIPELINE FLOW

**Note:** All instructions are single-cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

### FIGURE 6-4: CLOCK/INSTRUCTION CYCLE

| File Name         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0         Value on<br>POR, BOR           DMACON2         DLYCYC3         DLYCYC2         DLYCYC1         DLYCYC0         INTLVL3         INTLVL2         INTLVL1         INTLVL0         0000         0000           HUVDCON         VDIRMAG         BGVST         IRVST         HLVDLN         HLVDL3         HLVDL2         HLVDL1         HLVDL0         0000         0000           PORTE         RDPU         REPU         —         —         —         RE2         RE1         RE0         00xxxx           PORTD         RD7         RD6         RD5         RD4         RD3         RD2         RD1         RD0         xxxx xxxx           PORTB         RB7         RB6         RB5         RE4         RB3         RB2         RB1         RB0         xxxx xxxx           PORTA         RA7         RA6         RA5         —         RA3         RA2         RA1         RA0         xxxx xxxx           SPBRGH1         EUSART1 Baud Rate Generator Register High Byte          0000         0000         0000           BAUDCON2         ABDOVF         RCIDL<                                                                                                                   | Details<br>on<br>Page:<br>72, 285<br>72<br>72<br>72<br>72<br>72<br>72<br>72<br>72<br>72, 330<br>72<br>72, 330<br>73 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| HLVDCON         VDIRMAG         BGVST         IRVST         HLVDL3         HLVDL3         HLVDL1         HLVDL0         0000         0000           PORTE         RDPU         REPU         —         —         RE2         RE1         RE0         00xxx           PORTD         RD7         RD6         RD5         RD4         RD3         RD2         RD1         RD0         xxxx xxxx           PORTC         RC7         RC6         RC5         RC4         RC4         RC2         RC1         RC0         xxxx xxxx           PORTA         RA7         RA6         RA5         —         RA3         RA2         RA1         RA0         xxx- xxxx           PORTA         RA7         RA6         RA5         —         RA3         RA2         RA1         RA0         xxx- xxxx           SPBRGH1         EUSART1 Bauf Rate Generator Register High Byte         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000                                                                                                                           | 72<br>72<br>72<br>72<br>72<br>72<br>72<br>72<br>72, 330<br>72<br>72, 330                                            |

| PORTE         RDPU         REPU         —         —         RE2         RE1         RE0         00xxx           PORTD         RD7         RD6         RD5         RD4         RD3         RD2         RD1         RD0         xxxx         xxxx           PORTC         RC7         RC6         RC5         RC4         RC4         RC2         RC1         RC0         xxxx         xxxx           PORTB         RB7         RB6         RB5         RB4         RB3         RB2         RB1         RB0         xxxx         xxxx           PORTA         RA7         RA6         RA5         —         RA3         RA2         RA1         RA0         xxx-         xxxx           SPBRGH1         EUSART1 Baud Rate Generator Register High Byte         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         00                                                                                                                          | 72<br>72<br>72<br>72<br>72<br>72<br>72, 330<br>72<br>72, 330                                                        |

| PORTD         RD7         RD6         RD5         RD4         RD3         RD2         RD1         RD0         xxxx xxxx           PORTC         RC7         RC6         RC5         RC4         RC4         RC2         RC1         RC0         xxxx xxxx           PORTB         RB7         RB6         RB5         RB4         RB3         RB2         RB1         RB0         xxxx xxxx           PORTA         RA7         RA6         RA5         —         RA3         RA2         RA1         RA0         xxx- xxxx           SPBRGH1         EUSART1 Baud Rate Generator Register High Byte         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         <                                                                                                  | 72<br>72<br>72<br>72<br>72<br>72, 330<br>72<br>72, 330                                                              |

| PORTC         RC7         RC6         RC5         RC4         RC4         RC2         RC1         RC0         xxxx xxxx           PORTB         RB7         RB6         RB5         RB4         RB3         RB2         RB1         RB0         xxxx xxxx           PORTA         RA7         RA6         RA5         —         RA3         RA2         RA1         RA0         xxxx xxxx           SPBRGH1         EUSART1 Baud Rate Generator Register High Byte         0000         0000         0000         0000         0000           BAUDCON1         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           SPBRGH2         EUSART2 Baud Rate Generator Register High Byte          0000         0000         0000           BAUDCON2         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           TMR3H         Timer3 Register High Byte         xxxx xxxx         xxxx xxxx         xxxx xxxx         Xxxx xxxx           TMR3L         Timer4 Register         V         WUE         ABDEN         0100         0000         0000                                                                                                        | 72<br>72<br>72<br>72, 330<br>72<br>72, 330                                                                          |

| PORTB         RB7         RB6         RB5         RB4         RB3         RB2         RB1         RB0         xxxx xxxx           PORTA         RA7         RA6         RA5         —         RA3         RA2         RA1         RA0         xxx- xxxx           SPBRGH1         EUSART1 Baud Rate Generator Register High Byte         0000         0000         0000         0000           BAUDCON1         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           SPBRGH2         EUSART2 Baud Rate Generator Register High Byte         0000         0000         0000         0000           BAUDCON2         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           TMR3H         Timer3 Register High Byte         xxxx xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx           TMR3L         Timer3 Register Low Byte         xxxx xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxxx         xxxx         xxxx <td< td=""><td>72<br/>72<br/>72, 330<br/>72<br/>72, 330</td></td<>                      | 72<br>72<br>72, 330<br>72<br>72, 330                                                                                |

| PORTA         RA7         RA6         RA5         —         RA3         RA2         RA1         RA0         xxx-xxxx           SPBRGH1         EUSART1 Baud Rate Generator Register High Byte         0000 0000         0000         0000         0000           BAUDCON1         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100 0-00           SPBRGH2         EUSART2 Baud Rate Generator Register High Byte         0000 0000         0000         0000         0000         0000           BAUDCON2         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100 0-00           TMR3H         Timer3 Register High Byte         xxxx xxxx         xxxx xxxx         xxxx xxxx         Xxxx xxxx           T3CON         TMR3CS1         TMR3CS0         T3CKPS1         T3CKPS0         —         T3SYNC         RD16         TMR3ON         0000 -000           TMR4         Timer4 Register         0100 0-00         TMR4         Timer4 Register         1111 1111         1111 1111           T4CON         —         T40UTPS3         T40UTPS2         T40UTPS0         TMR4ON         T4CKPS0         -0000 0000 <t< td=""><td>72<br/>72<br/>72, 330<br/>72<br/>72, 330</td></t<> | 72<br>72<br>72, 330<br>72<br>72, 330                                                                                |

| SPBRGH1         EUSART1 Baud Rate Generator Register High Byte         0000         0000           BAUDCON1         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           SPBRGH2         EUSART2 Baud Rate Generator Register High Byte          0000         0000         0000           BAUDCON2         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           TMR3H         Timer3 Register High Byte         xxxx xxxx         XXXX         XXXX         XXXX         XXXX           TMR3L         Timer3 Register Low Byte         xxxx XXXX         XXXX         XXXX         XXXX           TMR4         Timer4 Register         0000         0000         0000         0000           PR4         Timer4 Period Register         T40UTPS2         T40UTPS1         T40UTPS0         TMR4ON         T4CKPS1         74CKPS0         -000         0000           SSP2BUF         MSSP2 Address Register (I <sup>2</sup> C™ Slave mode), MSSP2 Baud Rate Reload Register (I <sup>2</sup> C Master mode)         0000         0000         0000           SSP2MSK <sup>(4)</sup> MSK7         MSK6         MSK5         MSK4                      | 72<br>72, 330<br>72<br>72, 330                                                                                      |

| BAUDCON1         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           SPBRGH2         EUSART2 Baud Rate Generator Register High Byte         0000         0000         0000         0000           BAUDCON2         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           TMR3H         Timer3 Register High Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72, 330<br>72<br>72, 330                                                                                            |

| SPBRGH2         EUSART2 Baud Rate Generator Register High Byte         0000 0000           BAUDCON2         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100 0-00           TMR3H         Timer3 Register High Byte         xxxx xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx         xxxx                                                          | 72<br>72, 330                                                                                                       |

| BAUDCON2         ABDOVF         RCIDL         RXDTP         TXCKP         BRG16         —         WUE         ABDEN         0100         0-00           TMR3H         Timer3 Register High Byte         xxxx                                                                                 | 72, 330                                                                                                             |

| TMR3H       Timer3 Register High Byte       xxxx xxxx         TMR3L       Timer3 Register Low Byte       xxxx xxxx         T3CON       TMR3CS1       TMR3CS0       T3CKPS1       T3CKPS0       —       T3SYNC       RD16       TMR3ON       0000       -000         TMR4       Timer4 Register       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       -       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000       0000                                                                                                                                                                                |                                                                                                                     |

| TMR3L         Timer3 Register Low Byte         xxxx xxxx           T3CON         TMR3CS1         TMR3CS0         T3CKPS1         T3CKPS0         —         T3SYNC         RD16         TMR3ON         0000         -000           TMR4         Timer4 Register         0000         0000         0000         0000         0000         0000           PR4         Timer4 Register         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111                                                                                    | 73                                                                                                                  |

| T3CON         TMR3CS1         TMR3CS0         T3CKPS1         T3CKPS0         —         T3SYNC         RD16         TMR3ON         0000         -000           TMR4         Timer4 Register         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000 <t< td=""><td></td></t<>                                                            |                                                                                                                     |

| TMR4         Timer4 Register         0000         0000           PR4         Timer4 Period Register         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111         1111                                                                                  | 73                                                                                                                  |

| PR4         Timer4 Period Register         1111 1111           T4CON         —         T40UTPS3         T40UTPS2         T40UTPS1         T40UTPS0         TMR4ON         T4CKPS1         T4CKPS0         -000         0000           SSP2BUF         MSSP2 Receive Buffer/Transmit Register         xxxx xxxx         xxxx xxxx         xxxx xxxx           SSP2ADD/<br>SSP2MSK <sup>(4)</sup> MSK7         MSK6         MSK5         MSK4         MSK3         MSK2         MSK1         MSK0         1111         1111           SSP2STAT         SMP         CKE         D/Ā         P         S         R/W         UA         BF         0000         0000           SSP2CON1         WCOL         SSPOV         SSPEN         CKP         SSPM3         SSPM2         SSPM1         SSPM0         0000         0000           SSP2CON2         GCEN         ACKSTAT         ACKDT         ACKEN         RCEN         PEN         RSEN         SEN         0000         0000           CMSTAT         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         —         …         …         …                                                                                                                        | 73, 215                                                                                                             |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73                                                                                                                  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 73                                                                                                                  |

| SSP2ADD/<br>SSP2MSK <sup>(4)</sup> MSSP2 Address Register (l <sup>2</sup> C ™ Slave mode), MSSP2 Baud Rate Reload Register (l <sup>2</sup> C Master mode)         0000         0000           SSP2MSK <sup>(4)</sup> MSK7         MSK6         MSK5         MSK4         MSK3         MSK2         MSK1         MSK0         1111         1111           SSP2MSK <sup>(4)</sup> SMP         CKE         D/Ā         P         S         R/₩         UA         BF         0000         0000           SSP2CON1         WCOL         SSPOV         SSPEN         CKP         SSPM3         SSPM2         SSPM1         SSPM0         0000         0000           SSP2CON2         GCEN         ACKSTAT         ACKDT         ACKEN         RCEN         PEN         RSEN         SEN           CMSTAT         —         —         —         —         —         COUT2         COUT1                                                                                                                                                                                                                                                                                                                                                                                                                                       | 73, 225                                                                                                             |

| SSP2MSK <sup>(4)</sup> MSK7         MSK6         MSK5         MSK4         MSK3         MSK2         MSK1         MSK0         1111         1111           SSP2STAT         SMP         CKE         D/Ā         P         S         R/W         UA         BF         0000         0000           SSP2CON1         WCOL         SSPOV         SSPEN         CKP         SSPM3         SSPM2         SSPM1         SSPM0         0000         0000           SSP2CON2         GCEN         ACKSTAT         ACKDT         ACKEN         RCEN         PEN         RSEN         SEN         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000                                                                                                       | 73                                                                                                                  |

| Imisko         Imisko<      | 73, 295                                                                                                             |

| SSP2CON1         WCOL         SSPOV         SSPEN         CKP         SSPM3         SSPM2         SSPM1         SSPM0         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000         0000                                                                             | 73, 295                                                                                                             |

| SSP2CON2         GCEN         ACKSTAT         ACKDT         ACKEN         RCEN         PEN         RSEN         SEN         0000         0000           GCEN         ACKSTAT         ADMSK5 <sup>(4)</sup> ADMSK4 <sup>(4)</sup> ADMSK3 <sup>(4)</sup> ADMSK2 <sup>(4)</sup> ADMSK1 <sup>(4)</sup> SEN         0000         0000         0000           CMSTAT         -         -         -         -         -         COUT2         COUT1        11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73, 273                                                                                                             |

| GCEN         ACKSTAT         ADMSK5 <sup>(4)</sup> ADMSK4 <sup>(4)</sup> ADMSK3 <sup>(4)</sup> ADMSK2 <sup>(4)</sup> ADMSK1 <sup>(4)</sup> SEN           CMSTAT         -         -         -         -         -         COUT2         COUT1        11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 73, 293                                                                                                             |

| CMSTAT         -         -         -         -         COUT2         COUT1        11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73, 294                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                     |

| PMADDRH/ — CS1 Parallel Master Port Address High Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 73, 363                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 73, 179                                                                                                             |

| PMDOUT1H <sup>(5)</sup> Parallel Port Out Data High Byte (Buffer 1) 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 73, 179                                                                                                             |

| PMADDRL/         Parallel Master Port Address Low Byte         0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73, 179                                                                                                             |

| PMDOUT1L <sup>(5)</sup> Parallel Port Out Data Low Byte (Buffer 0) 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 73, 179                                                                                                             |

| PMDIN1H <sup>(5)</sup> Parallel Port In Data High Byte (Buffer 1) 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73                                                                                                                  |

| PMDIN1L <sup>(5)</sup> Parallel Port In Data Low Byte (Buffer 0) 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 73                                                                                                                  |

| TXADDRL         SPI DMA Transit Data Pointer Low Byte         0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 73                                                                                                                  |

| TXADDRH — — — SPI DMA Transit Data Pointer High Byte 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 73                                                                                                                  |

| RXADDRL         SPI DMA Receive Data Pointer Low Byte         0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                     |

| RXADDRH — — — SPI DMA Receive Data Pointer High Byte 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 73                                                                                                                  |

| DMABCL SPI DMA Byte Count Low Byte 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                     |

| DMABCH     —     —     —     —     SPI DMA Receive Data    00       Pointer High Byte     Pointer High Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 73                                                                                                                  |

| PMCONH <sup>(5)</sup> PMPEN — — ADRMUX1 ADRMUX0 PTBEEN PTWREN PTRDEN 00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 73<br>73                                                                                                            |

| PMCONL <sup>(5)</sup> CSF1 CSF0 ALP — CS1P BEP WRSP RDSP 000-0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 73<br>73<br>73                                                                                                      |

| PMMODEH <sup>(5)</sup> BUSY IRQM1 IRQM0 INCM1 INCM0 MODE16 MODE1 MODE0 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 73<br>73<br>73<br>73<br>73                                                                                          |

| PMMODEL <sup>(5)</sup> WAITB1 WAITB0 WAITM3 WAITM2 WAITM1 WAITM0 WAITE1 WAITE0 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73<br>73<br>73<br>73<br>73<br>73, 172                                                                               |

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved. Bold indicates shared access SFRs.

**Note** 1: Bit 21 of the PC is only available in Serial Programming (SP) modes.

2: Reset value is '0' when Two-Speed Start-up is enabled and '1' if disabled.

**3:** The SSPxMSK registers are only accessible when SSPxCON2<3:0> = 1001.

4: Alternate names and definitions for these bits when the MSSP module is operating in I<sup>2</sup>C™ Slave mode. See Section 19.5.3.2 "Address Masking Modes" for details.

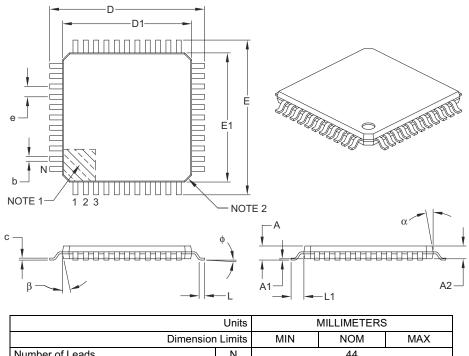

5: These bits and/or registers are only available in 44-pin devices; otherwise, they are unimplemented and read as '0'. Reset values are shown for 44-pin devices.

6: The PMADDRH/PMDOUT1H and PMADDRL/PMDOUT1L register pairs share the same physical registers and addresses, but have different functions determined by the module's operating mode. See Section 11.1.2 "Data Registers" for more information.

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

|       | _   | _   | IC2R4 | IC2R3 | IC2R2 | IC2R1 | IC2R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

|       |     |     |       |       |       |       |       |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                             |                    |  |  |  |

|-------------------|-----------------------------------------------------|-----------------------------|--------------------|--|--|--|