Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 48MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 16                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                |                                                                              |

| RAM Size                   | 3.8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf25j11t-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                                                 | Pin Nu                     | umber    |             |                |                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------|----------------------------|----------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                                        | 28-SPDIP/<br>SSOP/<br>SOIC | 28-QFN   | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                             |

| Vss1                                                                                            | 8                          | 5        | Р           | _              | Ground reference for logic and I/O pins.                                                                                                                                                                |

| Vss2                                                                                            | 19                         | 16       | —           | —              |                                                                                                                                                                                                         |

| Vdd                                                                                             | 20                         | 17       | Р           | —              | Positive supply for peripheral digital logic and I/O pins.                                                                                                                                              |

| VDDCORE/VCAP<br>VDDCORE<br>VCAP                                                                 | 6                          | 3        | P<br>P      | _              | Core logic power or external filter capacitor<br>connection.<br>Positive supply for microcontroller core logic<br>(regulator disabled).<br>External filter capacitor connection (regulator<br>enabled). |

| Legend: TTL = TTL compat<br>ST = Schmitt Trig<br>I = Input<br>P = Power<br>DIG = Digital output | ger input w                | ith CMOS | levels      | A<br>C         | MOS= CMOS compatible input or outputnalog= Analog inputo= OutputD= Open-Drain (no P diode to VDD)                                                                                                       |

### TABLE 1-3: PIC18F2XJ11 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin N      | umber       | Dia                       | Duffer                                   |                                                                                                                                                   |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|---------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44-<br>QFN | 44-<br>TQFP | Pin<br>Type               | Buffer<br>Type                           | Description                                                                                                                                       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |             |                           |                                          | PORTB is a bidirectional I/O port. PORTB can be<br>software programmed for internal weak pull-ups on<br>all inputs.                               |  |  |

| RB0/AN12/INT0/RP3<br>RB0<br>AN12<br>INT0<br>RP3                                                                                                                                                                                                                                                                                                                                                                                                                     | 9          | 8           | I/O<br>I<br>I<br>I/O      | DIG<br>Analog<br>ST<br>DIG               | Digital I/O.<br>Analog input 12.<br>External interrupt 0.<br>Remappable peripheral pin 3.                                                         |  |  |

| RB1/AN10/PMBE/RTCC/RP4<br>RB1<br>AN10<br>PMBE<br>RTCC<br>RP4                                                                                                                                                                                                                                                                                                                                                                                                        | 10         | 9           | I/O<br>I<br>O<br>I/O      | DIG<br>Analog<br>DIG<br>DIG<br>DIG       | Digital I/O.<br>Analog input 10.<br>Parallel Master Port byte enable.<br>Real Time Clock Calendar output.<br>Remappable peripheral pin 4.         |  |  |

| RB2/AN8/CTED1/PMA3/REFO/<br>RP5<br>RB2<br>AN8<br>CTED1<br>PMA3<br>REFO<br>RP5                                                                                                                                                                                                                                                                                                                                                                                       | 11         | 10          | I/O<br>I<br>I<br>O<br>I/O | DIG<br>Analog<br>ST<br>DIG<br>DIG<br>DIG | Digital I/O.<br>Analog input 8.<br>CTMU edge 1 input.<br>Parallel Master Port address.<br>Reference output clock.<br>Remappable peripheral pin 5. |  |  |

| RB3/AN9/CTED2/PMA2/RP6<br>RB3<br>AN9<br>CTED2<br>PMA2<br>RP6                                                                                                                                                                                                                                                                                                                                                                                                        | 12         | 11          | I/O<br>I<br>I<br>O<br>I/O | DIG<br>Analog<br>ST<br>DIG<br>DIG        | Digital I/O.<br>Analog input 9.<br>CTMU edge 2 input.<br>Parallel Master Port address.<br>Remappable peripheral pin 6.                            |  |  |

| RP6       I/O       DIG       Remappable peripheral pin 6.         Legend:       TTL = TTL compatible input       CMOS       = CMOS compatible input or output         ST       = Schmitt Trigger input with CMOS levels       Analog       = Analog input         I       = Input       O       = Output         P       = Power       OD       = Open-Drain (no P diode to VDD)         DIG       = Digital output       O       = Open-Drain (no P diode to VDD) |            |             |                           |                                          |                                                                                                                                                   |  |  |

# TABLE 1-4: PIC18F4XJ11 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

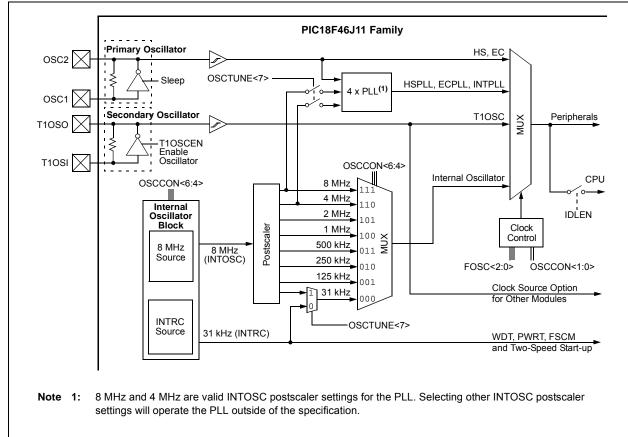

# 3.2.1 OSCILLATOR MODES

Figure 3-1 helps in understanding the oscillator structure of the PIC18F46J11 family of devices.

## FIGURE 3-1: PIC18F46J11 FAMILY CLOCK DIAGRAM

# 4.6.3 DEEP SLEEP WAKE-UP SOURCES

While in Deep Sleep mode, the device can be awakened by a MCLR, POR, RTCC, INTO I/O pin interrupt, DSWDT or ULPWU event. After waking, the device performs a POR. When the device is released from Reset, code execution will begin at the device's Reset vector.

The software can determine if the wake-up was caused from an exit from Deep Sleep mode by reading the DS bit (WDTCON<3>). If this bit is set, the POR was caused by a Deep Sleep exit. The DS bit must be manually cleared by the software.

The software can determine the wake event source by reading the DSWAKEH and DSWAKEL registers. When the application firmware is done using the DSWAKEH and DSWAKEL status registers, individual bits do not need to be manually cleared before entering Deep Sleep again. When entering Deep Sleep mode, these registers are automatically cleared.

#### 4.6.3.1 Wake-up Event Considerations

Deep Sleep wake-up events are only monitored while the processor is fully in Deep Sleep mode. If a wake-up event occurs before Deep Sleep mode is entered, the event status will not be reflected in the DSWAKE registers. If the wake-up source asserts prior to entering Deep Sleep, the CPU may go to the interrupt vector (if the wake source has an interrupt bit and the interrupt is fully enabled), and may abort the Deep Sleep entry sequence by executing past the SLEEP instruction. In this case, a wake-up event handler should be placed after the SLEEP instruction to process the event and re-attempt entry into Deep Sleep if desired.

When the device is in Deep Sleep with more than one wake-up source simultaneously enabled, only the first wake-up source to assert will be detected and logged in the DSWAKEH/DSWAKEL status registers.

### 4.6.4 DEEP SLEEP WATCHDOG TIMER (DSWDT)

Deep Sleep has its own dedicated WDT (DSWDT) with a postscaler for time-outs of 2.1 ms to 25.7 days, configurable through the bits, DSWDTPS<3:0> (CONFIG3L<7:4>).

The DSWDT can be clocked from either the INTRC or the T1OSC/T1CKI input. If the T1OSC/T1CKI source will be used with a crystal, the T1OSCEN bit in the T1CON register needs to be set prior to entering Deep Sleep. The reference clock source is configured through the DSWDTOSC bit (CONFIG3L<0>).

DSWDT is enabled through the DSWDTEN bit (CONFIG3L<3>). Entering Deep Sleep mode automatically clears the DSWDT. See **Section 26.0 "Special Features of the CPU"** for more information.

#### 4.6.5 DEEP SLEEP BROWN OUT RESET (DSBOR)

The Deep Sleep module contains a dedicated Deep Sleep BOR (DSBOR) circuit. This circuit may be optionally enabled through the DSBOREN Configuration bit (CONFIG3L<2>).

The DSBOR circuit monitors the VDD supply rail voltage. The behavior of the DSBOR circuit is described in **Section 5.4** "**Brown-out Reset (BOR)**".

#### 4.6.6 RTCC PERIPHERAL AND DEEP SLEEP

The RTCC can operate uninterrupted during Deep Sleep mode. It can wake the device from Deep Sleep by configuring an alarm.

The RTCC clock source is configured with the RTCOSC bit (CONFIG3L<1>). The available reference clock sources are the INTRC and T1OSC/T1CKI. If the INTRC is used, the RTCC accuracy will directly depend on the INTRC tolerance. For more information on configuring the RTCC peripheral, see Section 17.0 "Real-Time Clock and Calendar (RTCC)".

#### 6.2.3 INSTRUCTIONS IN PROGRAM MEMORY

The program memory is addressed in bytes. Instructions are stored as 2 bytes or 4 bytes in program memory. The Least Significant Byte (LSB) of an instruction word is always stored in a program memory location with an even address (LSB = 0). To maintain alignment with instruction boundaries, the PC increments in steps of 2 and the LSB will always read '0' (see Section 6.1.3 "Program Counter").

Figure 6-5 provides an example of how instruction words are stored in the program memory.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>. which accesses the desired byte address in program memory. Instruction #2 in Figure 6-5 displays how the instruction, GOTO 0006h, is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. Section 27.0 "Instruction Set Summary" provides further details of the instruction set.

| GURE 6-5: | INST           | RUCTION       | S IN PROGF        | RAM MEMORY |         |                           |  |

|-----------|----------------|---------------|-------------------|------------|---------|---------------------------|--|

|           |                |               |                   | LSB = 1    | LSB = 0 | Word Address $\downarrow$ |  |

|           |                | Program Me    |                   |            |         | 000000h                   |  |

|           |                | Byte Location | ons $\rightarrow$ |            |         | 000002h                   |  |

|           |                |               |                   |            |         | 000004h                   |  |

|           |                |               |                   |            |         | 000006h                   |  |

|           | Instruction 1: | MOVLW         | 055h              | 0Fh        | 55h     | 000008h                   |  |

|           | Instruction 2: | GOTO          | 0006h             | EFh        | 03h     | 00000Ah                   |  |

|           |                |               |                   | F0h        | 00h     | 00000Ch                   |  |

|           | Instruction 3: | MOVFF         | 123h, 456         | h C1h      | 23h     | 00000Eh                   |  |

|           |                |               |                   | F4h        | 56h     | 000010h                   |  |

|           |                |               |                   |            |         | 000012h                   |  |

|           |                |               |                   |            |         | 000014h                   |  |

### FIGI

#### 6.2.4 **TWO-WORD INSTRUCTIONS**

The standard PIC18 instruction set has four two-word instructions: CALL, MOVFF, GOTO and LSFR. In all cases, the second word of the instructions always has '1111' as its four Most Significant bits (MSbs); the other 12 bits are literal data, usually a data memory address.

The use of '1111' in the 4 MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence immediately after the first word, the data in the second word is accessed and

used by the instruction sequence. If the first word is skipped for some reason, and the second word is executed by itself, a NOP is executed instead. This is necessary for cases when the two-word instruction is preceded by a conditional instruction that changes the PC. Example 6-4 illustrates how this works.

Note: See Section 6.5 "Program Memory and the Extended Instruction Set" for information on two-word instructions in the extended instruction set.

EXAMPLE 6-4: TWO-WORD INSTRUCTIONS

| CASE 1:             |             |            |                              |

|---------------------|-------------|------------|------------------------------|

| Object Code         | Source Code | 9          |                              |

| 0110 0110 0000 0000 | TSTFSZ      | REG1       | ; is RAM location 0?         |

| 1100 0001 0010 0011 | MOVFF       | REG1, REG2 | ; No, skip this word         |

| 1111 0100 0101 0110 |             |            | ; Execute this word as a NOP |

| 0010 0100 0000 0000 | ADDWF       | REG3       | ; continue code              |

| CASE 2:             |             |            |                              |

| Object Code         | Source Code | 9          |                              |

| 0110 0110 0000 0000 | TSTFSZ      | REG1       | ; is RAM location 0?         |

| 1100 0001 0010 0011 | MOVFF       | REG1, REG2 | ; Yes, execute this word     |

| 1111 0100 0101 0110 |             |            | ; 2nd word of instruction    |

| 0010 0100 0000 0000 | ADDWF       | REG3       | ; continue code              |

### REGISTER 10-9: RPINR4: PERIPHERAL PIN SELECT INPUT REGISTER 4 (BANKED EEAh)

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | T0CKR4 | T0CKR3 | T0CKR2 | T0CKR1 | T0CKR0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

|       |     |     |        |        |        |        |        |

| Legend:           | $R/\overline{W}$ = Readable, Writable i | R/W = Readable, Writable if IOLOCK = 0 |                    |  |  |  |  |

|-------------------|-----------------------------------------|----------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit                        | U = Unimplemented bit, read as '0'     |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                        | '0' = Bit is cleared                   | x = Bit is unknown |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 TOCKR<4:0>: Timer0 External Clock Input (TOCKI) to the Corresponding RPn Pin bits

#### REGISTER 10-10: RPINR6: PERIPHERAL PIN SELECT INPUT REGISTER 6 (BANKED EECh)

| U-0   | U-0 | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | T3CKR4 | T3CKR3 | T3CKR2 | T3CKR1 | T3CKR0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable, Writable | R/W = Readable, Writable if IOLOCK = 0 |                    |  |  |  |  |

|-------------------|---------------------------------------|----------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit                      | U = Unimplemented bit, read as '0'     |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                      | '0' = Bit is cleared                   | x = Bit is unknown |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 T3CKR<4:0>: Timer 3 External Clock Input (T3CKI) to the Corresponding RPn Pin bits

#### REGISTER 10-11: RPINR7: PERIPHERAL PIN SELECT INPUT REGISTER 7 (BANKED EEDh)

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | IC1R4 | IC1R3 | IC1R2 | IC1R1 | IC1R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | R/W = Readable, Writable i | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                    |  |  |  |  |

|-------------------|----------------------------|-----------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0'                  |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 IC1R<4:0>: Assign Input Capture 1 (ECCP1) to the Corresponding RPn Pin bits

## REGISTER 10-21: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0 (BANKED EC6h)<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | _   |     | RP0R4 | RP0R3 | RP0R2 | RP0R1 | RP0R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                             |                    |  |  |

|-------------------|-----------------------------------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read | d as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared        | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP0R<4:0>:** Peripheral Output Function is Assigned to RP0 Output Pin bits (see Table 10-14 for peripheral function numbers)

**Note 1:** Register values can be changed only if PPSCON<IOLOCK> = 0.

#### REGISTER 10-22: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1 (BANKED EC7h)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | RP1R4 | RP1R3 | RP1R2 | RP1R1 | RP1R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                             |                    |  |

|-------------------|-----------------------------------------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read | l as '0'           |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared        | x = Bit is unknown |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP1R<4:0>:** Peripheral Output Function is Assigned to RP1 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-23: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2 (BANKED EC8h)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | _   |     | RP2R4 | RP2R3 | RP2R2 | RP2R1 | RP2R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                                    |                    |  |  |

|-------------------|-----------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP2R<4:0>:** Peripheral Output Function is Assigned to RP2 Output Pin bits (see Table 10-14 for peripheral function numbers)

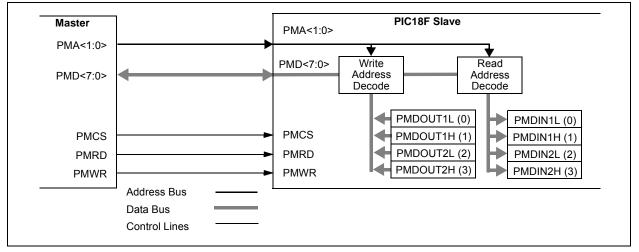

# 11.2.5 ADDRESSABLE PARALLEL SLAVE PORT MODE

In the Addressable Parallel Slave Port mode (PMMODEH<1:0> = 01), the module is configured with two extra inputs, PMA<1:0>, which are the address lines 1 and 0. This makes the 4-byte buffer space directly addressable as fixed pairs of read and write buffers. As with Legacy Buffered mode, data is output from PMDOUT1L, PMDOUT1H, PMDOUT2L and PMDOUT2H, and is read in on PMDIN1L, PMDIN1H, PMDIN2L and PMDIN2L and PMDIN2H. Table 11-1 provides the buffer addressing for the incoming address to the input and output registers.

### TABLE 11-1: SLAVE MODE BUFFER ADDRESSING

| PMA<1:0> | Output<br>Register<br>(Buffer) | Input Register<br>(Buffer) |

|----------|--------------------------------|----------------------------|

| 00       | PMDOUT1L (0)                   | PMDIN1L (0)                |

| 01       | PMDOUT1H (1)                   | PMDIN1H (1)                |

| 10       | PMDOUT2L (2)                   | PMDIN2L (2)                |

| 11       | PMDOUT2H((3)                   | PMDIN2H (3)                |

#### FIGURE 11-6: PARALLEL MASTER/SLAVE CONNECTION ADDRESSED BUFFER EXAMPLE

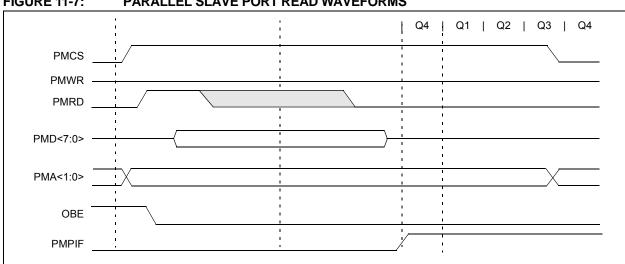

# 11.2.5.1 READ FROM SLAVE PORT

When chip select is active and a read strobe occurs (PMCS = 1 and PMRD = 1), the data from one of the four output bytes is presented onto PMD<7:0>. Which byte is read depends on the 2-bit address placed on ADDR<1:0>. Table 11-1 provides the corresponding

output registers and their associated address. When an output buffer is read, the corresponding OBxE bit is set. The OBxE flag bit is set when all the buffers are empty. If any buffer is already empty, OBxE = 1, the next read to that buffer will generate an OBUF event.

### FIGURE 11-7: PARALLEL SLAVE PORT READ WAVEFORMS

# 19.2 Control Registers

Each MSSP module has three associated control registers. These include a status register (SSPxSTAT) and two control registers (SSPxCON1 and SSPxCON2). The use of these registers and their individual Configuration bits differ significantly depending on whether the MSSP module is operated in SPI or I<sup>2</sup>C mode.

Additional details are provided under the individual sections.

Note: In devices with more than one MSSP module, it is very important to pay close attention to the SSPxCON register names. SSP1CON1 and SSP1CON2 control different operational aspects of the same module, while SSP1CON1 and SSP2CON1 control the same features for two different modules.

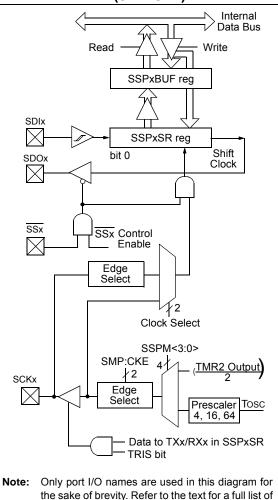

# 19.3 SPI Mode

The SPI mode allows 8 bits of data to be synchronously transmitted and received simultaneously. All four modes of SPI are supported.

When MSSP2 is used in SPI mode, it can optionally be configured to work with the SPI DMA submodule described in **Section 19.4 "SPI DMA Module"**.

To accomplish communication, typically three pins are used:

- Serial Data Out (SDOx) RC5/SDO1/RP16 or SDO2/Remappable

- Serial Data In (SDIx) RC4/SDI1/SDA1/RP15 or SDI2/Remappable

- Serial Clock (SCKx) RC3/SCK1/SCL1/RP14 or SCK2/Remappable

Additionally, a fourth pin may be used when in a Slave mode of operation:

Slave Select (SSx) – RA5/AN4/SS1/ HLVDIN/RP2 or SS2/Remappable

Figure 19-1 depicts the block diagram of the MSSP module when operating in SPI mode.

#### FIGURE 19-1: MSSPx BLOCK DIAGRAM (SPI MODE)

multiplexed functions.

### 19.5.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address, is accomplished by simply writing a value to the SSPxBUF register. This action will set the Buffer Full flag bit, BF, and allow the BRG to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDAx pin after the falling edge of SCLx is asserted (see data hold time specification parameter 106). SCLx is held low for one BRG rollover count (TBRG). Data should be valid before SCLx is released high (see data setup time specification parameter 107). When the SCLx pin is released high, it is held that way for TBRG.

The data on the SDAx pin must remain stable for that duration and some hold time after the next falling edge of SCLx. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDAx. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock.

If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared; if not, the bit is set. After the ninth clock, the SSPxIF bit is set and the master clock (BRG) is suspended until the next data byte is loaded into the SSPxBUF, leaving SCLx low and SDAx unchanged (Figure 19-23).

After the write to the SSPxBUF, each bit of the address will be shifted out on the falling edge of SCLx until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDAx pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDAx pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPxCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPxIF flag is set, the BF flag is cleared and the BRG is turned off until another write to the SSPxBUF takes place, holding SCLx low and allowing SDAx to float.

### 19.5.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPxSTAT<0>) is set when the CPU writes to SSPxBUF and is cleared when all eight bits are shifted out.

### 19.5.10.2 WCOL Status Flag

If the user writes the SSPxBUF when a transmit is already in progress (i.e., SSPxSR is still shifting out a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur) after 2 TcY after the SSPxBUF write. If SSPxBUF is rewritten within 2 TcY, the WCOL bit is set and SSPxBUF is updated. This may result in a corrupted transfer. The user should verify that the WCOL bit is clear after each write to SSPxBUF to ensure the transfer is correct. In all cases, WCOL must be cleared in software.

#### 19.5.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPxCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

# 19.5.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPxCON2<3>).

| Note: | The MSSP module must be in an inactive  |

|-------|-----------------------------------------|

|       | state before the RCEN bit is set or the |

|       | RCEN bit will be disregarded.           |

The BRG begins counting and on each rollover, the state of the SCLx pin changes (high-to-low/low-to-high) and data is shifted into the SSPxSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPxSR are loaded into the SSPxBUF, the BF flag bit is set, the SSPxIF flag bit is set and the BRG is suspended from counting, holding SCLx low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPxCON2<4>).

### 19.5.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPxBUF from SSPxSR. It is cleared when the SSPxBUF register is read.

#### 19.5.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPxSR and the BF flag bit is already set from a previous reception.

#### 19.5.11.3 WCOL Status Flag

If users write the SSPxBUF when a receive is already in progress (i.e., SSPxSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur). The ANCON0 and ANCON1 registers are used to configure the operation of the I/O pin associated with each analog channel. Setting any one of the PCFG bits configures the corresponding pin to operate as a digital only I/O. Clearing a bit configures the pin to operate as an analog input for either the A/D Converter or the comparator module; all digital peripherals are disabled and digital inputs read as '0'. As a rule, I/O pins that are multiplexed with analog inputs default to analog operation on device Resets.

In order to correctly perform A/D conversions on the VBG band gap reference (ADCON0<5:2> = 1111), the reference circuit must be powered on first. The VBGEN bit in the ANCON1 register allows the firmware to manually

request that the band gap reference circuit should be enabled. For best accuracy, firmware should allow a settling time of at least 10 ms prior to performing the first acquisition on this channel after enabling the band gap reference.

The reference circuit may already have been turned on if some other hardware module (such as comparators or HLVD) has already requested it. In this case, the initial turn-on settling time may have already elapsed and firmware does not need to wait as long before measuring VBG. Once the acquisition is complete, firmware may clear the VBGEN bit, which will save a small amount of power if no other modules are still requesting the VBG reference.

| REGISTER 21-3: | ANCON0: A/D PORT CONFIGURATION REGISTER 2 (BANKED F48h) |

|----------------|---------------------------------------------------------|

|----------------|---------------------------------------------------------|

| R/W-0         R/W-0 <th< th=""><th></th><th>h:+</th><th></th><th></th><th>II Induced a</th><th>antad hit raad</th><th> (0)</th><th></th></th<> |                      | h:+                  |                      |       | II Induced a | antad hit raad | (0)   |       |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|-------|--------------|----------------|-------|-------|--|

| PCFG7 <sup>(1)</sup> PCFG6 <sup>(1)</sup> PCFG5 <sup>(1)</sup> PCFG4 PCFG3 PCFG2 PCFG1 PCFG0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Legend:              |                      |                      |       |              |                |       |       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 7                |                      |                      |       |              |                |       | bit 0 |  |

| R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PCFG7 <sup>(1)</sup> | PCFG6 <sup>(1)</sup> | PCFG5 <sup>(1)</sup> | PCFG4 | PCFG3        | PCFG2          | PCFG1 | PCFG0 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                | R/W-0                | R/W-0                | R/W-0 | R/W-0        | R/W-0          | R/W-0 | R/W-0 |  |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

bit 7-0 **PCFG<7:0>:** Analog Port Configuration bits (AN<7:0>) 1 = Pin configured as a digital port 0 = Pin configured as an analog channel – digital input disabled and reads '0'

**Note 1:** These bits are not implemented on 28-pin devices.

### REGISTER 21-4: ANCON1: A/D PORT CONFIGURATION REGISTER 1 (BANKED F49h)

| R/W-0 | r | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|-------|---|-----|--------|--------|--------|-------|-------|

| VBGEN | — | —   | PCFG12 | PCFG11 | PCFG10 | PCFG9 | PCFG8 |

| bit 7 |   |     |        |        |        |       | bit 0 |

| Legend:           | r = Reserved     |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

| bit 7   | <b>VBGEN:</b> 1.2V Band Gap Reference Enable bit<br>1 = 1.2V band gap reference is powered on<br>0 = 1.2V band gap reference is turned off to save power (if no other modules are requesting it) |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | Reserved: Always maintain as '0' for lowest power consumption                                                                                                                                    |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                       |

| bit 4-0 | PCFG<12:8>: Analog Port Configuration bits (AN<12:8>)                                                                                                                                            |

|         | <ul> <li>1 = Pin configured as a digital port</li> <li>0 = Pin configured as an analog channel – digital input disabled and reads '0'</li> </ul>                                                 |

### 25.9 Registers

There are three control registers for the CTMU:

- CTMUCONH

- CTMUCONL

- CTMUICON

The CTMUCONH and CTMUCONL registers (Register 25-1 and Register 25-2) contain control bits for configuring the CTMU module edge source selection, edge source polarity selection, edge sequencing, A/D trigger, analog circuit capacitor discharge and enables. The CTMUICON register (Register 25-3) has bits for selecting the current source range and current source trim.

#### REGISTER 25-1: CTMUCONH: CTMU CONTROL REGISTER HIGH (ACCESS FB3h)

| R/W-0  | U-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0    | R/W-0   | U-0   |

|--------|-----|----------|-------|-------|----------|---------|-------|

| CTMUEN | —   | CTMUSIDL | TGEN  | EDGEN | EDGSEQEN | IDISSEN | —     |

| bit 7  |     |          |       |       |          |         | bit 0 |

|        |     |          |       |       |          |         |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | CTMUEN: CTMU Enable bit                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Module is enabled</li><li>0 = Module is disabled</li></ul>                                                             |

| bit 6 | Unimplemented: Read as '0'                                                                                                         |

| bit 5 | CTMUSIDL: Stop in Idle Mode bit                                                                                                    |

|       | <ul><li>1 = Discontinue module operation when device enters Idle mode</li><li>0 = Continue module operation in Idle mode</li></ul> |

| bit 4 | TGEN: Time Generation Enable bit                                                                                                   |

|       | <ul><li>1 = Enables edge delay generation</li><li>0 = Disables edge delay generation</li></ul>                                     |

| bit 3 | EDGEN: Edge Enable bit                                                                                                             |

|       | 1 = Edges are not blocked<br>0 = Edges are blocked                                                                                 |

| bit 2 | EDGSEQEN: Edge Sequence Enable bit                                                                                                 |

|       | <ul><li>1 = Edge 1 event must occur before Edge 2 event can occur</li><li>0 = No edge sequence is needed</li></ul>                 |

| bit 1 | IDISSEN: Analog Current Source Control bit                                                                                         |

|       | <ul><li>1 = Analog current source output is grounded</li><li>0 = Analog current source output is not grounded</li></ul>            |

| bit 0 | Reserved: Write as '0'                                                                                                             |

|       |                                                                                                                                    |

| R/W-0                                                                | R/W-0                                  | R/W-0                                                | R/W-0          | R/W-0             | R/W-0    | R/W-x           | R/W-x    |

|----------------------------------------------------------------------|----------------------------------------|------------------------------------------------------|----------------|-------------------|----------|-----------------|----------|

| EDG2POL                                                              | EDG2SEL1                               | EDG2SEL0                                             | EDG1POL        | EDG1SEL1          | EDG1SEL0 | EDG2STAT        | EDG1STAT |

| bit 7                                                                | •                                      | •                                                    |                | •                 | •        | •               | bit C    |

|                                                                      |                                        |                                                      |                |                   |          |                 |          |

| Legend:                                                              |                                        |                                                      |                |                   |          |                 |          |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                        |                                                      |                |                   |          |                 |          |

| -n = Value at                                                        | POR                                    | '1' = Bit is set                                     |                | '0' = Bit is clea | ared     | x = Bit is unkr | iown     |

| bit 7                                                                | EDG2POL: E                             | dge 2 Polarity                                       | Select bit     |                   |          |                 |          |

|                                                                      |                                        | rogrammed for<br>rogrammed for                       |                |                   |          |                 |          |

| bit 6-5                                                              | 11 = CTED1<br>10 = CTED2<br>01 = ECCP1 |                                                      | Frigger        | S                 |          |                 |          |

| bit 4                                                                | 1 = Edge 1 p                           | dge 1 Polarity<br>rogrammed for<br>rogrammed for     | a positive edg |                   |          |                 |          |

| bit 3-2                                                              | 11 = CTED1<br>10 = CTED2<br>01 = ECCP1 |                                                      | rigger         | S                 |          |                 |          |

| bit 1                                                                | 1 = Edge 2 e                           | Edge 2 Status b<br>vent has occur<br>vent has not oc | red            |                   |          |                 |          |

| bit 0                                                                | EDG1STAT: E                            | Edge 1 Status b<br>vent has occur<br>vent has not oc | it<br>red      |                   |          |                 |          |

| DEC          | FSZ                               | Decrement                                                                          | Decrement f, Skip if 0                                                                                                                                      |                                                                                |  |  |  |

|--------------|-----------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|

| Synta        | ax:                               | DECFSZ f                                                                           | DECFSZ f {,d {,a}}                                                                                                                                          |                                                                                |  |  |  |

| Oper         | ands:                             | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$ | d ∈ [0,1]                                                                                                                                                   |                                                                                |  |  |  |

| Oper         | ation:                            | (f) – 1 $\rightarrow$ de skip if result                                            |                                                                                                                                                             |                                                                                |  |  |  |

| Statu        | s Affected:                       | None                                                                               |                                                                                                                                                             |                                                                                |  |  |  |

| Enco         | ding:                             | 0010                                                                               | 11da ffi                                                                                                                                                    | ff ffff                                                                        |  |  |  |

| Description: |                                   | decremente<br>placed in W                                                          | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed back in register 'f' (default). |                                                                                |  |  |  |

|              |                                   | which is alro<br>and a NOP i                                                       | is '0', the nex<br>eady fetched i<br>s executed ins<br>le instruction.                                                                                      |                                                                                |  |  |  |

|              |                                   |                                                                                    | he BSR is use                                                                                                                                               | nk is selected.<br>d to select the                                             |  |  |  |

|              |                                   | set is enabl<br>in Indexed I<br>mode when<br>Section 27<br>Bit-Oriente             | nd the extend<br>ed, this instruct<br>Literal Offset /<br>lever $f \le 95$ (5<br>.2.3 "Byte-Or<br>ed Instruction<br>set Mode" for                           | ction operates<br>Addressing<br>Fh). See<br><b>iented and</b><br>Is in Indexed |  |  |  |

| Word         | ls:                               | 1                                                                                  | 1                                                                                                                                                           |                                                                                |  |  |  |

| Cycle        | es:                               | •                                                                                  | cles if skip an<br>2-word instru                                                                                                                            |                                                                                |  |  |  |

| QC           | ycle Activity:                    |                                                                                    |                                                                                                                                                             |                                                                                |  |  |  |

|              | Q1                                | Q2                                                                                 | Q3                                                                                                                                                          | Q4                                                                             |  |  |  |

|              | Decode                            | Read<br>register 'f'                                                               | Process<br>Data                                                                                                                                             | Write to destination                                                           |  |  |  |

| lf sk        | ip:                               | register i                                                                         | Data                                                                                                                                                        | destination                                                                    |  |  |  |

|              | ,<br>Q1                           | Q2                                                                                 | Q3                                                                                                                                                          | Q4                                                                             |  |  |  |

|              | No                                | No                                                                                 | No                                                                                                                                                          | No                                                                             |  |  |  |

|              | operation                         | operation                                                                          | operation                                                                                                                                                   | operation                                                                      |  |  |  |

| lf sk        | -                                 | d by 2-word in                                                                     |                                                                                                                                                             | <b>.</b>                                                                       |  |  |  |

|              | Q1                                | Q2                                                                                 | Q3                                                                                                                                                          | Q4                                                                             |  |  |  |

|              | No<br>operation                   | No<br>operation                                                                    | No<br>operation                                                                                                                                             | No<br>operation                                                                |  |  |  |

|              | No                                | No                                                                                 | No                                                                                                                                                          | No                                                                             |  |  |  |

|              | operation                         | operation                                                                          | operation                                                                                                                                                   | operation                                                                      |  |  |  |

| <u>Exan</u>  | nple:                             | HERE<br>CONTINUE                                                                   | DECFSZ<br>GOTO                                                                                                                                              | CNT, 1, 1<br>LOOP                                                              |  |  |  |

|              | Before Instruc<br>PC              | tion<br>= Address                                                                  | on                                                                                                                                                          |                                                                                |  |  |  |

|              | After Instructio<br>CNT<br>If CNT | = CNT - 1<br>= 0;                                                                  |                                                                                                                                                             |                                                                                |  |  |  |

|              | PC<br>If CNT                      | = Address<br>≠ 0;                                                                  | G (CONTINUE                                                                                                                                                 | ])                                                                             |  |  |  |

|              | PC                                | = Address                                                                          | 6 (HERE + 2                                                                                                                                                 | 2)                                                                             |  |  |  |

| DCFSNZ                                                                                                                                                                                                                                                                              | Decrement                                                                  | f, Skip if n                                                                                                                                                | not 0              |                       |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|--|--|--|

| Syntax:                                                                                                                                                                                                                                                                             | DCFSNZ                                                                     | DCFSNZ f {,d {,a}}                                                                                                                                          |                    |                       |  |  |  |

| Operands:                                                                                                                                                                                                                                                                           | $0 \leq f \leq 255$                                                        | $0 \le f \le 255$                                                                                                                                           |                    |                       |  |  |  |

|                                                                                                                                                                                                                                                                                     | d ∈ [0,1]<br>a ∈ [0,1]                                                     |                                                                                                                                                             |                    |                       |  |  |  |

| Operation:                                                                                                                                                                                                                                                                          | (f) – $1 \rightarrow de$ skip if resul                                     |                                                                                                                                                             |                    |                       |  |  |  |

| Status Affected:                                                                                                                                                                                                                                                                    | None                                                                       |                                                                                                                                                             |                    |                       |  |  |  |

| Encoding:                                                                                                                                                                                                                                                                           | 0100                                                                       | 11da f                                                                                                                                                      | fff                | ffff                  |  |  |  |

| Description:                                                                                                                                                                                                                                                                        | The conten<br>decremente<br>placed in W                                    | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed back in register 'f' (default). |                    |                       |  |  |  |

|                                                                                                                                                                                                                                                                                     | If the result<br>instruction<br>discarded a<br>instead, ma<br>instruction. | which is alreaded and a NOP is                                                                                                                              | eady fe<br>s execu | tched is<br>ted       |  |  |  |

|                                                                                                                                                                                                                                                                                     | lf 'a' is '0', t<br>If 'a' is '1', t<br>GPR bank                           | he BSR is u                                                                                                                                                 |                    |                       |  |  |  |

| If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operate<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 27.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexec<br>Literal Offset Mode" for details. |                                                                            |                                                                                                                                                             |                    |                       |  |  |  |

| Words:                                                                                                                                                                                                                                                                              | 1                                                                          |                                                                                                                                                             |                    |                       |  |  |  |

| Cycles:                                                                                                                                                                                                                                                                             |                                                                            | ycles if skip<br>a 2-word in                                                                                                                                |                    |                       |  |  |  |

| Q Cycle Activity:                                                                                                                                                                                                                                                                   |                                                                            |                                                                                                                                                             |                    |                       |  |  |  |

| Q1                                                                                                                                                                                                                                                                                  | Q2                                                                         | Q3                                                                                                                                                          |                    | Q4                    |  |  |  |

| Decode                                                                                                                                                                                                                                                                              | Read<br>register 'f'                                                       | Process<br>Data                                                                                                                                             |                    | /rite to<br>stination |  |  |  |

| lf skip:                                                                                                                                                                                                                                                                            |                                                                            | Data                                                                                                                                                        | uct                | Sunation              |  |  |  |

| Q1                                                                                                                                                                                                                                                                                  | Q2                                                                         | Q3                                                                                                                                                          |                    | Q4                    |  |  |  |

| No                                                                                                                                                                                                                                                                                  | No                                                                         | No                                                                                                                                                          |                    | No                    |  |  |  |