Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26j11-i-ml |

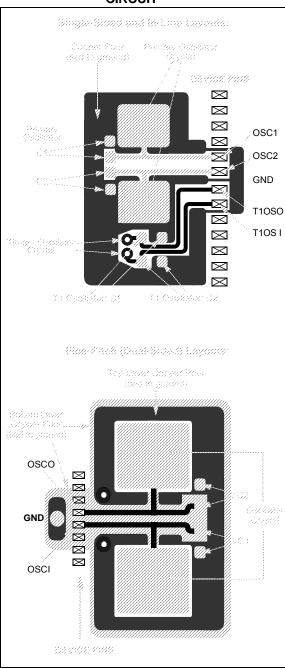

#### 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

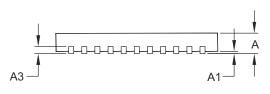

Layout suggestions are shown in Figure 2-5. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro® Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- · AN949, "Making Your Oscillator Work"

#### 2.7 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

FIGURE 2-5: SUGGESTED PLACEMENT

OF THE OSCILLATOR

CIRCUIT

#### 4.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block. This mode allows for controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then clear the SCS bits and execute SLEEP. When the clock source is switched to the INTOSC block, the primary oscillator is shut down and the OSTS bit is cleared.

When a wake event occurs, the peripherals continue to be clocked from the internal oscillator block. After the wake event, the CPU begins executing code being clocked by the INTRC. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the FSCM is enabled.

#### 4.5 Exiting Idle and Sleep Modes

An exit from Sleep mode, or any of the Idle modes, is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes sections (see Section 4.2 "Run Modes", Section 4.3 "Sleep Mode" and Section 4.4 "Idle Modes").

#### 4.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode, or the Sleep mode, to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

On all exits from Idle or Sleep modes by interrupt, code execution branches to the interrupt vector if the GIE/GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see **Section 9.0 "Interrupts"**).

#### 4.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs. If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 4.2 "Run Modes" and Section 4.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 26.2 "Watchdog Timer (WDT)").

The WDT and postscaler are cleared by one of the following events:

- Executing a SLEEP or CLRWDT instruction

- The loss of a currently selected clock source (if the FSCM is enabled)

#### 4.5.3 EXIT BY RESET

Exiting an Idle or Sleep mode by Reset automatically forces the device to run from the INTRC.

## 4.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode (where the primary clock source is not stopped) and the primary clock source is the EC mode

- PRI\_IDLE mode and the primary clock source is the ECPLL mode

In these instances, the primary clock source either does not require an oscillator start-up delay, since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (EC).

#### 4.6 Deep Sleep Mode

Deep Sleep mode brings the device into its lowest power consumption state without requiring the use of external switches to remove power from the device. During deep sleep, the on-chip VDDCORE voltage regulator is powered down, effectively disconnecting power to the core logic of the microcontroller.

Note:

Since Deep Sleep mode powers down the microcontroller by turning off the on-chip VDDCORE voltage regulator, Deep Sleep capability is available only on PIC18FXXJ members in the device family. The on-chip voltage regulator is not available in PIC18LFXXJ members of the device family, and therefore, they do not support Deep Sleep.

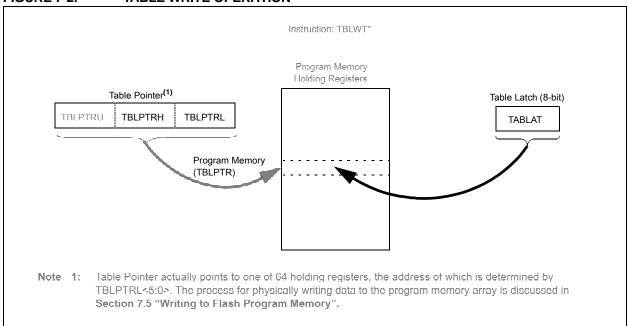

#### FIGURE 7-2: TABLE WRITE OPERATION

#### 7.2 Control Registers

Several control registers are used in conjunction with the TBLRD and TBLWT instructions. Those are:

- EECON1 register

- · EECON2 register

- · TABLAT register

- · TBLPTR registers

#### 7.2.1 EECON1 AND EECON2 REGISTERS

The EECON1 register (Register 7-1) is the control register for memory accesses. The EECON2 register is not a physical register; it is used exclusively in the memory write and erase sequences. Reading EECON2 will read all '0's.

The WPROG bit, when set, will allow programming two bytes per word on the execution of the WR command. If this bit is cleared, the WR command will result in programming on a block of 64 bytes.

The FREE bit, when set, will allow a program memory erase operation. When FREE is set, the erase operation is initiated on the next WR command. When FREE is clear, only writes are enabled.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set in hardware when the WR bit is set, and cleared when the internal programming timer expires and the write operation is complete.

**Note:** During normal operation, the WRERR is read as '1'. This can indicate that a write operation was prematurely terminated by a Reset, or a write operation was attempted improperly.

The WR control bit initiates write operations. The bit cannot be cleared, only set, in software. It is cleared in hardware at the completion of the write operation.

#### **EXAMPLE 7-3: WRITING TO FLASH PROGRAM MEMORY**

| EXAMPLE 7-3.      | ********** | I TU FLASH PRUGRAI       |                                          |

|-------------------|------------|--------------------------|------------------------------------------|

|                   | MOVLW      | CODE_ADDR_UPPER          | ; Load TBLPTR with the base address      |

|                   | MOVWF      | TBLPTRU                  | ; of the memory block, minus 1           |

|                   | MOVLW      | CODE_ADDR_HIGH           | •                                        |

|                   | MOVWF      | TBLPTRH                  |                                          |

|                   | MOVLW      | CODE_ADDR_LOW            |                                          |

|                   | MOVEW      |                          |                                          |

| EDAGE DI CON      | MOVMF      | TBLPTRL                  |                                          |

| ERASE_BLOCK       | 5.05       |                          |                                          |

|                   | BSF        |                          | ; enable write to memory                 |

|                   | BSF        | EECON1, FREE             | ; enable Erase operation                 |

|                   | BCF        | INTCON, GIE              | ; disable interrupts                     |

|                   | MOVLW      | 0x55                     |                                          |

|                   | MOVWF      | EECON2                   | ; write 55h                              |

|                   | MOVLW      | 0xAA                     |                                          |

|                   | MOVWF      | EECON2                   | ; write OAAh                             |

|                   | BSF        | EECON1, WR               | ; start erase (CPU stall)                |

|                   | BSF        | INTCON, GIE              | ; re-enable interrupts                   |

|                   | MOVLW      | D'16'                    | -                                        |

|                   | MOVWF      | WRITE_COUNTER            | ; Need to write 16 blocks of 64 to write |

|                   |            |                          | ; one erase block of 1024                |

| RESTART BUFFER    |            |                          |                                          |

|                   | MOVLW      | D'64'                    |                                          |

|                   | MOVWF      | COUNTER                  |                                          |

|                   | MOVLW      | BUFFER_ADDR_HIGH         | ; point to buffer                        |

|                   | MOVEW      | FSR0H                    | , point to built                         |

|                   | MOVLW      | -                        |                                          |

|                   |            | BUFFER_ADDR_LOW<br>FSR0L |                                          |

| ETI DIEEED        | MOVWF      | ПОЯСТ                    |                                          |

| FILL_BUFFER       |            |                          |                                          |

|                   | • • •      |                          | ; read the new data from I2C, SPI,       |

|                   |            |                          | ; PSP, USART, etc.                       |

| WRITE_BUFFER      |            | 5.64.                    |                                          |

|                   | MOVLW      |                          | ; number of bytes in holding register    |

|                   | MOVWF      | COUNTER                  |                                          |

| WRITE_BYTE_TO_HRE |            |                          |                                          |

|                   | MOVFF      | POSTINCO, WREG           | ; get low byte of buffer data            |

|                   | MOVWF      | TABLAT                   | ; present data to table latch            |

|                   | TBLWT+*    | •                        | ; write data, perform a short write      |

|                   |            |                          | ; to internal TBLWT holding register.    |

|                   | DECFSZ     | COUNTER                  | ; loop until buffers are full            |

|                   | BRA        | WRITE_BYTE_TO_HREGS      |                                          |

| PROGRAM_MEMORY    |            |                          |                                          |

|                   | BSF        | EECON1, WREN             | ; enable write to memory                 |

|                   | BCF        | INTCON, GIE              | ; disable interrupts                     |

|                   | MOVLW      | 0x55                     |                                          |

| Required          | MOVWF      | EECON2                   | ; write 55h                              |

| Sequence          | MOVLW      | 0xAA                     |                                          |

|                   | MOVWF      | EECON2                   | ; write OAAh                             |

|                   | BSF        | EECON1, WR               | ; start program (CPU stall)              |

|                   | BSF        | INTCON, GIE              | ; re-enable interrupts                   |

|                   | BCF        | EECON1, WREN             | ; disable write to memory                |

|                   | DCT.       | DECOME, MICEIN           | , albabic write to memory                |

|                   | DECEC7     | WRITE_COUNTER            | ; done with one write cycle              |

|                   |            |                          |                                          |

| Ì                 | BRA        | RESTART_BUFFER           | ; if not done replacing the erase block  |

|                   |            |                          |                                          |

#### 7.5.3 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

## 7.5.4 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and

reprogrammed if needed. If the write operation is interrupted by a  $\overline{\text{MCLR}}$  Reset or a WDT time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

## 7.6 Flash Program Operation During Code Protection

See Section 26.6 "Program Verification and Code Protection" for details on code protection of Flash program memory.

TABLE 7-2: REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

| Name    | Bit 7                                                       | Bit 6                                                            | Bit 5     | Bit 4       | Bit 3      | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values on<br>Page: |

|---------|-------------------------------------------------------------|------------------------------------------------------------------|-----------|-------------|------------|--------|--------|-------|-----------------------------|

| TBLPTRU | _                                                           | — bit 21 Program Memory Table Pointer Upper Byte (TBLPTR<20:16>) |           |             |            |        |        | 69    |                             |

| TBPLTRH | Program Memory Table Pointer High Byte (TBLPTR<15:8>)       |                                                                  |           |             |            |        |        | 69    |                             |

| TBLPTRL | Program M                                                   | emory Table                                                      | Pointer L | ow Byte (TB | LPTR<7:0>) | )      |        |       | 69                          |

| TABLAT  | Program M                                                   | emory Table                                                      | Latch     |             |            |        |        |       | 69                          |

| INTCON  | GIE/GIEH                                                    | PEIE/GIEL                                                        | TMR0IE    | INT0IE      | RBIE       | TMR0IF | INT0IF | RBIF  | 69                          |

| EECON2  | Program Memory Control Register 2 (not a physical register) |                                                                  |           |             |            |        |        | 71    |                             |

| EECON1  | _                                                           |                                                                  | WPROG     | FREE        | WRERR      | WREN   | WR     | _     | 71                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash program memory access.

Example 8-3 provides the instruction sequence for a 16 x 16 unsigned multiplication. Equation 8-1 provides the algorithm that is used. The 32-bit result is stored in four registers (RES<3:0>).

# EQUATION 8-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

```

RES3:RES0 = ARG1H:ARG1L · ARG2H:ARG2L

= (ARG1H · ARG2H · 2^{16}) +

(ARG1H · ARG2L · 2^{8}) +

(ARG1L · ARG2H · 2^{8}) +

(ARG1L · ARG2L)

```

## EXAMPLE 8-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

```

ARG1L, W

MOVE

MULWF

ARG2L

; ARG1L * ARG2L->

; PRODH:PRODL

PRODH, RES1

MOVFF

MOVFF

PRODL, RESO

ARG1H, W

MOVF

; ARG1H * ARG2H->

MULWF

ARG2H

; PRODH: PRODL

MOVFF

PRODH, RES3

;

PRODL, RES2

MOVFF

;

ARG1L, W

MOVF

MULWF

ARG2H

; ARG1L * ARG2H->

; PRODH: PRODL

MOVF

PRODL, W

RES1, F

; Add cross

ADDWF

MOVF

PRODH, W

; products

ADDWFC RES2, F

WREG

CLRF

ADDWFC RES3, F

ARG1H, W

MOVF

; ARG1H * ARG2L->

{\tt MULWF}

ARG2L

; PRODH:PRODL

PRODL, W

MOVF

ADDWF

RES1, F

; Add cross

MOVF

PRODH, W

; products

ADDWFC RES2, F

CLRF

WREG

;

ADDWFC RES3, F

```

Example 8-4 provides the sequence to do a 16 x 16 signed multiply. Equation 8-2 provides the algorithm used. The 32-bit result is stored in four registers (RES<3:0>). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

# EQUATION 8-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

```

RES3:RES0 = ARG1H:ARG1L · ARG2H:ARG2L

= (ARG1H · ARG2H · 2^{16}) +

(ARG1H · ARG2L · 2^{8}) +

(ARG1L · ARG2H · 2^{8}) +

(ARG1L · ARG2L) +

(-1 · ARG2H<7> · ARG1H:ARG1L · 2^{16}) +

(-1 · ARG1H<7> · ARG2H:ARG2L · 2^{16})

```

## EXAMPLE 8-4: 16 x 16 SIGNED MULTIPLY ROUTINE

```

ARG1L,

MOVE

MULWF

ARG2L

; ARG1L * ARG2L ->

; PRODH:PRODL

MOVFF

PRODH, RES1

MOVFF

PRODL, RESO

;

MOVF

ARG1H, W

; ARG1H * ARG2H ->

MULWF

ARG2H

; PRODH:PRODL

PRODH, RES3

MOVFF

;

PRODL, RES2

MOVEE

;

ARG1L, W

MOVF

; ARG1L * ARG2H ->

MULWF

ARG2H

; PRODH: PRODI.

MOVF

PRODL, W

ADDWF

RES1, F

; Add cross

MOVF

PRODH, W

; products

ADDWFC RES2, F

CLRF

WREG

ADDWFC RES3, F

MOVF

ARG1H, W

; ARG1H * ARG2L ->

MULWF

ARG2L

; PRODH:PRODL

MOVF

PRODL, W

ADDWF

RES1, F

; Add cross

MOVF

PRODH, W

; products

ADDWFC RES2, F

WREG

CLRF

ADDWFC RES3, F

BTFSS

ARG2H, 7

; ARG2H: ARG2L neg?

SIGN ARG1

; no, check ARG1

BRA

MOVF

ARG1L, W

;

SUBWF

MOVF

ARG1H, W

;

SUBWFB RES3

SIGN_ARG1

ARG1H, 7

; ARG1H:ARG1L neg?

BTFSS

BRA

CONT_CODE

; no, done

MOVF

ARG2L, W

;

SUBWE

RES2

;

MOVF

ARG2H, W

SUBWFB RES3

CONT_CODE

:

```

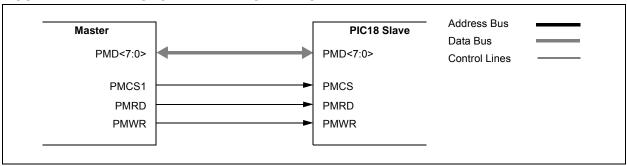

#### 11.2 Slave Port Modes

The primary mode of operation for the module is configured using the MODE<1:0> bits in the PMMODEH register. The setting affects whether the module acts as a slave or a master, and it determines the usage of the control pins.

#### 11.2.1 LEGACY MODE (PSP)

In Legacy mode (PMMODEH<1:0> = 00 and PMPEN = 1), the module is configured as a Parallel Slave Port (PSP) with the associated enabled module

pins dedicated to the module. In this mode, an external device, such as another microcontroller or microprocessor, can asynchronously read and write data using the 8-bit data bus (PMD<7:0>), the read (PMRD), write (PMWR) and chip select (PMCS1) inputs. It acts as a slave on the bus and responds to the read/write control signals.

Figure 11-2 displays the connection of the PSP. When chip select is active and a write strobe occurs (PMCS = 1 and PMWR = 1), the data from PMD<7:0> is captured into the PMDIN1L register.

FIGURE 11-2: LEGACY PARALLEL SLAVE PORT EXAMPLE

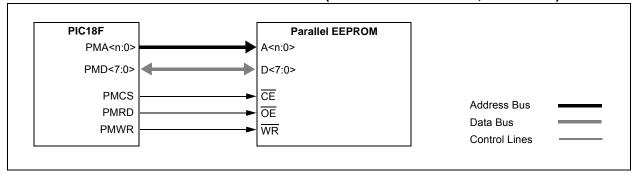

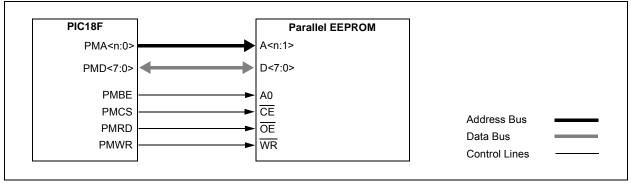

#### 11.4.3 PARALLEL EEPROM EXAMPLE

Figure 11-30 provides an example connecting parallel EEPROM to the PMP. Figure 11-31 demonstrates a slight variation to this, configuring the connection for 16-bit data from a single EEPROM.

FIGURE 11-30: PARALLEL EEPROM EXAMPLE (UP TO 15-BIT ADDRESS, 8-BIT DATA)

FIGURE 11-31: PARALLEL EEPROM EXAMPLE (UP TO 15-BIT ADDRESS, 16-BIT DATA)

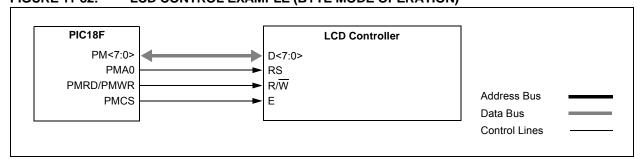

#### 11.4.4 LCD CONTROLLER EXAMPLE

The PMP module can be configured to connect to a typical LCD controller interface, as displayed in Figure 11-32. In this case, the PMP module is configured for active-high control signals since common LCD displays require active-high control.

FIGURE 11-32: LCD CONTROL EXAMPLE (BYTE MODE OPERATION)

#### 17.1 RTCC MODULE REGISTERS

The RTCC module registers are divided into following categories:

#### **RTCC Control Registers**

- RTCCFG

- RTCCAL

- PADCFG1

- ALRMCFG

- ALRMRPT

#### **RTCC Value Registers**

- RTCVALH and RTCVALL Can access the following registers

- YEAR

- MONTH

- DAY

- WEEKDAY

- HOUR

- MINUTE

- SECOND

#### **Alarm Value Registers**

- ALRMVALH and ALRMVALL Can access the following registers:

- ALRMMNTH

- ALRMDAY

- ALRMWD

- ALRMHR

- ALRMMIN

- ALRMSEC

Note:

The RTCVALH and RTCVALL registers can be accessed through RTCRPT<1:0>. ALRMVALH and ALRMVALL can be accessed through ALRMPTR<1:0>.

## 18.5.8 OPERATION IN POWER-MANAGED MODES

In Sleep mode, all clock sources are disabled. Timer2 will not increment and the state of the module will not change. If the ECCPx pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency from HFINTOSC and the postscaler may not be stable immediately.

In PRI\_IDLE mode, the primary clock will continue to clock the ECCPx module without change.

## 18.5.8.1 Operation with Fail-Safe Clock Monitor (FSCM)

If the Fail-Safe Clock Monitor (FSCM) is enabled, a clock failure will force the device into the power-managed RC RUN mode and the OSCFIF bit of

the PIR2 register will be set. The ECCPx will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

#### 18.5.9 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the ECCP registers to their Reset states.

This forces the ECCP module to reset to a state compatible with previous, non-enhanced ECCP modules used on other PIC18 and PIC16 devices.

TABLE 18-5: REGISTERS ASSOCIATED WITH ECCP1 MODULE AND TIMER1 TO TIMER3

| Name     | Bit 7                                    | Bit 6          | Bit 5          | Bit 4    | Bit 3    | Bit 2   | Bit 1   | Bit 0   | Reset<br>Values<br>on page: |

|----------|------------------------------------------|----------------|----------------|----------|----------|---------|---------|---------|-----------------------------|

| INTCON   | GIE/GIEH                                 | PEIE/GIEL      | TMR0IE         | INT0IE   | RABIE    | TMR0IF  | INT0IF  | RABIF   | 69                          |

| RCON     | IPEN                                     | -              | _              | RI       | TO       | PD      | POR     | BOR     | 70                          |

| PIR1     | PMPIF <sup>(1)</sup>                     | ADIF           | RCIF           | TXIF     | SSPIF    | CCP1IF  | TMR2IF  | TMR1IF  | 72                          |

| PIE1     | PMPIE <sup>(1)</sup>                     | ADIE           | RCIE           | TXIE     | SSPIE    | CCP1IE  | TMR2IE  | TMR1IE  | 72                          |

| IPR1     | PMPIP <sup>(1)</sup>                     | ADIP           | RCIP           | TXIP     | SSPIP    | CCP1IP  | TMR2IP  | TMR1IP  | 72                          |

| PIR2     | OSCFIF                                   | CM2IF          | CM1IF          | _        | BCL1IF   | LVDIF   | TMR3IF  | CCP2IF  | 72                          |

| PIE2     | OSCFIE                                   | CM2IE          | CM1IE          | _        | BCL1IE   | LVDIE   | TMR3IE  | CCP2IE  | 72                          |

| IPR2     | OSCFIP                                   | CM2IP          | CM1IP          | _        | BCL1IP   | LVDIP   | TMR3IP  | CCP2IP  | 72                          |

| TRISC    | TRISC7                                   | TRISC6         | TRISC5         | TRISC4   | TRISC3   | TRISC2  | TRISC1  | TRISC0  | 72                          |

| TMR1L    | Timer1 Regis                             | ster Low Byte  | )              |          |          |         |         |         | 70                          |

| TMR1H    | Timer1 Regis                             | ster High Byte | 9              |          |          |         |         |         | 70                          |

| TCLKCON  | _                                        | _              | _              | T1RUN    | _        | _       | T3CCP2  | T3CCP1  | 94                          |

| T1CON    | TMR1CS1                                  | TMR1CS0        | T1CKPS1        | T1CKPS0  | T10SCEN  | T1SYNC  | RD16    | TMR10N  | 70                          |

| TMR2     | Timer2 Regis                             | ster           |                |          |          |         |         |         | 70                          |

| T2CON    | _                                        | T2OUTPS3       | T2OUTPS2       | T2OUTPS1 | T2OUTPS0 | TMR2ON  | T2CKPS1 | T2CKPS0 | 70                          |

| PR2      | Timer2 Perio                             | d Register     |                |          |          |         |         |         | 70                          |

| TMR3L    | Timer3 Regis                             | ster Low Byte  | )              |          |          |         |         |         | 73                          |

| TMR3H    | Timer3 Regis                             | ster High Byte | 9              |          |          |         |         |         | 73                          |

| T3CON    | TMR3CS1                                  | TMR3CS0        | T3CKPS1        | T3CKPS0  | _        | T3SYNC  | RD16    | TMR3ON  | 73                          |

| CCPR1L   | Capture/Con                              | npare/PWM F    | Register 1 Lov | v Byte   |          |         |         |         | 72                          |

| CCPR1H   | Capture/Compare/PWM Register 1 High Byte |                |                |          |          |         | 72      |         |                             |

| CCP1CON  | P1M1                                     | P1M0           | DC1B1          | DC1B0    | CCP1M3   | CCP1M2  | CCP1M1  | CCP1M0  | 72                          |

| ECCP1AS  | ECCP1ASE                                 | ECCP1AS2       | ECCP1AS1       | ECCP1AS0 | PSS1AC1  | PSS1AC0 | PSS1BD1 | PSS1BD0 | 70                          |

| ECCP1DEL | P1RSEN                                   | P1DC6          | P1DC5          | P1DC4    | P1DC3    | P1DC2   | P1DC1   | P1DC0   | 72                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during ECCP operation.

Note 1: These bits are only available on 44-pin devices.

#### **EXAMPLE 20-1: CALCULATING BAUD RATE ERROR**

```

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, and 8-bit BRG:

Desired Baud Rate = Fosc/(64 ([SPBRGHx:SPBRGx] + 1))

Solving for SPBRGHx:SPBRGx:

X = ((Fosc/Desired Baud Rate)/64) - 1

= ((16000000/9600)/64) - 1

= [25.042] = 25

Calculated Baud Rate=16000000/(64 (25 + 1))

= 9615

Error = (Calculated Baud Rate - Desired Baud Rate)/Desired Baud Rate

= (9615 - 9600)/9600 = 0.16%

```

#### TABLE 20-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Name     | Bit 7                                          | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset Values on Page: |

|----------|------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-----------------------|

| TXSTAx   | CSRC                                           | TX9   | TXEN  | SYNC  | SENDB | BRGH  | TRMT  | TX9D  | 71                    |

| RCSTAx   | SPEN                                           | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 71                    |

| BAUDCONx | ABDOVF                                         | RCIDL | RXDTP | TXCKP | BRG16 | _     | WUE   | ABDEN | 73                    |

| SPBRGHx  | EUSARTx Baud Rate Generator Register High Byte |       |       |       |       |       |       |       | 73                    |

| SPBRGx   | EUSARTx Baud Rate Generator Register Low Byte  |       |       |       |       |       |       | 71    |                       |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the BRG.

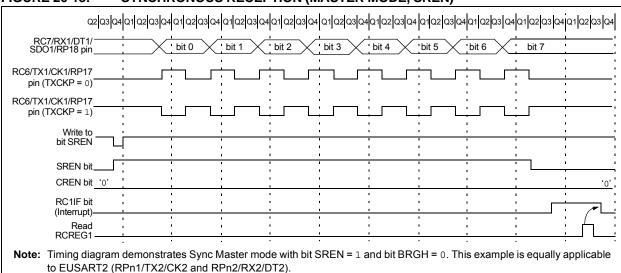

## 20.3.2 EUSART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either the Single Receive Enable bit, SREN (RCSTAx<5>) or the Continuous Receive Enable bit, CREN (RCSTAx<4>). Data is sampled on the RXx pin on the falling edge of the clock.

If enable bit, SREN, is set, only a single word is received. If enable bit, CREN, is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. Ensure bits, CREN and SREN, are clear.

- 4. If interrupts are desired, set enable bit, RCxIE.

- 5. If 9-bit reception is desired, set bit, RX9.

- 6. If a single reception is required, set bit, SREN. For continuous reception, set bit, CREN.

- 7. Interrupt flag bit, RCxIF, will be set when reception is complete and an interrupt will be generated if the enable bit, RCxIE, was set.

- 8. Read the RCSTAx register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREGx register.

- If any error occurred, clear the error by clearing bit, CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### FIGURE 20-13: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

#### REGISTER 25-3: CTMUICON: CTMU CURRENT CONTROL REGISTER (ACCESS FB1h)

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|--------|--------|--------|--------|--------|--------|-------|-------|

| ITRIM5 | ITRIM4 | ITRIM3 | ITRIM2 | ITRIM1 | ITRIM0 | IRNG1 | IRNG0 |

| bit 7  |        |        |        |        |        |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-2 ITRIM<5:0>: Current Source Trim bits

011111 = Maximum positive change from nominal current

011110

•

.

000001 = Minimum positive change from nominal current

000000 = Nominal current output specified by IRNG<1:0>

111111 = Minimum negative change from nominal current

•

•

100010

100001 = Maximum negative change from nominal current

bit 1-0 IRNG<1:0>: Current Source Range Select bits

11 = 100 × Base current

10 = 10 × Base current

01 = Base current level (0.55  $\mu$ A nominal)

00 = Current source disabled

#### TABLE 25-1: REGISTERS ASSOCIATED WITH CTMU MODULE

| Name     | Bit 7   | Bit 6    | Bit 5    | Bit 4   | Bit 3    | Bit 2    | Bit 1    | Bit 0    | Reset<br>Values<br>on page: |

|----------|---------|----------|----------|---------|----------|----------|----------|----------|-----------------------------|

| CTMUCONH | CTMUEN  | _        | CTMUSIDL | TGEN    | EDGEN    | EDGSEQEN | IDISSEN  | _        | 71                          |

| CTMUCONL | EDG2POL | EDG2SEL1 | EDG2SEL0 | EDG1POL | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | 71                          |

| CTMUICON | ITRIM5  | ITRIM4   | ITRIM3   | ITRIM2  | ITRIM1   | ITRIM0   | IRNG1    | IRNG0    | 71                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during ECCP operation.

**ANDWF** AND W with f Syntax: ANDWF  $f \{ d \{ a \} \}$ Operands:  $0 \le f \le 255$  $d \in [0,1]$  $a \in [0,1]$ (W) .AND. (f)  $\rightarrow$  dest

Operation:

Status Affected: N, Z

Encoding: 0001 01da ffff ffff

Description: The contents of W are ANDed with register 'f'. If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back

in register 'f' (default).

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the

GPR bank (default).

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See Section 27.2.3 "Byte-Oriented and **Bit-Oriented Instructions in Indexed** Literal Offset Mode" for details.

Words: Cycles:

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4          |

|--------|--------------|---------|-------------|

| Decode | Read         | Process | Write to    |

|        | register 'f' | Data    | destination |

Example: ANDWF REG, 0, 0

Before Instruction

REG C2h

After Instruction

W 02h REG C2h BC **Branch if Carry**

Syntax: BC n

Operands:  $\text{-}128 \leq n \leq 127$ Operation: if Carry bit is '1',

$(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1110 0010 nnnn nnnn

Description: If the Carry bit is '1', then the program will branch.

> The 2's complement number '2n' is added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a

two-cycle instruction.

Words:

Cycles: 1(2)

Q Cycle Activity:

If Jump:

| Q1        | Q2           | Q3        | Q4        |

|-----------|--------------|-----------|-----------|

| Decode    | Read literal | Process   | Write to  |

|           | ʻn'          | Data      | PC        |

| No        | No           | No        | No        |

| operation | operation    | operation | operation |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | 'n'          | Data    | operation |

Example: HERE BC 5

Before Instruction

PC address (HERE)

After Instruction

If Carry PC

address (HERE + 12)

If Carry PC

address (HERE + 2)

**BRA Unconditional Branch**

Syntax: BRA n

Operands:  $\text{-}1024 \leq n \leq 1023$  $(PC) + 2 + 2n \rightarrow PC$ Operation:

Status Affected: None

Encoding: 1101 0nnn nnnn nnnn

Add the 2's complement number '2n' to Description: the PC. Since the PC will have

incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is a

two-cycle instruction.

Words: 1 2 Cycles:

Q Cycle Activity:

| Q1        | Q2           | Q3        | Q4        |

|-----------|--------------|-----------|-----------|

| Decode    | Read literal | Process   | Write to  |

|           | ʻn'          | Data      | PC        |

| No        | No           | No        | No        |

| operation | operation    | operation | operation |

Example: HERE BRA Jump

Before Instruction

PC address (HERE)

After Instruction

PC address (Jump)

| BSF              | Bit Set f                                             |               |        |   |  |  |  |

|------------------|-------------------------------------------------------|---------------|--------|---|--|--|--|

| Syntax:          | BSF f, b                                              | BSF f, b {,a} |        |   |  |  |  |

| Operands:        | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$ |               |        |   |  |  |  |

| Operation:       | $1 \rightarrow \text{f}$                              |               |        |   |  |  |  |

| Status Affected: | None                                                  |               |        |   |  |  |  |

| Encoding:        | 1000 bbba ffff ffff                                   |               |        |   |  |  |  |

| Description:     | Bit 'b' in re                                         | gister 'f' i  | s set. | • |  |  |  |

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the

GPR bank (default).

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See Section 27.2.3 "Byte-Oriented and **Bit-Oriented Instructions in Indexed** Literal Offset Mode" for details.

Words: Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: BSF FLAG\_REG, 7, 1

Before Instruction

FLAG\_REG 0Ah

After Instruction

FLAG\_REG 8Ah

**LFSR** Load FSR Syntax: LFSR f, k Operands:  $0 \leq f \leq 2$

$0 \le k \le 4095$

Operation:  $k \to FSRf$

Status Affected: None

Encoding: 1110 00ff 1110  $k_{11}kkk$ 1111 0000 k<sub>7</sub>kkk kkkk

Description: The 12-bit literal 'k' is loaded into the file select register pointed to by 'f'.

2 Words: Cycles: 2

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4            |

|--------|--------------|---------|---------------|

| Decode | Read literal | Process | Write         |

|        | 'k' MSB      | Data    | literal 'k'   |

|        |              |         | MSB to        |

|        |              |         | FSRfH         |

| Decode | Read literal | Process | Write literal |

|        | 'k' LSB      | Data    | 'k' to FSRfL  |

Example: LFSR 2, 0x3AB

After Instruction

FSR2H FSR2L 03h ABh

| MOVF             | Move f                                                                         |           |      |      |

|------------------|--------------------------------------------------------------------------------|-----------|------|------|

| Syntax:          | MOVF f                                                                         | {,d {,a}} |      | _    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \\ a \in [0,1] \end{array}$ | 5         |      |      |

| Operation:       | $f \to dest$                                                                   |           |      |      |

| Status Affected: | N, Z                                                                           |           |      |      |

| Encoding:        | 0101                                                                           | 00da      | ffff | ffff |

| Description:     | The contents of register 'f' are moved to a destination dependent upon the     |           |      |      |

status of 'd'. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed back in register 'f' (default). Location 'f' can be anywhere in the

256-byte bank.

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the

GPR bank (default).

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See Section 27.2.3 "Byte-Oriented and **Bit-Oriented Instructions in Indexed**

Literal Offset Mode" for details.

Words: Cycles: 1

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4    |

|--------|--------------|---------|-------|

| Decode | Read         | Process | Write |

|        | register 'f' | Data    | W     |

Example: MOVF REG, 0, 0

Before Instruction

REG W 22h FFh

After Instruction

REG W 22h 22h

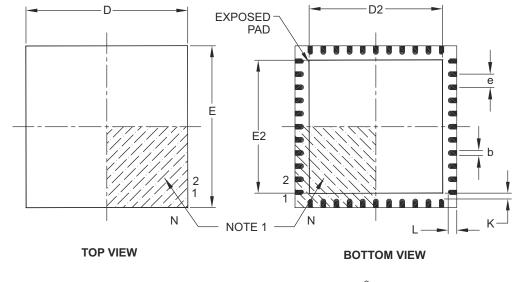

#### 44-Lead Plastic Quad Flat, No Lead Package (ML) – 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |      | MILLIMETERS | 3    |

|------------------------|------------------|------|-------------|------|

|                        | Dimension Limits | MIN  | NOM         | MAX  |

| Number of Pins         | N                |      | 44          |      |

| Pitch                  | е                |      | 0.65 BSC    |      |

| Overall Height         | A                | 0.80 | 0.90        | 1.00 |

| Standoff               | A1               | 0.00 | 0.02        | 0.05 |

| Contact Thickness      | A3               |      | 0.20 REF    |      |

| Overall Width          | E                |      | 8.00 BSC    |      |

| Exposed Pad Width      | E2               | 6.30 | 6.45        | 6.80 |

| Overall Length         | D                |      | 8.00 BSC    |      |

| Exposed Pad Length     | D2               | 6.30 | 6.45        | 6.80 |

| Contact Width          | b                | 0.25 | 0.30        | 0.38 |

| Contact Length         | L                | 0.30 | 0.40        | 0.50 |

| Contact-to-Exposed Pad | K                | 0.20 | -           | _    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103B

## APPENDIX A: REVISION HISTORY

#### **Revision A (October 2008)**

Original data sheet for the PIC18F46J11 family of devices.

#### **Revision B (February 2009)**

Changes to the Electrical Characteristics and minor edits throughout text.

#### **Revision C (October 2009)**

Removed "Preliminary" marking.

#### **Revision D (March 2011)**

Committed data sheet errata changes and minor corrections throughout text.

## APPENDIX B: DEVICE DIFFERENCES

The differences between the devices listed in this data sheet are shown in Table B-1,

TABLE B-1: DEVICE DIFFERENCES BETWEEN PIC18F46J11 FAMILY MEMBERS

| Features                      | PIC18F24J11                                | PIC18F25J11 | PIC18F26J11         | PIC18F44J11         | PIC18F45J11 | PIC18F46J11 |

|-------------------------------|--------------------------------------------|-------------|---------------------|---------------------|-------------|-------------|

| Program Memory                | 16K                                        | 32K         | 64K                 | 16K                 | 32K         | 64K         |

| Program Memory (Instructions) | 8,192                                      | 16,384      | 32,768              | 8,192               | 16,384      | 32,768      |

| I/O Ports (Pins)              | Ports A, B, C                              |             |                     | Ports A, B, C, D, E |             |             |

| 10-Bit ADC Module             | 10 Input Channels                          |             | 13 Input Channels   |                     |             |             |

| Packages                      | 28-Pin QFN, SOIC, SSOP and SPDIP (300 mil) |             | 44-Pin QFN and TQFP |                     |             |             |

| NEGF                                            | 441            | L                                                    |       |

|-------------------------------------------------|----------------|------------------------------------------------------|-------|

| NOP                                             |                | LFSR                                                 | 437   |

| Opcode Field Descriptions                       | 414            | Low-Power Modes                                      |       |

| POP                                             | 442            | Clock Transitions and Status Indicators              |       |

| PUSH                                            | 442            |                                                      |       |

| RCALL                                           | 443            | Deep Sleep Mode                                      | 54    |

| RESET                                           |                | and RTCC Peripheral                                  |       |

| RETFIE                                          |                | Brown-out Reset (DSBOR)                              |       |

| RETLW                                           |                | Preparing for                                        |       |

| RETURN                                          |                | Registers                                            | 58    |

|                                                 |                | Typical Sequence                                     |       |

| RLCF                                            |                | Wake-up Sources                                      | 56    |

| RLNCF                                           |                | Watchdog Timer (DSWDT)                               |       |

| RRCF                                            |                | Exiting Idle and Sleep Modes                         |       |

| RRNCF                                           | 447            | By Interrupt                                         |       |

| SETF                                            |                | By Reset                                             |       |

| SETF (Indexed Literal Offset Mode)              | 461            | By WDT Time-out                                      |       |

| SLEEP                                           | 448            | Without an Oscillator Start-up Delay                 |       |

| Standard Instructions                           | 413            |                                                      |       |

| SUBFWB                                          | 448            | Idle Modes                                           |       |

| SUBLW                                           |                | PRI_IDLE                                             |       |

| SUBWF                                           |                | RC_IDLE                                              |       |

| SUBWFB                                          |                | SEC_IDLE                                             |       |

|                                                 |                | Multiple Sleep Commands                              |       |

| SWAPF                                           |                | Run Modes                                            | 48    |

| TBLRD                                           |                | PRI_RUN                                              | 48    |

| TBLWT                                           |                | RC_RUN                                               | 50    |

| TSTFSZ                                          |                | SEC_RUN                                              |       |

| XORLW                                           |                | Sleep Mode                                           |       |

| XORWF                                           | 454            | Summary (table)                                      |       |

| INTCON                                          | 117            | Ultra Low-Power Wake-up                              |       |

| INTCON Registers                                | 117            | Ollia Low-i Owei Wake-up                             | 01    |

| Inter-Integrated Circuit. See I <sup>2</sup> C. |                | M                                                    |       |

| Internal Oscillator                             |                | Master Clear (MCLR)                                  | G.E.  |

| Frequency Drift. See INTOSC Frequency Drift     | +              |                                                      | 05    |

| Internal Oscillator Block                       |                | Master Synchronous Serial Port (MSSP). See MSSP.     |       |

| Adjustment                                      |                | Memory Organization                                  |       |

|                                                 |                | Data Memory                                          |       |

| OSCTUNE Register Internal RC Oscillator         | 41             | Program Memory                                       |       |

|                                                 | 405            | Return Address Stack                                 | 79    |

| Use with WDT                                    |                | Memory Programming Requirements                      | . 482 |

| Internal Voltage Reference Specifications       |                | Microchip Internet Web Site                          | . 533 |

| Internet Address                                |                | MOVF                                                 | . 437 |

| Interrupt Sources                               | 395            | MOVFF                                                | . 438 |

| A/D Conversion Complete                         | 355            | MOVLB                                                | 438   |

| Capture Complete (ECCP)                         | 249            | MOVLW                                                |       |

| Compare Complete (ECCP)                         | 251            | MOVSF                                                |       |

| Interrupt-on-Change (RB7:RB4)                   |                | MOVSS                                                |       |

| TMR0 Overflow                                   |                | MOVWF                                                |       |

| TMR1 Overflow                                   |                |                                                      |       |

| TMR3 Overflow                                   |                | MPLAB ASM30 Assembler, Linker, Librarian             |       |

| TMR4 to PR4 Match                               |                | MPLAB ICD 2 In-Circuit Debugger                      |       |

|                                                 |                | MPLAB ICE 2000 High-Performance Universal In-Circuit |       |

| TMR4 to PR4 Match (PWM)                         |                | Emulator                                             |       |

| Interrupts                                      |                | MPLAB Integrated Development Environment Software    | . 463 |

| Control Bits                                    | 115            | MPLAB PM3 Device Programmer                          | . 465 |

| Control Registers. See INTCON Registers.        |                | MPLAB REAL ICE In-Circuit Emulator System            | . 465 |

| During, Context Saving                          | 130            | MPLINK Object Linker/MPLIB Object Librarian          | . 464 |

| INTx Pin                                        | 130            | MSSP                                                 |       |

| PORTB, Interrupt-on-Change                      | 130            | ACK Pulse                                            | 299   |

| RCON Register                                   | 129            | I <sup>2</sup> C Mode. See I <sup>2</sup> C Mode.    | , _55 |

| TMR0                                            |                | Module Overview                                      | 271   |

| Interrupts, Flag Bits                           | - <del>-</del> |                                                      |       |

| Interrupt-on-Change (RB7:RB4) Flag (RBIF Bi     | it) 138        | SPI Master/Slave Connection                          |       |

| INTOSC Frequency Drift                          |                | TMR4 Output for Clock Shift                          |       |

| INTOSC, INTRC. See Internal Oscillator Block.   | 71             | MULLW                                                |       |

| IORLW                                           | 126            | MULWF                                                | . 440 |

|                                                 |                | N                                                    |       |

| IORWF                                           | 430            |                                                      |       |

|                                                 |                | NEGF                                                 | . 441 |

| ALRMVAL Register Mapping                        | 242 | SUBLW                                              | . 449 |

|-------------------------------------------------|-----|----------------------------------------------------|-------|

| Calibration                                     | 242 | SUBULNK                                            | . 459 |

| Clock Source                                    | 240 | SUBWF                                              | . 449 |

| Digit Carry Rules                               | 240 | SUBWFB                                             | . 450 |

| General Functionality                           |     | SWAPF                                              | . 450 |

| Leap Year                                       |     |                                                    |       |

| Register Mapping                                |     | Т                                                  |       |

| RTCVAL Register Mapping                         |     | Table Pointer Operations with TBLRD, TBLWT (table) | 106   |

|                                                 |     | Table Reads/Table Writes                           |       |

| Safety Window for Register Reads and Write      |     | TAD                                                |       |

| Write Lock                                      |     |                                                    |       |

| Peripheral Module Disable (PMD) Register        |     | TBLRD                                              |       |

| Register Interface                              |     | TBLWT                                              |       |

| Register Maps                                   |     | Timer0                                             |       |

| Reset                                           | 244 | Associated Registers                               |       |

| Device                                          | 244 | Operation                                          | 198   |

| Power-on Reset (POR)                            | 244 | Overflow Interrupt                                 | 199   |

| Value Registers (RTCVAL)                        |     | Prescaler                                          | 199   |

| RTCEN Bit Write                                 |     | Switching Assignment                               | . 199 |

|                                                 | 00  | Prescaler Assignment (PSA Bit)                     |       |

| S                                               |     | Prescaler Select (T0PS2:T0PS0 Bits)                |       |

| SCKx                                            | 272 | Reads and Writes in 16-Bit Mode                    |       |

| SDIx                                            |     | Source Edge Select (T0SE Bit)                      |       |

|                                                 |     |                                                    |       |

| SDOx                                            |     | Source Select (T0CS Bit)                           |       |

| SEC_IDLE Mode                                   |     | Timer1                                             |       |

| SEC_RUN Mode                                    |     | 16-Bit Read/Write Mode                             |       |

| Serial Clock, SCKx                              |     | Associated Registers                               |       |

| Serial Data In (SDIx)                           | 272 | Clock Source Selection                             | . 204 |

| Serial Data Out (SDOx)                          | 272 | Gate                                               | . 208 |

| Serial Peripheral Interface. See SPI Mode.      |     | Interrupt                                          | 207   |

| SETF                                            | 447 | Operation                                          | . 204 |

| Shoot-Through Current                           |     | Oscillator                                         |       |

| Slave Select (SSx)                              |     | Layout Considerations                              |       |

| SLEEP                                           |     | Resetting, Using the ECCP Special Event Trigger .  |       |

| Software Simulator (MPLAB SIM)                  |     | TMR1H Register                                     |       |

| Special Event Trigger. See Compare (ECCP Mode). | 404 | TMR1L Register                                     |       |

|                                                 | 205 |                                                    |       |

| Special Features of the CPU                     |     | Use as a Clock Source                              |       |

| SPI Mode (MSSP)                                 |     | Timer2                                             |       |

| Associated Registers                            |     | Associated Registers                               |       |

| Bus Mode Compatibility                          |     | Interrupt                                          |       |

| Clock Speed, Interactions                       |     | Operation                                          | 213   |

| Effects of a Reset                              | 280 | Output                                             | . 214 |

| Enabling SPI I/O                                | 276 | Timer3                                             | 215   |

| Master Mode                                     | 277 | 16-Bit Read/Write Mode                             | 219   |

| Master/Slave Connection                         | 276 | Associated Registers                               | . 223 |

| Operation                                       | 275 | Gate                                               | 219   |

| Open-Drain Output Option                        |     | Operation                                          |       |

| Operation in Power-Managed Modes                |     | Oscillator                                         |       |

|                                                 |     |                                                    | •     |

| Registers                                       |     | Overflow Interrupt                                 |       |

| Serial Clock                                    |     | Special Event Trigger (ECCP)                       |       |

| Serial Data In                                  |     | TMR3H Register                                     |       |

| Serial Data Out                                 | 272 | TMR3L Register                                     | 215   |

| Slave Mode                                      | 278 | Timer4                                             |       |

| Slave Select                                    | 272 | Associated Registers                               | . 226 |

| Slave Select Synchronization                    | 278 | Interrupt                                          | 226   |

| SPI Clock                                       |     | MSSP Clock Shift                                   |       |

| SSPxBUF Register                                |     | Operation                                          |       |

| SSPxSR Register                                 |     | Output                                             |       |

| Typical Connection                              |     | Postscaler, See Postscaler, Timer4.                | . 220 |

| <b>71</b>                                       |     | •                                                  | 225   |

| SSPOV                                           |     | PR4 Register                                       | . 225 |

| SSPOV Status Flag                               | 316 | Prescaler. See Prescaler, Timer4.                  |       |

| SSPxS <u>TA</u> T Register                      |     | TMR4 Register                                      |       |

| R/W Bit290                                      | -   | TMR4 to PR4 Match Interrupt 225                    | , 226 |

| SSx                                             | 272 | Timing Diagrams                                    |       |

| Stack Full/Underflow Resets                     | 81  | A/D Conversion                                     | . 506 |

| SUBFSR                                          | 459 | Asynchronous Reception                             |       |

| SUBFWB                                          |     | Asynchronous Transmission                          |       |

|                                                 |     | •                                                  |       |