Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 16                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 10x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

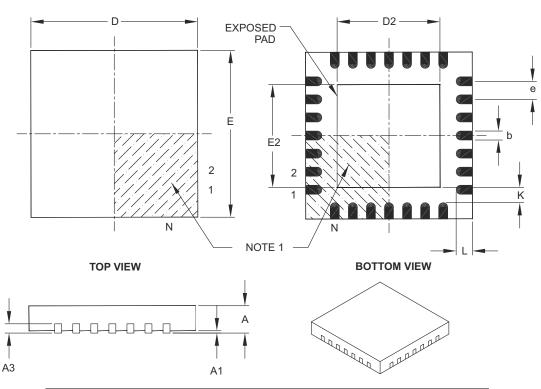

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26j11-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the VDDCORE voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R), or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%/-82\%$ . Due to the extreme temperature tolerance, a 10 µF nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum VDDCORE voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the VDDCORE regulator if the application must operate over a wide temperature range.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

A typical DC bias voltage vs. capacitance graph for X7R type and Y5V type capacitors is shown in Figure 2-4.

#### FIGURE 2-4: DC BIAS VOLTAGE vs. CAPACITANCE **CHARACTERISTICS** Change (%) 0 -10 6V Capacitor -20 -30 Capacitance -40 10V Capacitor -50 -60 -70 6.3V Capacitor -80 -9 10 11 12 13 0 2 3 7 8 14 15 16 DC Bias Voltage (VDC)

When selecting a ceramic capacitor to be used with the VDDCORE voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. For example, choose a ceramic capacitor rated at 16V for the 2.5V VDDCORE voltage. Suggested capacitors are shown in Table 2-1.

## 2.5 ICSP Pins

The PGC and PGD pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed 100 $\Omega$ .

Pull-up resistors, series diodes, and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins), programmed into the device, matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to **Section 28.0 "Development Support"**.

#### REGISTER 9-9: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3 (ACCESS FA3h)

| R/W-0         | R/W-0                       | R/W-0             | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

|---------------|-----------------------------|-------------------|-----------------|-------------------|------------------|-----------------|--------|--|--|--|--|

| SSP2IE        | BCL2IE                      | RC2IE             | TX2IE           | TMR4IE            | CTMUIE           | TMR3GIE         | RTCCIE |  |  |  |  |

| bit 7         |                             |                   |                 |                   |                  |                 | bit 0  |  |  |  |  |

|               |                             |                   |                 |                   |                  |                 |        |  |  |  |  |

| Legend:       |                             |                   |                 |                   |                  |                 |        |  |  |  |  |

| R = Readabl   | le bit                      | W = Writable      | bit             | U = Unimplem      | nented bit, read | l as '0'        |        |  |  |  |  |

| -n = Value at | t POR                       | '1' = Bit is set  | 1               | '0' = Bit is clea | ared             | x = Bit is unkn | own    |  |  |  |  |

|               |                             |                   |                 |                   | 1. 1.9           |                 |        |  |  |  |  |

| bit 7         | 1 = Enabled                 | •                 | us Serial Port  | 2 Interrupt Enab  | ie dit           |                 |        |  |  |  |  |

|               | 1 = Enabled<br>0 = Disabled |                   |                 |                   |                  |                 |        |  |  |  |  |

| bit 6         | BCL2IE: Bus                 | s Collision Inter | upt Enable bit  | (MSSP2 modul      | e)               |                 |        |  |  |  |  |

|               | 1 = Enabled                 |                   |                 | · ·               | ,                |                 |        |  |  |  |  |

|               | 0 = Disabled                | t                 |                 |                   |                  |                 |        |  |  |  |  |

| bit 5         | RC2IE: EUS                  | ART2 Receive      | Interrupt Enab  | le bit            |                  |                 |        |  |  |  |  |

|               | 1 = Enabled                 |                   |                 |                   |                  |                 |        |  |  |  |  |

|               | 0 = Disableo                | -                 |                 |                   |                  |                 |        |  |  |  |  |

| bit 4         |                             | ART2 Transmit     | Interrupt Enab  | le bit            |                  |                 |        |  |  |  |  |

|               | 1 = Enabled<br>0 = Disabled |                   |                 |                   |                  |                 |        |  |  |  |  |

| bit 3         |                             |                   | ob Intorrupt Er | able bit          |                  |                 |        |  |  |  |  |

| DIL 3         | 1 = Enabled                 | R4 to PR4 Mat     | ch interrupt Ei |                   |                  |                 |        |  |  |  |  |

|               | 0 = Disabled                |                   |                 |                   |                  |                 |        |  |  |  |  |

| bit 2         | CTMUIE: Ch                  | arge Time Mea     | surement Unit   | (CTMU) Interru    | pt Enable bit    |                 |        |  |  |  |  |

|               | 1 = Enabled                 | •                 |                 | ,                 | •                |                 |        |  |  |  |  |

|               | 0 = Disabled                | t                 |                 |                   |                  |                 |        |  |  |  |  |

| bit 1         | TMR3GIE: T                  | imer3 Gate Inte   | rrupt Enable b  | oit               |                  |                 |        |  |  |  |  |

|               |                             | 1 = Enabled       |                 |                   |                  |                 |        |  |  |  |  |

|               | 0 = Disabled                |                   |                 |                   |                  |                 |        |  |  |  |  |

| bit 0         |                             | CC Interrupt Er   | able bit        |                   |                  |                 |        |  |  |  |  |

|               | 1 = Enabled                 |                   |                 |                   |                  |                 |        |  |  |  |  |

|               | 0 = Disableo                | 1<br>L            |                 |                   |                  |                 |        |  |  |  |  |

#### 10.7.3.3 Mapping Limitations

The control schema of the PPS is extremely flexible. Other than systematic blocks that prevent signal contention caused by two physical pins being configured as the same functional input or two functional outputs configured as the same pin, there are no hardware enforced lock outs. The flexibility extends to the point of allowing a single input to drive multiple peripherals or a single functional output to drive multiple output pins.

# 10.7.4 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC18F devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- Continuous state monitoring

- Configuration bit remapping lock

### 10.7.4.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes will appear to execute normally, but the contents of the registers will remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (PPSCON<0>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 55h to EECON2<7:0>.

- 2. Write AAh to EECON2<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

IOLOCK remains in one state until changed. This allows all of the PPS registers to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

#### 10.7.4.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

#### 10.7.4.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (CONFIG3H<0>) Configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the PPS control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows users unlimited access (with the proper use of the unlock sequence) to the PPS registers.

#### 10.7.5 CONSIDERATIONS FOR PERIPHERAL PIN SELECTION

The ability to control peripheral pin selection introduces several considerations into application design that could be overlooked. This is particularly true for several common peripherals that are available only as remappable peripherals.

The main consideration is that the PPS is not available on default pins in the device's default (Reset) state. Since all RPINRx registers reset to '11111' and all RPORx registers reset to '00000', all PPS inputs are tied to RP31 and all PPS outputs are disconnected.

Note: In tying PPS inputs to RP31, RP31 does not have to exist on a device for the registers to be reset to it.

This situation requires the user to initialize the device with the proper peripheral configuration before any other application code is executed. Since the IOLOCK bit resets in the unlocked state, it is not necessary to execute the unlock sequence after the device has come out of Reset.

For application safety, however, it is best to set IOLOCK and lock the configuration after writing to the control registers.

Because the unlock sequence is timing critical, it must be executed as an assembly language routine. If the bulk of the application is written in C or another highlevel language, the unlock sequence should be performed by writing in-line assembly.

# 13.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Reset on ECCP Special Event Trigger

- Device clock status flag (T1RUN)

- · Timer with gated control

Figure 13-1 displays a simplified block diagram of the Timer1 module.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 is controlled through the T1CON Control register (Register 13-1). It also contains the Timer1 oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

The Fosc clock source (TMR1CS<1:0> = 01) should not be used with the ECCP capture/compare features. If the timer will be used with the capture or compare features, always select one of the other timer clocking options.

| R/W-0       | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0 | R/W-0  |  |  |

|-------------|---------|---------|---------|---------|--------|-------|--------|--|--|

| TMR1CS1     | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | RD16  | TMR10N |  |  |

| bit 7 bit 0 |         |         |         |         |        |       |        |  |  |

#### REGISTER 13-1: T1CON: TIMER1 CONTROL REGISTER (ACCESS FCDh)

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-6 | TMR1CS<1:0>: Timer1 Clock Source Select bits                                                                                                               |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 10 = Timer1 clock source is T1OSC or T1CKI pin                                                                                                             |

|         | 01 = Timer1 clock source is system clock (Fosc) <sup>(1)</sup>                                                                                             |

|         | 00 = Timer1 clock source is instruction clock (Fosc/4)                                                                                                     |

| bit 5-4 | T1CKPS<1:0>: Timer1 Input Clock Prescale Select bits                                                                                                       |

|         | 11 = 1:8 Prescale value                                                                                                                                    |

|         | 10 = 1:4 Prescale value                                                                                                                                    |

|         | 01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                                                                                                         |

| L:1 0   |                                                                                                                                                            |

| bit 3   | T10SCEN: Timer1 Crystal Oscillator Enable bit                                                                                                              |

|         | 1 = Timer1 oscillator circuit enabled                                                                                                                      |

|         | <ul> <li>0 = Timer1 oscillator circuit disabled</li> <li>The oscillator inverter and feedback resistor are turned off to eliminate power drain.</li> </ul> |

| h:1 0   |                                                                                                                                                            |

| bit 2   | T1SYNC: Timer1 External Clock Input Synchronization Select bit                                                                                             |

|         | $\frac{\text{TMR1CS}<1:0>=10:}{1-\text{De net evretered electric input}}$                                                                                  |

|         | <ul> <li>1 = Do not synchronize external clock input</li> <li>0 = Synchronize external clock input</li> </ul>                                              |

|         | TMR1CS<1:0> = $0x$ :                                                                                                                                       |

|         | This bit is ignored. Timer1 uses the internal clock when TMR1CS<1:0> = $0x$ .                                                                              |

| bit 1   | <b>RD16:</b> 16-Bit Read/Write Mode Enable bit                                                                                                             |

|         | 1 = Enables register read/write of Timer1 in one 16-bit operation                                                                                          |

|         | 0 = Enables register read/write of Timer1 in two 8-bit operations                                                                                          |

| bit 0   | TMR1ON: Timer1 On bit                                                                                                                                      |

| DILU    |                                                                                                                                                            |

|         | 1 = Enables Timer1                                                                                                                                         |

|         | 0 = Stops Timer1                                                                                                                                           |

| Note 1  | The Ease clock source should not be selected if the timer will be used with the ECCP capture/comp                                                          |

**Note 1:** The FOSC clock source should not be selected if the timer will be used with the ECCP capture/compare features.

#### REGISTER 17-5: ALRMRPT: ALARM REPEAT COUNTER (ACCESS F90h)

| bit 7 |       |       |       |       |       |       | bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ARPT7 | ARPT6 | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 |

| R/W-0 |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits 11111111 = Alarm will repeat 255 more times

.

00000000 = Alarm will not repeat

The counter decrements on any alarm event. The counter is prevented from rolling over from 00h to FFh unless CHIME = 1.

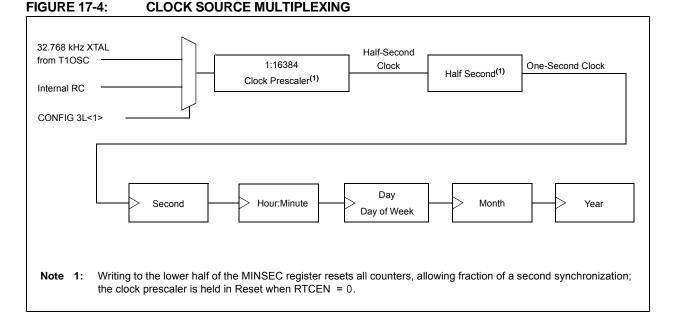

#### 17.2.2 CLOCK SOURCE

As mentioned earlier, the RTCC module is intended to be clocked by an external Real-Time Clock crystal oscillating at 32.768 kHz, but also can be clocked by the INTRC oscillator. The RTCC clock selection is decided by the RTCOSC bit (CONFIG3L<1>). Calibration of the crystal can be done through this module to yield an error of 3 seconds or less per month. (For further details, see **Section 17.2.9 "Calibration**".)

#### 17.2.2.1 Real-Time Clock Enable

The RTCC module can be clocked by an external, 32.768 kHz crystal (Timer1 oscillator) or the INTRC oscillator, which can be selected in CONFIG3L<1>.

If the Timer1 oscillator will be used as the clock source for the RTCC, make sure to enable it by setting T1CON<3> (T1OSCEN). The selected clock can be brought out to the RTCC pin by the RTSECSEL<1:0> bits in the PADCFG1 register.

#### 17.2.3 DIGIT CARRY RULES

This section explains which timer values are affected when there is a rollover.

- Time of Day: From 23:59:59 to 00:00:00 with a carry to the Day field

- Month: From 12/31 to 01/01 with a carry to the Year field

- Day of Week: From 6 to 0 with no carry (see Table 17-1)

- Year Carry: From 99 to 00; this also surpasses the use of the RTCC

For the day to month rollover schedule, see Table 17-2.

Considering that the following values are in BCD format, the carry to the upper BCD digit will occur at a count of 10 and not at 16 (SECONDS, MINUTES, HOURS, WEEKDAY, DAYS and MONTHS).

#### TABLE 17-1: DAY OF WEEK SCHEDULE

| Day of Week |   |  |  |  |  |  |

|-------------|---|--|--|--|--|--|

| Sunday      | 0 |  |  |  |  |  |

| Monday      | 1 |  |  |  |  |  |

| Tuesday     | 2 |  |  |  |  |  |

| Wednesday   | 3 |  |  |  |  |  |

| Thursday    | 4 |  |  |  |  |  |

| Friday      | 5 |  |  |  |  |  |

| Saturday    | 6 |  |  |  |  |  |

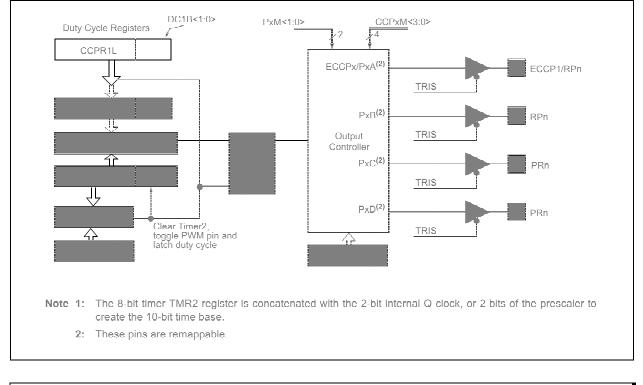

### 18.5 PWM (Enhanced Mode)

The Enhanced PWM mode can generate a PWM signal on up to four different output pins with up to 10 bits of resolution. It can do this through four different PWM Output modes:

- Single PWM

- Half-Bridge PWM

- Full-Bridge PWM, Forward mode

- Full-Bridge PWM, Reverse mode

To select an Enhanced PWM mode, the PxM bits of the CCPxCON register must be set appropriately.

The PWM outputs are multiplexed with I/O pins and are designated: PxA, PxB, PxC and PxD. The polarity of the PWM pins is configurable and is selected by setting the CCPxM bits in the CCPxCON register appropriately.

Table 18-1 provides the pin assignments for each Enhanced PWM mode.

Figure 18-5 provides an example of a simplified block diagram of the Enhanced PWM module.

**Note:** To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

#### FIGURE 18-5: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

#### **Note 1:** The TRIS register value for each PWM output must be configured appropriately.

2: Any pin not used by an Enhanced PWM mode is available for alternate pin functions.

Г

# EXAMPLE 19-2: 512-BYTE SPI MASTER MODE Init AND TRANSFER (CONTINUED)

|                    |              |                | ;Somewhere else in our project, lets assume we have<br>;allocated some RAM for use as SPI receive and<br>;transmit buffers.                                                                                                                                                                                                                         |

|--------------------|--------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ;<br>;DestBuf<br>; | udata<br>res | 0x500<br>0x200 | ;Let's reserve 0x500-0x6FF for use as our SPI<br>;receive data buffer in this example                                                                                                                                                                                                                                                               |

| ;SrcBuf<br>;       | res          | 0x200          | ;Lets reserve 0x700-0x8FF for use as our SPI<br>;transmit data buffer in this example                                                                                                                                                                                                                                                               |

| PrepareTrans       | fer:         |                |                                                                                                                                                                                                                                                                                                                                                     |

| movlw              | HIGH(Des     | tBuf)          | ;Get high byte of DestBuf address (0x05)                                                                                                                                                                                                                                                                                                            |

| movwf              | RXADDRH      | ,              | ¿Load upper four bits of the RXADDR register                                                                                                                                                                                                                                                                                                        |

| movlw              | LOW(Dest     | Buf)           | ;Get low byte of the DestBuf address (0x00)                                                                                                                                                                                                                                                                                                         |

| movwf              | RXADDRL      | . ,            | ;Load lower eight bits of the RXADDR register                                                                                                                                                                                                                                                                                                       |

| movlw              | HIGH(Src     | Buf)           | ;Get high byte of SrcBuf address (0x07)                                                                                                                                                                                                                                                                                                             |

| movwf              | TXADDRH      |                | ;Load upper four bits of the TXADDR register                                                                                                                                                                                                                                                                                                        |

| movlw              | LOW(SrcB     | uf)            | ;Get low byte of the SrcBuf address (0x00)                                                                                                                                                                                                                                                                                                          |

| movwf              | TXADDRL      |                | ;Load lower eight bits of the TXADDR register                                                                                                                                                                                                                                                                                                       |

| movlw              | 0x01         |                | ;Lets move 0x200 (512) bytes in one DMA xfer                                                                                                                                                                                                                                                                                                        |

| movwf              | DMABCH       |                | ;Load the upper two bits of DMABC register                                                                                                                                                                                                                                                                                                          |

| movlw              | 0xFF         |                | ;Actual bytes transferred is (DMABC + 1), so                                                                                                                                                                                                                                                                                                        |

| movwf              | DMABCL       |                | ;we load 0x01FF into DMABC to xfer 0x200 bytes                                                                                                                                                                                                                                                                                                      |

| BeginXfer:         |              |                |                                                                                                                                                                                                                                                                                                                                                     |

| bsf                | DMACON1,     | DMAEN          | ;The SPI DMA module will now begin transferring<br>;the data taken from SrcBuf, and will store<br>;received bytes into DestBuf.                                                                                                                                                                                                                     |

| ;Execute           | whatever     |                | ;CPU is now free to do whatever it wants to<br>;and the DMA operation will continue without<br>;intervention, until it completes.                                                                                                                                                                                                                   |

|                    |              |                | ;When the transfer is complete, the SSP2IF flag in<br>;the PIR3 register will become set, and the DMAEN bit<br>;is automatically cleared by the hardware.<br>;The DestBuf (0x500-0x7FF) will contain the received<br>;data. To start another transfer, firmware will need<br>;to reinitialize RXADDR, TXADDR, DMABC and then<br>;set the DMAEN bit. |

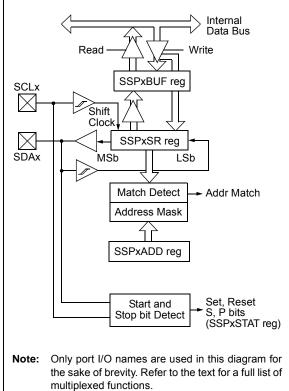

# 19.5 I<sup>2</sup>C Mode

The MSSP module in I<sup>2</sup>C mode fully implements all master and slave functions (including general call support), and provides interrupts on Start and Stop bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications and 7-bit and 10-bit addressing.

Two pins are used for data transfer:

- Serial Clock (SCLx) RC3/SCK1/SCL1/RP14 or RD0/PMD0/SCL2

- Serial Data (SDAx) RC4/SDI1/SDA1/RP15 or RD1/PMD1/SDA2

The user must configure these pins as inputs by setting the associated TRIS bits.

### FIGURE 19-7: MSSPx BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MODE)

# 19.5.1 REGISTERS

The MSSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. These are:

- MSSPx Control Register 1 (SSPxCON1)

- MSSPx Control Register 2 (SSPxCON2)

- MSSPx Status Register (SSPxSTAT)

- Serial Receive/Transmit Buffer Register (SSPxBUF)

- MSSPx Shift Register (SSPxSR) Not directly accessible

- MSSPx Address Register (SSPxADD)

- MSSPx 7-Bit Address Mask Register (SSPxMSK)

SSPxCON1, SSPxCON2 and SSPxSTAT are the control and status registers in I<sup>2</sup>C mode operation. The SSPxCON1 and SSPxCON2 registers are readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

SSPxSR is the shift register used for shifting data in or out. SSPxBUF is the buffer register to which data bytes are written to or read from.

SSPxADD contains the slave device address when the MSSP is configured in I<sup>2</sup>C Slave mode. When the MSSP is configured in Master mode, the lower seven bits of SSPxADD act as the Baud Rate Generator (BRG) reload value.

SSPxMSK holds the slave address mask value when the module is configured for 7-Bit Address Masking mode. While it is a separate register, it shares the same SFR address as SSPxADD; it is only accessible when the SSPM<3:0> bits are specifically set to permit access. Additional details are provided in Section 19.5.3.4 "7-Bit Address Masking Mode".

In receive operations, SSPxSR and SSPxBUF together, create a double-buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not double-buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

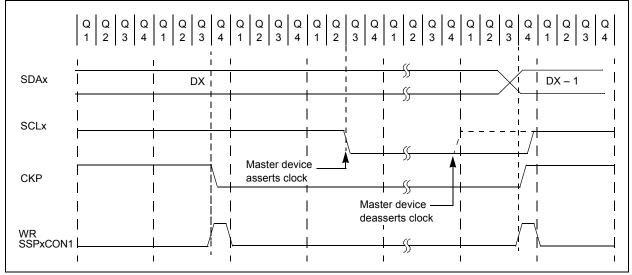

#### 19.5.4.5 Clock Synchronization and CKP bit

When the CKP bit is cleared, the SCLx output is forced to '0'. However, clearing the CKP bit will not assert the SCLx output low until the SCLx output is already sampled low. Therefore, the CKP bit will not assert the SCLx line until an external  $I^2C$  master device has

already asserted the SCLx line. The SCLx output will remain low until the CKP bit is set and all other devices on the  $I^2C$  bus have deasserted SCLx. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCLx (see Figure 19-14).

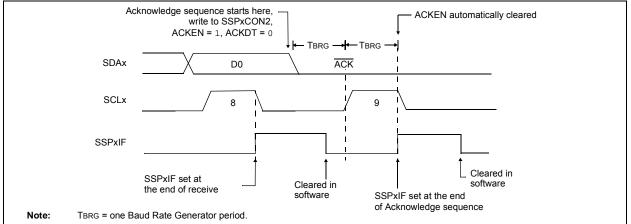

#### 19.5.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit. ACKEN (SSPxCON2<4>). When this bit is set, the SCLx pin is pulled low and the contents of the Acknowledge data bit are presented on the SDAx pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The BRG then counts for one rollover period (TBRG) and the SCLx pin is deasserted (pulled high). When the SCLx pin is sampled high (clock arbitration), the BRG counts for TBRG; the SCLx pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the BRG is turned off and the MSSP module then goes into an inactive state (Figure 19-25).

#### 19.5.12.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write does not occur).

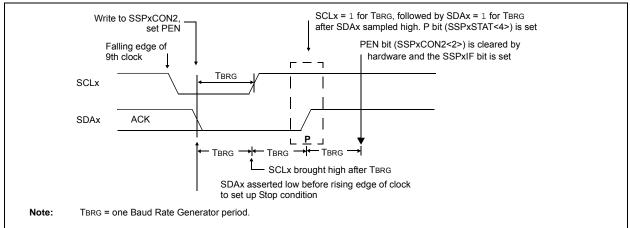

#### 19.5.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDAx pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPxCON2<2>). At the end of a receive/transmit, the SCLx line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDAx line low. When the SDAx line is sampled low, the BRG is reloaded and counts down to 0. When the BRG times out, the SCLx pin will be brought high and one Baud Rate Generator rollover count (TBRG) later, the SDAx pin will be deasserted. When the SDAx pin is sampled high while SCLx is high, the Stop bit (SSPxSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 19-26).

#### 19.5.13.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write does not occur).

### FIGURE 19-25: ACKNOWLEDGE SEQUENCE WAVEFORM

#### FIGURE 19-26: STOP CONDITION RECEIVE OR TRANSMIT MODE

#### 20.3.2 EUSART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either the Single Receive Enable bit, SREN (RCSTAx<5>) or the Continuous Receive Enable bit, CREN (RCSTAx<4>). Data is sampled on the RXx pin on the falling edge of the clock.

If enable bit, SREN, is set, only a single word is received. If enable bit, CREN, is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. Ensure bits, CREN and SREN, are clear.

- 4. If interrupts are desired, set enable bit, RCxIE.

- 5. If 9-bit reception is desired, set bit, RX9.

- 6. If a single reception is required, set bit, SREN. For continuous reception, set bit, CREN.

- 7. Interrupt flag bit, RCxIF, will be set when reception is complete and an interrupt will be generated if the enable bit, RCxIE, was set.

- 8. Read the RCSTAx register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREGx register.

- 10. If any error occurred, clear the error by clearing bit, CREN.

- 11. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| RC7/RX1/DT1/<br>SDO1/RP18 pin       |             | bit 0       | bit 1       | bit 2    | bit 3       | bit 4  | 4 bit       | 5 | bit 6     | bit 7       |             |

|-------------------------------------|-------------|-------------|-------------|----------|-------------|--------|-------------|---|-----------|-------------|-------------|

| RC6/TX1/CK1/RP17<br>pin (TXCKP = 0) | ÷r          |             |             |          |             |        |             |   |           | ;<br>;      | 1<br>1<br>1 |

| RC6/TX1/CK1/RP17<br>pin (TXCKP = 1) | :<br>: L    |             |             |          |             |        |             |   |           | ;<br>;      | 1<br>1<br>1 |

| Write to<br>bit SREN                |             | 1<br>1<br>1 |             |          |             |        | 1<br>1<br>1 |   | <br> <br> | ·<br>·<br>· | <br> <br>   |

| SREN bit                            | <u>.</u>    |             | <br>        | <u> </u> |             |        | <u> </u>    |   | I.<br>I   | <u> </u>    |             |

| CREN bit '0'                        | 1           |             | ı<br>1      |          | 1           | 1<br>1 | 1           |   |           | н<br>1      | 1<br>1      |

| RC1IF bit<br>(Interrupt)———         | 1<br>1      | 1<br>1<br>1 | 1<br>1<br>1 | 1        | 1<br>1<br>1 | 1      | 1           |   |           | <u> </u>    | <u> </u>    |

| Read<br>RCREG1                      | 1<br>1<br>1 | 1<br>1<br>1 | 1<br>1<br>1 |          |             |        |             |   |           | ,<br>,      | <u> </u>    |

#### FIGURE 20-13: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

### 22.2 Comparator Operation

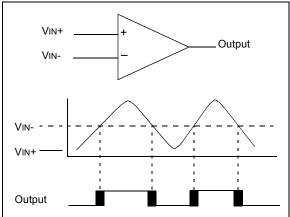

A single comparator is shown in Figure 22-2, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input, VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input, VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 22-2 represent the uncertainty due to input offsets and response time.

FIGURE 22-2: SINGLE COMPARATOR

#### 22.3 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response to a comparator input change. Otherwise, the maximum delay of the comparators should be used (see **Section 29.0 "Electrical Characteristics"**).

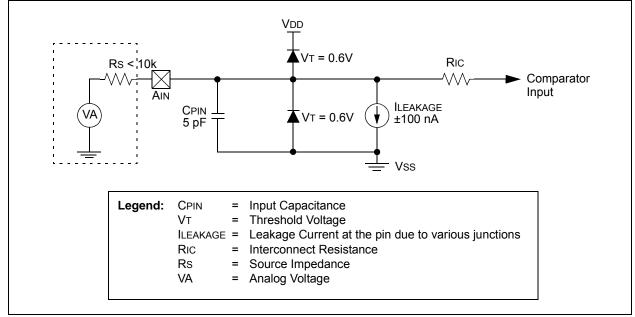

### 22.4 Analog Input Connection Considerations

Figure 22-3 provides a simplified circuit for an analog input. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

NOTES:

| <b>TABLE 27-2</b> : | PIC18F46J11 FAMILY INSTRUCTION SET |

|---------------------|------------------------------------|

|                     |                                    |

| Mnemonic, |                                 | Description                              | Qualas     | 16-  | Bit Instr | uction W | /ord | Status          | Netes      |

|-----------|---------------------------------|------------------------------------------|------------|------|-----------|----------|------|-----------------|------------|

| Opera     | nds                             | Description                              | Cycles     | MSb  |           |          | LSb  | Affected        | Notes      |

| BYTE-ORIE | NTED O                          | PERATIONS                                |            |      |           |          |      |                 |            |

| ADDWF     | f, d, a                         | Add WREG and f                           | 1          | 0010 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ADDWFC    | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010 | 00da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF     | f, d, a                         | AND WREG with f                          | 1          | 0001 | 01da      | ffff     | ffff | Z, N            | 1,2        |

| CLRF      | f, a                            | Clear f                                  | 1          | 0110 | 101a      | ffff     | ffff | Z               | 2          |

| COMF      | f, d, a                         | Complement f                             | 1          | 0001 | 11da      | ffff     | ffff | Z, N            | 1, 2       |

| CPFSEQ    | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110 | 001a      | ffff     | ffff | None            | 4          |

| CPFSGT    | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110 | 010a      | ffff     | ffff | None            | 4          |

| CPFSLT    | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110 | 000a      | ffff     | ffff | None            | 1, 2       |

| DECF      | f, d, a                         | Decrement f                              | 1          | 0000 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ    | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010 | 11da      | ffff     | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ    | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100 | 11da      | ffff     | ffff | None            | 1, 2       |

| INCF      | f, d, a                         | Increment f                              | 1          | 0010 | 10da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ    | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011 | 11da      | ffff     | ffff | None            | 4          |

| INFSNZ    | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100 | 10da      | ffff     | ffff | None            | 1, 2       |

| IORWF     | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001 | 00da      | ffff     | ffff | Z, N            | 1, 2       |

| MOVF      | f, d, a                         | Move f                                   | 1          | 0101 | 00da      | ffff     | ffff | Z, N            | 1          |

| MOVFF     | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100 | ffff      | ffff     | ffff | None            |            |

|           |                                 | f <sub>d</sub> (destination) 2nd word    |            | 1111 | ffff      | ffff     | ffff |                 |            |

| MOVWF     | f, a                            | Move WREG to f                           | 1          | 0110 | 111a      | ffff     | ffff | None            |            |

| MULWF     | f, a                            | Multiply WREG with f                     | 1          | 0000 | 001a      | ffff     | ffff | None            | 1, 2       |

| NEGF      | f, a                            | Negate f                                 | 1          | 0110 | 110a      | ffff     | ffff | C, DC, Z, OV, N |            |

| RLCF      | f, d, a                         | Rotate Left f through Carry              | 1          | 0011 | 01da      | ffff     | ffff | C, Z, N         | 1, 2       |

| RLNCF     | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100 | 01da      | ffff     | ffff | Z, N            |            |

| RRCF      | f, d, a                         | Rotate Right f through Carry             | 1          | 0011 | 00da      | ffff     | ffff | C, Z, N         |            |

| RRNCF     | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100 | 00da      | ffff     | ffff | Z, N            |            |

| SETF      | f, a                            | Set f                                    | 1          | 0110 | 100a      | ffff     | ffff | None            | 1, 2       |

| SUBFWB    | f, d, a                         | Subtract f from WREG with<br>Borrow      | 1          | 0101 | 01da      | ffff     | ffff | C, DC, Z, OV, N |            |

| SUBWF     | f, d, a                         | Subtract WREG from f                     | 1          | 0101 | 11da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWFB    | f, d, a                         | Subtract WREG from f with                | 1          | 0101 | 10da      | ffff     | ffff | C, DC, Z, OV, N |            |

|           |                                 | Borrow                                   |            |      |           |          |      |                 |            |

| SWAPF     | f, d, a                         | Swap Nibbles in f                        | 1          | 0011 | 10da      | ffff     | ffff | None            | 4          |

| TSTFSZ    | f, a                            | Test f, Skip if 0                        | 1 (2 or 3) | 0110 | 011a      | ffff     | ffff | None            | 1, 2       |

| XORWF     | f, d, a                         | Exclusive OR WREG with f                 | 1          | 0001 | 10da      | ffff     | ffff | Z, N            |            |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

3: If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

#### 27.1.1 STANDARD INSTRUCTION SET

| ADDLW                                                  | ADD Litera              | al to W          |                  | ADDWF                                                      | ADD W to                               | f                                                                                                     |                                         |

|--------------------------------------------------------|-------------------------|------------------|------------------|------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------|

| Syntax:                                                | ADDLW                   | k                |                  | Syntax:                                                    | ADDWF                                  | f {,d {,a}}                                                                                           |                                         |

| Operands:                                              | $0 \le k \le 255$       |                  |                  | Operands:                                                  | $0 \leq f \leq 255$                    |                                                                                                       |                                         |

| Operation:                                             | $(W) + k \rightarrow V$ | W                |                  |                                                            | $d \in [0,1]$                          |                                                                                                       |                                         |

| Status Affected:                                       | N, OV, C, E             | DC, Z            |                  | Onenetien                                                  | a ∈ [0,1]                              | ala a t                                                                                               |                                         |

| Encoding:                                              | 0000                    | 1111 kkł         | k kkkk           | Operation:                                                 | $(W) + (f) \rightarrow$                |                                                                                                       |                                         |

| Description:                                           | The conten              | its of W are ad  | ded to the       | Status Affected:                                           | N, OV, C, E                            | ,                                                                                                     |                                         |

|                                                        |                         | 'k' and the resu | ult is placed in | Encoding:                                                  | 0010                                   | 01da ff:                                                                                              |                                         |

|                                                        | W.                      |                  |                  | Description:                                               |                                        | egister 'f'. If 'd'<br>red in W. If 'd'                                                               |                                         |

| Words:                                                 | 1                       |                  |                  |                                                            |                                        | red back in re                                                                                        |                                         |

| Cycles:                                                | 1                       |                  |                  |                                                            | (default).                             |                                                                                                       |                                         |

| Q Cycle Activity:                                      |                         |                  |                  |                                                            |                                        | he Access Bai                                                                                         |                                         |

| Q1                                                     | Q2                      | Q3               | Q4               |                                                            | If 'a' is '1', t<br>GPR bank           | he BSR is use<br>(default)                                                                            | d to select the                         |

| Decode                                                 | Read<br>literal 'k'     | Process<br>Data  | Write to<br>W    |                                                            |                                        | nd the extend                                                                                         | ed instruction                          |

| Example:<br>Before Instruc<br>W =<br>After Instruction | tion<br>10h             | )x15             |                  |                                                            | mode wher<br>Section 27<br>Bit-Oriente | Literal Offset $i$<br>never f $\leq$ 95 (5<br><b>.2.3 "Byte-Or</b><br>ed Instruction<br>set Mode" for | Fh). See<br>iented and<br>is in Indexed |

| VV =                                                   | 25h                     |                  |                  | Words:                                                     | 1                                      |                                                                                                       |                                         |

|                                                        |                         |                  |                  | Cycles:                                                    | 1                                      |                                                                                                       |                                         |

|                                                        |                         |                  |                  | Q Cycle Activity:                                          |                                        |                                                                                                       |                                         |

|                                                        |                         |                  |                  | Q1                                                         | Q2                                     | Q3                                                                                                    | Q4                                      |

|                                                        |                         |                  |                  | Decode                                                     | Read<br>register 'f'                   | Process<br>Data                                                                                       | Write to destination                    |

|                                                        |                         |                  |                  | Example:                                                   | ADDWF                                  | REG, 0, 0                                                                                             |                                         |

|                                                        |                         |                  |                  | Before Instruc<br>W<br>REG<br>After Instructio<br>W<br>REG | = 17h<br>= 0C2h                        |                                                                                                       |                                         |

tions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s).

# PIC18F46J11 FAMILY

| DAW                       | Decimal A                                              | djust W Regis                                         | ter                           | DECF              | Decrement                                                    | f                                                                             |                         |

|---------------------------|--------------------------------------------------------|-------------------------------------------------------|-------------------------------|-------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------|

| Syntax:                   | DAW                                                    |                                                       |                               | Syntax:           | DECF f{,c                                                    | l {,a}}                                                                       |                         |

| Operands:                 | None                                                   |                                                       |                               | Operands:         | $0 \leq f \leq 255$                                          |                                                                               |                         |

| Operation:                | •                                                      | > 9] or [DC = 1                                       | ] then,                       |                   | d ∈ [0,1]<br>a ∈ [0,1]                                       |                                                                               |                         |

|                           | (W<3:0>) +<br>else,                                    | $6 \rightarrow W < 3:0>;$                             |                               | Operation:        | $(f) - 1 \rightarrow de$                                     | set                                                                           |                         |

|                           | (W<3:0>) –                                             | → W<3:0>                                              |                               | Status Affected:  | C, DC, N, C                                                  |                                                                               |                         |

|                           | If [\\/<7·4>                                           | > 9] or [C = 1]                                       | then                          | Encoding:         | 0000                                                         | 01da ff                                                                       | ff ffff                 |

|                           | •                                                      | $^{\circ}$ 6 $\rightarrow$ W<7:4>,                    | unen,                         | Description:      | Decrement                                                    | register 'f'. If                                                              |                         |

|                           | C = 1;                                                 |                                                       |                               | ·                 | result is sto                                                | red in W. If 'd                                                               | ' is '1', the           |

|                           | else,<br>(W<7:4>) –                                    | → W<7:4>                                              |                               |                   | result is sto<br>(default).                                  | red back in re                                                                | egister 'f'             |

| Status Affected:          | С                                                      |                                                       |                               |                   | If 'a' is '0', tl                                            | ne Access Ba                                                                  | nk is selected.         |

| Encoding:<br>Description: | 0000                                                   | 0000 000<br>ts the eight-bit                          |                               |                   | lf 'a' is '1', tl<br>GPR bank                                |                                                                               | ed to select the        |

|                           | resulting fro<br>variables (e<br>and produc<br>result. | om the earlier a<br>each in packed<br>es a correct pa | ddition of two<br>BCD format) |                   | set is enabl<br>in Indexed<br>mode when<br><b>Section 27</b> | ed, this instru<br>Literal Offset<br>lever f ≤ 95 (5<br><b>.2.3 "Byte-O</b> t | Fh). See<br>riented and |

| Words:                    | 1                                                      |                                                       |                               |                   |                                                              |                                                                               | ns in Indexed           |

| Cycles:                   | 1                                                      |                                                       |                               | Words:            | Literal Offs                                                 | set Mode" for                                                                 | details.                |

| Q Cycle Activity:<br>Q1   | Q2                                                     | Q3                                                    | Q4                            | Cycles:           | 1                                                            |                                                                               |                         |

| Decode                    | Read                                                   | Process                                               | Write                         | Q Cycle Activity: | I                                                            |                                                                               |                         |

|                           | register W                                             | Data                                                  | W                             | Q Cycle Activity. | Q2                                                           | Q3                                                                            | Q4                      |

| Example 1:                | DAW                                                    |                                                       |                               | Decode            | Read<br>register 'f'                                         | Process<br>Data                                                               | Write to destination    |

| Before Instruc            |                                                        |                                                       |                               |                   |                                                              |                                                                               |                         |

| W<br>C                    | = A5h<br>= 0                                           |                                                       |                               | Example:          | DECF                                                         | CNT, 1, 0                                                                     | )                       |

| DC<br>After Instruction   | = 0                                                    |                                                       |                               | Before Instru     |                                                              |                                                                               |                         |

| W                         | = 05h                                                  |                                                       |                               | CNT<br>Z          | = 01h<br>= 0                                                 |                                                                               |                         |

| C<br>DC                   | = 1<br>= 0                                             |                                                       |                               | After Instruct    | •                                                            |                                                                               |                         |

| Example 2:                | -                                                      |                                                       |                               | CNT<br>Z          | = 00h<br>= 1                                                 |                                                                               |                         |

| Before Instruct           | ction                                                  |                                                       |                               | <b>–</b>          | ·                                                            |                                                                               |                         |

| W                         | = CEh                                                  |                                                       |                               |                   |                                                              |                                                                               |                         |

| C<br>DC                   | = 0<br>= 0                                             |                                                       |                               |                   |                                                              |                                                                               |                         |

| After Instruction         |                                                        |                                                       |                               |                   |                                                              |                                                                               |                         |

| W<br>C                    | = 34h<br>= 1                                           |                                                       |                               |                   |                                                              |                                                                               |                         |

|                           |                                                        |                                                       |                               |                   |                                                              |                                                                               |                         |

# PIC18F46J11 FAMILY

| NEGF              | Negate f                                                                                            |                                                                  |                                                                    |                                                |

|-------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------|

| Syntax:           | NEGF f                                                                                              | {,a}                                                             |                                                                    |                                                |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 255 \\ a \in [0,1] \end{array}$                                     | 5                                                                |                                                                    |                                                |

| Operation:        | $(\overline{f}) + 1 \rightarrow f$                                                                  |                                                                  |                                                                    |                                                |

| Status Affected:  | N, OV, C,                                                                                           | DC, Z                                                            |                                                                    |                                                |

| Encoding:         | 0110                                                                                                | 110a                                                             | ffff                                                               | ffff                                           |

| Description:      | Location 'f<br>compleme<br>data meme                                                                | nt. The re                                                       | sult is place                                                      |                                                |

|                   | lf 'a' is '0',<br>lf 'a' is '1',<br>GPR bank                                                        | the BSR i                                                        | s used to s                                                        |                                                |

|                   | If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode whe<br>Section 2'<br>Bit-Orient<br>Literal Off | bled, this i<br>Literal O<br>never f ≤<br>7.2.3 "By<br>ed Instru | nstruction<br>ffset Addre<br>95 (5Fh).<br>te-Oriente<br>ictions in | operates<br>essing<br>See<br>ed and<br>Indexed |

| Words:            | 1                                                                                                   |                                                                  |                                                                    |                                                |

| Cycles:           | 1                                                                                                   |                                                                  |                                                                    |                                                |

| Q Cycle Activity: |                                                                                                     |                                                                  |                                                                    |                                                |

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

| Example: | NEGF | REG, | 1 |

|----------|------|------|---|

|          |      |      |   |

| Before Instru  | ction |      |      |       |

|----------------|-------|------|------|-------|

| REG            | =     | 0011 | 1010 | [3Ah] |