Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 48MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 16                                                                           |

| Program Memory Size        | 64KB (32K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                |                                                                              |

| RAM Size                   | 3.8K × 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26j11t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.0 LOW-POWER MODES

The PIC18F46J11 family devices can manage power consumption through clocking to the CPU and the peripherals. In general, reducing the clock frequency and the amount of circuitry being clocked reduces power consumption.

For managing power in an application, the primary modes of operation are:

- Run Mode

- Idle Mode

- Sleep Mode

- · Deep Sleep Mode

Additionally, there is an Ultra Low-Power Wake-up (ULPWU) mode for generating an interrupt-on-change on RA0.

These modes define which portions of the device are clocked and at what speed.

- The Run and Idle modes can use any of the three available clock sources (primary, secondary or internal oscillator blocks).

- The Sleep mode does not use a clock source.

The ULPWU mode on RA0 allows a slow falling voltage to generate an interrupt-on-change on RA0 without excess current consumption. See **Section 4.7** "**Ultra Low-Power Wake-up**".

The power-managed modes include several power-saving features offered on previous PIC<sup>®</sup> devices, such as clock switching, ULPWU and Sleep mode. In addition, the PIC18F46J11 family devices add a new power-managed Deep Sleep mode.

## 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires these decisions:

- Will the CPU be clocked?

- If so, which clock source will be used?

The IDLEN bit (OSCCON<7>) controls CPU clocking and the SCS<1:0> bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

## 4.1.1 CLOCK SOURCES

The SCS<1:0> bits allow the selection of one of three clock sources for power-managed modes. They are:

- Primary clock source Defined by the FOSC<2:0> Configuration bits

- Timer1 clock Provided by the secondary oscillator

- Postscaled internal clock Derived from the internal oscillator block

### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one clock source to another begins by loading the OSCCON register. The SCS<1:0> bits select the clock source.

Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch also may be subject to clock transition delays. These delays are discussed in **Section 4.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, the IDLEN bit or the DSEN bit prior to issuing a SLEEP instruction.

If the IDLEN and DSEN bits are already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

## TABLE 6-3: NON-ACCESS BANK SPECIAL FUNCTION REGISTER MAP

| Address | Name                    | Address | Name    | Address | Name | Address | Name    | Address | Name                  |

|---------|-------------------------|---------|---------|---------|------|---------|---------|---------|-----------------------|

| F5Fh    | PMCONH <sup>(1)</sup>   | F3Fh    | RTCCFG  | F1Fh    | —    | EFFh    | PPSCON  | EDFh    | _                     |

| F5Eh    | PMCONL <sup>(1)</sup>   | F3Eh    | RTCCAL  | F1Eh    | _    | EFEh    | RPINR24 | EDEh    | RPOR24 <sup>(1)</sup> |

| F5Dh    | PMMODEH <sup>(1)</sup>  | F3Dh    | REFOCON | F1Dh    | _    | EFDh    | RPINR23 | EDDh    | RPOR23 <sup>(1)</sup> |

| F5Ch    | PMMODEL <sup>(1)</sup>  | F3Ch    | PADCFG1 | F1Ch    | _    | EFCh    | RPINR22 | EDCh    | RPOR22 <sup>(1)</sup> |

| F5Bh    | PMDOUT2H <sup>(1)</sup> | F3Bh    | _       | F1Bh    | _    | EFBh    | RPINR21 | EDBh    | RPOR21 <sup>(1)</sup> |

| F5Ah    | PMDOUT2L <sup>(1)</sup> | F3Ah    | _       | F1Ah    | _    | EFAh    | _       | EDAh    | RPOR20 <sup>(1)</sup> |

| F59h    | PMDIN2H <sup>(1)</sup>  | F39h    | _       | F19h    | _    | EF9h    | _       | ED9h    | RPOR19 <sup>(1)</sup> |

| F58h    | PMDIN2L <sup>(1)</sup>  | F38h    | _       | F18h    | _    | EF8h    | _       | ED8h    | RPOR18                |

| F57h    | PMEH <sup>(1)</sup>     | F37h    | _       | F17h    | _    | EF7h    | RPINR17 | ED7h    | RPOR17                |

| F56h    | PMEL <sup>(1)</sup>     | F36h    |         | F16h    | —    | EF6h    | RPINR16 | ED6h    | RPOR16                |

| F55h    | PMSTATH <sup>(1)</sup>  | F35h    |         | F15h    | —    | EF5h    | _       | ED5h    | RPOR15                |

| F54h    | PMSTATL <sup>(1)</sup>  | F34h    |         | F14h    | —    | EF4h    | _       | ED4h    | RPOR14                |

| F53h    | CVRCON                  | F33h    |         | F13h    | —    | EF3h    | _       | ED3h    | RPOR13                |

| F52h    | TCLKCON                 | F32h    |         | F12h    | —    | EF2h    | _       | ED2h    | RPOR12                |

| F51h    | -                       | F31h    |         | F11h    | —    | EF1h    | _       | ED1h    | RPOR11                |

| F50h    | -                       | F30h    |         | F10h    | —    | EF0h    | _       | ED0h    | RPOR10                |

| F4Fh    | DSGPR1 <sup>(2)</sup>   | F2Fh    |         | F0Fh    | —    | EEFh    | _       | ECFh    | RPOR9                 |

| F4Eh    | DSGPR0 <sup>(2)</sup>   | F2Eh    | —       | F0Eh    | —    | EEEh    | RPINR8  | ECEh    | RPOR8                 |

| F4Dh    | DSCONH <sup>(2)</sup>   | F2Dh    | —       | F0Dh    | —    | EEDh    | RPINR7  | ECDh    | RPOR7                 |

| F4Ch    | DSCONL <sup>(2)</sup>   | F2Ch    | _       | F0Ch    | —    | EECh    | RPINR6  | ECCh    | RPOR6                 |

| F4Bh    | DSWAKEH <sup>(2)</sup>  | F2Bh    | _       | F0Bh    | —    | EEBh    | —       | ECBh    | RPOR5                 |

| F4Ah    | DSWAKEL <sup>(2)</sup>  | F2Ah    | _       | F0Ah    | —    | EEAh    | RPINR4  | ECAh    | RPOR4                 |

| F49h    | ANCON1                  | F29h    | _       | F09h    | —    | EE9h    | RPINR3  | EC9h    | RPOR3                 |

| F48h    | ANCON0                  | F28h    | _       | F08h    | —    | EE8h    | RPINR2  | EC8h    | RPOR2                 |

| F47h    | —                       | F27h    | _       | F07h    | —    | EE7h    | RPINR1  | EC7h    | RPOR1                 |

| F46h    | —                       | F26h    | _       | F06h    | —    | EE6h    | —       | EC6h    | RPOR0                 |

| F45h    | —                       | F25h    | _       | F05h    | —    | EE5h    | —       | EC5h    | —                     |

| F44h    | —                       | F24h    | _       | F04h    | —    | EE4h    | —       | EC4h    | —                     |

| F43h    | _                       | F23h    | _       | F03h    | _    | EE3h    | _       | EC3h    | _                     |

| F42h    | ODCON1                  | F22h    | —       | F02h    | _    | EE2h    | —       | EC2h    | —                     |

| F41h    | ODCON2                  | F21h    | _       | F01h    | _    | EE1h    | —       | EC1h    | _                     |

| F40h    | ODCON3                  | F20h    | _       | F00h    | _    | EE0h    | _       | EC0h    | —                     |

Note 1: This register is not available on 28-pin devices.

2: Deep Sleep registers are not available on LF devices.

## 7.5.3 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

## 7.5.4 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. If the write operation is interrupted by a MCLR Reset or a WDT time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

## 7.6 Flash Program Operation During Code Protection

See Section 26.6 "Program Verification and Code Protection" for details on code protection of Flash program memory.

| TABLE 7-2: | REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY |

|------------|------------------------------------------------|

|------------|------------------------------------------------|

| Name    | Bit 7     | Bit 6                                                              | Bit 5       | Bit 4          | Bit 3          | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values on<br>Page: |  |

|---------|-----------|--------------------------------------------------------------------|-------------|----------------|----------------|--------|--------|-------|-----------------------------|--|

| TBLPTRU | _         | — — bit 21 Program Memory Table Pointer Upper Byte (TBLPTR<20:16>) |             |                |                |        |        |       |                             |  |

| TBPLTRH | Program M | emory Table                                                        | e Pointer H | ligh Byte (TE  | BLPTR<15:8     | >)     |        |       | 69                          |  |

| TBLPTRL | Program M | emory Table                                                        | e Pointer L | ow Byte (TB    | LPTR<7:0>)     | )      |        |       | 69                          |  |

| TABLAT  | Program M | emory Table                                                        | e Latch     |                |                |        |        |       | 69                          |  |

| INTCON  | GIE/GIEH  | PEIE/GIEL                                                          | TMR0IE      | INT0IE         | RBIE           | TMR0IF | INTOIF | RBIF  | 69                          |  |

| EECON2  | Program M | emory Cont                                                         | rol Registe | er 2 (not a pl | nysical regist | ter)   |        |       | 71                          |  |

| EECON1  | —         | _                                                                  | WPROG       | FREE           | WRERR          | WREN   | WR     | —     | 71                          |  |

Legend: — = unimplemented, read as '0'. Shaded cells are not used during Flash program memory access.

| R/W-0         | R/W-0                                                                                                                                              | R-0                                  | R-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------|-------------------|------------------|-----------------|--------|--|--|--|--|

| SSP2IF        | BCL2IF                                                                                                                                             | RC2IF                                | TX2IF         | TMR4IF            | CTMUIF           | TMR3GIF         | RTCCIF |  |  |  |  |

| bit 7         |                                                                                                                                                    |                                      |               |                   |                  |                 | bit (  |  |  |  |  |

|               |                                                                                                                                                    |                                      |               |                   |                  |                 |        |  |  |  |  |

| Legend:       |                                                                                                                                                    |                                      |               |                   |                  |                 |        |  |  |  |  |

| R = Readabl   | le bit                                                                                                                                             | W = Writable                         | bit           |                   | nented bit, rea  | d as '0'        |        |  |  |  |  |

| -n = Value at | POR                                                                                                                                                | '1' = Bit is set                     |               | '0' = Bit is clea | ared             | x = Bit is unkn | iown   |  |  |  |  |

| h:+ 7         |                                                                                                                                                    | ton Cumphrone                        | o Coriol Dort |                   | L:4              |                 |        |  |  |  |  |

| bit 7         |                                                                                                                                                    | •                                    |               | 2 Interrupt Flag  |                  | 2)              |        |  |  |  |  |

|               |                                                                                                                                                    | o transmit/recep                     | •             | te (must be clea  | ired in soltware | e)              |        |  |  |  |  |

| bit 6         | •                                                                                                                                                  |                                      |               | ISSP2 module)     |                  |                 |        |  |  |  |  |

|               | 1 = A bus co                                                                                                                                       | llision occurred                     | (must be clea | ared in software  | )                |                 |        |  |  |  |  |

|               | 0 = No bus c                                                                                                                                       | ollision occurre                     | d             |                   |                  |                 |        |  |  |  |  |

| bit 5         | RC2IF: EUSA                                                                                                                                        | ART2 Receive I                       | nterrupt Flag | bit               |                  |                 |        |  |  |  |  |

|               | <ul> <li>1 = The EUSART2 receive buffer, RCREG2, is full (cleared when RCREG2 is read)</li> <li>0 = The EUSART2 receive buffer is empty</li> </ul> |                                      |               |                   |                  |                 |        |  |  |  |  |

|               |                                                                                                                                                    |                                      |               | ·                 |                  |                 |        |  |  |  |  |

| bit 4         |                                                                                                                                                    | RT2 Transmit I                       |               |                   |                  |                 |        |  |  |  |  |

|               |                                                                                                                                                    | SART2 transmit                       |               | 32, is empty (cl  | eared when 12    | KREG2 is writte | n)     |  |  |  |  |

| bit 3         |                                                                                                                                                    | R4 to PR4 Mate                       |               | aa hit            |                  |                 |        |  |  |  |  |

|               |                                                                                                                                                    |                                      |               | be cleared in sof | ftware)          |                 |        |  |  |  |  |

|               |                                                                                                                                                    | 4 to PR4 match                       | · ·           |                   | (Indi O)         |                 |        |  |  |  |  |

| bit 2         | CTMUIF: Cha                                                                                                                                        | arge Time Meas                       | surement Unit | Interrupt Flag b  | bit              |                 |        |  |  |  |  |

|               |                                                                                                                                                    |                                      | ``            | e cleared in soft | ware)            |                 |        |  |  |  |  |

|               | $0 = CTMU e^{i}$                                                                                                                                   | vent has not oc                      | curred        |                   |                  |                 |        |  |  |  |  |

| bit 1         |                                                                                                                                                    | mer3 Gate Eve                        | •             | •                 |                  |                 |        |  |  |  |  |

|               |                                                                                                                                                    | •                                    | • •           | be cleared in s   | oftware)         |                 |        |  |  |  |  |

|               |                                                                                                                                                    | r3 gate event co                     | •             |                   |                  |                 |        |  |  |  |  |

| bit 0         |                                                                                                                                                    | CC Interrupt Fla                     | -             |                   | ,                |                 |        |  |  |  |  |

|               |                                                                                                                                                    | terrupt occurred<br>C interrupt occu |               | ared in software  | e)               |                 |        |  |  |  |  |

|               | 0 = 100  KIGC                                                                                                                                      |                                      | iieu          |                   |                  |                 |        |  |  |  |  |

|               |                                                                                                                                                    |                                      |               |                   |                  |                 |        |  |  |  |  |

## REGISTER 9-6: PIR3: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 3 (ACCESS FA4h)

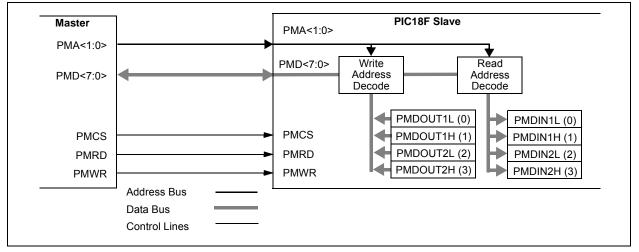

## 11.2.5 ADDRESSABLE PARALLEL SLAVE PORT MODE

In the Addressable Parallel Slave Port mode (PMMODEH<1:0> = 01), the module is configured with two extra inputs, PMA<1:0>, which are the address lines 1 and 0. This makes the 4-byte buffer space directly addressable as fixed pairs of read and write buffers. As with Legacy Buffered mode, data is output from PMDOUT1L, PMDOUT1H, PMDOUT2L and PMDOUT2H, and is read in on PMDIN1L, PMDIN1H, PMDIN2L and PMDIN2L and PMDIN2H. Table 11-1 provides the buffer addressing for the incoming address to the input and output registers.

## TABLE 11-1: SLAVE MODE BUFFER ADDRESSING

| PMA<1:0> | Output<br>Register<br>(Buffer) | Input Register<br>(Buffer) |

|----------|--------------------------------|----------------------------|

| 00       | PMDOUT1L (0)                   | PMDIN1L (0)                |

| 01       | PMDOUT1H (1)                   | PMDIN1H (1)                |

| 10       | PMDOUT2L (2)                   | PMDIN2L (2)                |

| 11       | PMDOUT2H((3)                   | PMDIN2H (3)                |

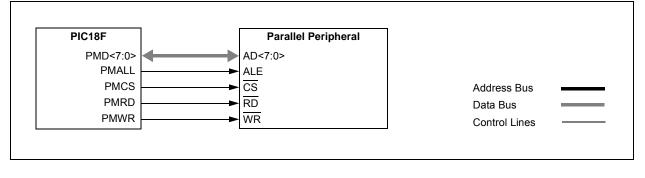

### FIGURE 11-6: PARALLEL MASTER/SLAVE CONNECTION ADDRESSED BUFFER EXAMPLE

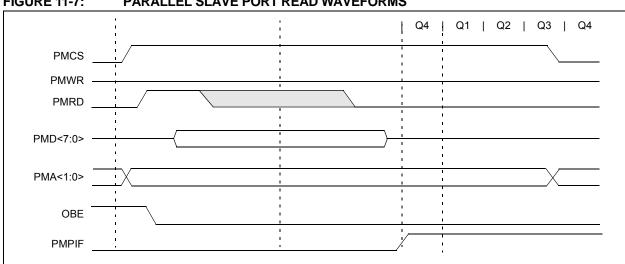

## 11.2.5.1 READ FROM SLAVE PORT

When chip select is active and a read strobe occurs (PMCS = 1 and PMRD = 1), the data from one of the four output bytes is presented onto PMD<7:0>. Which byte is read depends on the 2-bit address placed on ADDR<1:0>. Table 11-1 provides the corresponding

output registers and their associated address. When an output buffer is read, the corresponding OBxE bit is set. The OBxE flag bit is set when all the buffers are empty. If any buffer is already empty, OBxE = 1, the next read to that buffer will generate an OBUF event.

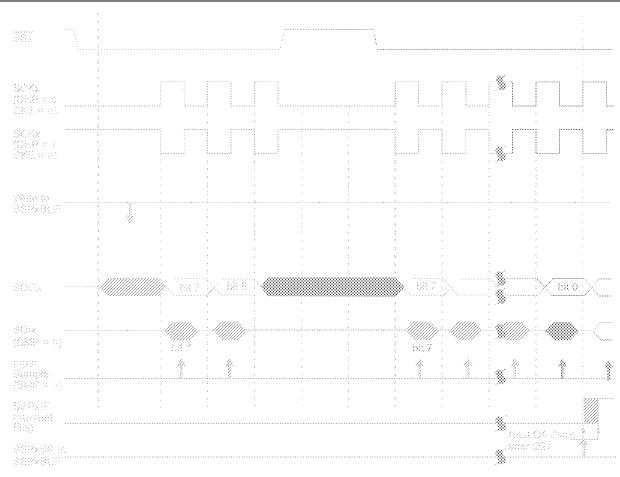

## FIGURE 11-7: PARALLEL SLAVE PORT READ WAVEFORMS

## **11.4** Application Examples

This section introduces some potential applications for the PMP module.

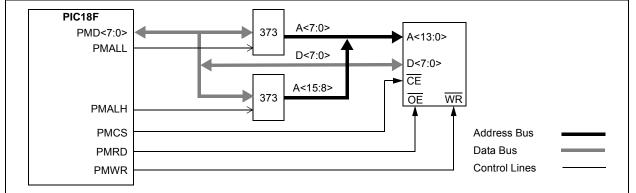

## 11.4.1 MULTIPLEXED MEMORY OR PERIPHERAL

Figure 11-27 demonstrates the hookup of a memory or another addressable peripheral in Full Multiplex mode. Consequently, this mode achieves the best pin saving from the microcontroller perspective. However, for this configuration, there needs to be some external latches to maintain the address.

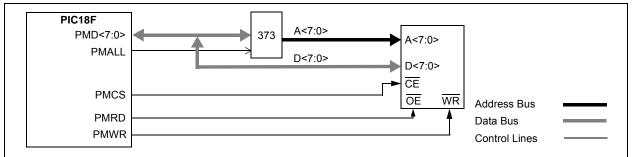

## 11.4.2 PARTIALLY MULTIPLEXED MEMORY OR PERIPHERAL

Partial multiplexing implies using more pins; however, for a few extra pins, some extra performance can be achieved. Figure 11-28 provides an example of a memory or peripheral that is partially multiplexed with an external latch. If the peripheral has internal latches, as displayed in Figure 11-29, then no extra circuitry is required except for the peripheral itself.

## FIGURE 11-28: EXAMPLE OF A PARTIALLY MULTIPLEXED ADDRESSING APPLICATION

### FIGURE 11-29: EXAMPLE OF AN 8-BIT MULTIPLEXED ADDRESS AND DATA APPLICATION

## REGISTER 17-16: ALRMWD: ALARM WEEKDAY VALUE REGISTER (ACCESS F8Fh, PTR 01b)<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-x | R/W-x | R/W-x |

|-------|-----|-----|-----|-----|-------|-------|-------|

| —     | —   | —   | —   | —   | WDAY2 | WDAY1 | WDAY0 |

| bit 7 |     |     |     |     |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 **WDAY<2:0>:** Binary Coded Decimal Value of Weekday Digit bits Contains a value from 0 to 6.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

## REGISTER 17-17: ALRMHR: ALARM HOURS VALUE REGISTER (ACCESS F8Eh, PTR 01b)<sup>(1)</sup>

| U-0   | U-0 | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  | R/W-x  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | HRTEN1 | HRTEN0 | HRONE3 | HRONE2 | HRONE1 | HRONE0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                                                                |                      |                    |  |  |

|-------------------|----------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | idable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared | x = Bit is unknown |  |  |

| bit 7-6 | Unimplemented: Read as '0'                                                                                  |

|---------|-------------------------------------------------------------------------------------------------------------|

| bit 5-4 | <b>HRTEN&lt;1:0&gt;:</b> Binary Coded Decimal Value of Hour's Tens Digit bits Contains a value from 0 to 2. |

| bit 3-0 | <b>HRONE3:HRONE0:</b> Binary Coded Decimal Value of Hour's Ones Digit bits Contains a value from 0 to 9.    |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

| Name    | Bit 7           | Bit 6                  | Bit 5    | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on Page: |  |

|---------|-----------------|------------------------|----------|----------|----------|--------|---------|---------|-----------------------------|--|

| INTCON  | <b>GIE/GIEH</b> | PEIE/GIEL              | TMR0IE   | INT0IE   | RBIE     | TMR0IF | INT0IF  | RBIF    | 69                          |  |

| RCON    | IPEN            | _                      | CM       | RI       | TO       | PD     | POR     | BOR     | 70                          |  |

| PIR1    | PMPIF           | ADIF                   | RC1IF    | TX1IF    | SSP1IF   | CCP1IF | TMR2IF  | TMR1IF  | 72                          |  |

| PIE1    | PMPIE           | ADIE                   | RC1IE    | TX1IE    | SSP1IE   | CCP1IE | TMR2IE  | TMR1IE  | 72                          |  |

| IPR1    | PMPIP           | ADIP                   | RC1IP    | TX1IP    | SSP1IP   | CCP1IP | TMR2IP  | TMR1IP  | 72                          |  |

| IPR2    | OSCFIP          | CM2IP                  | CM1IP    | _        | BCL1IP   | LVDIP  | TMR3IP  | CCP2IP  | 71                          |  |

| PIR2    | OSCFIF          | CM2IF                  | CM1IF    | _        | BCL1IF   | LVDIF  | TMR3IF  | CCP2IF  | 71                          |  |

| PIE2    | OSCFIE          | CM2IE                  | CM1IE    | _        | BCL1IE   | LVDIE  | TMR3IE  | CCP2IE  | 71                          |  |

| TCLKCON | _               | —                      | _        | T1RUN    | _        | _      | T3CCP2  | T3CCP1  | 74                          |  |

| PIR3    | SSP2IF          | BCL2IF                 | RC2IF    | TX2IF    | TMR4IF   | CTMUIF | TMR3GIF | RTCCIF  | 72                          |  |

| PIE3    | SSP2IE          | BCL2IE                 | RC2IE    | TX2IE    | TMR4IE   | CTMUIE | TMR3GIE | RTCCIE  | 72                          |  |

| IPR3    | SSP2IP          | BCL2IP                 | RC2IP    | TX2IP    | TMR4IP   | CTMUIP | TMR3GIP | RTCCIP  | 72                          |  |

| TMR2    | Timer2 Reg      | jister                 |          |          |          |        |         |         | 70                          |  |

| PR2     | Timer2 Peri     | iod Register           |          |          |          |        |         |         | 70                          |  |

| T2CON   | _               | T2OUTPS3               | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 70                          |  |

| TMR4    | Timer4 Reg      | jister                 |          |          |          |        |         |         | 73                          |  |

| PR4     | Timer4 Peri     | Timer4 Period Register |          |          |          |        |         |         |                             |  |

| T4CON   | _               | T4OUTPS3               | T4OUTPS2 | T4OUTPS1 | T4OUTPS0 | TMR4ON | T4CKPS1 | T4CKPS0 | 73                          |  |

| ODCON1  | _               | —                      | _        | —        | —        | _      | ECCP2OD | ECCP10D | 74                          |  |

## TABLE 18-3: REGISTERS ASSOCIATED WITH PWM, TIMER2 AND TIMER4

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PWM, Timer2 or Timer4.

## 18.5.4 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the ECCPxAS<2:0> bits of the ECCPAS register. A shutdown event may be generated by:

- A logic '0' on the pin that is assigned the FLT0 input function

- Comparator C1

- Comparator C2

- Setting the ECCPxASE bit in firmware

A shutdown condition is indicated by the ECCPxASE (Auto-Shutdown Event Status) bit of the ECCPxAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The ECCPxASE bit is set to '1'. The ECCPxASE will remain set until cleared in firmware or an auto-restart occurs (see **Section 18.5.5 "Auto-Restart Mode"**).

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [PxA/PxC] and [PxB/PxD]. The state of each pin pair is determined by the PSSxAC and PSSxBD bits of the ECCPxAS register. Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

### REGISTER 18-2: ECCPxAS: ECCPx AUTO-SHUTDOWN CONTROL REGISTER (ACCESS FBEh/FB8h)

| R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|----------|----------|----------|----------|---------|---------|---------|---------|

| ECCPxASE | ECCPxAS2 | ECCPxAS1 | ECCPxAS0 | PSSxAC1 | PSSxAC0 | PSSxBD1 | PSSxBD0 |

| bit 7    |          |          |          |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | ECCPxASE: ECCP Auto-Shutdown Event Status bit<br>1 = A shutdown event has occurred; ECCP outputs are in a shutdown state<br>0 = ECCP outputs are operating                                                                                                                                                                                                                                                                                           |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | ECCPxAS<2:0>: ECCP Auto-Shutdown Source Select bits<br>000 = Auto-shutdown is disabled<br>001 = Comparator C1OUT output is high<br>010 = Comparator C2OUT output is high<br>011 = Either Comparator C1OUT or C2OUT is high<br>100 = VIL on FLT0 pin<br>101 = VIL on FLT0 pin or Comparator C1OUT output is high<br>110 = VIL on FLT0 pin or Comparator C2OUT output is high<br>111 = VIL on FLT0 pin or Comparator C1OUT or Comparator C2OUT is high |

| bit 3-2 | PSSxAC<1:0>: Pins PxA and PxC Shutdown State Control bits<br>00 = Drive pins PxA and PxC to '0'<br>01 = Drive pins PxA and PxC to '1'<br>10 = Pins PxA and PxC tri-state                                                                                                                                                                                                                                                                             |

| bit 1-0 | PSSxBD<1:0>: Pins PxB and PxD Shutdown State Control bits<br>00 = Drive pins PxB and PxD to '0'<br>01 = Drive pins PxB and PxD to '1'<br>10 = Pins PxB and PxD tri-state                                                                                                                                                                                                                                                                             |

| 2:      | The auto-shutdown condition is a level-based signal, not an edge-based signal. As long as the level is present, the auto-shutdown will persist.<br>Writing to the ECCPxASE bit is disabled while an auto-shutdown condition persists.<br>Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart), the PWM signal will always restart at the beginning of the next PWM period.              |

## 19.3.7 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCKx. When the last bit is latched, the SSPxIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCKx pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device can be configured to wake-up from Sleep.

## 19.3.8 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SSx}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with the  $\overline{SSx}$  pin control enabled (SSPxCON1<3:0> = 04h). When the  $\overline{SSx}$  pin is low, transmission and reception are enabled and the SDOx pin is driven. When the  $\overline{SSx}$  pin goes high, the SDOx pin is no longer driven, even if in the middle of a

transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | Wher  | n the S   | PI is i | n Slave          | mode   | e with |

|---------|-------|-----------|---------|------------------|--------|--------|

|         | the   | SSx       | pin     | control          | en     | abled  |

|         | (SSP: | xCON1     | <3:0> = | •0100 <b>)</b> , | the    | SPI    |

|         | modu  | le will r | eset if | the SSx          | oin is | set to |

|         | Vdd.  |           |         |                  |        |        |

|         |       |           |         |                  |        |        |

2: If the SPI is used in Slave mode with CKE set, then the SSx pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SSx pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDOx pin can be connected to the SDIx pin. When the SPI needs to operate as a receiver, the SDOx pin can be configured as an input. This disables transmissions from the SDOx. The SDIx can always be left as an input (SDIx function) since it cannot create a bus conflict.

FIGURE 19-4: SLAVE SYNCHRONIZATION WAVEFORM

|             |                       | <b>SYNC</b> = 0, <b>BRGH</b> = 0, <b>BRG16</b> = 0 |                             |                       |                   |                             |                       |                   |                             |                       |                  |                             |  |

|-------------|-----------------------|----------------------------------------------------|-----------------------------|-----------------------|-------------------|-----------------------------|-----------------------|-------------------|-----------------------------|-----------------------|------------------|-----------------------------|--|

| BAUD        | Fosc                  | Fosc = 40.000 MHz                                  |                             |                       | Fosc = 20.000 MHz |                             |                       | Fosc = 10.000 MHz |                             |                       | Fosc = 8.000 MHz |                             |  |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error                                         | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 0.3         | _                     |                                                    |                             |                       |                   |                             |                       |                   | _                           | _                     | _                | _                           |  |

| 1.2         | —                     | —                                                  | —                           | 1.221                 | 1.73              | 255                         | 1.202                 | 0.16              | 129                         | 1.201                 | -0.16            | 103                         |  |

| 2.4         | 2.441                 | 1.73                                               | 255                         | 2.404                 | 0.16              | 129                         | 2.404                 | 0.16              | 64                          | 2.403                 | -0.16            | 51                          |  |

| 9.6         | 9.615                 | 0.16                                               | 64                          | 9.766                 | 1.73              | 31                          | 9.766                 | 1.73              | 15                          | 9.615                 | -0.16            | 12                          |  |

| 19.2        | 19.531                | 1.73                                               | 31                          | 19.531                | 1.73              | 15                          | 19.531                | 1.73              | 7                           | _                     | _                | _                           |  |

| 57.6        | 56.818                | -1.36                                              | 10                          | 62.500                | 8.51              | 4                           | 52.083                | -9.58             | 2                           | —                     | _                | _                           |  |

| 115.2       | 125.000               | 8.51                                               | 4                           | 104.167               | -9.58             | 2                           | 78.125                | -32.18            | 1                           | —                     | _                | _                           |  |

### TABLE 20-3: BAUD RATES FOR ASYNCHRONOUS MODES

|              |                       | <b>SYNC =</b> 0, <b>BRGH =</b> 0, <b>BRG16 =</b> 0 |                             |                       |            |                             |                       |            |                             |

|--------------|-----------------------|----------------------------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fos                   | Fosc = 4.000 MHz                                   |                             |                       | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                                         | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                 | 0.16                                               | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16      | 51                          |

| 1.2          | 1.202                 | 0.16                                               | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16      | 12                          |

| 2.4          | 2.404                 | 0.16                                               | 25                          | 2.403                 | -0.16      | 12                          | _                     | _          | _                           |

| 9.6          | 8.929                 | -6.99                                              | 6                           | _                     | _          | _                           | _                     | _          | _                           |

| 19.2         | 20.833                | 8.51                                               | 2                           | —                     | _          | _                           | —                     | _          | _                           |

| 57.6         | 62.500                | 8.51                                               | 0                           | —                     | _          | _                           | —                     | _          | _                           |

| 115.2        | 62.500                | -45.75                                             | 0                           | _                     | _          | —                           | _                     | —          | —                           |

|              |                       | SYNC = 0, BRGH = 1, BRG16 = 0       |                             |                       |            |                             |                       |            |                             |                       |            |                             |

|--------------|-----------------------|-------------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc                  | Fosc = 40.000 MHz Fosc = 20.000 MHz |                             |                       |            | ) MHz                       | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                          | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | —                     | _                                   | _                           | —                     | _          | _                           | _                     | _          | _                           | _                     | _          | _                           |

| 1.2          | —                     | —                                   | —                           | —                     | —          | —                           | —                     | —          | —                           | —                     | —          | —                           |

| 2.4          | —                     | _                                   | _                           | —                     | _          | _                           | 2.441                 | 1.73       | 255                         | 2.403                 | -0.16      | 207                         |

| 9.6          | 9.766                 | 1.73                                | 255                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9615.                 | -0.16      | 51                          |

| 19.2         | 19.231                | 0.16                                | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |

| 57.6         | 58.140                | 0.94                                | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |

| 115.2        | 113.636               | -1.36                               | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           | —                     | _          | _                           |

|              |                       | <b>SYNC =</b> 0, <b>BRGH =</b> 1, <b>BRG16 =</b> 0 |                             |                       |            |                             |                       |            |                             |  |

|--------------|-----------------------|----------------------------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|

| BAUD<br>RATE | Foso                  | Fosc = 4.000 MHz                                   |                             |                       | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                                         | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 0.3          |                       |                                                    | _                           |                       |            | _                           | 0.300                 | -0.16      | 207                         |  |

| 1.2          | 1.202                 | 0.16                                               | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |  |

| 2.4          | 2.404                 | 0.16                                               | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |  |

| 9.6          | 9.615                 | 0.16                                               | 25                          | 9.615                 | -0.16      | 12                          | _                     | _          | _                           |  |

| 19.2         | 19.231                | 0.16                                               | 12                          | _                     | _          | _                           | _                     | _          | _                           |  |

| 57.6         | 62.500                | 8.51                                               | 3                           | _                     | _          | _                           | _                     | _          | _                           |  |

| 115.2        | 125.000               | 8.51                                               | 1                           | _                     | _          | —                           | _                     | _          | _                           |  |

© 2011 Microchip Technology Inc.

## 20.4 EUSART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTAx<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the CKx pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

### 20.4.1 EUSART SYNCHRONOUS SLAVE TRANSMISSION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep mode.

If two words are written to the TXREGx and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREGx register.

- c) Flag bit, TXxIF, will not be set.

- d) When the first word has been shifted out of TSR, the TXREGx register will transfer the second word to the TSR and flag bit, TXxIF, will now be set.

- e) If enable bit, TXxIE, is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. Clear bits, CREN and SREN.

- 3. If interrupts are desired, set enable bit, TXxIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting enable bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| R/W-0         | R/W-0                                                                                                                                                                        | R/W-0                                                | R/W-0          | R/W-0             | R/W-0            | R/W-x           | R/W-x    |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------|-------------------|------------------|-----------------|----------|

| EDG2POL       | EDG2SEL1                                                                                                                                                                     | EDG2SEL0                                             | EDG1POL        | EDG1SEL1          | EDG1SEL0         | EDG2STAT        | EDG1STAT |

| bit 7         | •                                                                                                                                                                            | •                                                    |                | •                 | •                | •               | bit C    |

|               |                                                                                                                                                                              |                                                      |                |                   |                  |                 |          |

| Legend:       |                                                                                                                                                                              |                                                      |                |                   |                  |                 |          |

| R = Readable  | e bit                                                                                                                                                                        | W = Writable                                         | bit            | U = Unimplen      | nented bit, read | l as '0'        |          |

| -n = Value at | POR                                                                                                                                                                          | '1' = Bit is set                                     |                | '0' = Bit is clea | ared             | x = Bit is unkr | iown     |

| bit 7         | EDG2POL: E                                                                                                                                                                   | dge 2 Polarity                                       | Select bit     |                   |                  |                 |          |

|               |                                                                                                                                                                              | rogrammed for<br>rogrammed for                       |                |                   |                  |                 |          |

| bit 6-5       | 11 = CTED1<br>10 = CTED2<br>01 = ECCP1                                                                                                                                       |                                                      | Frigger        | S                 |                  |                 |          |

| bit 4         | 1 = Edge 1 p                                                                                                                                                                 | dge 1 Polarity<br>rogrammed for<br>rogrammed for     | a positive edg |                   |                  |                 |          |

| bit 3-2       | 11 = CTED1<br>10 = CTED2<br>01 = ECCP1                                                                                                                                       |                                                      | rigger         | S                 |                  |                 |          |

| bit 1         | 1 = Edge 2 e                                                                                                                                                                 | Edge 2 Status b<br>vent has occur<br>vent has not oc | red            |                   |                  |                 |          |

| bit 0         | <ul> <li>0 = Edge 2 event has not occurred</li> <li>EDG1STAT: Edge 1 Status bit</li> <li>1 = Edge 1 event has occurred</li> <li>0 = Edge 1 event has not occurred</li> </ul> |                                                      |                |                   |                  |                 |          |

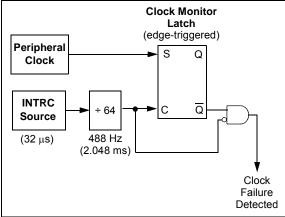

### FIGURE 26-4: FSCM BLOCK DIAGRAM

Clock failure is tested for on the falling edge of the sample clock. If a sample clock falling edge occurs while the clock monitor is still set, and a clock failure has been detected (Figure 26-5), the following results:

- The FSCM generates an oscillator fail interrupt by setting bit, OSCFIF (PIR2<7>);

- The device clock source is switched to the internal oscillator block (OSCCON is not updated to show the current clock source – this is the Fail-safe condition); and

- The WDT is reset.

During switchover, the postscaler frequency from the internal oscillator block may not be sufficiently stable for timing-sensitive applications. In these cases, it may be desirable to select another clock configuration and enter an alternate power-managed mode. This can be done to attempt a partial recovery or execute a controlled shutdown. See Section 4.1.4 "Multiple Sleep Commands" and Section 26.4.1 "Special Considerations for Using Two-Speed Start-up" for more details.

The FSCM will detect failures of the primary or secondary clock sources only. If the internal oscillator block fails, no failure would be detected, nor would any action be possible.

## 26.5.1 FSCM AND THE WATCHDOG TIMER

Both the FSCM and the WDT are clocked by the INTRC oscillator. Since the WDT operates with a separate divider and counter, disabling the WDT has no effect on the operation of the INTRC oscillator when the FSCM is enabled.

As already noted, the clock source is switched to the INTRC clock when a clock failure is detected; this may mean a substantial change in the speed of code execution. If the WDT is enabled with a small prescale value, a decrease in clock speed allows a WDT time-out to occur and a subsequent device Reset. For this reason, Fail-Safe Clock Monitor events also reset the WDT and postscaler, allowing it to start timing from when execution speed was changed and decreasing the likelihood of an erroneous time-out.

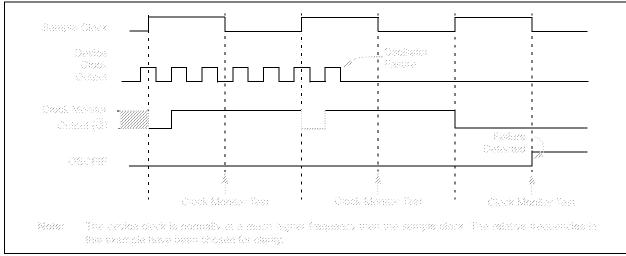

## FIGURE 26-5: FSCM TIMING DIAGRAM

## 26.7 In-Circuit Serial Programming (ICSP)

PIC18F46J11 family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

## 26.8 In-Circuit Debugger

When the  $\overline{\text{DEBUG}}$  Configuration bit is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some resources are not available for general use.

Table 26-4 lists the resources required by the background debugger.

| I/O pins: | RB6, RB7                |

|-----------|-------------------------|

| Stack:    | TOSx registers reserved |

| BCF               | Bit Clear f                                                            |                                                                                                                                                                                                                                                                                      |                                    | BN               |  |  |  |

|-------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------|--|--|--|

| Syntax:           | BCF f, b                                                               | {,a}                                                                                                                                                                                                                                                                                 |                                    | Syntax:          |  |  |  |

| Operands:         | $0 \leq f \leq 255$                                                    | $0 \leq f \leq 255$                                                                                                                                                                                                                                                                  |                                    |                  |  |  |  |

|                   | 0 ≤ b ≤ 7<br>a ∈ [0,1]                                                 |                                                                                                                                                                                                                                                                                      |                                    | Operation        |  |  |  |

| Operation:        | $0 \rightarrow f \le b >$                                              |                                                                                                                                                                                                                                                                                      |                                    | Status Affe      |  |  |  |

| Status Affected:  | None                                                                   |                                                                                                                                                                                                                                                                                      |                                    | Encoding:        |  |  |  |

| Encoding:         | 1001                                                                   | bbba ff:                                                                                                                                                                                                                                                                             | ff ffff                            | Descriptio       |  |  |  |

| Description:      | Bit 'b' in reg                                                         | jister 'f' is clea                                                                                                                                                                                                                                                                   | red.                               |                  |  |  |  |

|                   |                                                                        | he BSR is use                                                                                                                                                                                                                                                                        | nk is selected.<br>d to select the |                  |  |  |  |

|                   | set is enabl<br>in Indexed I<br>mode when<br>Section 27<br>Bit-Oriente | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 27.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                    |                  |  |  |  |

| Words:            | 1                                                                      |                                                                                                                                                                                                                                                                                      |                                    | If Jump:         |  |  |  |

| Cycles:           | 1                                                                      |                                                                                                                                                                                                                                                                                      |                                    | De               |  |  |  |

| Q Cycle Activity: |                                                                        |                                                                                                                                                                                                                                                                                      |                                    |                  |  |  |  |

| Q1                | Q2                                                                     | Q3                                                                                                                                                                                                                                                                                   | Q4                                 |                  |  |  |  |

| Decode            | Read<br>register 'f'                                                   | Process<br>Data                                                                                                                                                                                                                                                                      | Write<br>register 'f'              | ope<br>If No Jum |  |  |  |

|                   | register i                                                             | Data                                                                                                                                                                                                                                                                                 | register i                         |                  |  |  |  |

| Example:          |                                                                        | LAG_REG,                                                                                                                                                                                                                                                                             | 7, 0                               | De               |  |  |  |

| Before Instruc    | tion<br>EG = C7h                                                       |                                                                                                                                                                                                                                                                                      |                                    |                  |  |  |  |

| After Instruction |                                                                        |                                                                                                                                                                                                                                                                                      |                                    | Example:         |  |  |  |

| FLAG_R            | EG = 47h                                                               |                                                                                                                                                                                                                                                                                      |                                    | Befor            |  |  |  |

|                   |                                                                        |                                                                                                                                                                                                                                                                                      |                                    | After            |  |  |  |

| BN                                                                                                        |                       | Branch if N                                                                                                                                                                                                                | legative                                                  |                 |  |  |  |

|-----------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------|--|--|--|

| Synta                                                                                                     | ax:                   | BN n                                                                                                                                                                                                                       | BN n                                                      |                 |  |  |  |

| Oper                                                                                                      | ands:                 | -128 ≤ n ≤ 1                                                                                                                                                                                                               | $-128 \le n \le 127$                                      |                 |  |  |  |

| Oper                                                                                                      | ation:                | if Negative bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                  |                                                           |                 |  |  |  |

| Statu                                                                                                     | s Affected:           | None                                                                                                                                                                                                                       |                                                           |                 |  |  |  |

| Enco                                                                                                      | ding:                 | 1110                                                                                                                                                                                                                       | 0110 nnn                                                  | in nnnn         |  |  |  |

| Description:                                                                                              |                       |                                                                                                                                                                                                                            | If the Negative bit is '1', then the program will branch. |                 |  |  |  |

|                                                                                                           |                       | The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |                                                           |                 |  |  |  |

| Words: 1                                                                                                  |                       |                                                                                                                                                                                                                            |                                                           |                 |  |  |  |

| Cycle                                                                                                     | es:                   | 1(2)                                                                                                                                                                                                                       |                                                           |                 |  |  |  |

| Q C <u>y</u><br>If Ju                                                                                     | ycle Activity:<br>mp: |                                                                                                                                                                                                                            |                                                           |                 |  |  |  |

|                                                                                                           | Q1                    | Q2                                                                                                                                                                                                                         | Q3                                                        | Q4              |  |  |  |

|                                                                                                           | Decode                | Read literal<br>'n'                                                                                                                                                                                                        | Process<br>Data                                           | Write to<br>PC  |  |  |  |