Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 34                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | <u> </u>                                                                    |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 13x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf45j11-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                                                                                                                                                                                                         | Pin N                                                  | umber | Pin Buffer                |                                          |                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------|---------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                                                                                                                                                                                                | Africa Ad-<br>Ad-<br>Ad-<br>Ad-<br>Type<br>AFN<br>TQFP |       | Buffer<br>Type            | Description                              |                                                                                                                                                   |

|                                                                                                                                                                                                                                                         |                                                        |       |                           |                                          | PORTB is a bidirectional I/O port. PORTB can be<br>software programmed for internal weak pull-ups on<br>all inputs.                               |

| RB0/AN12/INT0/RP3<br>RB0<br>AN12<br>INT0<br>RP3                                                                                                                                                                                                         | 9                                                      | 8     | I/O<br>I<br>I<br>I/O      | DIG<br>Analog<br>ST<br>DIG               | Digital I/O.<br>Analog input 12.<br>External interrupt 0.<br>Remappable peripheral pin 3.                                                         |

| RB1/AN10/PMBE/RTCC/RP4<br>RB1<br>AN10<br>PMBE<br>RTCC<br>RP4                                                                                                                                                                                            | 10                                                     | 9     | I/O<br>I<br>O<br>I/O      | DIG<br>Analog<br>DIG<br>DIG<br>DIG       | Digital I/O.<br>Analog input 10.<br>Parallel Master Port byte enable.<br>Real Time Clock Calendar output.<br>Remappable peripheral pin 4.         |

| RB2/AN8/CTED1/PMA3/REFO/<br>RP5<br>RB2<br>AN8<br>CTED1<br>PMA3<br>REFO<br>RP5                                                                                                                                                                           | 11                                                     | 10    | I/O<br>I<br>I<br>O<br>I/O | DIG<br>Analog<br>ST<br>DIG<br>DIG<br>DIG | Digital I/O.<br>Analog input 8.<br>CTMU edge 1 input.<br>Parallel Master Port address.<br>Reference output clock.<br>Remappable peripheral pin 5. |

| RB3/AN9/CTED2/PMA2/RP6<br>RB3<br>AN9<br>CTED2<br>PMA2<br>RP6                                                                                                                                                                                            | 12                                                     | 11    | I/O<br>I<br>I<br>O<br>I/O | DIG<br>Analog<br>ST<br>DIG<br>DIG        | Digital I/O.<br>Analog input 9.<br>CTMU edge 2 input.<br>Parallel Master Port address.<br>Remappable peripheral pin 6.                            |

| Legend:TTL = TTL compatible inputCMOS= CMOS compatible input or outputST = Schmitt Trigger input with CMOS levelsAnalog= Analog inputI = InputO= OutputP = PowerOD= Open-Drain (no P diode to VDD)DIG = Digital outputO= Open-Drain (no P diode to VDD) |                                                        |       |                           | Analog = Analog input<br>D = Output      |                                                                                                                                                   |

## TABLE 1-4: PIC18F4XJ11 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

## 6.0 MEMORY ORGANIZATION

There are two types of memory in PIC18 Flash microcontrollers:

- Program Memory

- Data RAM

As Harvard architecture devices, the data and program memories use separate busses; this allows for concurrent access of the two memory spaces.

Section 7.0 "Flash Program Memory" provides additional information on the operation of the Flash program memory.

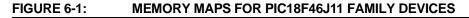

## 6.1 Program Memory Organization

PIC18 microcontrollers implement a 21-bit program counter, which is capable of addressing a 2-Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address returns all '0's (a NOP instruction).

The PIC18F46J11 family offers a range of on-chip Flash program memory sizes, from 16 Kbytes (up to 8,192 single-word instructions) to 64 Kbytes (32,768 single-word instructions).

Figure 6-1 provides the program memory maps for individual family devices.

### 6.1.4.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration register 1L. When STVREN is set, a full or underflow condition sets the appropriate STKFUL or STKUNF bit and then causes a device Reset. When STVREN is cleared, a full or underflow condition sets the appropriate STKFUL or STKUNF bit, but does not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a POR.

#### 6.1.5 FAST REGISTER STACK (FRS)

A Fast Register Stack (FRS) is provided for the STATUS, WREG and BSR registers to provide a "fast return" option for interrupts. This stack is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources push values into the Stack registers. The values in the registers are then loaded back into the working registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low-priority and high-priority interrupts are enabled, the Stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the Stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the FRS for returns from interrupt. If no interrupts are used, the FRS can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the FRS.

Example 6-1 provides a source code example that uses the FRS during a subroutine call and return.

#### EXAMPLE 6-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST     | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|---------------------|---------------------------------------------------------|

| SUB1<br>RETURN FAST | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

### 6.1.6 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures or look-up tables in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

### 6.1.6.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the PC. An example is shown in Example 6-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next executed instruction will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the PC should advance and should be multiples of 2 (LSb = 0).

In this method, only one byte may be stored in each instruction location; room on the return address stack is required.

#### EXAMPLE 6-2: COMPUTED GOTO USING AN OFFSET VALUE

|       | MOVF  | OFFSET, W |

|-------|-------|-----------|

|       | CALL  | TABLE     |

| ORG   | nn00h |           |

| TABLE | ADDWF | PCL       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       |       |           |

|       |       |           |

|       |       |           |

|       |       |           |

## 6.1.6.2 Table Reads

A better method of storing data in program memory allows two bytes to be stored in each instruction location.

Look-up table data may be stored two bytes per program word while programming. The Table Pointer (TBLPTR) specifies the byte address and the Table Latch (TABLAT) contains the data that is read from the program memory. Data is transferred from program memory one byte at a time.

Table read operation is discussed further inSection 7.1 "Table Reads and Table Writes".

## 7.5.2 FLASH PROGRAM MEMORY WRITE SEQUENCE (WORD PRORAMMING).

The PIC18F46J11 family of devices has a feature that allows programming a single word (two bytes). This feature is enabled when the WPROG bit is set. If the memory location is already erased, the following sequence is required to enable this feature:

- 1. Load the Table Pointer register with the address of the data to be written. (It must be an even address.)

- 2. Write the 2 bytes into the holding registers by performing table writes. (Do not post-increment on the second table write.)

- Set the WREN bit (EECON1<2>) to enable writes and the WPROG bit (EECON1<5>) to select Word Write mode.

- 4. Disable interrupts.

- 5. Write 55h to EECON2.

- 6. Write 0AAh to EECON2.

- 7. Set the WR bit; this will begin the write cycle.

- The CPU will stall for the duration of the write for TIW (see parameter D133A).

- 9. Re-enable interrupts.

| EAAIVIFLE / 4. |         |                 |                                                         |

|----------------|---------|-----------------|---------------------------------------------------------|

|                | MOVLW   | CODE_ADDR_UPPER | ; Load TBLPTR with the base address                     |

|                | MOVWF   | TBLPTRU         |                                                         |

|                | MOVLW   | CODE_ADDR_HIGH  |                                                         |

|                | MOVWF   | TBLPTRH         |                                                         |

|                | MOVLW   | CODE_ADDR_LOW   | ; The table pointer must be loaded with an even address |

|                | MOVWF   | TBLPTRL         |                                                         |

|                | MOVLW   | DATA0           | ; LSB of word to be written                             |

|                | MOVWF   | TABLAT          |                                                         |

|                | TBLWT*- |                 |                                                         |

|                | MOVLW   | DATA1           | ; MSB of word to be written                             |

|                | MOVWF   | TABLAT          |                                                         |

|                | TBLWT*  |                 | ; The last table write must not increment the table     |

|                |         |                 | pointer! The table pointer needs to point to the        |

|                |         |                 | MSB before starting the write operation.                |

| PROGRAM_MEMORY |         |                 |                                                         |

|                | BSF     | EECON1, WPROG   | ; enable single word write                              |

|                | BSF     | EECON1, WREN    | ; enable write to memory                                |

|                | BCF     | INTCON, GIE     | ; disable interrupts                                    |

|                | MOVLW   | 0x55            |                                                         |

| Required       | MOVWF   | EECON2          | ; write 55h                                             |

| Sequence       | MOVLW   | 0xAA            |                                                         |

|                | MOVWF   | EECON2          | ; write AAh                                             |

|                | BSF     | EECON1, WR      | ; start program (CPU stall)                             |

|                | BSF     | INTCON, GIE     | ; re-enable interrupts                                  |

|                | BCF     | EECON1, WPROG   | ; disable single word write                             |

|                | BCF     | EECON1, WREN    | ; disable write to memory                               |

|                |         |                 |                                                         |

#### EXAMPLE 7-4: SINGLE-WORD WRITE TO FLASH PROGRAM MEMORY

## 9.1 INTCON Registers

The INTCON registers are readable and writable registers, which contain various enable, priority and flag bits.

Note: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

### **REGISTER 9-1:** INTCON: INTERRUPT CONTROL REGISTER (ACCESS FF2h)

| R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x               |

|----------|-----------|--------|--------|-------|--------|--------|---------------------|

| GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF <sup>(1)</sup> |

| bit 7    |           |        |        |       |        |        | bit 0               |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7  | GIE/GIEH: Global Interrupt Enable bit                                                                       |

|--------|-------------------------------------------------------------------------------------------------------------|

|        | When IPEN = 0:                                                                                              |

|        | 1 = Enables all unmasked interrupts                                                                         |

|        | 0 = Disables all interrupts                                                                                 |

|        | When IPEN = 1:                                                                                              |

|        | 1 = Enables all high-priority interrupts                                                                    |

|        | 0 = Disables all interrupts                                                                                 |

| bit 6  | PEIE/GIEL: Peripheral Interrupt Enable bit                                                                  |

|        | When IPEN = 0:                                                                                              |

|        | 1 = Enables all unmasked peripheral interrupts                                                              |

|        | 0 = Disables all peripheral interrupts                                                                      |

|        | <u>When IPEN = 1 and GIEH = 1:</u><br>1 = Enables all low-priority peripheral interrupts                    |

|        | 0 = Disables all low-priority peripheral interrupts                                                         |

| bit 5  | TMR0IE: TMR0 Overflow Interrupt Enable bit                                                                  |

|        | 1 = Enables the TMR0 overflow interrupt                                                                     |

|        | 0 = Disables the TMR0 overflow interrupt                                                                    |

| bit 4  | INTOIE: INTO External Interrupt Enable bit                                                                  |

|        | 1 = Enables the INT0 external interrupt                                                                     |

|        | 0 = Disables the INTO external interrupt                                                                    |

| bit 3  | RBIE: RB Port Change Interrupt Enable bit                                                                   |

|        | 1 = Enables the RB port change interrupt                                                                    |

|        | 0 = Disables the RB port change interrupt                                                                   |

| bit 2  | TMR0IF: TMR0 Overflow Interrupt Flag bit                                                                    |

|        | 1 = TMR0 register has overflowed (must be cleared in software)                                              |

|        | 0 = TMR0 register did not overflow                                                                          |

| bit 1  | INTOIF: INTO External Interrupt Flag bit                                                                    |

|        | 1 = The INTO external interrupt occurred (must be cleared in software)                                      |

|        | 0 = The INT0 external interrupt did not occur                                                               |

| bit 0  | RBIF: RB Port Change Interrupt Flag bit <sup>(1)</sup>                                                      |

|        | 1 = At least one of the RB<7:4> pins changed state (must be cleared in software)                            |

|        | 0 = None of the RB<7:4> pins have changed state                                                             |

| Note 1 | A mismatch condition will continue to get this bit. Reading DODTR and waiting 1 Toy will and the mismatches |

**Note 1:** A mismatch condition will continue to set this bit. Reading PORTB and waiting 1 TCY will end the mismatch condition and allow the bit to be cleared.

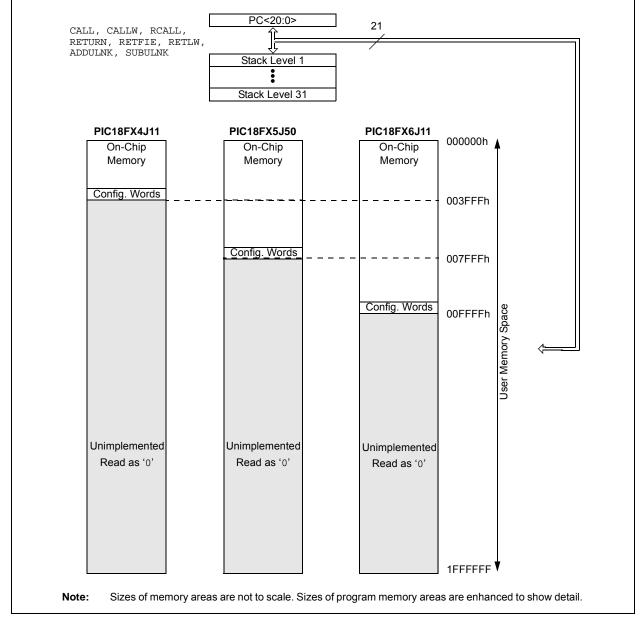

## 10.0 I/O PORTS

Depending on the device selected and features enabled, there are up to five ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (Data Direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (Data Latch)

The Data Latch (LAT register) is useful for read-modifywrite operations on the value that the I/O pins are driving.

Figure 10-1 displays a simplified model of a generic I/O port, without the interfaces to other peripherals.

FIGURE 10-1: GENERIC I/O PORT OPERATION

## 10.1 I/O Port Pin Capabilities

When developing an application, the capabilities of the port pins must be considered. Outputs on some pins have higher output drive strength than others. Similarly, some pins can tolerate higher than VDD input levels.

## 10.1.1 PIN OUTPUT DRIVE

The output pin drive strengths vary for groups of pins intended to meet the needs for a variety of applications. PORTB and PORTC are designed to drive higher loads, such as LEDs. All other ports are designed for small loads, typically indication only. Table 10-1 summarizes the output capabilities. Refer to **Section 29.0 "Electrical Characteristics"** for more details.

TABLE 10-1: OUTPUT DRIVE LEVELS

| Port                  | Drive   | Description                              |

|-----------------------|---------|------------------------------------------|

| PORTA<br>(except RA6) |         |                                          |

| PORTD                 | Minimum | Intended for indication.                 |

| PORTE                 |         |                                          |

| PORTB                 |         |                                          |

| PORTC                 | High    | Suitable for direct LED<br>drive levels. |

| PORTA<6>              |         |                                          |

#### 10.1.2 INPUT PINS AND VOLTAGE CONSIDERATIONS

The voltage tolerance of pins used as device inputs is dependent on the pin's input function. Pins that are used as digital only inputs are able to handle DC voltages up to 5.5V; a level typical for digital logic circuits. In contrast, pins that also have analog input functions of any kind can only tolerate voltages up to VDD. Voltage excursions beyond VDD on these pins should be avoided. Table 10-2 summarizes the input capabilities. Refer to **Section 29.0 "Electrical Characteristics"** for more details.

#### TABLE 10-2: INPUT VOLTAGE LEVELS

| Port or Pin | Tolerated<br>Input | Description                      |

|-------------|--------------------|----------------------------------|

| PORTA<7:0>  |                    |                                  |

| PORTB<3:0>  | Voo                | Only VDD input levels tolerated. |

| PORTC<2:0>  | VDD                |                                  |

| PORTE<2:0>  |                    |                                  |

| PORTB<7:4>  |                    | Tolerates input levels           |

| PORTC<7:3>  | 5.5V               | above VDD, useful for            |

| PORTD<7:0>  |                    | most standard logic.             |

| IADLE 10-3. |                     |                 |     |             |                                                                                                                |  |

|-------------|---------------------|-----------------|-----|-------------|----------------------------------------------------------------------------------------------------------------|--|

| Pin         | Function            | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                                    |  |

| RB4/PMA1/   | RB4                 | 0               | 0   | DIG         | LATB<4> data output; not affected by analog input.                                                             |  |

| KBI0/RP7    |                     | 1               | I   | TTL         | PORTB<4> data input; weak pull-up when RBPU bit is cleared. Disabled when analog input enabled. <sup>(1)</sup> |  |

|             | PMA1 <sup>(3)</sup> | 0               | 0   | DIG         | Parallel Master Port address.                                                                                  |  |

|             |                     | 1               | Ι   | ST/TTL      | Parallel Slave Port address input.                                                                             |  |

|             | KBI0                | 1               | Ι   | TTL         | Interrupt-on-change pin.                                                                                       |  |

|             | RP7                 | 1               | Ι   | ST          | Remappable peripheral pin 7 input.                                                                             |  |

|             |                     | 0               | 0   | DIG         | Remappable peripheral pin 7 output.                                                                            |  |

| RB5/PMA0/   | RB5                 | 0               | 0   | DIG         | LATB<5> data output.                                                                                           |  |

| KBI1/RP8    |                     | 1               | Ι   | TTL         | PORTB<5> data input; weak pull-up when RBPU bit is cleared.                                                    |  |

|             | PMA0 <sup>(3)</sup> | 0               | 0   | DIG         | Parallel Master Port address.                                                                                  |  |

|             |                     | 1               | Ι   | ST/TTL      | Parallel Slave Port address input.                                                                             |  |

|             | KBI1                | 1               | Ι   | TTL         | Interrupt-on-change pin.                                                                                       |  |

|             | RP8                 | 1               | Ι   | ST          | Remappable peripheral pin 8 input.                                                                             |  |

|             |                     | 0               | 0   | DIG         | Remappable peripheral pin 8 output.                                                                            |  |

| RB6/KBI2/   | RB6                 | 0               | 0   | DIG         | LATB<6> data output.                                                                                           |  |

| PGC/RP9     |                     | 1               | Ι   | TTL         | PORTB<6> data input; weak pull-up when RBPU bit is cleared.                                                    |  |

|             | KBI2                | 1               | Ι   | TTL         | Interrupt-on-change pin.                                                                                       |  |

|             | PGC                 | x               | Ι   | ST          | Serial execution (ICSP™) clock input for ICSP and ICD operation. <sup>(2)</sup>                                |  |

|             | RP9                 | 1               | Ι   | ST          | Remappable peripheral pin 9 input.                                                                             |  |

|             |                     | 0               | 0   | DIG         | Remappable peripheral pin 9 output.                                                                            |  |

| RB7/KBI3/   | RB7                 | 0               | 0   | DIG         | LATB<7> data output.                                                                                           |  |

| PGD/RP10    |                     | 1               | Ι   | TTL         | PORTB<7> data input; weak pull-up when RBPU bit is cleared.                                                    |  |

|             | KBI3                | 1               | I   | TTL         | Interrupt-on-change pin.                                                                                       |  |

|             | PGD                 | x               | 0   | DIG         | Serial execution data output for ICSP and ICD operation. <sup>(2)</sup>                                        |  |

|             |                     | x               | I   | ST          | Serial execution data input for ICSP and ICD operation. <sup>(2)</sup>                                         |  |

|             | RP10                | 1               | Ι   | ST          | Remappable peripheral pin 10 input.                                                                            |  |

|             |                     | 0               | 0   | ST          | Remappable peripheral pin 10 output.                                                                           |  |

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRIS bit does not affect port direction or is overridden for this option)

**Note 1:** Pins are configured as analog inputs by default on POR. Using these pins for digital inputs requires setting the appropriate bits in ANCON1 first.

2: All other pin functions are disabled when ICSP<sup>™</sup> or ICD are enabled.

**3:** This bit is not available on 28-pin devices.

| Pin       | Function | TRIS<br>Setting | I/O | I/O<br>Type | Description                          |

|-----------|----------|-----------------|-----|-------------|--------------------------------------|

| RD6/PMD6/ | RD6      | 1               | Ι   | ST          | PORTD<6> data input.                 |

| RP23      |          | 0               | 0   | DIG         | LATD<6> data output.                 |

|           | PMD6     | 1               | I   | ST/TTL      | Parallel Master Port data in.        |

|           |          | 0               | 0   | DIG         | Parallel Master Port data out.       |

| RP23      |          | 1               | I   | ST          | Remappable peripheral pin 23 input.  |

|           |          | 0               | 0   | DIG         | Remappable peripheral pin 23 output. |

| RD7/PMD7/ | RD7      | 1               | I   | ST          | PORTD<7> data input.                 |

| RP24      |          | 0               | 0   | DIG         | LATD<7> data output.                 |

|           | PMD7     | 1               | Ι   | ST/TTL      | Parallel Master Port data in.        |

|           |          | 0               | 0   | DIG         | Parallel Master Port data out.       |

|           | RP24     | 1               | Ι   | ST          | Remappable peripheral pin 24 input.  |

|           |          | 0               | 0   | DIG         | Remappable peripheral pin 24 output. |

TABLE 10-9: PORTD I/O SUMMARY (CONTINUED)

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer;  $I^2C/SMB = I^2C/SMB$ us input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

| Name                 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|----------------------|--------|--------|--------|--------|--------|--------|--------|--------|----------------------------|

| PORTD <sup>(1)</sup> | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | 93                         |

| LATD <sup>(1)</sup>  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | 92                         |

| TRISD <sup>(1)</sup> | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | 92                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTD.

Note 1: These registers are not available in 28-pin devices.

| REGISTER 10-24: | : RPOR3: PERIPHERAL PIN SELECT OUTPUT REC | GISTER 3 (BANKED EC9h) |

|-----------------|-------------------------------------------|------------------------|

|-----------------|-------------------------------------------|------------------------|

| U-0                                                                | U-0 | U-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 | R/W-0 |

|--------------------------------------------------------------------|-----|-----|------------------------------------|-------|-----------------|-------|-------|

| _                                                                  | _   | —   | RP3R4                              | RP3R3 | RP3R2           | RP3R1 | RP3R0 |

| bit 7                                                              |     |     |                                    |       |                 |       | bit 0 |

|                                                                    |     |     |                                    |       |                 |       |       |

| <b>Legend:</b> $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |     |     |                                    |       |                 |       |       |

| R = Readable bit W = Writable bit                                  |     | bit | U = Unimplemented bit, read as '0' |       |                 |       |       |

| -n = Value at POR '1' = Bit is set                                 |     | ł   | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP3R<4:0>:** Peripheral Output Function is Assigned to RP3 Output Pin bits (see Table 10-14 for peripheral function numbers)

### REGISTER 10-25: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4 (BANKED ECAh)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | _   |     | RP4R4 | RP4R3 | RP4R2 | RP4R1 | RP4R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                             |                    |  |  |

|-------------------|-----------------------------------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, read | as '0'             |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared        | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP4R<4:0>:** Peripheral Output Function is Assigned to RP4 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-26: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5 (BANKED ECBh)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | RP5R4 | RP5R3 | RP5R2 | RP5R1 | RP5R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable, Writable if IOLOCK = 0 |                            |                    |  |  |

|-------------------|-----------------------------------------------------|----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                    | U = Unimplemented bit, rea | d as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared       | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP5R<4:0>:** Peripheral Output Function is Assigned to RP5 Output Pin bits (see Table 10-14 for peripheral function numbers)

## 14.0 TIMER2 MODULE

The Timer2 module incorporates the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4 and 1:16)

- Software programmable postscaler (1:1 through 1:16)

- Interrupt on TMR2 to PR2 match

- Optional use as the shift clock for the MSSP modules

The module is controlled through the T2CON register (Register 14-1) which enables or disables the timer and configures the prescaler and postscaler. Timer2 can be shut off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption.

A simplified block diagram of the module is shown in Figure 14-1.

## 14.1 Timer2 Operation

In normal operation, TMR2 is incremented from 00h on each clock (Fosc/4). A 4-bit counter/prescaler on the clock input gives direct input, divide-by-4 and divide-by-16 prescale options. These are selected by the prescaler control bits, T2CKPS<1:0> (T2CON<1:0>). The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/postscaler (see Section 14.2 "Timer2 Interrupt").

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, while the PR2 register initializes at FFh. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- a write to the T2CON register

- any device Reset (Power-on Reset (POR), MCLR Reset, Watchdog Timer Reset (WDTR) or Brown-out Reset (BOR))

TMR2 is not cleared when T2CON is written.

## REGISTER 14-1: T2CON: TIMER2 CONTROL REGISTER (ACCESS FCAh)

| U-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0  | R/W-0   | R/W-0   |

|-------|----------|----------|----------|----------|--------|---------|---------|

| —     | T2OUTPS3 | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |

| bit 7 |          |          |          |          |        |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                        |

|---------|---------------------------------------------------|

| bit 6-3 | T2OUTPS<3:0>: Timer2 Output Postscale Select bits |

|         | 0000 = 1:1 Postscale                              |

|         | 0001 = 1:2 Postscale                              |

|         | •                                                 |

|         | •                                                 |

|         | •                                                 |

|         | 1111 = 1:16 Postscale                             |

| bit 2   | TMR2ON: Timer2 On bit                             |

|         | 1 = Timer2 is on                                  |

|         | 0 = Timer2 is off                                 |

| bit 1-0 | T2CKPS<1:0>: Timer2 Clock Prescale Select bits    |

|         | 00 = Prescaler is 1                               |

|         | 01 = Prescaler is 4                               |

|         | 1x = Prescaler is 16                              |

## REGISTER 17-4: ALRMCFG: ALARM CONFIGURATION REGISTER (ACCESS F91h)

| R/W-0         | R/W-0                             | R/W-0                                 | R/W-0         | R/W-0             | R/W-0             | R/W-0            | R/W-0       |

|---------------|-----------------------------------|---------------------------------------|---------------|-------------------|-------------------|------------------|-------------|

| ALRMEN        | CHIME                             | AMASK3                                | AMASK2        | AMASK1            | AMASK0            | ALRMPTR1         | ALRMPTR0    |

| bit 7         | •                                 | ł                                     |               |                   |                   |                  | bit 0       |

|               |                                   |                                       |               |                   |                   |                  |             |

| Legend:       |                                   |                                       |               |                   |                   |                  |             |

| R = Readabl   | e bit                             | W = Writable                          | bit           | U = Unimpler      | nented bit, read  | d as '0'         |             |

| -n = Value at | POR                               | '1' = Bit is set                      |               | '0' = Bit is cle  | ared              | x = Bit is unki  | nown        |

| L:1 7         |                                   | lawa Enable bit                       |               |                   |                   |                  |             |

| bit 7         |                                   | larm Enable bit                       | doutomotical  | ly offer an elern | n overtweene      | or ADDT 27:05    |             |

|               |                                   | enabled (cleare                       | automatical   | iy alter an alarr | n event whenev    | /el ARP1<7.0>    | - 0000 0000 |

|               | 0 = Alarm is                      | ,                                     |               |                   |                   |                  |             |

| bit 6         | CHIME: Chir                       | me Enable bit                         |               |                   |                   |                  |             |

|               | 1 = Chime is                      | s enabled; ALRI                       | MRPT<7:0> b   | its are allowed   | to roll over from | m 00h to FFh     |             |

|               | 0 = Chime is                      | s disabled; ALR                       | MRPT<7:0> b   | its stop once tl  | ney reach 00h     |                  |             |

| bit 5-2       | AMASK<3:0                         | >: Alarm Mask                         | Configuration | bits              |                   |                  |             |

|               |                                   | ry half second                        |               |                   |                   |                  |             |

|               | 0001 = Eve                        |                                       |               |                   |                   |                  |             |

|               | 0010 = Eve<br>0011 = Eve          | ry 10 seconds                         |               |                   |                   |                  |             |

|               |                                   | ery 10 minutes                        |               |                   |                   |                  |             |

|               | 0101 = Eve                        |                                       |               |                   |                   |                  |             |

|               | 0110 = Ond                        | •                                     |               |                   |                   |                  |             |

|               | 0111 = Ond                        | ce a week                             |               |                   |                   |                  |             |

|               | 1000 = Onc                        |                                       |               |                   | e e th            |                  |             |

|               |                                   | ce a year (excep<br>served – do not i |               | ured for Februa   | ary 29", once e   | every four years | 6)          |

|               |                                   | served – do not i                     |               |                   |                   |                  |             |

| bit 1-0       |                                   | 1:0>: Alarm Val                       |               | indow Pointer     | hits              |                  |             |

|               |                                   | e corresponding                       | -             |                   |                   | AI RMVAI H ar    | d ALRMVALL  |

|               |                                   | e ALRMPTR<1:                          |               |                   |                   |                  |             |

|               | ʻ00'.                             |                                       |               |                   | ,<br>,            |                  |             |

|               | <u>ALRMVALH</u>                   | <u>&lt;15:8&gt;:</u>                  |               |                   |                   |                  |             |

|               | 00 <b>= ALRM</b>                  |                                       |               |                   |                   |                  |             |

|               | 01 = ALRMV                        |                                       |               |                   |                   |                  |             |

|               | 10 = ALRMN<br>11 = Unimpl         |                                       |               |                   |                   |                  |             |

|               | -                                 |                                       |               |                   |                   |                  |             |

|               | <u>ALRMVALL&lt;</u><br>00 = ALRMS |                                       |               |                   |                   |                  |             |

|               | 01 = ALRMH                        |                                       |               |                   |                   |                  |             |

|               |                                   |                                       |               |                   |                   |                  |             |

|               | 10 = ALRME                        |                                       |               |                   |                   |                  |             |

| R/W-0           | R/W-0                                                                             | R/W-0                                                       | R/W-0                                                        | R/W-0                                                                   | R/W-0                                             | R/W-0                 | R/W-0       |

|-----------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------|-----------------------|-------------|

| SSCON1          | SSCON0                                                                            | TXINC                                                       | RXINC                                                        | DUPLEX1                                                                 | DUPLEX0                                           | DLYINTEN              | DMAEN       |

| bit 7           |                                                                                   | •                                                           |                                                              |                                                                         |                                                   |                       | bit         |

| Legend:         |                                                                                   |                                                             |                                                              |                                                                         |                                                   |                       |             |

| R = Readable    | bit                                                                               | W = Writable                                                | bit                                                          | U = Unimpler                                                            | nented bit, read                                  | d as '0'              |             |

| -n = Value at F | POR                                                                               | '1' = Bit is set                                            | t                                                            | '0' = Bit is cle                                                        | ared                                              | x = Bit is unkn       | iown        |

| bit 7-6         | $11 = \frac{\text{SSDMA}}{\text{SSDMA}}$ $01 = \frac{\text{SSDMA}}{\text{SSDMA}}$ | is asserted for<br>is asserted for<br>is asserted for       | the duration<br>the duration<br>the duration                 | of 2 bytes; DLY<br>of 1 byte; DLYI                                      | INTEN is alway<br>INTEN is alway<br>NTEN is alway | ys reset low          | nable       |

| bit 5           | TXINC: Trans<br>Allows the tra<br>1 = The trans                                   | smit Address Ir<br>Insmit address<br>Imit address is        | to increment Enal<br>to increment to<br>to be increme        | ole bit<br>as the transfer<br>inted from the i                          | progresses.                                       | XADDR<11:0>           |             |

| bit 4           | Allows the recei                                                                  | ved address is                                              | to increment a to be increme                                 | is the transfer pented from the                                         | -                                                 | RXADDR<11:0><br>11:0> |             |

| bit 3-2         | 10 = SPI DM<br>01 = DMA op                                                        | A operates in F<br>erates in Half-                          | Full-Duplex mo<br>Duplex mode,                               | ing Mode Seleo<br>ode, data is sim<br>data is transm<br>data is receive | ultaneously tra<br>itted only                     | nsmitted and re       | ceived      |

| bit 1           | <b>DLYINTEN:</b> DEnables the i<br>elapsed from<br>1 = The intern                 | Delay Interrupt<br>nterrupt to be<br>the latest com         | Enable bit<br>invoked after<br>pleted transfe<br>, SSCON<1:0 | the number of                                                           | SCK cycles sp                                     | ecified in DLYC       | YC<2:0> ha  |

| bit 0           | <b>DMAEN:</b> DM<br>This bit is set                                               | A Operation St<br>by the users'<br>the DMA opera<br>session | art/Stop bit<br>software to st                               | art the DMA op<br>eted or aborted                                       |                                                   | eset back to zer      | o by the DM |

## REGISTER 19-3: DMACON1: DMA CONTROL REGISTER 1 (ACCESS F88h)

## 20.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

The Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) module is one of two serial I/O modules. (Generically, the EUSART is also known as a Serial Communications Interface or SCI.) The EUSART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs and so on.

The Enhanced USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These make it ideally suited for use in Local Interconnect Network bus (LIN/J2602 bus) systems.

All members of the PIC18F46J11 family are equipped with two independent EUSART modules, referred to as EUSART1 and EUSART2. They can be configured in the following modes:

- Asynchronous (full-duplex) with:

- Auto-wake-up on character reception

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half-duplex) with selectable clock polarity

- Synchronous Slave (half-duplex) with selectable clock polarity

The pins of EUSART1 and EUSART2 are multiplexed with the functions of PORTC (RC6/PMA5/TX1/CK1/RP17 and RC7/PMA4/RX1/DT1/RP18) and remapped (RPn1/TX2/CK2 and RPn2/RX2/DT2), respectively. In order to configure these pins as an EUSART:

- For EUSART1:

- SPEN bit (RCSTA1<7>) must be set (= 1)

- TRISC<7> bit must be set (= 1)

- TRISC<6> bit must be cleared (= 0) for Asynchronous and Synchronous Master modes

- TRISC<6> bit must be set (= 1) for Synchronous Slave mode

- For EUSART2:

- SPEN bit (RCSTA2<7>) must be set (= 1)

- TRIS bit for RPn2/RX2/DT2 = 1

- TRIS bit for RPn1/TX2/CK2 = 0 for Asynchronous and Synchronous Master modes

- TRISC<6> bit must be set (= 1) for Synchronous Slave mode

Note: The EUSART control will automatically reconfigure the pin from input to output as needed.

The TXx/CKx I/O pins have an optional open-drain output capability. By default, when this pin is used by the EUSART as an output, it will function as a standard push-pull CMOS output. The TXx/CKx I/O pins' open-drain, output feature can be enabled by setting the corresponding UxOD bit in the ODCON2 register. For more details, see **Section 19.3.3 "Open-Drain Output Option"**.

The operation of each Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTAx)

- Receive Status and Control (RCSTAx)

- Baud Rate Control (BAUDCONx)

These are covered in detail in Register 20-1, Register 20-2 and Register 20-3, respectively.

Note: Throughout this section, references to register and bit names that may be associated with a specific EUSART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "RCSTAx" might refer to the Receive Status register for either EUSART1 or EUSART2.

# PIC18F46J11 FAMILY

The WUE bit is automatically cleared once a low-to-high transition is observed on the RXx line following the wake-up event. At this point, the EUSART module is in Idle mode and returns to normal operation. This signals to the user that the Sync Break event is over.

## 20.2.4.1 Special Considerations Using Auto-Wake-up

Since auto-wake-up functions by sensing rising edge transitions on RXx/DTx, information with any state changes before the Stop bit may signal a false End-Of-Character (EOC) and cause data or framing errors. To work properly, therefore, the initial character in the transmission must be all '0's. This can be 00h (8 bits) for standard RS-232 devices or 000h (12 bits) for LIN/J2602 bus.

Oscillator start-up time must also be considered, especially in applications using oscillators with longer start-up intervals (i.e., HS or HSPLL mode). The Sync Break (or Wake-up Signal) character must be of sufficient length and be followed by a sufficient interval to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

## 20.2.4.2 Special Considerations Using the WUE Bit

The timing of WUE and RCxIF events may cause some confusion when it comes to determining the validity of received data. As noted, setting the WUE bit places the EUSART in an Idle mode. The wake-up event causes a receive interrupt by setting the RCxIF bit. The WUE bit is cleared after this when a rising edge is seen on RXx/DTx. The interrupt condition is then cleared by reading the RCREGx register. Ordinarily, the data in RCREGx will be dummy data and should be discarded.

The fact that the WUE bit has been cleared (or is still set) and the RCxIF flag is set should not be used as an indicator of the integrity of the data in RCREGx. Users should consider implementing a parallel method in firmware to verify received data integrity.

To assure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

## FIGURE 20-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING NORMAL OPERATION

## FIGURE 20-9: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

|                                                            | soli svenski<br>Hodel      |                    | · · · · · · · · · · · · · · · · · · · |      |                                         |  |  |

|------------------------------------------------------------|----------------------------|--------------------|---------------------------------------|------|-----------------------------------------|--|--|

| exe: înfreden verden en e | 985,855 (58 <sup>32)</sup> | sigye tas titt<br> | · · · · · · · · · · · · · · · · · · · | <br> | ···· ··· ··· ·· ·· ·· ·· ·· ·· ·· ·· ·· |  |  |

More still if the water-up event requires long coolising water-up time, the supporter of the Vitili set over the test the second or there is a second or the second or the presence of C device.

2: The EUSART commune in the while the VEUE at a set.

| Bit 7                | Bit 6                                                                                                                                                                             | Bit 5                                                                                                                                                                                                                | Bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Reset<br>Values<br>on Page:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GIE/GIEH             | PEIE/GIEL                                                                                                                                                                         | TMR0IE                                                                                                                                                                                                               | INT0IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RBIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TMR0IF                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>INT0IF</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RBIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PMPIF <sup>(1)</sup> | ADIF                                                                                                                                                                              | RC1IF                                                                                                                                                                                                                | TX1IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SSP1IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CCP1IF                                                                                                                                                                                                                                                                                                                                                                                                                                              | TMR2IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TMR1IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |