Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 48MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 34                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 3.8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 44-QFN (8x8)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf45j11t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

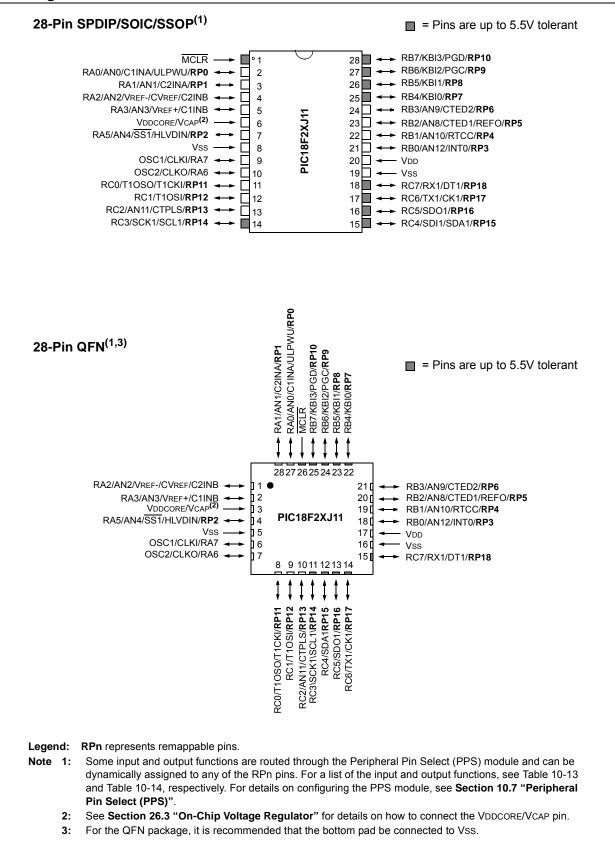

#### **Pin Diagrams**

# 5.5 Configuration Mismatch (CM)

The Configuration Mismatch (CM) Reset is designed to detect, and attempt to recover from, random memory corrupting events. These include Electrostatic Discharge (ESD) events, which can cause widespread single bit changes throughout the device and result in catastrophic failure.

In PIC18FXXJ Flash devices, the device Configuration registers (located in the configuration memory space) are continuously monitored during operation by comparing their values to complimentary shadow registers. If a mismatch is detected between the two sets of registers, a CM Reset automatically occurs. These events are captured by the CM bit (RCON<5>). The state of the bit is set to '0' whenever a CM event occurs; it does not change for any other Reset event.

A CM Reset behaves similarly to a MCLR, RESET instruction, WDT time-out or Stack Event Resets. As with all hard and power Reset events, the device Configuration Words are reloaded from the Flash Configuration Words in program memory as the device restarts.

## 5.6 Power-up Timer (PWRT)

PIC18F46J11 family devices incorporate an on-chip PWRT to help regulate the POR process. The PWRT is always enabled. The main function is to ensure that the device voltage is stable before code is executed.

The Power-up Timer (PWRT) of the PIC18F46J11 family devices is a 5-bit counter which uses the INTRC source as the clock input. This yields an approximate time interval of  $32 \times 32 \ \mu s = 1 \ ms$ . While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip-to-chip due to temperature and process variation. See DC parameter 33 (TPWRT) for details.

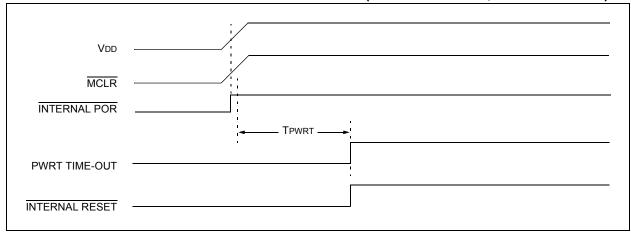

#### 5.6.1 TIME-OUT SEQUENCE

The PWRT time-out is invoked after the POR pulse has cleared. The total time-out will vary based on the status of the PWRT. Figure 5-2, Figure 5-3, Figure 5-4 and Figure 5-5 all depict time-out sequences on power-up with the PWRT.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$ is kept low long enough, the PWRT will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately if a clock source is available (Figure 5-4). This is useful for testing purposes, or to synchronize more than one PIC18FXXXX device operating in parallel.

#### FIGURE 5-2: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD, VDD RISE < TPWRT)

### TABLE 6-3: NON-ACCESS BANK SPECIAL FUNCTION REGISTER MAP

| Address | Name                    | Address | Name    | Address | Name | Address | Name    | Address | Name                  |

|---------|-------------------------|---------|---------|---------|------|---------|---------|---------|-----------------------|

| F5Fh    | PMCONH <sup>(1)</sup>   | F3Fh    | RTCCFG  | F1Fh    | —    | EFFh    | PPSCON  | EDFh    | _                     |

| F5Eh    | PMCONL <sup>(1)</sup>   | F3Eh    | RTCCAL  | F1Eh    | _    | EFEh    | RPINR24 | EDEh    | RPOR24 <sup>(1)</sup> |

| F5Dh    | PMMODEH <sup>(1)</sup>  | F3Dh    | REFOCON | F1Dh    | _    | EFDh    | RPINR23 | EDDh    | RPOR23 <sup>(1)</sup> |

| F5Ch    | PMMODEL <sup>(1)</sup>  | F3Ch    | PADCFG1 | F1Ch    | _    | EFCh    | RPINR22 | EDCh    | RPOR22 <sup>(1)</sup> |

| F5Bh    | PMDOUT2H <sup>(1)</sup> | F3Bh    | _       | F1Bh    | _    | EFBh    | RPINR21 | EDBh    | RPOR21 <sup>(1)</sup> |

| F5Ah    | PMDOUT2L <sup>(1)</sup> | F3Ah    | _       | F1Ah    | _    | EFAh    | _       | EDAh    | RPOR20 <sup>(1)</sup> |

| F59h    | PMDIN2H <sup>(1)</sup>  | F39h    | _       | F19h    | _    | EF9h    | _       | ED9h    | RPOR19 <sup>(1)</sup> |

| F58h    | PMDIN2L <sup>(1)</sup>  | F38h    | _       | F18h    | _    | EF8h    | _       | ED8h    | RPOR18                |

| F57h    | PMEH <sup>(1)</sup>     | F37h    | _       | F17h    | _    | EF7h    | RPINR17 | ED7h    | RPOR17                |

| F56h    | PMEL <sup>(1)</sup>     | F36h    |         | F16h    | —    | EF6h    | RPINR16 | ED6h    | RPOR16                |

| F55h    | PMSTATH <sup>(1)</sup>  | F35h    |         | F15h    | —    | EF5h    | _       | ED5h    | RPOR15                |

| F54h    | PMSTATL <sup>(1)</sup>  | F34h    |         | F14h    | —    | EF4h    | _       | ED4h    | RPOR14                |

| F53h    | CVRCON                  | F33h    |         | F13h    | —    | EF3h    | _       | ED3h    | RPOR13                |

| F52h    | TCLKCON                 | F32h    |         | F12h    | —    | EF2h    | _       | ED2h    | RPOR12                |

| F51h    | -                       | F31h    |         | F11h    | —    | EF1h    | _       | ED1h    | RPOR11                |

| F50h    | -                       | F30h    |         | F10h    | —    | EF0h    | _       | ED0h    | RPOR10                |

| F4Fh    | DSGPR1 <sup>(2)</sup>   | F2Fh    |         | F0Fh    | —    | EEFh    | _       | ECFh    | RPOR9                 |

| F4Eh    | DSGPR0 <sup>(2)</sup>   | F2Eh    | —       | F0Eh    | —    | EEEh    | RPINR8  | ECEh    | RPOR8                 |

| F4Dh    | DSCONH <sup>(2)</sup>   | F2Dh    | —       | F0Dh    | —    | EEDh    | RPINR7  | ECDh    | RPOR7                 |

| F4Ch    | DSCONL <sup>(2)</sup>   | F2Ch    | _       | F0Ch    | —    | EECh    | RPINR6  | ECCh    | RPOR6                 |

| F4Bh    | DSWAKEH <sup>(2)</sup>  | F2Bh    | _       | F0Bh    | —    | EEBh    | —       | ECBh    | RPOR5                 |

| F4Ah    | DSWAKEL <sup>(2)</sup>  | F2Ah    | _       | F0Ah    | —    | EEAh    | RPINR4  | ECAh    | RPOR4                 |

| F49h    | ANCON1                  | F29h    | _       | F09h    | —    | EE9h    | RPINR3  | EC9h    | RPOR3                 |

| F48h    | ANCON0                  | F28h    | _       | F08h    | —    | EE8h    | RPINR2  | EC8h    | RPOR2                 |

| F47h    | —                       | F27h    | _       | F07h    | —    | EE7h    | RPINR1  | EC7h    | RPOR1                 |

| F46h    | —                       | F26h    | _       | F06h    | —    | EE6h    | —       | EC6h    | RPOR0                 |

| F45h    | —                       | F25h    | _       | F05h    | —    | EE5h    | —       | EC5h    | —                     |

| F44h    | —                       | F24h    | _       | F04h    | —    | EE4h    | —       | EC4h    | —                     |

| F43h    | _                       | F23h    | _       | F03h    | _    | EE3h    | _       | EC3h    | _                     |

| F42h    | ODCON1                  | F22h    | —       | F02h    | _    | EE2h    | —       | EC2h    | —                     |

| F41h    | ODCON2                  | F21h    | _       | F01h    | _    | EE1h    | —       | EC1h    | _                     |

| F40h    | ODCON3                  | F20h    | _       | F00h    | _    | EE0h    | _       | EC0h    | —                     |

Note 1: This register is not available on 28-pin devices.

2: Deep Sleep registers are not available on LF devices.

| File Name              | Bit 7        | Bit 6           | Bit 5                     | Bit 4                 | Bit 3                 | Bit 2                         | Bit 1                      | Bit 0    | Value on<br>POR, BOR | Details<br>on<br>Page: |

|------------------------|--------------|-----------------|---------------------------|-----------------------|-----------------------|-------------------------------|----------------------------|----------|----------------------|------------------------|

| STATUS                 | —            | —               | —                         | N                     | OV                    | Z                             | DC                         | С        | x xxxx               | 70, 96                 |

| TMR0H                  | Timer0 Regis | ter High Byte   |                           |                       |                       |                               |                            |          | 0000 0000            | 70                     |

| TMR0L                  | Timer0 Regis | ter Low Byte    |                           |                       |                       |                               |                            |          | XXXX XXXX            | 70                     |

| T0CON                  | TMR0ON       | T08BIT          | TOCS                      | T0SE                  | PSA                   | T0PS2                         | T0PS1                      | T0PS0    | 1111 1111            | 70, 197                |

| OSCCON                 | IDLEN        | IRCF2           | IRCF1                     | IRCF0                 | OSTS <sup>(2)</sup>   |                               | SCS1                       | SCS0     | 0110 q-00            | 70, 44                 |

| CM1CON                 | CON          | COE             | CPOL                      | EVPOL1                | EVPOL0                | CREF                          | CCH1                       | CCH0     | 0001 1111            | 70, 362                |

| CM2CON                 | CON          | COE             | CPOL                      | EVPOL1                | EVPOL0                | CREF                          | CCH1                       | CCH0     | 0001 1111            | 70, 362                |

| RCON                   | IPEN         | _               | CM                        | RI                    | TO                    | PD                            | POR                        | BOR      | 0-11 1100            | 70, 129                |

| TMR1H                  | Timer1 Regis | ter High Byte   |                           |                       |                       |                               |                            |          | xxxx xxxx            | 70                     |

| TMR1L                  | Timer1 Regis | ter Low Byte    |                           |                       |                       |                               |                            |          | xxxx xxxx            | 70                     |

| T1CON                  | TMR1CS1      | TMR1CS0         | T1CKPS1                   | T1CKPS0               | T1OSCEN               | T1SYNC                        | RD16                       | TMR10N   | 0000 0000            | 70, 201                |

| TMR2                   | Timer2 Regis | ter             |                           | •                     |                       | •                             | •                          | •        | 0000 0000            | 70                     |

| PR2                    | Timer2 Perio | d Register      |                           |                       |                       |                               |                            |          | 1111 1111            | 70                     |

| T2CON                  | —            | T2OUTPS3        | T2OUTPS2                  | T2OUTPS1              | T2OUTPS0              | TMR2ON                        | T2CKPS1                    | T2CKPS0  | -000 0000            | 70, 213                |

| SSP1BUF                | MSSP1 Rece   | eive Buffer/Tra | nsmit Register            | r                     |                       | •                             | •                          | •        | xxxx xxxx            | 70                     |

| SSP1ADD                | MSSP1 Addr   | ess Register (  | I <sup>2</sup> C™ Slave m | ode), MSSP1           | Baud Rate Re          | load Register (l <sup>2</sup> | <sup>2</sup> C Master mode | e)       | 0000 0000            | 70                     |

| SSP1MSK <sup>(4)</sup> | MSK7         | MSK6            | MSK5                      | MSK4                  | MSK3                  | MSK2                          | MSK1                       | MSK0     | 1111 1111            | 70, 295                |

| SSP1STAT               | SMP          | CKE             | D/A                       | Р                     | S                     | R/W                           | UA                         | BF       | 0000 0000            | 70, 292                |

| SSP1CON1               | WCOL         | SSPOV           | SSPEN                     | CKP                   | SSPM3                 | SSPM2                         | SSPM1                      | SSPM0    | 0000 0000            | 70, 293                |

| SSP1CON2               | GCEN         | ACKSTAT         | ACKDT                     | ACKEN                 | RCEN                  | PEN                           | RSEN                       | SEN      | 0000 0000            | 70, 294                |

|                        | GCEN         | ACKSTAT         | ADMSK5 <sup>(4)</sup>     | ADMSK4 <sup>(4)</sup> | ADMSK3 <sup>(4)</sup> | ADMSK2(4)                     | ADMSK1 <sup>(4)</sup>      | SEN      |                      |                        |

| ADRESH                 | A/D Result R | egister High B  | yte                       |                       |                       |                               |                            |          | XXXX XXXX            | 70                     |

| ADRESL                 | A/D Result R | egister Low B   | yte                       |                       |                       |                               |                            |          | xxxx xxxx            | 70                     |

| ADCON0                 | VCFG1        | VCFG0           | CHS3                      | CHS2                  | CHS1                  | CHS0                          | GO/DONE                    | ADON     | 0000 0000            | 70, 351                |

| ADCON1                 | ADFM         | ADCAL           | ACQT2                     | ACQT1                 | ACQT0                 | ADCS2                         | ADCS1                      | ADCS0    | 0000 0000            | 70, 352                |

| WDTCON                 | REGSLP       | LVDSTAT         | ULPLVL                    | —                     | DS                    | ULPEN                         | ULPSINK                    | SWDTEN   | 1qq- q00             | 70, 406                |

| PSTR1CON               | CMPL1        | CMPL0           | _                         | STRSYNC               | STRD                  | STRC                          | STRB                       | STRA     | 00-0 0001            | 70, 267                |

| ECCP1AS                | ECCP1ASE     | ECCP1AS2        | ECCP1AS1                  | ECCP1AS0              | PSS1AC1               | PSS1AC0                       | PSS1BD1                    | PSS1BD0  | 0000 0000            | 70                     |

| ECCP1DEL               | P1RSEN       | P1DC6           | P1DC5                     | P1DC4                 | P1DC3                 | P1DC2                         | P1DC1                      | P1DC0    | 0000 0000            | 71                     |

| CCPR1H                 | Capture/Com  | pare/PWM Re     | egister 1 Hlgh            | Byte                  |                       |                               |                            |          | XXXX XXXX            | 71                     |

| CCPR1L                 | Capture/Com  | pare/PWM Re     | gister 1 Low E            | Byte                  |                       |                               | r                          | 1        | XXXX XXXX            | 71                     |

| CCP1CON                | P1M1         | P1M0            | DC1B1                     | DC1B0                 | CCP1M3                | CCP1M2                        | CCP1M1                     | CCP1M0   | 0000 0000            | 71                     |

| PSTR2CON               | CMPL1        | CMPL0           | —                         | STRSYNC               | STRD                  | STRC                          | STRB                       | STRA     | 00-0 0001            | 71, 267                |

| ECCP2AS                | ECCP2ASE     | ECCP2AS2        | ECCP2AS1                  | ECCP2AS0              | PSS2AC1               | PSS2AC0                       | PSS2BD1                    | PSS2BD0  | 0000 0000            | 71                     |

| ECCP2DEL               | P2RSEN       | P2DC6           | P2DC5                     | P2DC4                 | P2DC3                 | P2DC2                         | P2DC1                      | P2DC0    | 0000 0000            | 71                     |

| CCPR2H                 | Capture/Com  | pare/PWM Re     | egister 2 High            | Byte                  |                       |                               |                            |          | XXXX XXXX            | 71                     |

| CCPR2L                 | Capture/Com  | pare/PWM Re     | gister 2 Low E            | Byte                  |                       |                               | r                          | 1        | XXXX XXXX            | 71                     |

| CCP2CON                | P2M1         | P2M0            | DC2B1                     | DC2B0                 | CCP2M3                | CCP2M2                        | CCP2M1                     | CCP2M0   | 0000 0000            | 71                     |

| CTMUCONH               | CTMUEN       | —               | CTMUSIDL                  | TGEN                  | EDGEN                 | EDGSEQEN                      | IDISSEN                    | —        | 0-00 000-            | 71                     |

| CTMUCONL               | EDG2POL      | EDG2SEL1        | EDG2SEL0                  | EDG1POL               | EDG1SEL1              | EDG1SEL0                      | EDG2STAT                   | EDG1STAT | 0000 00xx            | 71                     |

| CTMUICON               | ITRIM5       | ITRIM4          | ITRIM3                    | ITRIM2                | ITRIM1                | ITRIM0                        | IRNG1                      | IRNG0    | 0000 0000            | 71                     |

| SPBRG1                 | EUSART1 Ba   | aud Rate Gene   | erator Register           | r Low Byte            |                       |                               |                            |          | 0000 0000            | 71                     |

| TABLE 6-4: | <b>REGISTER FILE SUMMARY</b> | (PIC18F46J11 FAMILY) |

|------------|------------------------------|----------------------|

|            |                              |                      |

Note 1: Bit 21 of the PC is only available in Serial Programming (SP) modes.

2: Reset value is '0' when Two-Speed Start-up is enabled and '1' if disabled.

3: The SSPxMSK registers are only accessible when SSPxCON2<3:0> = 1001.

Alternate names and definitions for these bits when the MSSP module is operating in I<sup>2</sup>C<sup>TM</sup> Slave mode. See Section 19.5.3.2 "Address 4: Masking Modes" for details.

5: These bits and/or registers are only available in 44-pin devices; otherwise, they are unimplemented and read as '0'. Reset values are shown for 44-pin devices.

6: The PMADDRH/PMDOUT1H and PMADDRL/PMDOUT1L register pairs share the same physical registers and addresses, but have different functions determined by the module's operating mode. See Section 11.1.2 "Data Registers" for more information.

| Pin       | Function      | TRIS<br>Setting     | I/O | I/O<br>Type | Description                          |

|-----------|---------------|---------------------|-----|-------------|--------------------------------------|

| RD6/PMD6/ | RD6/PMD6/ RD6 |                     | Ι   | ST          | PORTD<6> data input.                 |

| RP23      |               | 0                   | 0   | DIG         | LATD<6> data output.                 |

|           | PMD6          | 1                   | I   | ST/TTL      | Parallel Master Port data in.        |

|           |               | 0                   | 0   | DIG         | Parallel Master Port data out.       |

| RP23      |               | 1                   | I   | ST          | Remappable peripheral pin 23 input.  |

|           |               | 0                   | 0   | DIG         | Remappable peripheral pin 23 output. |

| RD7/PMD7/ | RD7           | 1                   | I   | ST          | PORTD<7> data input.                 |

| RP24      | RP24          |                     | 0   | DIG         | LATD<7> data output.                 |

|           | PMD7          | 1                   | Ι   | ST/TTL      | Parallel Master Port data in.        |

|           |               | 0                   | 0   | DIG         | Parallel Master Port data out.       |

|           | RP24          | RP24 1 I ST Remappa |     | ST          | Remappable peripheral pin 24 input.  |

|           |               | 0                   | 0   | DIG         | Remappable peripheral pin 24 output. |

TABLE 10-9: PORTD I/O SUMMARY (CONTINUED)

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer;  $I^2C/SMB = I^2C/SMB$ us input buffer; x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

| Name                 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|----------------------|--------|--------|--------|--------|--------|--------|--------|--------|----------------------------|

| PORTD <sup>(1)</sup> | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | 93                         |

| LATD <sup>(1)</sup>  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | 92                         |

| TRISD <sup>(1)</sup> | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | 92                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTD.

Note 1: These registers are not available in 28-pin devices.

# 16.0 TIMER4 MODULE

The Timer4 timer module has the following features:

- 8-Bit Timer register (TMR4)

- 8-Bit Period register (PR4)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMR4 match of PR4

Timer4 has a control register shown in Register 16-1. Timer4 can be shut off by clearing control bit, TMR4ON (T4CON<2>), to minimize power consumption. The prescaler and postscaler selection of Timer4 is also controlled by this register. Figure 16-1 is a simplified block diagram of the Timer4 module.

## 16.1 Timer4 Operation

Timer4 can be used as the PWM time base for the PWM mode of the ECCP modules. The TMR4 register is readable and writable and is cleared on any device Reset. The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits, T4CKPS<1:0> (T4CON<1:0>). The match output of TMR4 goes through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling inclusive) to generate a TMR4 interrupt, latched in flag bit, TMR4IF (PIR3<3>).

The prescaler and postscaler counters are cleared when any of the following occurs:

- · a write to the TMR4 register

- a write to the T4CON register

- any device Reset (Power-on Reset (POR), MCLR Reset, Watchdog Timer Reset (WDTR) or Brown-out Reset (BOR))

TMR4 is not cleared when T4CON is written.

#### REGISTER 16-1: T4CON: TIMER4 CONTROL REGISTER (ACCESS F76h)

| U-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0  | R/W-0   | R/W-0   |

|-------|----------|----------|----------|----------|--------|---------|---------|

| —     | T4OUTPS3 | T4OUTPS2 | T4OUTPS1 | T4OUTPS0 | TMR4ON | T4CKPS1 | T4CKPS0 |

| bit 7 |          |          |          |          |        |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 7 Unimplemented: Read as '0'

| bit 6-3 | <b>T4OUTPS&lt;3:0&gt;:</b> Timer4 Output Postscale Select bits<br>0000 = 1:1 Postscale<br>0001 = 1:2 Postscale |

|---------|----------------------------------------------------------------------------------------------------------------|

|         | •                                                                                                              |

|         | •                                                                                                              |

|         | 1111 = 1:16 Postscale                                                                                          |

| bit 2   | TMR4ON: Timer4 On bit                                                                                          |

|         | 1 = Timer4 is on                                                                                               |

|         | 0 = Timer4 is off                                                                                              |

| bit 1-0 | T4CKPS<1:0>: Timer4 Clock Prescale Select bits                                                                 |

|         | 00 = Prescaler is 1                                                                                            |

|         | 01 = Prescaler is 4                                                                                            |

|         | 1x = Prescaler is 16                                                                                           |

### REGISTER 17-5: ALRMRPT: ALARM REPEAT COUNTER (ACCESS F90h)

| bit 7 bit 0 |       |       |       |       |       |       |       |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| ARPT7       | ARPT6 | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 |  |  |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

| Legend:                                                              |                  |                      |                    |  |  |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|--|--|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |  |  |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits 11111111 = Alarm will repeat 255 more times

.

00000000 = Alarm will not repeat

The counter decrements on any alarm event. The counter is prevented from rolling over from 00h to FFh unless CHIME = 1.

#### 18.5.8 **OPERATION IN POWER-MANAGED** MODES

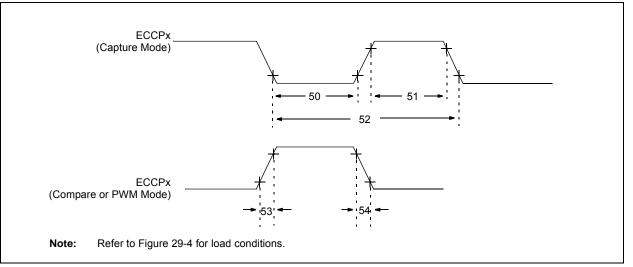

In Sleep mode, all clock sources are disabled. Timer2 will not increment and the state of the module will not change. If the ECCPx pin is driving a value, it will continue to drive that value. When the device wakes up, it will continue from this state. If Two-Speed Start-ups are enabled, the initial start-up frequency from HFINTOSC and the postscaler may not be stable immediately.

In PRI IDLE mode, the primary clock will continue to clock the ECCPx module without change.

#### 18.5.8.1 Operation with Fail-Safe Clock Monitor (FSCM)

If the Fail-Safe Clock Monitor (FSCM) is enabled, a clock failure will force the device into the power-managed RC RUN mode and the OSCFIF bit of the PIR2 register will be set. The ECCPx will then be clocked from the internal oscillator clock source, which may have a different clock frequency than the primary clock.

#### EFFECTS OF A RESET 18.5.9

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the ECCP registers to their Reset states.

This forces the ECCP module to reset to a state compatible with previous, non-enhanced ECCP modules used on other PIC18 and PIC16 devices.

| Name     | Bit 7                | Bit 6          | Bit 5          | Bit 4    | Bit 3    | Bit 2   | Bit 1   | Bit 0   | Reset<br>Values<br>on page: |

|----------|----------------------|----------------|----------------|----------|----------|---------|---------|---------|-----------------------------|

| INTCON   | GIE/GIEH             | PEIE/GIEL      | TMR0IE         | INT0IE   | RABIE    | TMR0IF  | INT0IF  | RABIF   | 69                          |

| RCON     | IPEN                 |                | _              | RI       | TO       | PD      | POR     | BOR     | 70                          |

| PIR1     | PMPIF <sup>(1)</sup> | ADIF           | RCIF           | TXIF     | SSPIF    | CCP1IF  | TMR2IF  | TMR1IF  | 72                          |

| PIE1     | PMPIE <sup>(1)</sup> | ADIE           | RCIE           | TXIE     | SSPIE    | CCP1IE  | TMR2IE  | TMR1IE  | 72                          |

| IPR1     | PMPIP <sup>(1)</sup> | ADIP           | RCIP           | TXIP     | SSPIP    | CCP1IP  | TMR2IP  | TMR1IP  | 72                          |

| PIR2     | OSCFIF               | CM2IF          | CM1IF          | _        | BCL1IF   | LVDIF   | TMR3IF  | CCP2IF  | 72                          |

| PIE2     | OSCFIE               | CM2IE          | CM1IE          | _        | BCL1IE   | LVDIE   | TMR3IE  | CCP2IE  | 72                          |

| IPR2     | OSCFIP               | CM2IP          | CM1IP          | _        | BCL1IP   | LVDIP   | TMR3IP  | CCP2IP  | 72                          |

| TRISC    | TRISC7               | TRISC6         | TRISC5         | TRISC4   | TRISC3   | TRISC2  | TRISC1  | TRISC0  | 72                          |

| TMR1L    | Timer1 Regi          | ster Low Byte  |                |          |          |         |         |         | 70                          |

| TMR1H    | Timer1 Regi          | ster High Byte | 9              |          |          |         |         |         | 70                          |

| TCLKCON  | _                    |                |                | T1RUN    | _        | _       | T3CCP2  | T3CCP1  | 94                          |

| T1CON    | TMR1CS1              | TMR1CS0        | T1CKPS1        | T1CKPS0  | T10SCEN  | T1SYNC  | RD16    | TMR10N  | 70                          |

| TMR2     | Timer2 Regi          | ster           |                |          |          |         |         |         | 70                          |

| T2CON    | _                    | T2OUTPS3       | T2OUTPS2       | T2OUTPS1 | T2OUTPS0 | TMR2ON  | T2CKPS1 | T2CKPS0 | 70                          |

| PR2      | Timer2 Peric         | d Register     |                |          |          |         |         |         | 70                          |

| TMR3L    | Timer3 Regi          | ster Low Byte  |                |          |          |         |         |         | 73                          |

| TMR3H    | Timer3 Regi          | ster High Byte | 9              |          |          |         |         |         | 73                          |

| T3CON    | TMR3CS1              | TMR3CS0        | T3CKPS1        | T3CKPS0  | _        | T3SYNC  | RD16    | TMR3ON  | 73                          |

| CCPR1L   | Capture/Cor          | npare/PWM F    | Register 1 Lov | v Byte   |          |         |         |         | 72                          |

| CCPR1H   | Capture/Cor          | npare/PWM F    | Register 1 Hig | h Byte   |          |         |         |         | 72                          |

| CCP1CON  | P1M1                 | P1M0           | DC1B1          | DC1B0    | CCP1M3   | CCP1M2  | CCP1M1  | CCP1M0  | 72                          |

| ECCP1AS  | ECCP1ASE             | ECCP1AS2       | ECCP1AS1       | ECCP1AS0 | PSS1AC1  | PSS1AC0 | PSS1BD1 | PSS1BD0 | 70                          |

| ECCP1DEL | P1RSEN               | P1DC6          | P1DC5          | P1DC4    | P1DC3    | P1DC2   | P1DC1   | P1DC0   | 72                          |

## TABLE 18-5: REGISTERS ASSOCIATED WITH ECCP1 MODULE AND TIMER1 TO TIMER3

nimplemented, read as '0'. Shaded cells are not used during ECCP operation.

Note 1: These bits are only available on 44-pin devices.

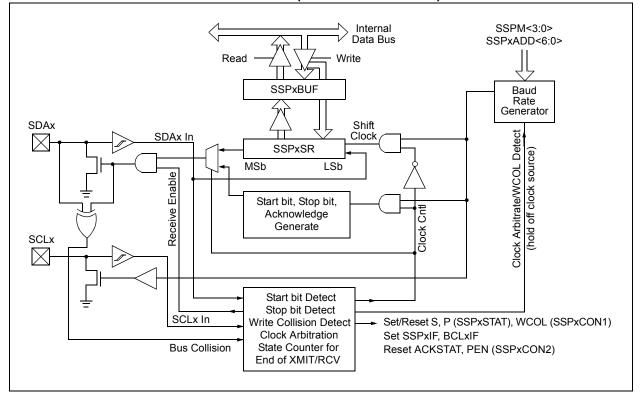

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPxBUF register to initiate transmission before the Start condition is complete. In this case, the SSPxBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPxBUF did not occur.

The following events will cause the MSSP Interrupt Flag bit, SSPxIF, to be set (and MSSP interrupt, if enabled):

- · Start condition

- Stop condition

- · Data transfer byte transmitted/received

- · Acknowledge transmitted

- Repeated Start

#### FIGURE 19-18: MSSPx BLOCK DIAGRAM (I<sup>2</sup>C<sup>™</sup> MASTER MODE)

#### 19.5.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDAx while SCLx outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. S and P conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address, followed by a '1' to indicate the receive bit. Serial data is received via SDAx, while SCLx outputs the serial clock. Serial data is received, an Acknowledge bit is transmitted. S and P conditions indicate the beginning and end of transmission.

The BRG, used for the SPI mode operation, is used to set the SCLx clock frequency for either 100 kHz, 400 kHz or 1 MHz  $I^2$ C operation. See **Section 19.5.7 "Baud Rate"** for more details.

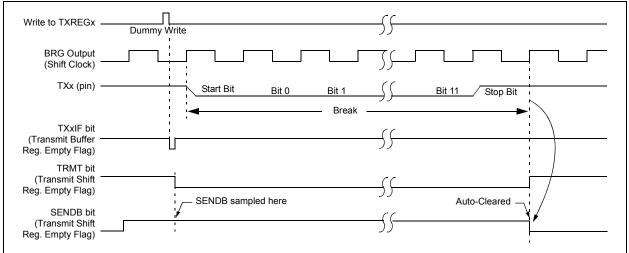

### 20.2.5 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN/J2602 bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTAx<3> and TXSTAx<5>) are set while the Transmit Shift Register is loaded with data.

Note that the value of data written to TXREGx will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN/J2602 specification).

Note that the data value written to the TXREGx for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 20-10 for the timing of the Break character sequence.

#### 20.2.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN/J2602 bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREGx with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREGx to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREGx becomes empty, as indicated by the TXxIF, the next data byte can be written to TXREGx.

#### 20.2.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in **Section 20.2.4 "Auto-Wake-up on Sync Break Character"**. By enabling this feature, the EUSART will sample the next two transitions on RXx/DTx, cause an RCxIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABDEN bit once the TXxIF interrupt is observed.

#### FIGURE 20-10: SEND BREAK CHARACTER SEQUENCE

## 26.5.2 EXITING FAIL-SAFE OPERATION

The Fail-Safe Clock Monitor condition is terminated by either a device Reset or by entering a power-managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 2H (with any required start-up delays that are required for the oscillator mode, such as OST or PLL timer). The INTRC oscillator provides the device clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The FSCM then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTRC oscillator. The OSCCON register will remain in its Reset state until a power-managed mode is entered.

#### 26.5.3 FSCM INTERRUPTS IN POWER-MANAGED MODES

By entering a power-managed mode, the clock multiplexer selects the clock source selected by the OSCCON register. FSCM of the power-managed clock source resumes in the power-managed mode.

If an oscillator failure occurs during power-managed operation, the subsequent events depend on whether or not the oscillator failure interrupt is enabled. If enabled (OSCFIF = 1), code execution will be clocked by the INTRC multiplexer. An automatic transition back to the failed clock source will not occur.

If the interrupt is disabled, subsequent interrupts while in Idle mode will cause the CPU to begin executing instructions while being clocked by the INTRC source.

#### 26.5.4 POR OR WAKE-UP FROM SLEEP

The FSCM is designed to detect oscillator failure at any point after the device has exited Power-on Reset (POR) or low-power Sleep mode. When the primary device clock is either the EC or INTRC modes, monitoring can begin immediately following these events.

For HS or HSPLL modes, the situation is somewhat different. Since the oscillator may require a start-up time considerably longer than the FSCM sample clock time, a false clock failure may be detected. To prevent this, the internal oscillator block is automatically configured as the device clock and functions until the primary clock is stable (the OST and PLL timers have timed out). This is identical to Two-Speed Start-up mode. Once the primary clock is stable, the INTRC returns to its role as the FSCM source.

| Note: | The same logic that prevents false             |

|-------|------------------------------------------------|

|       | oscillator failure interrupts on POR, or       |

|       | wake-up from Sleep, will also prevent the      |

|       | detection of the oscillator's failure to start |

|       | at all following these events. This can be     |

|       | avoided by monitoring the OSTS bit and         |

|       | using a timing routine to determine if the     |

|       | oscillator is taking too long to start. Even   |

|       | so, no oscillator failure interrupt will be    |

|       | flagged.                                       |

As noted in Section 26.4.1 "Special Considerations for Using Two-Speed Start-up", it is also possible to select another clock configuration and enter an alternate power-managed mode while waiting for the primary clock to become stable. When the new power-managed mode is selected, the primary clock is disabled.

## 26.6 Program Verification and Code Protection

For all devices in the PIC18F46J11 family of devices, the on-chip program memory space is treated as a single block. Code protection for this block is controlled by one Configuration bit, CP0. This bit inhibits external reads and writes to the program memory space. It has no direct effect in normal execution mode.

#### 26.6.1 CONFIGURATION REGISTER PROTECTION

The Configuration registers are protected against untoward changes or reads in two ways. The primary protection is the write-once feature of the Configuration bits, which prevents reconfiguration once the bit has been programmed during a power cycle. To safeguard against unpredictable events, Configuration bit changes resulting from individual cell level disruptions (such as ESD events) will cause a parity error and trigger a device Reset. This is seen by the user as a Configuration Mismatch (CM) Reset.

The data for the Configuration registers is derived from the FCW in program memory. When the CP0 bit is set, the source data for device configuration is also protected as a consequence.

| BRA   |                                                         | Unconditio                                                                               | Unconditional Branch                                |                                       |                   |  |  |  |  |

|-------|---------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------|-------------------|--|--|--|--|

| Synta | ax:                                                     | BRA n                                                                                    | BRA n                                               |                                       |                   |  |  |  |  |

| Oper  | ands:                                                   | -1024 ≤ n ≤                                                                              | 1023                                                |                                       |                   |  |  |  |  |

| Oper  | ation:                                                  | (PC) + 2 + 2                                                                             | $2n \rightarrow PC$                                 |                                       |                   |  |  |  |  |

| Statu | s Affected:                                             | None                                                                                     |                                                     |                                       |                   |  |  |  |  |

| Enco  | ding:                                                   | 1101                                                                                     | 0nnn                                                | nnnr                                  | n nnnn            |  |  |  |  |

| Desc  | ription:                                                | Add the 2's<br>the PC. Sin<br>incrementer<br>instruction,<br>PC + 2 + 2r<br>two-cycle in | ce the PC<br>d to fetch<br>the new a<br>n. This ins | will h<br>the ne<br>addres<br>tructio | ext<br>ss will be |  |  |  |  |

| Word  | ls:                                                     | 1                                                                                        |                                                     |                                       |                   |  |  |  |  |

| Cycle | es:                                                     | 2                                                                                        | 2                                                   |                                       |                   |  |  |  |  |

| QC    | ycle Activity:                                          |                                                                                          |                                                     |                                       |                   |  |  |  |  |

|       | Q1                                                      | Q2                                                                                       | Q3                                                  |                                       | Q4                |  |  |  |  |

|       | Decode                                                  | Read literal<br>'n'                                                                      | Proces<br>Data                                      | S                                     | Write to<br>PC    |  |  |  |  |

|       | No<br>operation                                         | No<br>operation                                                                          | No<br>operatio                                      | on                                    | No<br>operation   |  |  |  |  |

|       | nple:<br>Before Instruc<br>PC<br>After Instructio<br>PC | = ad                                                                                     |                                                     | ump<br>ERE)<br>ump)                   |                   |  |  |  |  |

| BSF               | Bit Set f                                                                                               |                                                                         |                                                             |                                                           |

|-------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------|

| Syntax:           | BSF f, b {                                                                                              | [,a}                                                                    |                                                             |                                                           |

| Operands:         | $0 \le f \le 255$<br>$0 \le b \le 7$<br>$a \in [0,1]$                                                   |                                                                         |                                                             |                                                           |

| Operation:        | $1 \rightarrow \text{f}$                                                                                |                                                                         |                                                             |                                                           |

| Status Affected:  | None                                                                                                    |                                                                         |                                                             |                                                           |

| Encoding:         | 1000                                                                                                    | bbba                                                                    | ffff                                                        | ffff                                                      |

| Description:      | Bit 'b' in reg                                                                                          | gister 'f' i                                                            | s set.                                                      |                                                           |

|                   | If 'a' is '0', th<br>If 'a' is '1', th<br>GPR bank                                                      | he BSR i                                                                | s used to                                                   |                                                           |

|                   | If 'a' is '0' a<br>set is enabl<br>in Indexed<br>mode wher<br>Section 27<br>Bit-Oriente<br>Literal Offs | led, this i<br>Literal O<br>never f ≤<br>7 <b>.2.3 "By</b><br>ed Instru | nstructio<br>ffset Add<br>95 (5Fh)<br>te-Orien<br>ictions i | n operates<br>Iressing<br>). See<br>Ited and<br>n Indexed |

| Words:            | 1                                                                                                       |                                                                         |                                                             |                                                           |

| Cycles:           | 1                                                                                                       |                                                                         |                                                             |                                                           |

| Q Cycle Activity: |                                                                                                         |                                                                         |                                                             |                                                           |

| Q1                | Q2                                                                                                      | Q                                                                       | 3                                                           | Q4                                                        |

| Decode            | Read<br>register 'f'                                                                                    | Proce<br>Dat                                                            |                                                             | Write<br>egister 'f'                                      |

|                   |                                                                                                         |                                                                         |                                                             |                                                           |

| Example:          | BSF F                                                                                                   | LAG_RE                                                                  | G, 7,                                                       | 1                                                         |

| IORI        | w                   | Inclusive                            | OR Liter     | al with | w |               |

|-------------|---------------------|--------------------------------------|--------------|---------|---|---------------|

| Synt        | ax:                 | IORLW k                              |              |         |   |               |

| Oper        | rands:              | $0 \le k \le 25$                     | 5            |         |   |               |

| Oper        | ration:             | (W) .OR. k                           | $x \to W$    |         |   |               |

| Statu       | is Affected:        | N, Z                                 |              |         |   |               |

| Enco        | oding:              | 0000                                 | 1001         | kkk     | k | kkkk          |

| Desc        | cription:           | The conter<br>eight-bit lit<br>in W. |              |         |   |               |

| Word        | ds:                 | 1                                    |              |         |   |               |

| Cycle       | es:                 | 1                                    |              |         |   |               |

| QC          | ycle Activity:      |                                      |              |         |   |               |

|             | Q1                  | Q2                                   | Q            | 3       |   | Q4            |

|             | Decode              | Read<br>literal 'k'                  | Proce<br>Dat |         | V | /rite to<br>W |

|             |                     |                                      |              |         |   |               |

| <u>Exar</u> | <u>nple:</u>        | IORLW                                | 35h          |         |   |               |

|             | Before Instruc<br>W | = 9Ah                                |              |         |   |               |

After Instruction W = BFh

| IORWF                                                                        | Inclusive C                                                                                                                                                                                                                                                                          | DR W wi                                                                                                                                         | th f    |                                 |  |  |  |  |  |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------|--|--|--|--|--|

| Syntax:                                                                      | IORWF f                                                                                                                                                                                                                                                                              | {,d {,a}}                                                                                                                                       |         |                                 |  |  |  |  |  |

| Operands:                                                                    | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                   | d ∈ [0,1]                                                                                                                                       |         |                                 |  |  |  |  |  |

| Operation:                                                                   | (W) .OR. (f)                                                                                                                                                                                                                                                                         | $) \rightarrow dest$                                                                                                                            |         |                                 |  |  |  |  |  |

| Status Affected:                                                             | N, Z                                                                                                                                                                                                                                                                                 |                                                                                                                                                 |         |                                 |  |  |  |  |  |

| Encoding:                                                                    | 0001                                                                                                                                                                                                                                                                                 | 00da                                                                                                                                            | fff     | f ffff                          |  |  |  |  |  |

| Description:                                                                 | ʻ0', the resu                                                                                                                                                                                                                                                                        | Inclusive OR W with register 'f'. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed back in register 'f' (default). |         |                                 |  |  |  |  |  |

|                                                                              |                                                                                                                                                                                                                                                                                      | he BSR i                                                                                                                                        | is used | k is selected.<br>to select the |  |  |  |  |  |

|                                                                              | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 27.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                                                                                                                                 |         |                                 |  |  |  |  |  |

| Words:                                                                       | 1                                                                                                                                                                                                                                                                                    |                                                                                                                                                 |         |                                 |  |  |  |  |  |

| Cycles:                                                                      | 1                                                                                                                                                                                                                                                                                    |                                                                                                                                                 |         |                                 |  |  |  |  |  |

| Q Cycle Activity:                                                            |                                                                                                                                                                                                                                                                                      |                                                                                                                                                 |         |                                 |  |  |  |  |  |

| Q1                                                                           | Q2                                                                                                                                                                                                                                                                                   | Q                                                                                                                                               | 3       | Q4                              |  |  |  |  |  |

| Decode                                                                       | Read<br>register 'f'                                                                                                                                                                                                                                                                 | Proce<br>Dat                                                                                                                                    |         | Write to destination            |  |  |  |  |  |

| Example:<br>Before Instruc<br>RESULT<br>W<br>After Instructio<br>RESULT<br>W | tion<br>= 13h<br>= 91h<br>on                                                                                                                                                                                                                                                         | ESULT,                                                                                                                                          | 0, 1    |                                 |  |  |  |  |  |

| TSTFSZ Test f, Skip if 0                                                                                                                                                                                                                                                           |                                                   |                              |                                                                                                                                                                     |                 |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| Synta                                                                                                                                                                                                                                                                              | ax:                                               | TSTFSZ f {                   | TSTFSZ f {,a}                                                                                                                                                       |                 |  |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                               | ands:                                             | 0 ≤ f ≤ 255<br>a ∈ [0,1]     | $0 \le f \le 255$                                                                                                                                                   |                 |  |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                               | ation:                                            | skip if f = 0                |                                                                                                                                                                     |                 |  |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                              | s Affected:                                       | None                         |                                                                                                                                                                     |                 |  |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                               | ding:                                             | 0110                         | 011a fff                                                                                                                                                            | f ffff          |  |  |  |  |  |

| Desc                                                                                                                                                                                                                                                                               | ription:                                          | during the c<br>is discarded | If 'f' = 0, the next instruction fetched<br>during the current instruction execution<br>is discarded and a NOP is executed,<br>making this a two-cycle instruction. |                 |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                    |                                                   |                              | he Access Bar<br>he BSR is use<br>(default).                                                                                                                        |                 |  |  |  |  |  |

| If 'a' is '0' and the extended instructio<br>set is enabled, this instruction operate<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 27.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                                   |                              |                                                                                                                                                                     |                 |  |  |  |  |  |

| Word                                                                                                                                                                                                                                                                               | s:                                                | 1                            | 1                                                                                                                                                                   |                 |  |  |  |  |  |

| Cycle                                                                                                                                                                                                                                                                              |                                                   |                              | vcles if skip an<br>a 2-word instru                                                                                                                                 |                 |  |  |  |  |  |

| QC                                                                                                                                                                                                                                                                                 | ycle Activity:                                    | 00                           | 00                                                                                                                                                                  | 04              |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                  | Q1<br>Decode                                      | Q2<br>Read                   | Q3<br>Process                                                                                                                                                       | Q4<br>No        |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                    | Debbuc                                            | register 'f'                 | Data                                                                                                                                                                | operation       |  |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                                              | ip:                                               | -                            |                                                                                                                                                                     |                 |  |  |  |  |  |

| i                                                                                                                                                                                                                                                                                  | Q1                                                | Q2                           | Q3                                                                                                                                                                  | Q4              |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                    | No                                                | No                           | No                                                                                                                                                                  | No              |  |  |  |  |  |

| lf ek                                                                                                                                                                                                                                                                              | operation                                         | operation                    | operation                                                                                                                                                           | operation       |  |  |  |  |  |

| 11 51                                                                                                                                                                                                                                                                              | Q1                                                | Q2                           | Q3                                                                                                                                                                  | Q4              |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                    | No                                                | No                           | No                                                                                                                                                                  | No              |  |  |  |  |  |