Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 48MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 34                                                                           |

| Program Memory Size        | 64KB (32K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 3.8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 44-QFN (8x8)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf46j11t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### EXAMPLE 4-1: ULTRA LOW-POWER WAKE-UP INITIALIZATION

```

//Configure a remappable output pin with interrupt capability

//for ULPWU function (RP21 => RD4/INT1 in this example)

RPOR21 = 13;// ULPWU function mapped to RP21/RD4

RPINR1 = 21;// INT1 mapped to RP21 (RD4)

//*********

//Charge the capacitor on RAO

TRISAbits.TRISA0 = 0;

LATAbits.LATA0 = 1;

for(i = 0; i < 10000; i++) Nop();</pre>

//Stop Charging the capacitor on RAO

TRISAbits.TRISA0 = 1;

//Enable the Ultra Low Power Wakeup module

//and allow capacitor discharge

WDTCONbits.ULPEN = 1;

WDTCONbits.ULPSINK = 1;

//For Sleep, Enable Interrupt for ULPW.

INTCON3bits.INT1IF = 0;

INTCON3bits.INT1IE = 1;

//**************

//Configure Sleep Mode

//*******************

//For Sleep

OSCCONbits.IDLEN = 0;

//For Deep Sleep

OSCCONDits.IDLEN = 0i// enable deep sleep

DSCONHbits.DSEN = 1;// Note: must be set just before executing Sleep();

/ / * * * * * * * * * * * * * * * *

//Enter Sleep Mode

/ / * * * * * * * * * * * * * * * *

Sleep();

// for sleep, execution will resume here

// for deep sleep, execution will restart at reset vector (use WDTCONbits.DS to detect)

```

#### 10.7.6 PERIPHERAL PIN SELECT REGISTERS

The PIC18F46J11 family of devices implements a total of 37 registers for remappable peripheral configuration of 44-pin devices. The 28-pin devices have 31 registers for remappable peripheral configuration.

**Note:** Input and output register values can only be changed if PPS<IOLOCK> = 0. See Example 10-7 for a specific command sequence.

### REGISTER 10-5: PPSCON: PERIPHERAL PIN SELECT INPUT REGISTER 0 (BANKED EFFh)<sup>(1)</sup>

| U-0   |   |  | U-0 | U-0 | U-0 | U-0 | R/W-0  |  |  |

|-------|---|--|-----|-----|-----|-----|--------|--|--|

| _     | — |  |     | —   | —   | _   | IOLOCK |  |  |

| bit 7 |   |  |     |     |     |     |        |  |  |

| Legend:           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

### bit 7-1 Unimplemented: Read as '0'

bit 0

IOLOCK: I/O Lock Enable bit

1 = I/O lock active, RPORx and RPINRx registers are write-protected

0 = I/O lock not active, pin configurations can be changed

Note 1: Register values can only be changed if PPSCON<IOLOCK> = 0.

### REGISTER 11-7: PMSTATH: PARALLEL PORT STATUS REGISTER HIGH BYTE (BANKED F55h)<sup>(1)</sup>

| R-0       R/W-0       U-0       U-0       R-0       R-0       R-0       R-0         IBF       IBOV       -       -       IB3F       IB2F       IB1F       IB0F         bit 7       IBF       IBOV       -       -       IB3F       IB2F       IB1F       IB0F         bit 7       IBer       IBOV       -       -       IB3F       IB2F       IB1F       IB0F         Legend:       R       Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - |                  |                                                                                                                                                   |                                                                                                                     |                                                                          |                   |                  | •               |      |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------|------------------|-----------------|------|--|--|--|--|--|--|--|--|

| bit 7       bit         Legend:       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7       IBF: Input Buffer Full Status bit       1 = All writable input buffer registers are full       0 = Some or all of the writable input buffer registers are empty         bit 6       IBOV: Input Buffer Overflow Status bit       1 = A write attempt to a full input byte register occurred (must be cleared in software)       0 = No overflow occurred         bit 5-4       Unimplemented: Read as '0'       bits       1 = Input Buffer x Status Full bits         1 = Input buffer contains data that has not been read (reading buffer will clear this bit)       1 = Input buffer contains data that has not been read (reading buffer will clear this bit)                                                                                                                                      | R-0              | R/W-0                                                                                                                                             | U-0                                                                                                                 | U-0                                                                      | R-0               | R-0              | R-0             | R-0  |  |  |  |  |  |  |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7       IBF: Input Buffer Full Status bit       1 = All writable input buffer registers are full       0 = Some or all of the writable input buffer registers are empty         bit 6       IBOV: Input Buffer Overflow Status bit       1 = A write attempt to a full input byte register occurred (must be cleared in software)         0 = No overflow occurred       0 = No overflow occurred         bit 5-4       Unimplemented: Read as '0'         bit 3-0       IB3F:IBOF: Input Buffer x Status Full bits         1 = Input buffer contains data that has not been read (reading buffer will clear this bit)                                                                                                                                                                                         | IBF              | IBOV                                                                                                                                              |                                                                                                                     | _                                                                        | IB3F              | IB2F             | IB1F            | IB0F |  |  |  |  |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7       IBF: Input Buffer Full Status bit       1 = All writable input buffer registers are full       0 = Some or all of the writable input buffer registers are empty         bit 6       IBOV: Input Buffer Overflow Status bit       1 = A write attempt to a full input byte register occurred (must be cleared in software)         0 = No overflow occurred       0 = No overflow occurred         bit 5-4       Unimplemented: Read as '0'         bit 3-0       IB3F:IBOF: Input Buffer x Status Full bits         1 = Input buffer contains data that has not been read (reading buffer will clear this bit)                                                                                                                                                                                                         | bit 7            | .7                                                                                                                                                |                                                                                                                     |                                                                          |                   |                  |                 |      |  |  |  |  |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7       IBF: Input Buffer Full Status bit       1 = All writable input buffer registers are full       0 = Some or all of the writable input buffer registers are empty         bit 6       IBOV: Input Buffer Overflow Status bit       1 = A write attempt to a full input byte register occurred (must be cleared in software)         0 = No overflow occurred       0 = No overflow occurred       IB3F:IBOF: Input Buffer x Status Full bits         1 = Input buffer contains data that has not been read (reading buffer will clear this bit)       1                                                                                                                                                                                                                                                                  |                  |                                                                                                                                                   |                                                                                                                     |                                                                          |                   |                  |                 |      |  |  |  |  |  |  |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7       IBF: Input Buffer Full Status bit       1 = All writable input buffer registers are full       0 = Some or all of the writable input buffer registers are empty         bit 6       IBOV: Input Buffer Overflow Status bit       1 = A write attempt to a full input byte register occurred (must be cleared in software)         0 = No overflow occurred       0 = No overflow occurred         bit 3-0       IB3F:IBOF: Input Buffer x Status Full bits         1 = Input buffer contains data that has not been read (reading buffer will clear this bit)                                                                                                                                                                                                                                                                                                                                                   | Legend:          |                                                                                                                                                   |                                                                                                                     |                                                                          |                   |                  |                 |      |  |  |  |  |  |  |  |  |

| <ul> <li>bit 7 IBF: Input Buffer Full Status bit</li> <li>1 = All writable input buffer registers are full</li> <li>0 = Some or all of the writable input buffer registers are empty</li> <li>bit 6 IBOV: Input Buffer Overflow Status bit</li> <li>1 = A write attempt to a full input byte register occurred (must be cleared in software)</li> <li>0 = No overflow occurred</li> <li>bit 5-4 Unimplemented: Read as '0'</li> <li>bit 3-0 IB3F:IB0F: Input Buffer x Status Full bits</li> <li>1 = Input buffer contains data that has not been read (reading buffer will clear this bit)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                            | R = Readab       | le bit                                                                                                                                            | W = Writable I                                                                                                      | bit                                                                      | U = Unimplem      | nented bit, read | d as '0'        |      |  |  |  |  |  |  |  |  |

| <ul> <li>1 = All writable input buffer registers are full</li> <li>0 = Some or all of the writable input buffer registers are empty</li> <li>bit 6</li> <li>IBOV: Input Buffer Overflow Status bit</li> <li>1 = A write attempt to a full input byte register occurred (must be cleared in software)</li> <li>0 = No overflow occurred</li> <li>bit 5-4</li> <li>Unimplemented: Read as '0'</li> <li>bit 3-0</li> <li>IB3F:IB0F: Input Buffer x Status Full bits</li> <li>1 = Input buffer contains data that has not been read (reading buffer will clear this bit)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -n = Value a     | t POR                                                                                                                                             | '1' = Bit is set                                                                                                    |                                                                          | '0' = Bit is clea | ared             | x = Bit is unkr | nown |  |  |  |  |  |  |  |  |

| 1 = Input buffer contains data that has not been read (reading buffer will clear this bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 6<br>bit 5-4 | <ol> <li>1 = All writab</li> <li>0 = Some or</li> <li>IBOV: Input E</li> <li>1 = A write a</li> <li>0 = No overfi</li> <li>Unimplement</li> </ol> | le input buffer r<br>all of the writab<br>Buffer Overflow<br>ttempt to a full i<br>low occurred<br>tted: Read as '0 | egisters are fu<br>le input buffer<br>Status bit<br>nput byte regis<br>, | registers are er  |                  | d in software)  |      |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | dit 3-0          | 1 = Input buf                                                                                                                                     | fer contains dat                                                                                                    | a that has not                                                           | •                 | ding buffer will | clear this bit) |      |  |  |  |  |  |  |  |  |

Note 1: This register is only available in 44-pin devices.

## REGISTER 11-8: PMSTATL: PARALLEL PORT STATUS REGISTER LOW BYTE (BANKED F54h)<sup>(1)</sup>

| R-1   | R/W-0 | U-0 | U-0 | R-1  | R-1  | R-1  | R-1   |

|-------|-------|-----|-----|------|------|------|-------|

| OBE   | OBUF  | —   | —   | OB3E | OB2E | OB1E | OB0E  |

| bit 7 |       |     |     |      |      |      | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7        | <b>OBE:</b> Output Buffer Empty Status bit<br>1 = All readable output buffer registers are empty                                            |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| <b>h</b> # C | 0 = Some or all of the readable output buffer registers are full                                                                            |

| bit 6        | <b>OBUF:</b> Output Buffer Underflow Status bit                                                                                             |

|              | <ul> <li>1 = A read occurred from an empty output byte register (must be cleared in software)</li> <li>0 = No underflow occurred</li> </ul> |

| bit 5-4      | Unimplemented: Read as '0'                                                                                                                  |

| bit 3-0      | OB3E:OB0E: Output Buffer x Status Empty bits                                                                                                |

|              | 1 = Output buffer is empty (writing data to the buffer will clear this bit)                                                                 |

|              | 0 = Output buffer contains data that has not been transmitted                                                                               |

|              |                                                                                                                                             |

Note 1: This register is only available in 44-pin devices.

#### 12.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module. The prescaler is not directly readable or writable. Its value is set by the PSA and T0PS<2:0> bits (T0CON<3:0>), which determine the prescaler assignment and prescale ratio.

Clearing the PSA bit assigns the prescaler to the Timer0 module. When it is assigned, prescale values from 1:2 through 1:256 in power-of-2 increments are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF TMR0, MOVWF TMR0, BSF TMR0, etc.) clear the prescaler count.

| Note: | Writing to TMR0 when the prescaler is       |

|-------|---------------------------------------------|

|       | assigned to Timer0 will clear the prescaler |

|       | count but will not change the prescaler     |

|       | assignment.                                 |

#### 12.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control and can be changed "on-the-fly" during program execution.

### 12.4 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h in 8-bit mode, or from FFFFh to 0000h in 16-bit mode. This overflow sets the TMR0IF flag bit. The interrupt can be masked by clearing the TMR0IE bit (INTCON<5>). Before re-enabling the interrupt, the TMR0IF bit must be cleared in software by the Interrupt Service Routine (ISR).

Since Timer0 is shut down in Sleep mode, the TMR0 interrupt cannot awaken the processor from Sleep.

| Name   | Bit 7                                                          | Bit 6         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Values<br>on Page: |  |

|--------|----------------------------------------------------------------|---------------|-------|-------|-------|-------|-------|-------|-----------------------------|--|

| TMR0L  | Timer0 Reg                                                     | ister Low By  | te    |       |       |       |       |       | 91                          |  |

| TMR0H  | Timer0 Reg                                                     | ister High By | /te   |       |       |       |       |       | 91                          |  |

| INTCON | NTCON GIE/GIEH PEIE/GIEL TMROIE INTOIE RBIE TMROIF INTOIF RBIF |               |       |       |       |       |       |       |                             |  |

| T0CON  | ON TMROON T08BIT TOCS TOSE PSA T0PS2 T0PS1 T0PS0               |               |       |       |       |       |       |       |                             |  |

TABLE 12-1:

REGISTERS ASSOCIATED WITH TIMER0

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by Timer0.

#### REGISTER 17-4: ALRMCFG: ALARM CONFIGURATION REGISTER (ACCESS F91h)

| R/W-0         | R/W-0                                          | R/W-0                                 | R/W-0         | R/W-0             | R/W-0             | R/W-0            | R/W-0       |  |  |  |  |

|---------------|------------------------------------------------|---------------------------------------|---------------|-------------------|-------------------|------------------|-------------|--|--|--|--|

| ALRMEN        | CHIME                                          | AMASK3                                | AMASK2        | AMASK1            | AMASK0            | ALRMPTR1         | ALRMPTR0    |  |  |  |  |

| bit 7         | ·                                              | ł                                     |               |                   |                   |                  | bit 0       |  |  |  |  |

|               |                                                |                                       |               |                   |                   |                  |             |  |  |  |  |

| Legend:       |                                                |                                       |               |                   |                   |                  |             |  |  |  |  |

| R = Readabl   | e bit                                          | W = Writable                          | bit           | U = Unimpler      | nented bit, read  | d as '0'         |             |  |  |  |  |

| -n = Value at | POR                                            | '1' = Bit is set                      |               | '0' = Bit is cle  | ared              | x = Bit is unki  | nown        |  |  |  |  |

| L:1 7         |                                                | lawa Enable bit                       |               |                   |                   |                  |             |  |  |  |  |

| bit 7         |                                                | larm Enable bit                       | doutomotical  | ly offer an eler  | n overtweene      | or ADDT 27:05    |             |  |  |  |  |

|               |                                                | enabled (cleare                       | automatical   | iy alter an alarr | n event whenev    | /el ARP1<7.0>    | - 0000 0000 |  |  |  |  |

|               | 0 = Alarm is                                   | ,                                     |               |                   |                   |                  |             |  |  |  |  |

| bit 6         | CHIME: Chir                                    | me Enable bit                         |               |                   |                   |                  |             |  |  |  |  |

|               | 1 = Chime is                                   | s enabled; ALRI                       | MRPT<7:0> b   | its are allowed   | to roll over from | m 00h to FFh     |             |  |  |  |  |

|               | 0 = Chime is                                   | s disabled; ALR                       | MRPT<7:0> b   | its stop once tl  | ney reach 00h     |                  |             |  |  |  |  |

| bit 5-2       | AMASK<3:0                                      | >: Alarm Mask                         | Configuration | bits              |                   |                  |             |  |  |  |  |

|               | 0000 = Every half second                       |                                       |               |                   |                   |                  |             |  |  |  |  |

|               | 0001 = Every second                            |                                       |               |                   |                   |                  |             |  |  |  |  |

|               | 0010 = Every 10 seconds<br>0011 = Every minute |                                       |               |                   |                   |                  |             |  |  |  |  |

|               | 0011 = Every minute<br>0100 = Every 10 minutes |                                       |               |                   |                   |                  |             |  |  |  |  |

|               | 0101 = Eve                                     |                                       |               |                   |                   |                  |             |  |  |  |  |

|               | 0110 = Ond                                     | •                                     |               |                   |                   |                  |             |  |  |  |  |

|               | 0111 = Ond                                     | ce a week                             |               |                   |                   |                  |             |  |  |  |  |

|               | 1000 = Onc                                     |                                       |               |                   | a a th            |                  |             |  |  |  |  |

|               |                                                | ce a year (excep<br>served – do not i |               | ured for Februa   | ary 29", once e   | every four years | 6)          |  |  |  |  |

|               |                                                | served – do not i                     |               |                   |                   |                  |             |  |  |  |  |

| bit 1-0       |                                                | 1:0>: Alarm Val                       |               | indow Pointer     | hits              |                  |             |  |  |  |  |

|               |                                                | e corresponding                       | -             |                   |                   | AI RMVAI H ar    | d ALRMVALL  |  |  |  |  |

|               |                                                | e ALRMPTR<1:                          |               |                   |                   |                  |             |  |  |  |  |

|               | ʻ00'.                                          |                                       |               |                   | ,<br>,            |                  |             |  |  |  |  |

|               | <u>ALRMVALH</u>                                | <u>&lt;15:8&gt;:</u>                  |               |                   |                   |                  |             |  |  |  |  |

|               | 00 = ALRMMIN                                   |                                       |               |                   |                   |                  |             |  |  |  |  |

|               | 01 = ALRMWD                                    |                                       |               |                   |                   |                  |             |  |  |  |  |

|               | 10 = ALRMMNTH<br>11 = Unimplemented            |                                       |               |                   |                   |                  |             |  |  |  |  |

|               | -                                              |                                       |               |                   |                   |                  |             |  |  |  |  |

|               | <u>ALRMVALL&lt;</u><br>00 = ALRMS              |                                       |               |                   |                   |                  |             |  |  |  |  |

|               | 01 = ALRMH                                     |                                       |               |                   |                   |                  |             |  |  |  |  |

|               |                                                |                                       |               |                   |                   |                  |             |  |  |  |  |

|               | 10 = ALRME                                     |                                       |               |                   |                   |                  |             |  |  |  |  |

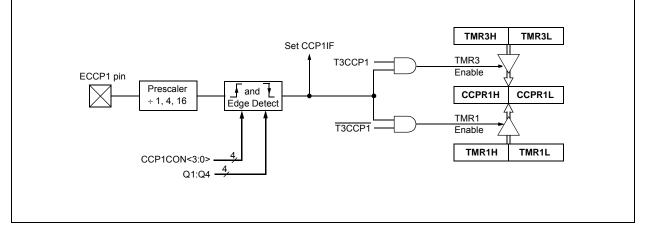

### 18.2.4 ECCP PRESCALER

There are four prescaler settings in Capture mode; they are specified as part of the operating mode selected by the mode select bits (CCPxM<3:0>). Whenever the ECCP module is turned off, or Capture mode is disabled, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 18-1 provides the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 18-1: CHANGING BETWEEN CAPTURE PRESCALERS

|       |         |   | Turn CCP module off<br>Load WREG with the |

|-------|---------|---|-------------------------------------------|

|       |         | ; | new prescaler mode                        |

|       |         | ; | value and CCP ON                          |

| MOVWF | CCP1CON | ; | Load CCP1CON with                         |

|       |         | ; | this value                                |

|       |         |   |                                           |

|             |                       | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |                       |                  |                             |  |  |  |

|-------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------------|-----------------------------|--|--|--|

| BAUD        | Fosc = 40.000 MHz     |                               |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fos                   | Fosc = 8.000 MHz |                             |  |  |  |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |  |  |

| 0.3         | _                     |                               |                             |                       |            |                             |                       |            |                             | _                     | _                | _                           |  |  |  |

| 1.2         | —                     | —                             | —                           | 1.221                 | 1.73       | 255                         | 1.202                 | 0.16       | 129                         | 1.201                 | -0.16            | 103                         |  |  |  |

| 2.4         | 2.441                 | 1.73                          | 255                         | 2.404                 | 0.16       | 129                         | 2.404                 | 0.16       | 64                          | 2.403                 | -0.16            | 51                          |  |  |  |

| 9.6         | 9.615                 | 0.16                          | 64                          | 9.766                 | 1.73       | 31                          | 9.766                 | 1.73       | 15                          | 9.615                 | -0.16            | 12                          |  |  |  |

| 19.2        | 19.531                | 1.73                          | 31                          | 19.531                | 1.73       | 15                          | 19.531                | 1.73       | 7                           | _                     | _                | _                           |  |  |  |

| 57.6        | 56.818                | -1.36                         | 10                          | 62.500                | 8.51       | 4                           | 52.083                | -9.58      | 2                           | —                     | _                | _                           |  |  |  |

| 115.2       | 125.000               | 8.51                          | 4                           | 104.167               | -9.58      | 2                           | 78.125                | -32.18     | 1                           | —                     | _                | _                           |  |  |  |

#### TABLE 20-3: BAUD RATES FOR ASYNCHRONOUS MODES

|              |                       | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc = 4.000 MHz      |                               |                             | Fosc = 2.000 MHz      |            |                             | Fosc = 1.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                 | 0.16                          | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16      | 51                          |

| 1.2          | 1.202                 | 0.16                          | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16      | 12                          |

| 2.4          | 2.404                 | 0.16                          | 25                          | 2.403                 | -0.16      | 12                          | —                     | _          | _                           |

| 9.6          | 8.929                 | -6.99                         | 6                           | —                     | _          | _                           | —                     | _          | _                           |

| 19.2         | 20.833                | 8.51                          | 2                           | —                     | _          | _                           | —                     | _          | _                           |

| 57.6         | 62.500                | 8.51                          | 0                           | —                     | _          | _                           | —                     | _          | _                           |

| 115.2        | 62.500                | -45.75                        | 0                           | _                     | _          | —                           | _                     |            | —                           |

|              |                                    | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                       |                   |                             |                       |                  |                             |                       |            |                             |

|--------------|------------------------------------|-------------------------------|-----------------------------|-----------------------|-------------------|-----------------------------|-----------------------|------------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc = 40.000 MHz Fosc = 20.000 MH |                               |                             | ) MHz                 | Fosc = 10.000 MHz |                             |                       | Fosc = 8.000 MHz |                             |                       |            |                             |

| (K)          | Actual<br>Rate<br>(K)              | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          |                                    | _                             | _                           | _                     | _                 | _                           |                       |                  | _                           | _                     | _          | _                           |

| 1.2          | —                                  | —                             | —                           | —                     | —                 | —                           | —                     | —                | —                           | —                     | —          | —                           |

| 2.4          | —                                  | _                             | _                           | —                     | _                 | _                           | 2.441                 | 1.73             | 255                         | 2.403                 | -0.16      | 207                         |

| 9.6          | 9.766                              | 1.73                          | 255                         | 9.615                 | 0.16              | 129                         | 9.615                 | 0.16             | 64                          | 9615.                 | -0.16      | 51                          |

| 19.2         | 19.231                             | 0.16                          | 129                         | 19.231                | 0.16              | 64                          | 19.531                | 1.73             | 31                          | 19.230                | -0.16      | 25                          |

| 57.6         | 58.140                             | 0.94                          | 42                          | 56.818                | -1.36             | 21                          | 56.818                | -1.36            | 10                          | 55.555                | 3.55       | 8                           |

| 115.2        | 113.636                            | -1.36                         | 21                          | 113.636               | -1.36             | 10                          | 125.000               | 8.51             | 4                           | —                     | _          | _                           |

|              |                       | <b>SYNC</b> = 0, <b>BRGH</b> = 1, <b>BRG16</b> = 0 |                             |                       |            |                             |                       |            |                             |

|--------------|-----------------------|----------------------------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc = 4.000 MHz      |                                                    |                             | Fosc = 2.000 MHz      |            |                             | Fosc = 1.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                                         | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | _                     |                                                    | _                           | _                     |            | _                           | 0.300                 | -0.16      | 207                         |

| 1.2          | 1.202                 | 0.16                                               | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |

| 2.4          | 2.404                 | 0.16                                               | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |

| 9.6          | 9.615                 | 0.16                                               | 25                          | 9.615                 | -0.16      | 12                          | _                     | _          | _                           |

| 19.2         | 19.231                | 0.16                                               | 12                          | _                     | _          | _                           | _                     | _          | _                           |

| 57.6         | 62.500                | 8.51                                               | 3                           | —                     | _          | _                           | —                     | _          | _                           |

| 115.2        | 125.000               | 8.51                                               | 1                           | _                     | _          | _                           | _                     | _          | _                           |

© 2011 Microchip Technology Inc.

| R/W-0         | R/W-0                                                                                                                                                                        | R/W-0                                            | R/W-0          | R/W-0             | R/W-0            | R/W-x           | R/W-x    |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------|-------------------|------------------|-----------------|----------|

| EDG2POL       | EDG2SEL1                                                                                                                                                                     | EDG2SEL0                                         | EDG1POL        | EDG1SEL1          | EDG1SEL0         | EDG2STAT        | EDG1STAT |

| bit 7         | •                                                                                                                                                                            | •                                                |                | •                 | •                | •               | bit C    |

|               |                                                                                                                                                                              |                                                  |                |                   |                  |                 |          |

| Legend:       |                                                                                                                                                                              |                                                  |                |                   |                  |                 |          |

| R = Readable  | e bit                                                                                                                                                                        | W = Writable                                     | bit            | U = Unimplen      | nented bit, read | l as '0'        |          |

| -n = Value at | POR                                                                                                                                                                          | '1' = Bit is set                                 |                | '0' = Bit is clea | ared             | x = Bit is unkr | iown     |

| bit 7         | EDG2POL: E                                                                                                                                                                   | dge 2 Polarity                                   | Select bit     |                   |                  |                 |          |

|               | <ul> <li>1 = Edge 2 programmed for a positive edge response</li> <li>0 = Edge 2 programmed for a negative edge response</li> </ul>                                           |                                                  |                |                   |                  |                 |          |

| bit 6-5       | EDG2SEL<1:0>: Edge 2 Source Select bits<br>11 = CTED1 pin<br>10 = CTED2 pin<br>01 = ECCP1 Special Event Trigger<br>00 = ECCP2 Special Event Trigger                          |                                                  |                |                   |                  |                 |          |

| bit 4         | 1 = Edge 1 p                                                                                                                                                                 | dge 1 Polarity<br>rogrammed for<br>rogrammed for | a positive edg |                   |                  |                 |          |

| bit 3-2       | EDG1SEL<1:0>: Edge 1 Source Select bits<br>11 = CTED1 pin<br>10 = CTED2 pin<br>01 = ECCP1 Special Event Trigger<br>00 = ECCP2 Special Event Trigger                          |                                                  |                |                   |                  |                 |          |

| bit 1         | EDG2STAT: Edge 2 Status bit<br>1 = Edge 2 event has occurred<br>0 = Edge 2 event has not occurred                                                                            |                                                  |                |                   |                  |                 |          |

| bit 0         | <ul> <li>0 = Edge 2 event has not occurred</li> <li>EDG1STAT: Edge 1 Status bit</li> <li>1 = Edge 1 event has occurred</li> <li>0 = Edge 1 event has not occurred</li> </ul> |                                                  |                |                   |                  |                 |          |

#### REGISTER 26-2: CONFIG1H: CONFIGURATION REGISTER 1 HIGH (BYTE ADDRESS 300001h)

| U-1     | U-1 | U-1 | U-1 | U-0 | R/WO-1 | U-0 | U-0   |

|---------|-----|-----|-----|-----|--------|-----|-------|

| —       | —   | —   | —   | —   | CP0    | —   | —     |

| bit 7   |     |     |     | •   |        |     | bit 0 |

|         |     |     |     |     |        |     |       |

| Legend: |     |     |     |     |        |     |       |

| R = Readable bit    | WO = Write-Once bit | U = Unimplemented bit, read | d as '0'           |

|---------------------|---------------------|-----------------------------|--------------------|

| -n = Value at Reset | '1' = Bit is set    | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-4 | <b>Unimplemented:</b> Program the corresponding Flash Configuration bit to '1' |

|---------|--------------------------------------------------------------------------------|

|         | omplemented. I regram the conceptionality hash configuration bit to 1          |

| bit 3 | Unimplemented: Maintain as '0' |

|-------|--------------------------------|

|-------|--------------------------------|

```

bit 2 CP0: Code Protection bit

```

- 1 = Program memory is not code-protected

- 0 = Program memory is code-protected

- bit 1-0 Unimplemented: Maintain as '0'

# 26.7 In-Circuit Serial Programming (ICSP)

PIC18F46J11 family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

### 26.8 In-Circuit Debugger

When the  $\overline{\text{DEBUG}}$  Configuration bit is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some resources are not available for general use.

Table 26-4 lists the resources required by the background debugger.

| I/O pins: | RB6, RB7                |

|-----------|-------------------------|

| Stack:    | TOSx registers reserved |

### 27.0 INSTRUCTION SET SUMMARY

The PIC18F46J11 family of devices incorporates the standard set of 75 PIC18 core instructions, and an extended set of eight new instructions for the optimization of code that is recursive or that utilizes a software stack. The extended set is discussed later in this section.

### 27.1 Standard Instruction Set

The standard PIC18 instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from these PIC MCU instruction sets. Most instructions are a single program memory word (16 bits), but there are four instructions that require two program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal operations

- Control operations

The PIC18 instruction set summary in Table 27-2 lists the **byte-oriented**, **bit-oriented**, **literal** and **control** operations.

Table 27-1 provides the opcode field descriptions.

Most Byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator, 'f', specifies which file register is to be used by the instruction. The destination designator, 'd', specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the WREG register. If 'd' is '1', the result is placed in the file register specified in the instruction.

All **Bit-oriented** instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator 'b' selects the number of the bit affected by the operation, while the file register designator, 'f', represents the number of the file in which the bit is located.

The **Literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **Control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the CALL or RETURN instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '---')

All instructions are a single word, except for four double-word instructions. These instructions were made double-word to contain the required information in 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the Program Counter (PC) is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 27-1 provides the general formats that the instructions can have. All examples use the convention 'nnh' to represent a hexadecimal number.

The instruction set summary, provided in Table 27-2, lists the standard instructions recognized by the Microchip MPASM<sup>™</sup> Assembler.

Section 27.1.1 "Standard Instruction Set" provides a description of each instruction.

| <b>TABLE 27-2</b> : | PIC18F46J11 FAMILY INSTRUCTION SET |

|---------------------|------------------------------------|

|                     |                                    |

| Mnemonic,<br>Operands |                                 | Description                              | 16-Bit Instruction Word |      | Status | Natas |      |                 |            |

|-----------------------|---------------------------------|------------------------------------------|-------------------------|------|--------|-------|------|-----------------|------------|

|                       |                                 | Description                              | Cycles                  | MSb  |        |       | LSb  | Affected        | Notes      |

| BYTE-ORIE             | BYTE-ORIENTED OPERATIONS        |                                          |                         |      |        |       |      |                 |            |

| ADDWF                 | f, d, a                         | Add WREG and f                           | 1                       | 0010 | 01da   | ffff  | ffff | C, DC, Z, OV, N | 1, 2       |

| ADDWFC                | f, d, a                         | Add WREG and Carry bit to f              | 1                       | 0010 | 00da   | ffff  | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF                 | f, d, a                         | AND WREG with f                          | 1                       | 0001 | 01da   | ffff  | ffff | Z, N            | 1,2        |

| CLRF                  | f, a                            | Clear f                                  | 1                       | 0110 | 101a   | ffff  | ffff | Z               | 2          |

| COMF                  | f, d, a                         | Complement f                             | 1                       | 0001 | 11da   | ffff  | ffff | Z, N            | 1, 2       |

| CPFSEQ                | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3)              | 0110 | 001a   | ffff  | ffff | None            | 4          |

| CPFSGT                | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3)              | 0110 | 010a   | ffff  | ffff | None            | 4          |

| CPFSLT                | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3)              | 0110 | 000a   | ffff  | ffff | None            | 1, 2       |

| DECF                  | f, d, a                         | Decrement f                              | 1                       | 0000 | 01da   | ffff  | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ                | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3)              | 0010 | 11da   | ffff  | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ                | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3)              | 0100 | 11da   | ffff  | ffff | None            | 1, 2       |

| INCF                  | f, d, a                         | Increment f                              | 1                       | 0010 | 10da   | ffff  | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ                | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3)              | 0011 | 11da   | ffff  | ffff | None            | 4          |

| INFSNZ                | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3)              | 0100 | 10da   | ffff  | ffff | None            | 1, 2       |

| IORWF                 | f, d, a                         | Inclusive OR WREG with f                 | 1                       | 0001 | 00da   | ffff  | ffff | Z, N            | 1, 2       |

| MOVF                  | f, d, a                         | Move f                                   | 1                       | 0101 | 00da   | ffff  | ffff | Z, N            | 1          |

| MOVFF                 | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2                       | 1100 | ffff   | ffff  | ffff | None            |            |

|                       |                                 | f <sub>d</sub> (destination) 2nd word    |                         | 1111 | ffff   | ffff  | ffff |                 |            |

| MOVWF                 | f, a                            | Move WREG to f                           | 1                       | 0110 | 111a   | ffff  | ffff | None            |            |

| MULWF                 | f, a                            | Multiply WREG with f                     | 1                       | 0000 | 001a   | ffff  | ffff | None            | 1, 2       |

| NEGF                  | f, a                            | Negate f                                 | 1                       | 0110 | 110a   | ffff  | ffff | C, DC, Z, OV, N |            |

| RLCF                  | f, d, a                         | Rotate Left f through Carry              | 1                       | 0011 | 01da   | ffff  | ffff | C, Z, N         | 1, 2       |

| RLNCF                 | f, d, a                         | Rotate Left f (No Carry)                 | 1                       | 0100 | 01da   | ffff  | ffff | Z, N            |            |

| RRCF                  | f, d, a                         | Rotate Right f through Carry             | 1                       | 0011 | 00da   | ffff  | ffff | C, Z, N         |            |

| RRNCF                 | f, d, a                         | Rotate Right f (No Carry)                | 1                       | 0100 | 00da   | ffff  | ffff | Z, N            |            |

| SETF                  | f, a                            | Set f                                    | 1                       | 0110 | 100a   | ffff  | ffff | None            | 1, 2       |

| SUBFWB                | f, d, a                         | Subtract f from WREG with<br>Borrow      | 1                       | 0101 | 01da   | ffff  | ffff | C, DC, Z, OV, N |            |

| SUBWF                 | f, d, a                         | Subtract WREG from f                     | 1                       | 0101 | 11da   | ffff  | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWFB                | f, d, a                         | Subtract WREG from f with                | 1                       | 0101 | 10da   | ffff  | ffff | C, DC, Z, OV, N |            |

|                       |                                 | Borrow                                   |                         |      |        |       |      |                 |            |

| SWAPF                 | f, d, a                         | Swap Nibbles in f                        | 1                       | 0011 | 10da   | ffff  | ffff | None            | 4          |

| TSTFSZ                | f, a                            | Test f, Skip if 0                        | 1 (2 or 3)              | 0110 | 011a   | ffff  | ffff | None            | 1, 2       |

| XORWF                 | f, d, a                         | Exclusive OR WREG with f                 | 1                       | 0001 | 10da   | ffff  | ffff | Z, N            |            |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

3: If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

| BNO                                                                                                                                | v               | Branch if N                                               | Branch if Not Overflow                                                                                                                                                                                                     |            |                |  |  |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------|--|--|

| Synta                                                                                                                              | ax:             | BNOV n                                                    | BNOV n                                                                                                                                                                                                                     |            |                |  |  |

| Oper                                                                                                                               | ands:           | $-128 \le n \le 1$                                        | 27                                                                                                                                                                                                                         |            |                |  |  |

| Oper                                                                                                                               | ation:          | if Overflow<br>(PC) + 2 + 2                               | ,                                                                                                                                                                                                                          |            |                |  |  |

| Statu                                                                                                                              | s Affected:     | None                                                      |                                                                                                                                                                                                                            |            |                |  |  |

| Enco                                                                                                                               | ding:           | 1110                                                      | 0101                                                                                                                                                                                                                       | nnnn       | nnnn           |  |  |

| Desc                                                                                                                               | ription:        | If the Overfiprogram with                                 |                                                                                                                                                                                                                            | 0', then t | the            |  |  |

|                                                                                                                                    |                 | added to th<br>have incren<br>instruction,<br>PC + 2 + 2r | The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |            |                |  |  |

| Word                                                                                                                               | ls:             | 1                                                         | 1                                                                                                                                                                                                                          |            |                |  |  |

| Cycle                                                                                                                              | es:             | 1(2)                                                      |                                                                                                                                                                                                                            |            |                |  |  |

| Q C<br>If Ju                                                                                                                       | ycle Activity:  |                                                           |                                                                                                                                                                                                                            |            |                |  |  |

|                                                                                                                                    | Q1              | Q2                                                        | Q3                                                                                                                                                                                                                         |            | Q4             |  |  |

|                                                                                                                                    | Decode          | Read literal<br>'n'                                       | Proces:<br>Data                                                                                                                                                                                                            | s V        | Vrite to<br>PC |  |  |

|                                                                                                                                    | No<br>operation | No<br>operation                                           | No<br>operatio                                                                                                                                                                                                             | n op       | No<br>peration |  |  |

| lf No                                                                                                                              | o Jump:         |                                                           |                                                                                                                                                                                                                            |            |                |  |  |

|                                                                                                                                    | Q1              | Q2                                                        | Q3                                                                                                                                                                                                                         |            | Q4             |  |  |

|                                                                                                                                    | Decode          | Read literal<br>'n'                                       | Proces:<br>Data                                                                                                                                                                                                            | -          | No<br>peration |  |  |

| Example: HERE BNOV Jump<br>Before Instruction                                                                                      |                 |                                                           |                                                                                                                                                                                                                            |            |                |  |  |

| PC = address (HERE)<br>After Instruction<br>If Overflow = 0;<br>PC = address (Jump)<br>If Overflow = 1;<br>PC = address (HERE + 2) |                 |                                                           |                                                                                                                                                                                                                            |            |                |  |  |