#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 48MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 34                                                                           |

| Program Memory Size        | 64KB (32K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | <u>.</u>                                                                     |

| RAM Size                   | 3.8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                    |

| Data Converters            | A/D 13x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf46j11t-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

#### 3.2.5.1 OSCTUNE Register

The internal oscillator's output has been calibrated at the factory but can be adjusted in the user's application. This is done by writing to the OSCTUNE register (Register 3-1).

When the OSCTUNE register is modified, the INTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has completed.

The OSCTUNE register also contains the INTSRC bit. The INTSRC bit allows users to select which internal oscillator provides the clock source when the 31 kHz frequency option is selected. This is covered in more detail in **Section 3.3.1 "Oscillator Control Register"**.

The 4x Phase Locked Loop (PLL) can be used with the internal oscillator block to produce faster device clock speeds than are normally possible with the internal oscillator sources. When enabled, the PLL produces a clock speed up to 32 MHz.

PLL operation is controlled through software. The control bit, PLLEN (OSCTUNE<6>), is used to enable or disable its operation. The PLL is available only to INTOSC when the device is configured to use one of the INTPLL modes as the primary clock source, SCS<1:0> = 00 (FOSC<2:0> = 011 or 010). Additionally, the PLL will only function when the selected output frequency is either 4 MHz or 8 MHz (OSCCON<6:4> = 111 or 110).

When configured for one of the PLL enabled modes, setting the PLLEN bit does not immediately switch the device clock to the PLL output. The PLL requires up to two milliseconds to start-up and lock, during which time, the device continues to be clocked. Once the PLL output is ready, the microcontroller core will automatically switch to the PLL derived frequency.

#### 3.2.5.2 Internal Oscillator Output Frequency and Drift

The internal oscillator block is calibrated at the factory to produce an INTOSC output frequency of 8.0 MHz. However, this frequency may drift as VDD or temperature changes, which can affect the controller operation in a variety of ways.

The low-frequency INTRC oscillator operates independently of the INTOSC source. Any changes in INTOSC across voltage and temperature are not necessarily reflected by changes in INTRC and vice versa.

### 3.2.5.3 Compensating for INTOSC Drift

It is possible to adjust the INTOSC frequency by modifying the value in the OSCTUNE register. This has no effect on the INTRC clock source frequency.

Tuning the INTOSC source requires knowing when to make the adjustment, in which direction it should be made, and in some cases, how large a change is needed. When using the EUSART, for example, an adjustment may be required when it begins to generate framing errors or receives data with errors while in Asynchronous mode. Framing errors indicate that the device clock frequency is too high; to adjust for this, decrement the value in OSCTUNE to reduce the clock frequency. On the other hand, errors in data may suggest that the clock speed is too low; to compensate, increment OSCTUNE to increase the clock frequency.

It is also possible to verify device clock speed against a reference clock. Two timers may be used: one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the Timer1 oscillator. Both timers are cleared, but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value is greater than expected, then the internal oscillator block is running too fast. To adjust for this, decrement the OSCTUNE register.

Finally, an ECCP module can use free-running Timer1 (or Timer3), clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded for use later. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

If the measured time is greater than the calculated time, the internal oscillator block is running too fast; to compensate, decrement the OSCTUNE register. If the measured time is less than the calculated time, the internal oscillator block is running too slow; to compensate, increment the OSCTUNE register.

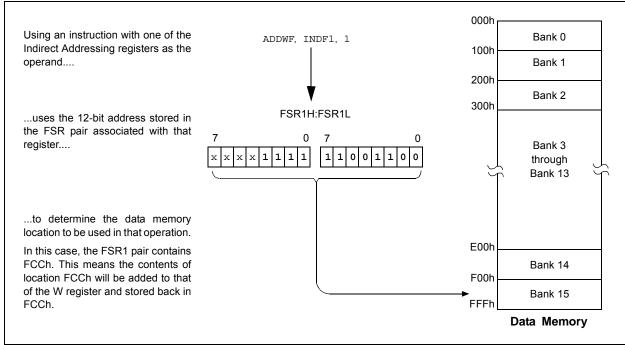

#### 6.4.3.1 FSR Registers and the INDF Operand (INDF)

At the core of Indirect Addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. The four upper bits of the FSRnH register are not used, so each FSR pair holds a 12-bit value. This represents a value that can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect Addressing is accomplished with a set of INDF operands, INDF0 through INDF2. These can be presumed to be "virtual" registers: they are mapped in the

FIGURE 6-8: INDIRECT ADDRESSING

SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because Indirect Addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

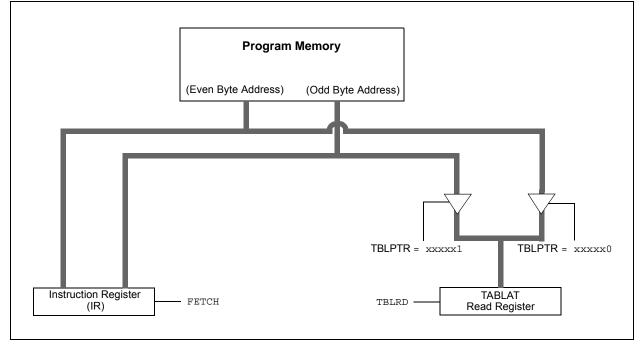

#### 7.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

The internal program memory is typically organized by words. The LSb of the address selects between the high and low bytes of the word.

Figure 7-4 illustrates the interface between the internal program memory and the TABLAT.

# FIGURE 7-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 7-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW   | CODE_ADDR_UPPER | ;   | Load TBLPTR with the base      |

|-----------|---------|-----------------|-----|--------------------------------|

|           | MOVWF   | TBLPTRU         | ; ; | address of the word            |

|           | MOVLW   | CODE_ADDR_HIGH  |     |                                |

|           | MOVWF   | TBLPTRH         |     |                                |

|           | MOVLW   | CODE_ADDR_LOW   |     |                                |

|           | MOVWF   | TBLPTRL         |     |                                |

| READ_WORD |         |                 |     |                                |

|           | TBLRD*+ | -               | ;   | read into TABLAT and increment |

|           | MOVF    | TABLAT, W       | ;   | get data                       |

|           | MOVWF   | WORD_EVEN       |     |                                |

|           | TBLRD*+ | -               | ;   | read into TABLAT and increment |

|           | MOVF    | TABLAT, W       | ;   | get data                       |

|           | MOVWF   | WORD_ODD        |     |                                |

### 9.2 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Request (Flag) registers (PIR1, PIR2, PIR3).

- Note 1: Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INT-CON<7>).

- 2: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt and after servicing that interrupt.

### REGISTER 9-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1 (ACCESS F9Eh)

| R/W-0                | R/W-0 | R-0   | R-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|-------|-------|--------|--------|--------|--------|

| PMPIF <sup>(1)</sup> | ADIF  | RC1IF | TX1IF | SSP1IF | CCP1IF | TMR2IF | TMR1IF |

| bit 7                |       |       |       |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7 | PMPIF: Parallel Master Port Read/Write Interrupt Flag bit <sup>(1)</sup>                                                                                  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = A read or a write operation has taken place (must be cleared in software)                                                                             |

|       | 0 = No read or write has occurred                                                                                                                         |

| bit 6 | ADIF: A/D Converter Interrupt Flag bit                                                                                                                    |

|       | <ul> <li>1 = An A/D conversion completed (must be cleared in software)</li> <li>0 = The A/D conversion is not complete</li> </ul>                         |

| bit 5 | RC1IF: EUSART1 Receive Interrupt Flag bit                                                                                                                 |

|       | <ul> <li>1 = The EUSART1 receive buffer, RCREG1, is full (cleared when RCREG1 is read)</li> <li>0 = The EUSART1 receive buffer is empty</li> </ul>        |

| bit 4 | TX1IF: EUSART1 Transmit Interrupt Flag bit                                                                                                                |

|       | <ul> <li>1 = The EUSART1 transmit buffer, TXREG1, is empty (cleared when TXREG1 is written)</li> <li>0 = The EUSART1 transmit buffer is full</li> </ul>   |

| bit 3 | SSP1IF: Master Synchronous Serial Port 1 Interrupt Flag bit                                                                                               |

|       | <ul> <li>1 = The transmission/reception is complete (must be cleared in software)</li> <li>0 = Waiting to transmit/receive</li> </ul>                     |

| bit 2 | CCP1IF: ECCP1 Interrupt Flag bit                                                                                                                          |

|       | Capture mode:                                                                                                                                             |

|       | 1 = A TMR1/TMR3 register capture occurred (must be cleared in software)                                                                                   |

|       | 0 = No TMR1/TMR3 register capture occurred                                                                                                                |

|       | <u>Compare mode:</u><br>1 = A TMR1/TMR3 register compare match occurred (must be cleared in software)<br>0 = No TMR1/TMR3 register compare match occurred |

|       | PWM mode:                                                                                                                                                 |

|       | Unused in this mode.                                                                                                                                      |

| bit 1 | TMR2IF: TMR2 to PR2 Match Interrupt Flag bit                                                                                                              |

|       | <ul> <li>1 = TMR2 to PR2 match occurred (must be cleared in software)</li> <li>0 = No TMR2 to PR2 match occurred</li> </ul>                               |

| bit 0 | TMR1IF: TMR1 Overflow Interrupt Flag bit                                                                                                                  |

|       | <ul><li>1 = TMR1 register overflowed (must be cleared in software)</li><li>0 = TMR1 register did not overflow</li></ul>                                   |

|       |                                                                                                                                                           |

Note 1: These bits are unimplemented on 28-pin devices.

| R/W-1            | R/W-1                                                                   | R/W-1             | R/W-1            | R/W-1             | R/W-1            | R/W-1           | R/W-1  |  |  |  |  |

|------------------|-------------------------------------------------------------------------|-------------------|------------------|-------------------|------------------|-----------------|--------|--|--|--|--|

| SSP2IP           | BCL2IP                                                                  | RC2IP             | TX2IP            | TMR4IP            | CTMUIP           | TMR3GIP         | RTCCIP |  |  |  |  |

| bit 7            | •                                                                       | •                 | ·                |                   | •                |                 | bit C  |  |  |  |  |

| <del></del>      |                                                                         |                   |                  |                   |                  |                 |        |  |  |  |  |

| Legend:          |                                                                         |                   |                  |                   |                  |                 |        |  |  |  |  |

| R = Readab       |                                                                         | W = Writable      |                  |                   | nented bit, read |                 |        |  |  |  |  |

| -n = Value a     | t POR                                                                   | '1' = Bit is set  |                  | '0' = Bit is clea | ared             | x = Bit is unkn | own    |  |  |  |  |

| bit 7            | SSDOID, Ma                                                              | ster Synchronou   | a Sorial Dort    | 2 Interrunt Drier | ity bit          |                 |        |  |  |  |  |

|                  | 1 = High privations                                                     | ,                 |                  |                   |                  |                 |        |  |  |  |  |

|                  | 0 = Low price                                                           | •                 |                  |                   |                  |                 |        |  |  |  |  |

| bit 6            | it 6 <b>BCL2IP:</b> Bus Collision Interrupt Priority bit (MSSP2 module) |                   |                  |                   |                  |                 |        |  |  |  |  |

|                  | 1 = High pri                                                            |                   |                  | ,                 | ,                |                 |        |  |  |  |  |

| 0 = Low priority |                                                                         |                   |                  |                   |                  |                 |        |  |  |  |  |

| bit 5            | RC2IP: EUSART2 Receive Interrupt Priority bit                           |                   |                  |                   |                  |                 |        |  |  |  |  |

|                  | 1 = High priority                                                       |                   |                  |                   |                  |                 |        |  |  |  |  |

| 1.11.4           | 0 = Low price                                                           | •                 |                  |                   |                  |                 |        |  |  |  |  |

| bit 4            |                                                                         | ART2 Transmit     | Interrupt Prior  | ity bit           |                  |                 |        |  |  |  |  |

|                  | 1 = High pri-0 = Low price                                              | •                 |                  |                   |                  |                 |        |  |  |  |  |

| bit 3            |                                                                         | IR4 to PR4 Inter  | rupt Priority b  | it                |                  |                 |        |  |  |  |  |

|                  |                                                                         | 1 = High priority |                  |                   |                  |                 |        |  |  |  |  |

|                  | 0 = Low price                                                           | •                 |                  |                   |                  |                 |        |  |  |  |  |

| bit 2            | CTMUIP: Ch                                                              | arge Time Mea     | surement Unit    | (CTMU) Interru    | pt Priority bit  |                 |        |  |  |  |  |

|                  | 1 = High priority                                                       |                   |                  |                   |                  |                 |        |  |  |  |  |

|                  | 0 = Low price                                                           | -                 |                  |                   |                  |                 |        |  |  |  |  |

| bit 1            |                                                                         | ïmer3 Gate Inte   | rrupt Priority b | bit               |                  |                 |        |  |  |  |  |

|                  | 1 = High pri-0 = Low price                                              |                   |                  |                   |                  |                 |        |  |  |  |  |

| bit 0            | -                                                                       | CC Interrupt Pri  | ority bit        |                   |                  |                 |        |  |  |  |  |

|                  | 1 = High pri                                                            |                   | only bit         |                   |                  |                 |        |  |  |  |  |

|                  | 0 = Low price                                                           | •                 |                  |                   |                  |                 |        |  |  |  |  |

### REGISTER 9-12: IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 3 (ACCESS FA5h)

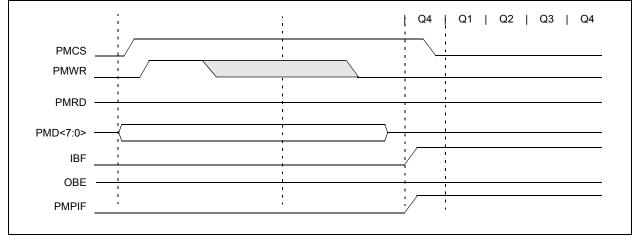

#### 11.2.2 WRITE TO SLAVE PORT

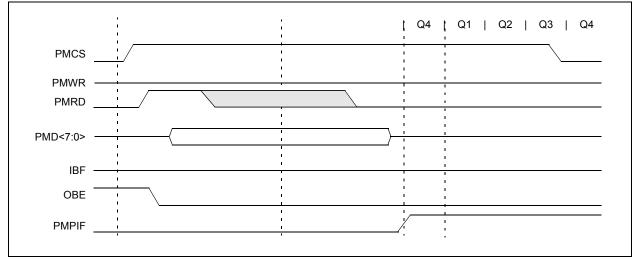

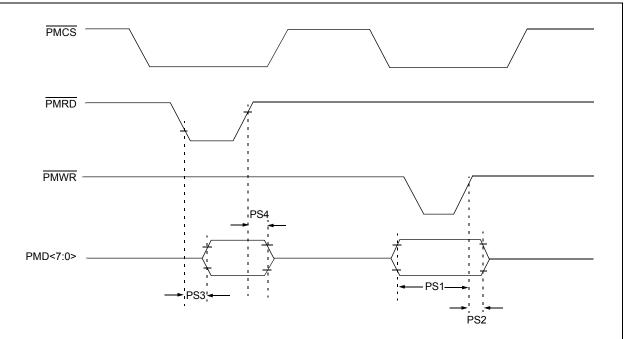

When chip select is active and a write strobe occurs (PMCS = 1 and PMWR = 1), the data from PMD<7:0> is captured into the lower PMDIN1L register. The PMPIF and IBF flag bits are set when the write ends. The timing for the control signals in Write mode is displayed in Figure 11-3. The polarity of the control signals are configurable.

### 11.2.3 READ FROM SLAVE PORT

When chip select is active and a read strobe occurs (PMCS = 1 and PMRD = 1), the data from the PMDOUT1L register (PMDOUT1L<7:0>) is presented onto PMD<7:0>. Figure 11-4 provides the timing for the control signals in Read mode.

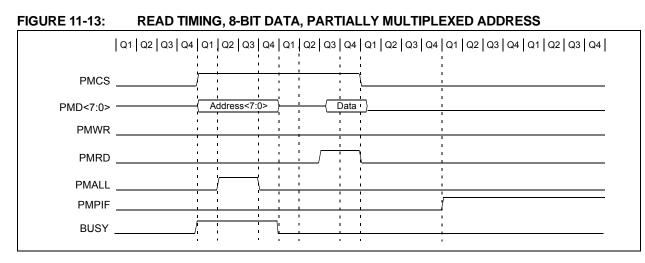

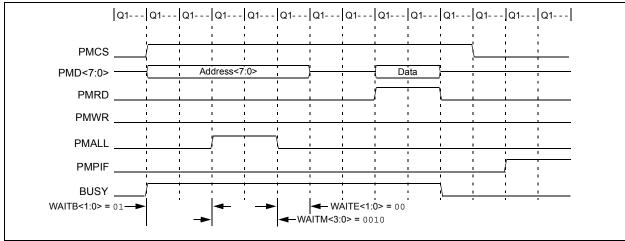

#### 11.3.11 MASTER MODE TIMING

This section contains a number of timing examples that represent the common Master mode configuration options. These options vary from 8-bit to 16-bit data, fully demultiplexed to fully multiplexed address and Wait states.

#### FIGURE 11-12: READ AND WRITE TIMING, 8-BIT DATA, DEMULTIPLEXED ADDRESS

| Q1       | Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q            | Q1   Q2   Q3   Q4   Q1   Q2   Q3   Q4 | Q1 Q2 | Q3 Q4       | Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 |

|----------|-----------------------------------|---------------------------------------|-------|-------------|-------------------------|

|          |                                   | 1                                     |       | 1<br>1<br>1 |                         |

| PMCS     |                                   | ]                                     |       |             | <u> </u>                |

| PMD<7:0> |                                   |                                       | (     | -           | <u>.</u>                |

| PMA<7:0> | ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; | <br> <br>                             |       | 1           | <u>й</u>                |

| PMWR     |                                   |                                       | · · · |             |                         |

| PMRD     |                                   | י<br>י<br>י                           | İ     | 1           | <u> </u>                |

| PMPIF    |                                   |                                       | · · · | 1           | :                       |

| BUSY     |                                   | 1                                     |       |             | · · ·                   |

# FIGURE 11-14: READ TIMING, 8-BIT DATA, WAIT STATES ENABLED, PARTIALLY MULTIPLEXED ADDRESS

# 13.7 Resetting Timer1 Using the ECCP Special Event Trigger

If ECCP1 or ECCP2 is configured to use Timer1 and to generate a Special Event Trigger in Compare mode (CCPxM<3:0> = 1011), this signal will reset Timer3. The trigger from ECCP2 will also start an A/D conversion if the A/D module is enabled (see **Section 18.3.4** "**Special Event Trigger**" for more information).

The module must be configured as either a timer or a synchronous counter to take advantage of this feature. When used this way, the CCPRxH:CCPRxL register pair effectively becomes a Period register for Timer1.

If Timer1 is running in Asynchronous Counter mode, this Reset operation may not work.

In the event that a write to Timer1 coincides with a Special Event Trigger, the write operation will take precedence.

| Note: | The Special Event Trigger from the   |  |  |  |  |  |  |  |  |

|-------|--------------------------------------|--|--|--|--|--|--|--|--|

|       | ECCPx module will not set the TMR1IF |  |  |  |  |  |  |  |  |

|       | interrupt flag bit (PIR1<0>).        |  |  |  |  |  |  |  |  |

# 13.8 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using the Timer1 gate circuitry. This is also referred to as Timer1 gate count enable.

The Timer1 gate can also be driven by multiple selectable sources.

# 13.8.1 TIMER1 GATE COUNT ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 13-4 for timing details.

| TABLE 13-3: | TIMER1 GATE ENABLE |

|-------------|--------------------|

|             | SELECTIONS         |

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| 1          | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| 1          | 1      | 0   | Holds Count      |

| 1          | 1      | 1   | Counts           |

#### 15.5.2 TIMER3 GATE SOURCE SELECTION

The Timer3 gate source can be selected from one of four different sources. Source selection is controlled by the T3GSSx bits of the T3GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T3GPOL bit of the T3GCON register.

TABLE 15-2: TIMER3 GATE SOURCES

| T3GSS<1:0> | Timer3 Gate Source                                      |

|------------|---------------------------------------------------------|

| 00         | Timer3 Gate Pin                                         |

| 01         | Overflow of Timer0<br>(TMR0 increments from FFh to 00h) |

| 10         | TMR2 to Match PR2<br>(TMR2 increments to match PR2)     |

| 11         | Reserved                                                |

### 15.5.2.1 T3G Pin Gate Operation

The T3G pin is one source for Timer3 gate control. It can be used to supply an external source to the Timer3 gate circuitry.

#### 15.5.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-to-high pulse will automatically be generated and internally supplied to the Timer3 gate circuitry.

# 15.5.2.3 Timer2 Match Gate Operation

The TMR2 register will increment until it matches the value in the PR2 register. On the very next increment cycle, TMR2 will be reset to 00h. When this Reset occurs, a low-to-high pulse will automatically be generated and internally supplied to the Timer3 gate circuitry.

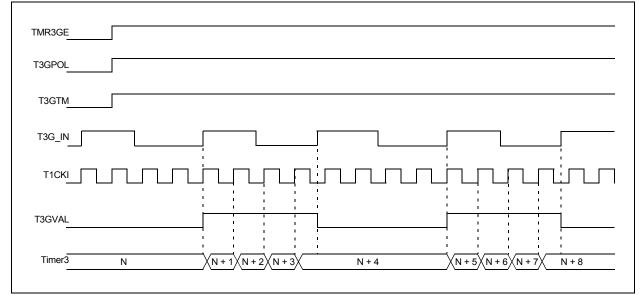

#### 15.5.3 TIMER3 GATE TOGGLE MODE

When Timer3 Gate Toggle mode is enabled, it is possible to measure the full cycle length of a Timer3 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 15-3 for timing details.

The T3GVAL bit will indicate when the Toggled mode is active and the timer is counting.

Timer3 Gate Toggle mode is enabled by setting the T3GTM bit of the T3GCON register. When the T3GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

#### FIGURE 15-3: TIMER3 GATE TOGGLE MODE

|             |                       |                                     |                             |                       | SYNC              | = 0, BRGH                   | l = 0, BRG            | <b>616 =</b> 0   |                             |                       |            |                             |

|-------------|-----------------------|-------------------------------------|-----------------------------|-----------------------|-------------------|-----------------------------|-----------------------|------------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fosc                  | Fosc = 40.000 MHz Fosc = 20.000 MHz |                             |                       | Fosc = 10.000 MHz |                             |                       | Fosc = 8.000 MHz |                             |                       |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error                          | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | _                     |                                     |                             |                       |                   |                             |                       |                  | _                           | _                     |            | _                           |

| 1.2         | —                     | —                                   | —                           | 1.221                 | 1.73              | 255                         | 1.202                 | 0.16             | 129                         | 1.201                 | -0.16      | 103                         |

| 2.4         | 2.441                 | 1.73                                | 255                         | 2.404                 | 0.16              | 129                         | 2.404                 | 0.16             | 64                          | 2.403                 | -0.16      | 51                          |

| 9.6         | 9.615                 | 0.16                                | 64                          | 9.766                 | 1.73              | 31                          | 9.766                 | 1.73             | 15                          | 9.615                 | -0.16      | 12                          |

| 19.2        | 19.531                | 1.73                                | 31                          | 19.531                | 1.73              | 15                          | 19.531                | 1.73             | 7                           | _                     | _          | _                           |

| 57.6        | 56.818                | -1.36                               | 10                          | 62.500                | 8.51              | 4                           | 52.083                | -9.58            | 2                           | —                     | _          | _                           |

| 115.2       | 125.000               | 8.51                                | 4                           | 104.167               | -9.58             | 2                           | 78.125                | -32.18           | 1                           | —                     | _          | _                           |

#### TABLE 20-3: BAUD RATES FOR ASYNCHRONOUS MODES

|              |                       |            | S                           | YNC = 0, E            | BRGH = (   | , BRG16 =                   | 0                     |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fos                   | c = 4.000  | MHz                         | Fos                   | c = 2.000  | MHz                         | Fos                   | c = 1.000  | MHz                         |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | 0.300                 | 0.16       | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16      | 51                          |

| 1.2          | 1.202                 | 0.16       | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16      | 12                          |

| 2.4          | 2.404                 | 0.16       | 25                          | 2.403                 | -0.16      | 12                          | —                     | _          | _                           |

| 9.6          | 8.929                 | -6.99      | 6                           | —                     | _          | _                           | —                     | _          | _                           |

| 19.2         | 20.833                | 8.51       | 2                           | —                     | _          | _                           | —                     | _          | _                           |

| 57.6         | 62.500                | 8.51       | 0                           | —                     | _          | _                           | —                     | _          | _                           |

| 115.2        | 62.500                | -45.75     | 0                           | _                     | _          | —                           | _                     |            | —                           |

|              |                       |            |                             |                       | SYNC       | = 0, BRGH                   | I = 1, BRG            | 1 <b>6 =</b> 0 |                             |                       |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|----------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc                  | = 40.000   | ) MHz                       | Fosc                  | = 20.000   | ) MHz                       | Fosc                  | = 10.000       | ) MHz                       | Fos                   | c = 8.000  | MHz                         |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error     | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          |                       | _          | _                           | _                     | _          | _                           |                       |                | _                           | _                     | _          | _                           |

| 1.2          | —                     | —          | —                           | —                     | —          | —                           | —                     | —              | —                           | —                     | —          | —                           |

| 2.4          | —                     | _          | _                           | —                     | _          | _                           | 2.441                 | 1.73           | 255                         | 2.403                 | -0.16      | 207                         |

| 9.6          | 9.766                 | 1.73       | 255                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16           | 64                          | 9615.                 | -0.16      | 51                          |

| 19.2         | 19.231                | 0.16       | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73           | 31                          | 19.230                | -0.16      | 25                          |

| 57.6         | 58.140                | 0.94       | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36          | 10                          | 55.555                | 3.55       | 8                           |

| 115.2        | 113.636               | -1.36      | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51           | 4                           | —                     | _          | _                           |

|              |                       |            | S                           | YNC = 0, E            | BRGH = 1   | L, BRG16 =                  | 0                     |            |                             |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Foso                  | c = 4.000  | MHz                         | Fos                   | c = 2.000  | MHz                         | Fos                   | c = 1.000  | MHz                         |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | _                     |            | _                           | _                     |            | _                           | 0.300                 | -0.16      | 207                         |

| 1.2          | 1.202                 | 0.16       | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |

| 2.4          | 2.404                 | 0.16       | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |

| 9.6          | 9.615                 | 0.16       | 25                          | 9.615                 | -0.16      | 12                          | _                     | _          | _                           |

| 19.2         | 19.231                | 0.16       | 12                          | —                     | _          | _                           | _                     | _          | _                           |

| 57.6         | 62.500                | 8.51       | 3                           | —                     | _          | _                           | —                     | _          | _                           |

| 115.2        | 125.000               | 8.51       | 1                           | _                     | _          | _                           | _                     | _          | _                           |

© 2011 Microchip Technology Inc.

#### 20.2.2 EUSART ASYNCHRONOUS RECEIVER

The receiver block diagram is displayed in Figure 20-6. The data is received on the RXx pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

#### 20.2.2.1 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero (after accounting for RXDTP setting). Following the Start bit will be the Least Significant bit of the data character being received. As each bit is received, the value will be sampled and shifted into the Receive Shift Register (RSR). After all 8 or 9 data bits (user selectable option) of the character have been shifted in, one final bit time is measured and the level sampled. This is the Stop bit, which should always be a '1' (after accounting for RXDTP setting). If the data recovery circuit samples a '0' in the Stop bit position then a framing error (FERR) is set for this character, otherwise the framing error is cleared for this character.

Once all data bits of the character and the Stop bit has been received, the data bits in the RSR will immediately be transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters before software is required to service the EUSART receiver. The RSR register is not directly accessible by software. Firmware can read data from the FIFO by reading the RCREGx register. Each firmware initiated read from the RCREGx register will advance the FIFO by one character, and will clear the receive interrupt flag (RCxIF), if no additional data exists in the FIFO.

#### 20.2.2.2 Receive Overrun Error

If the user firmware allows the FIFO to become full, and a third character is received before the firmware reads from RCREGx, a buffer overrun error condition will occur. In this case, the hardware will block the RSR contents (the third byte received) from being copied into the receive FIFO, the character will be lost and the OERR status bit in the RCSTAx register will become set. If an OERR condition is allowed to occur, firmware must clear the condition by clearing and then resetting CREN, before additional characters can be successfully received.

| Note: | If the receive FIFO is overrun, no addi-     |

|-------|----------------------------------------------|

|       | tional characters will be received until the |

|       | overrun condition is cleared.                |

#### 20.2.2.3 Setting Up Asynchronous Receive

To set up an Asynchronous Reception:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, RCxIE.

- 4. If 9-bit reception is desired, set bit, RX9.

- 5. Enable the reception by setting bit, CREN.

- 6. Flag bit, RCxIF, will be set when reception is complete and an interrupt will be generated if enable bit, RCxIE, was set.

- 7. Read the RCSTAx register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREGx register.

- 9. If any error occurred, clear the error by clearing enable bit, CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### 20.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are required, set the RCEN bit and select the desired priority level with the RCxIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- The RCxIF bit will be set when reception is complete. The interrupt will be Acknowledged if the RCxIE and GIE bits are set.

- 8. Read the RCSTAx register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREGx to determine if the device is being addressed.

#### 20.4 EUSART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTAx<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the CKx pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

#### 20.4.1 EUSART SYNCHRONOUS SLAVE TRANSMISSION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep mode.

If two words are written to the TXREGx and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREGx register.

- c) Flag bit, TXxIF, will not be set.

- d) When the first word has been shifted out of TSR, the TXREGx register will transfer the second word to the TSR and flag bit, TXxIF, will now be set.

- e) If enable bit, TXxIE, is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. Clear bits, CREN and SREN.

- 3. If interrupts are desired, set enable bit, TXxIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting enable bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

# 24.0 HIGH/LOW VOLTAGE DETECT (HLVD)

PIC18F46J11 family devices (including PIC18LF46J11 family devices) have a High/Low Voltage Detect (HLVD) module for monitoring the absolute voltage on VDD or the HLVDIN pin. This is a programmable circuit that allows the user to specify both a device voltage trip point and the direction of change from that point.

If the module detects an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt. The High/Low-Voltage Detect Control register (Register 24-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

Figure 24-1 provides a block diagram for the HLVD module.

### REGISTER 24-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER (ACCESS F85h)

| R/W-0   | R-0   | R-0   | R/W-0  | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|---------|-------|-------|--------|-----------------------|-----------------------|-----------------------|-----------------------|

| VDIRMAG | BGVST | IRVST | HLVDEN | HLVDL3 <sup>(1)</sup> | HLVDL2 <sup>(1)</sup> | HLVDL1 <sup>(1)</sup> | HLVDL0 <sup>(1)</sup> |

| bit 7   |       |       |        |                       |                       |                       | bit 0                 |

| Legend:       |                     |                               |                                  |                                                                               |

|---------------|---------------------|-------------------------------|----------------------------------|-------------------------------------------------------------------------------|

| R = Readabl   | e bit               | W = Writable bit              | U = Unimplemented bit            | , read as '0'                                                                 |

| -n = Value at | t POR               | '1' = Bit is set              | '0' = Bit is cleared             | x = Bit is unknown                                                            |

|               |                     |                               |                                  |                                                                               |

| bit 7         | VDIRMA              | G: Voltage Direction Magnitu  | ide Select bit                   |                                                                               |

|               |                     | •                             | s or exceeds trip point (HLVD    |                                                                               |

|               | 0 <b>= Even</b>     | t occurs when voltage equal   | s or falls below trip point (HLV | /DL<3:0>)                                                                     |

| bit 6         |                     | Band Gap Reference Voltage    | •                                |                                                                               |

|               |                     | ates internal band gap voltag |                                  |                                                                               |

|               |                     | ates internal band gap voltag |                                  |                                                                               |

| bit 5         |                     | ternal Reference Voltage St   | -                                |                                                                               |

|               |                     |                               |                                  | t flag at the specified voltage range<br>errupt flag at the specified voltage |

|               |                     | e and the HLVD interrupt sh   |                                  | enupt hag at the specified voltage                                            |

| bit 4         | •                   | : High/Low-Voltage Detect P   |                                  |                                                                               |

|               |                     | D enabled                     |                                  |                                                                               |

|               | 0 = HLV             | D disabled                    |                                  |                                                                               |

| bit 3-0       | HLVDL<              | 3:0>: Voltage Detection Limi  | t bits <sup>(1)</sup>            |                                                                               |

|               |                     | -                             | (input comes from the HLVDI      | N pin)                                                                        |

|               | 1110 <b>= N</b>     | laximum setting               |                                  |                                                                               |

|               | •                   |                               |                                  |                                                                               |

|               | •                   |                               |                                  |                                                                               |

|               | •<br>1000 = N       | /inimum setting               |                                  |                                                                               |

|               | $0 \times 1000 = K$ | 0                             |                                  |                                                                               |

|               |                     | -                             |                                  |                                                                               |

#### Note 1: See Table 29-8 in Section 29.0 "Electrical Characteristics" for specifications.

The module is enabled by setting the HLVDEN bit. Each time the module is enabled, the circuitry requires some time to stabilize. The IRVST bit is a read-only bit that indicates when the circuit is stable. The module can generate an interrupt only after the circuit is stable and IRVST is set. The VDIRMAG bit determines the overall operation of the module. When VDIRMAG is cleared, the module monitors for drops in VDD below a predetermined set point. When the bit is set, the module monitors for rises in VDD above the set point.

© 2011 Microchip Technology Inc.

### 26.3 On-Chip Voltage Regulator

| Note 1: | The on-chip voltage regulator is only      |

|---------|--------------------------------------------|

|         | available in parts designated with an "F", |

|         | such as PIC18F25J11. The on-chip           |

|         | regulator is disabled on devices with "LF" |

|         | in their part number.                      |

2: The VDDCORE/VCAP pin must never be left floating. On "F" devices, it must be connected to a capacitor, of size CEFC, to ground. On "LF" devices, VDDCORE/VCAP must be connected to a power supply source between 2.0V and 2.7V.

The digital core logic of the PIC18F46J11 family devices is designed on an advanced manufacturing process, which requires 2.0V to 2.7V. The digital core logic obtains power from the VDDCORE/VCAP power supply pin.

However, in many applications it may be inconvenient to run the I/O pins at the same core logic voltage, as it would restrict the ability of the device to interface with other, higher voltage devices, such as those run at a nominal 3.3V. Therefore, all PIC18F46J11 family devices implement a dual power supply rail topology. The core logic obtains power from the VDDCORE/VCAP pin, while the general purpose I/O pins obtain power from the VDD pin of the microcontroller, which may be supplied with a voltage between 2.15V to 3.6V ("F" devices) or 2.0V to 3.6V ("LF" devices).

This dual supply topology allows the microcontroller to interface with standard 3.3V logic devices, while running the core logic at a lower voltage of nominally 2.5V.

In order to make the microcontroller more convenient to use, an integrated 2.5V low dropout, low quiescent current linear regulator has been integrated on the die inside PIC18F46J11 family devices. This regulator is designed specifically to supply the core logic of the device. It allows PIC18F46J11 family devices to effectively run from a single power supply rail, without the need for external regulators.

The on-chip voltage regulator is always enabled on "F" devices. The VDDCORE/VCAP pin serves simultaneously as the regulator output pin and the core logic supply power input pin. A capacitor should be connected to the VDDCORE/VCAP pin to ground and is necessary for regulator stability. For example connections for PIC18F and PIC18LF devices, see Figure 26-2.

On "LF" devices, the on-chip regulator is always disabled. This allows the device to save a small amount of quiescent current consumption, which may be advantageous in some types of applications, such as those which will entirely be running at a nominal 2.5V. On PIC18LF46J11 family devices, the VDDCORE/VCAP pin still serves as the core logic power supply input pin, and therefore, must be connected to a 2.0V to 2.7V supply rail at the application circuit board level. On these devices, the I/O pins may still optionally be supplied with a voltage between 2.0V to 3.6V, provided that VDD is always greater than, or equal to, VDDCORE/VCAP. For example connections for PIC18F and PIC18LF devices, see Figure 26-2.

Note: In parts designated with an "LF", such as PIC18LF46J11, VDDCORE must never exceed VDD.

The specifications for core voltage and capacitance are listed in Section 29.3 "DC Characteristics: PIC18F46J11 Family (Industrial)".

#### 26.3.1 VOLTAGE REGULATOR TRACKING MODE AND LOW-VOLTAGE DETECTION

When it is enabled, the on-chip regulator provides a constant voltage of 2.5V nominal to the digital core logic. The regulator can provide this level from a VDD of about 2.5V, all the way up to the device's VDDMAX. It does not have the capability to boost VDD levels below 2.5V. When the VDD supply input voltage drops too low to regulate to 2.5V, the regulator enters Tracking mode. In Tracking mode, the regulator output follows VDD, with a typical voltage drop of 100 mV or less.

The on-chip regulator includes a simple, Low-Voltage Detect (LVD) circuit. This circuit is separate and independent of the High/Low-Voltage Detect (HLVD) module described in **Section 24.0** "**High/Low Voltage Detect** (**HLVD**)". The on-chip regulator LVD circuit continuously monitors the VDDCORE voltage level and updates the LVDSTAT bit in the WDTCON register. The LVD detect threshold is set slightly below the normal regulation set point of the on-chip regulator.

Application firmware may optionally poll the LVDSTAT bit to determine when it is safe to run at the maximum rated frequency, so as not to inadvertently violate the voltage versus frequency requirements provided by Figure 29-1.

The VDDCORE monitoring LVD circuit is only active when the on-chip regulator is enabled. On "LF" devices, the Analog-to-Digital Converter and the HLVD module can still be used to provide firmware with VDD and VDDCORE voltage level information.

| BNO          | v                                                               | Branch if N                                                                              | lot Overfl                                             | ow                                |                             |

|--------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------|-----------------------------|

| Synta        | ax:                                                             | BNOV n                                                                                   |                                                        |                                   |                             |

| Oper         | ands:                                                           | $-128 \le n \le 1$                                                                       | 27                                                     |                                   |                             |

| Oper         | ation:                                                          | if Overflow<br>(PC) + 2 + 2                                                              | ,                                                      |                                   |                             |

| Statu        | s Affected:                                                     | None                                                                                     |                                                        |                                   |                             |

| Enco         | ding:                                                           | 1110                                                                                     | 0101                                                   | nnnn                              | nnnn                        |

| Desc         | ription:                                                        | If the Overfi<br>program wi                                                              |                                                        | 0', then t                        | the                         |

|              |                                                                 | The 2's con<br>added to th<br>have incren<br>instruction,<br>PC + 2 + 2r<br>two-cycle in | e PC. Sind<br>nented to f<br>the new a<br>n. This inst | ce the P<br>fetch the<br>ddress v | C will<br>e next<br>will be |

| Word         | ls:                                                             | 1                                                                                        |                                                        |                                   |                             |

| Cycle        | es:                                                             | 1(2)                                                                                     |                                                        |                                   |                             |

| Q C<br>If Ju | ycle Activity:                                                  |                                                                                          |                                                        |                                   |                             |

|              | Q1                                                              | Q2                                                                                       | Q3                                                     |                                   | Q4                          |

|              | Decode                                                          | Read literal<br>'n'                                                                      | Proces:<br>Data                                        | s V                               | Vrite to<br>PC              |

|              | No<br>operation                                                 | No<br>operation                                                                          | No<br>operatio                                         | n op                              | No<br>peration              |

| lf No        | o Jump:                                                         |                                                                                          |                                                        |                                   |                             |

|              | Q1                                                              | Q2                                                                                       | Q3                                                     |                                   | Q4                          |

|              | Decode                                                          | Read literal<br>'n'                                                                      | Proces:<br>Data                                        | -                                 | No<br>peration              |

| <u>Exan</u>  | n <u>ple:</u><br>Before Instruc                                 | HERE                                                                                     | BNOV J1                                                | ump                               |                             |

|              | PC<br>After Instruction<br>If Overflo<br>PC<br>If Overflo<br>PC | on<br>ow = 0;<br>= add<br>ow = 1;                                                        | dress (HE<br>dress (Ju<br>dress (HE                    | _                                 | 2)                          |

| BNZ          |                       | Branch if N                                | lot Zero         |                          |

|--------------|-----------------------|--------------------------------------------|------------------|--------------------------|

| Synta        | ax:                   | BNZ n                                      |                  |                          |

| Oper         | ands:                 | -128 ≤ n ≤ ′                               | 127              |                          |

| Oper         | ation:                | if Zero bit is<br>(PC) + 2 + 2             | ,                |                          |

| Statu        | s Affected:           | None                                       |                  |                          |

| Enco         | ding:                 | 1110                                       | 0001 nn          | nn nnnn                  |

| Desc         | ription:              | If the Zero I<br>will branch.              | bit is '0', then | the program              |

|              |                       | added to th<br>have incren<br>instruction, |                  | he PC will<br>h the next |

| Word         | ls:                   | 1                                          |                  |                          |

| Cycle        | es:                   | 1(2)                                       |                  |                          |

| Q C<br>If Ju | ycle Activity:<br>mp: |                                            |                  |                          |

|              | Q1                    | Q2                                         | Q3               | Q4                       |

|              | Decode                | Read literal<br>'n'                        | Process<br>Data  | Write to<br>PC           |

|              | No                    | No                                         | No               | No                       |

|              | operation             | operation                                  | operation        | operation                |

| lf No        | o Jump:               |                                            |                  | _                        |

|              | Q1                    | Q2                                         | Q3               | Q4                       |

|              | Decode                | Read literal<br>'n'                        | Process<br>Data  | No<br>operation          |

| Exan         | nple:                 | HERE                                       | BNZ Jump         | )                        |

|              | Before Instruc        | tion                                       | -                |                          |

|              |                       |                                            | -l               |                          |

| PC                | = | address (HERE)     |

|-------------------|---|--------------------|

| After Instruction |   |                    |

| If Zero           | = | 0:                 |

| PC                | = | address (Jump)     |

| If Zero           | = | 1;                 |

| PC                | = | address (HERE + 2) |

| RLNCF                             | Rotate Lef                                                 | t f (No Carry                                     | )                                                                       |

|-----------------------------------|------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------|

| Syntax:                           | RLNCF                                                      | f {,d {,a}}                                       |                                                                         |

| Operands:                         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$        |                                                   |                                                                         |

| Operation:                        | $(f \le n >) \rightarrow d$<br>$(f \le 7 >) \rightarrow d$ | est <n +="" 1="">,<br/>est&lt;0&gt;</n>           |                                                                         |

| Status Affected:                  | N, Z                                                       |                                                   |                                                                         |

| Encoding:                         | 0100                                                       | 01da ff                                           | ff ffff                                                                 |

| Description:                      | one bit to thi<br>is placed in                             | he left. If 'd' is                                | 'f' are rotated<br>'0', the result<br>', the result is<br>'' (default). |

|                                   | selected. If                                               | the Access B<br>'a' is '1', the I<br>GPR bank (de | BSR is used to                                                          |

|                                   | ates in Inde<br>ing mode v<br>Section 27<br>Bit-Oriente    | whenever f ≤ 9<br>7.2.3 "Byte-O                   | Offset Address-<br>95 (5Fh). See<br>Priented and<br>ns in Indexed       |

|                                   | -                                                          | register                                          | f                                                                       |

| Words:                            | 1                                                          |                                                   |                                                                         |

| Cycles:                           | 1                                                          |                                                   |                                                                         |

| Q Cycle Activity:                 |                                                            |                                                   |                                                                         |

| Q1                                | Q2                                                         | Q3                                                | Q4                                                                      |

| Decode                            | Read<br>register 'f'                                       | Process<br>Data                                   | Write to destination                                                    |

| Example:<br>Before Instruc<br>REG | RLNCF<br>tion<br>= 1010 1                                  | REG, 1,<br>011                                    | 0                                                                       |

| After Instructic<br>REG           |                                                            | 111                                               |                                                                         |

|                                   |                                                            |                                                   |                                                                         |

| RRCF                                                                                     | Rotate Rig                                                                                                                                                                               |                                                                                                                                      |                                                                                                                                   |                                                        |

|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Syntax:                                                                                  | RRCF f{,                                                                                                                                                                                 | d {,a}}                                                                                                                              |                                                                                                                                   |                                                        |

| Operands:                                                                                | $0 \leq f \leq 255$                                                                                                                                                                      |                                                                                                                                      |                                                                                                                                   |                                                        |

|                                                                                          | d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                   |                                                                                                                                      |                                                                                                                                   |                                                        |

| Operation:                                                                               | u ∈ [0, 1]<br>(f <n>) → de</n>                                                                                                                                                           | osten - <sup>2</sup>                                                                                                                 |                                                                                                                                   |                                                        |

| operation.                                                                               | $(f<0>) \rightarrow C$                                                                                                                                                                   |                                                                                                                                      | L <b>-</b> ,                                                                                                                      |                                                        |

|                                                                                          | $(C) \rightarrow dest$                                                                                                                                                                   | <7>                                                                                                                                  |                                                                                                                                   |                                                        |