Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | HCS12                                                                  |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 25MHz                                                                  |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SCI, SPI                                    |

| Peripherals                | POR, PWM, WDT                                                          |

| Number of I/O              | 60                                                                     |

| Program Memory Size        | 256KB (256K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 16K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 2.75V                                                          |

| Data Converters            | A/D 16x10b; D/A 2x8b                                                   |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 80-QFP                                                                 |

| Supplier Device Package    | 80-QFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9s12e256mfue |

## **List of Chapters**

| Chapter 1         | MC9S12E256 Device Overview (MC9S12E256DGV1) 21               |

|-------------------|--------------------------------------------------------------|

| Chapter 2         | 256 Kbyte Flash Module (S12FTS256K2V1)81                     |

| Chapter 3         | Port Integration Module (PIM9E256V1) Block Description 121   |

| Chapter 4         | Clocks and Reset Generator (CRGV4) Block Description 167     |

| Chapter 5         | Oscillator (OSCV2) Block Description203                      |

| Chapter 6<br>207  | Analog-to-Digital Converter (ATD10B16CV4) Block Description  |

| Chapter 7<br>241  | Digital-to-Analog Converter (DAC8B1CV1) Block Description .  |

| Chapter 8         | Serial Communication Interface (SCIV4) Block Description 249 |

| Chapter 9         | Serial Peripheral Interface (SPIV3) Block Description 283    |

| Chapter 10        | Inter-Integrated Circuit (IICV2) Block Description305        |

| Chapter 11<br>329 | Pulse Width Modulator with Fault Protection(PMF15B6C)Moule   |

| Chapter 12        | Pulse-Width Modulator (PWM8B6CV1) Block Description385       |

| Chapter 13        | Timer (S12TIM16B4CV1) Block Description                      |

| Chapter 14<br>445 | Dual Output Voltage Regulator (VREG3V3V2) Block Descrition   |

| Chapter 15        | Background Debug Module (BDMV4) Block Description 453        |

| Chapter 16        | Debug Module (DBGV1) Block Description                       |

| Chapter 17        | Interrupt (INTV1) Block Description                          |

| Chapter 18        | Multiplexed External Bus Interface (MEBIV3)521               |

| Chapter 19        | Module Mapping Control (MMCV4) Block Description 551         |

| Appendix A        | Electrical Characteristics571                                |

| Appendix B        | Ordering Information and Mechanical Drawings606              |

MC9S12E256 Data Sheet, Rev. 1.10

Freescale Semiconductor 5

Chapter 1 MC9S12E256 Device Overview (MC9S12E256DGV1)

#### PE7 / NOACC / XCLKS — Port E I/O Pin 7 1.4.8

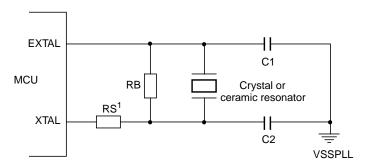

PE7 is a general purpose input or output pin. During MCU expanded modes of operation, the NOACC signal, when enabled, is used to indicate that the current bus cycle is an unused or "free cycle". This signal will assert when the CPU is not using the bus. The  $\overline{XCLKS}$  is an input signal which controls whether a crystal in combination with the internal Colpitts (low power) oscillator is used or whether Pierce oscillator/external clock circuitry is used. The state of this pin is latched at the rising edge of RESET. If the input is a logic low the EXTAL pin is configured for an external clock drive or a Pierce Oscillator. If the input is a logic high a Colpitts oscillator circuit is configured on EXTAL and XTAL. Since this pin is an input with a pull-up device during reset, if the pin is left floating, the default configuration is a Colpitts oscillator circuit on EXTAL and XTAL.

1. Due to the nature of a translated ground Colpitts oscillator a DC voltage bias is applied to the crystal. Please contact the crystal manufacturer for crystal DC

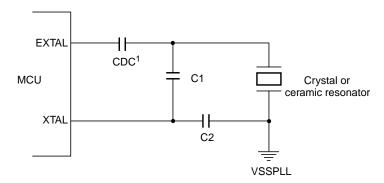

Figure 1-5. Colpitts Oscillator Connections (PE7 = 1)

1. Rs can be zero (shorted) when use with higher frequency crystals. Refer to manufacturer's data.

Figure 1-6. Pierce Oscillator Connections (PE7 = 0)

#### 1.4.9 PE6 / MODB / IPIPE1 — Port E I/O Pin 6

PE6 is a general purpose input or output pin. It is used as a MCU operating mode select pin during reset. The state of this pin is latched to the MODB bit at the rising edge of RESET. This pin is shared with the instruction queue tracking signal IPIPE1. This pin is an input with a pull-down device which is only active when RESET is low. PE6 is not available in the 80 pin package version.

MC9S12E256 Data Sheet, Rev. 1.10 62 Freescale Semiconductor

a high impedance input pin. Consult Chapter 3, "Port Integration Module (PIM9E256V1) Block Description" and Chapter 9, "Serial Peripheral Interface (SPIV3) Block Description" for information about pin configurations.

#### 1.4.31 PS6 / SCK — Port S I/O Pin 6

PS6 is a general purpose input or output pin. When the Serial Peripheral Interface (SPI) is enabled PS6 becomes the serial clock pin, SCK. While in reset and immediately out of reset the PS6 pin is configured as a high impedance input pin. Consult Chapter 3, "Port Integration Module (PIM9E256V1) Block Description" and Chapter 9, "Serial Peripheral Interface (SPIV3) Block Description" for information about pin configurations.

#### 1.4.32 PS5 / MOSI — Port S I/O Pin 5

PS5 is a general purpose input or output pin. When the Serial Peripheral Interface (SPI) is enabled PS5 is the master output (during master mode) or slave input (during slave mode) pin. While in reset and immediately out of reset the PS5 pin is configured as a high impedance input pin Consult Chapter 3, "Port Integration Module (PIM9E256V1) Block Description" and Chapter 9, "Serial Peripheral Interface (SPIV3) Block Description" for information about pin configurations.

#### 1.4.33 PS4 / MISO — Port S I/O Pin 4

PS4 is a general purpose input or output pin. When the Serial Peripheral Interface (SPI) is enabled PS4 is the master input (during master mode) or slave output (during slave mode) pin. While in reset and immediately out of reset the PS4 pin is configured as a high impedance input pin. Consult Chapter 3, "Port Integration Module (PIM9E256V1) Block Description" and Chapter 9, "Serial Peripheral Interface (SPIV3) Block Description" for information about pin configurations.

## 1.4.34 PS3 / TXD1 — Port S I/O Pin 3

PS3 is a general purpose input or output. When the Serial Communications Interface 1 (SCI1) transmitter is enabled the PS3 pin is configured as the transmit pin, TXD1, of SCI1. While in reset and immediately out of reset the PS3 pin is configured as a high impedance input pin. Consult Chapter 3, "Port Integration Module (PIM9E256V1) Block Description" and Chapter 8, "Serial Communication Interface (SCIV4) Block Description" for information about pin configurations.

#### 1.4.35 PS2 / RXD1 — Port S I/O Pin 2

PS2 is a general purpose input or output. When the Serial Communications Interface 1 (SCI1) receiver is enabled the PS2 pin is configured as the receive pin RXD1 of SCI1. While in reset and immediately out of reset the PS2 pin is configured as a high impedance input pin. Consult Chapter 3, "Port Integration Module (PIM9E256V1) Block Description" and Chapter 8, "Serial Communication Interface (SCIV4) Block Description" for information about pin configurations.

Trying to alter data in any of the protected areas in the Flash block will result in a protection violation error and the PVIOL flag will be set in the FSTAT register. A mass erase of the Flash block is not possible if any of the contained Flash sectors are protected.

**Table 2-12. FPROT Field Descriptions**

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FPOPEN      | <ul> <li>Protection Function Bit — The FPOPEN bit determines the protection function for program or erase as shown in Table 2-13.</li> <li>0 FPHDIS and FPLDIS bits define unprotected address ranges as specified by the corresponding FPHS[1:0] and FPLS[1:0] bits. For an MCU without an EEPROM module, the FPOPEN clear state allows the main part of the Flash block to be protected while a small address range can remain unprotected for EEPROM emulation.</li> <li>1 FPHDIS and FPLDIS bits enable protection for the address range specified by the corresponding FPHS[1:0] and FPLS[1:0] bits.</li> </ul> |

| 6<br>RNV[6]      | Reserved Nonvolatile Bit — The RNV[6] bit must remain in the erased state 1 for future enhancements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5<br>FPHDIS      | Flash Protection Higher Address Range Disable — The FPHDIS bit determines whether there is a protected/unprotected area in the higher address space of the Flash block.  O Protection/Unprotection enabled  1 Protection/Unprotection disabled                                                                                                                                                                                                                                                                                                                                                                       |

| 4:3<br>FPHS[1:0] | Flash Protection Higher Address Size — The FPHS[1:0] bits determine the size of the protected/unprotected area as shown in Table 2-14. The FPHS[1:0] bits can only be written to while the FPHDIS bit is set.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2<br>FPLDIS      | Flash Protection Lower address range Disable — The FPLDIS bit determines whether there is a protected/unprotected area in the lower address space of the Flash block.  O Protection/Unprotection enabled  1 Protection/Unprotection disabled                                                                                                                                                                                                                                                                                                                                                                         |

| 1:0<br>FPLS[1:0] | Flash Protection Lower Address Size — The FPLS[1:0] bits determine the size of the protected/unprotected area as shown in Table 2-15. The FPLS[1:0] bits can only be written to while the FPLDIS bit is set.                                                                                                                                                                                                                                                                                                                                                                                                         |

**Table 2-13. Flash Protection Function**

| FPOPEN | FPHDIS | FPLDIS | Function <sup>1</sup>           |  |

|--------|--------|--------|---------------------------------|--|

| 1      | 1      | 1      | No Protection                   |  |

| 1      | 1      | 0      | Protected Low Range             |  |

| 1      | 0      | 1      | Protected High Range            |  |

| 1      | 0      | 0      | Protected High and Low Ranges   |  |

| 0      | 1      | 1      | Full Block Protected            |  |

| 0      | 1      | 0      | Unprotected Low Range           |  |

| 0      | 0      | 1      | Unprotected High Range          |  |

| 0      | 0      | 0      | Unprotected High and Low Ranges |  |

<sup>1</sup> For range sizes, refer to Table 2-14 and Table 2-15.

Chapter 3 Port Integration Module (PIM9E256V1) Block Description

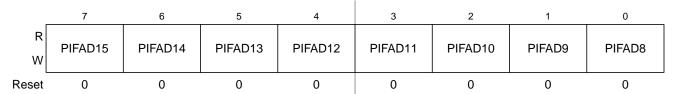

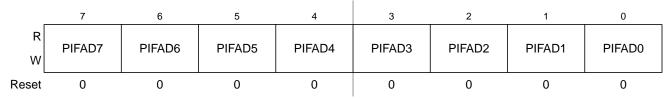

## 3.3.1.8 Port AD Interrupt Flag Register (PIFAD)

Module Base + 0x003E

Module Base + 0x003F

Figure 3-9. Port AD Interrupt Flag Register (PIFAD)

Read: Anytime. Write: Anytime.

Each flag is set by an active edge on the associated input pin. The active edge could be rising or falling based on the state of the corresponding PPSADx bit. To clear each flag, write "1" to the corresponding PIFADx bit. Writing a "0" has no effect.

#### **NOTE**

If the ATDDIEN0(1) bit of the associated pin is set to 0 (digital input buffer is disabled), active edges can not be detected.

**Table 3-8. PIFAD Field Descriptions**

| Field | Description                                                                                                                                                                                                                                 |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|       | Interrupt Flags Port AD  0 No active edge pending. Writing a "0" has no effect.  1 Active edge on the associated bit has occurred (an interrupt will occur if the associated enable bit is set).  Writing a "1" clears the associated flag. |  |

#### Table 4-11. Outcome of Clock Loss in Wait Mode

| CME | SCME | SCMIE | CRG Actions                                                                                                                                                                                                                                                                                                 |  |  |

|-----|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0   | Х    | Х     | Clock failure> No action, clock loss not detected.                                                                                                                                                                                                                                                          |  |  |

| 1   | 0    | Х     | Clock failure> CRG performs Clock Monitor Reset immediately                                                                                                                                                                                                                                                 |  |  |

| 1   | 1    | 0     | Clock failure>                                                                                                                                                                                                                                                                                              |  |  |

|     |      |       | Scenario 1: OSCCLK recovers prior to exiting Wait Mode.  - MCU remains in Wait Mode,  - VREG enabled,  - PLL enabled,  - SCM activated,  - Start Clock Quality Check,  - Set SCMIF interrupt flag.                                                                                                          |  |  |

|     |      |       | Some time later OSCCLK recovers.                                                                                                                                                                                                                                                                            |  |  |

|     |      |       | <ul> <li>CM no longer indicates a failure,</li> <li>4096 OSCCLK cycles later Clock Quality Check indicates clock o.k.,</li> <li>SCM deactivated,</li> <li>PLL disabled depending on PLLWAI,</li> <li>VREG remains enabled (never gets disabled in Wait Mode).</li> <li>MCU remains in Wait Mode.</li> </ul> |  |  |

|     |      |       | Some time later either a wakeup interrupt occurs (no SCM interrupt)  – Exit Wait Mode using OSCCLK as system clock (SYSCLK),  – Continue normal operation.                                                                                                                                                  |  |  |

|     |      |       | or an External Reset is applied.  – Exit Wait Mode using OSCCLK as system clock,  – Start reset sequence.                                                                                                                                                                                                   |  |  |

|     |      |       | Scenario 2: OSCCLK does not recover prior to exiting Wait Mode.  - MCU remains in Wait Mode,  - VREG enabled,  - PLL enabled,  - SCM activated,  - Start Clock Quality Check,  - Set SCMIF interrupt flag,  - Keep performing Clock Quality Checks (could continue infinitely)  while in Wait Mode.         |  |  |

|     |      |       | Some time later either a wakeup interrupt occurs (no SCM interrupt)  – Exit Wait Mode in SCM using PLL clock (f <sub>SCM</sub> ) as system clock,  – Continue to perform additional Clock Quality Checks until OSCCLK is o.k. again.                                                                        |  |  |

|     |      |       | or an External RESET is applied.  – Exit Wait Mode in SCM using PLL clock (f <sub>SCM</sub> ) as system clock,  – Start reset sequence,  – Continue to perform additional Clock Quality Checks until OSCCLK is o.k.again.                                                                                   |  |  |

#### Chapter 4 Clocks and Reset Generator (CRGV4) Block Description

If the MCU gets an external reset during pseudo-stop mode active, the CRG asynchronously restores all configuration bits in the register space to its default settings and starts the reset generator. After completing the reset sequence processing begins by fetching the normal reset vector. Pseudo-stop mode is exited and the MCU is in run mode again.

If the clock monitor is enabled (CME = 1) the MCU is able to leave pseudo-stop mode when loss of oscillator/external clock is detected by a clock monitor fail. If the SCME bit is not asserted the CRG generates a clock monitor fail reset (CMRESET). The CRG's behavior for CMRESET is the same compared to external reset, but another reset vector is fetched after completion of the reset sequence. If the SCME bit is asserted the CRG generates a SCM interrupt if enabled (SCMIE=1). After generating the interrupt the CRG enters self-clock mode and starts the clock quality checker (see Section 4.4.4, "Clock Quality Checker"). Then the MCU continues with normal operation. If the SCM interrupt is blocked by SCMIE = 0, the SCMIF flag will be asserted but the CRG will not wake-up from pseudo-stop mode.

If any other interrupt source (e.g. RTI) triggers exit from pseudo-stop mode the MCU immediately continues with normal operation. Because the PLL has been powered-down during stop mode the PLLSEL bit is cleared and the MCU runs on OSCCLK after leaving stop mode. The software must set the PLLSEL bit again, in order to switch system and core clocks to the PLLCLK.

Table 4-12 summarizes the outcome of a clock loss while in pseudo-stop mode.

#### Table 4-12. Outcome of Clock Loss in Pseudo-Stop Mode

| СМЕ | SCME | SCMIE | CRG Actions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|-----|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0   | Х    | Х     | Clock failure> No action, clock loss not detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| 1   | 0    | Х     | Clock failure> CRG performs Clock Monitor Reset immediately                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 1   | 1    | 0     | Clock Monitor failure>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 1   | 1    | 0     | Clock Monitor failure>  Scenario 1: OSCCLK recovers prior to exiting Pseudo-Stop Mode.  - MCU remains in Pseudo-Stop Mode,  - VREG enabled,  - PLL enabled,  - SCM activated,  - Start Clock Quality Check,  - Set SCMIF interrupt flag.  Some time later OSCCLK recovers.  - CM no longer indicates a failure,  - 4096 OSCCLK cycles later Clock Quality Check indicates clock o.k.,  - SCM deactivated,  - PLL disabled,  - VREG disabled.  - WRU remains in Pseudo-Stop Mode.  Some time later either a wakeup interrupt occurs (no SCM interrupt)  - Exit Pseudo-Stop Mode using OSCCLK as system clock (SYSCLK),  - Continue normal operation.  or an External Reset is applied.  - Exit Pseudo-Stop Mode using OSCCLK as system clock,  - Start reset sequence.  Scenario 2: OSCCLK does not recover prior to exiting Pseudo-Stop Mode.  - MCU remains in Pseudo-Stop Mode,  - VREG enabled,  - PLL enabled,  - SCM activated,  - SCM activated,  - Start Clock Quality Check,  - Set SCMIF interrupt flag,  - Keep performing Clock Quality Checks (could continue infinitely) while in Pseudo-Stop Mode in SCM using PLL clock (f <sub>SCM</sub> ) as system clock  - Continue to perform additional Clock Quality Checks until OSCCLK is o.k. again. |  |  |

|     |      |       | or an External RESET is applied.  – Exit Pseudo-Stop Mode in SCM using PLL clock (f <sub>SCM</sub> ) as system clock  – Start reset sequence,  – Continue to perform additional Clock Quality Checks until OSCCLK is o.k.again.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

Chapter 5 Oscillator (OSCV2) Block Description

## 5.3 Memory Map and Register Definition

The CRG contains the registers and associated bits for controlling and monitoring the OSCV2 module.

## 5.4 Functional Description

The OSCV2 block has two external pins, EXTAL and XTAL. The oscillator input pin, EXTAL, is intended to be connected to either a crystal or an external clock source. The selection of Colpitts oscillator or Pierce oscillator/external clock depends on the XCLKS signal which is sampled during reset. The XTAL pin is an output signal that provides crystal circuit feedback.

A buffered EXTAL signal, OSCCLK, becomes the internal reference clock. To improve noise immunity, the oscillator is powered by the  $V_{DDPLL}$  and  $V_{SSPLL}$  power supply pins.

The Pierce oscillator can be used for higher frequencies compared to the low power Colpitts oscillator.

## 5.4.1 Amplitude Limitation Control (ALC)

The Colpitts oscillator is equipped with a feedback system which does not waste current by generating harmonics. Its configuration is "Colpitts oscillator with translated ground." The transconductor used is driven by a current source under the control of a peak detector which will measure the amplitude of the AC signal appearing on EXTAL node in order to implement an amplitude limitation control (ALC) loop. The ALC loop is in charge of reducing the quiescent current in the transconductor as a result of an increase in the oscillation amplitude. The oscillation amplitude can be limited to two values. The normal amplitude which is intended for non power saving modes and a small amplitude which is intended for low power operation modes. Please refer to the CRG block description chapter for the control and assignment of the amplitude value to operation modes.

## 5.4.2 Clock Monitor (CM)

The clock monitor circuit is based on an internal resistor-capacitor (RC) time delay so that it can operate without any MCU clocks. If no OSCCLK edges are detected within this RC time delay, the clock monitor indicates a failure which asserts self clock mode or generates a system reset depending on the state of SCME bit. If the clock monitor is disabled or the presence of clocks is detected no failure is indicated. The clock monitor function is enabled/disabled by the CME control bit, described in the CRG block description chapter.

## 5.5 Interrupts

OSCV2 contains a clock monitor, which can trigger an interrupt or reset. The control bits and status bits for the clock monitor are described in the CRG block description chapter.

MC9S12E256 Data Sheet, Rev. 1.10

Chapter 6 Analog-to-Digital Converter (ATD10B16CV4) Block Description

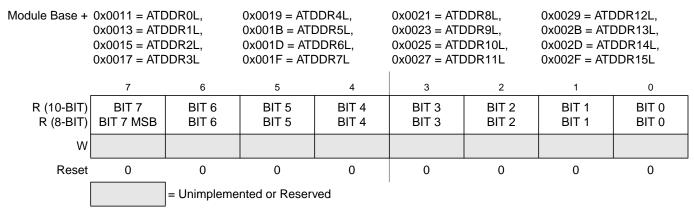

#### 6.3.2.16.2 Right Justified Result Data

| Module Base + 0x0010 = ATDDR0H,<br>0x0012 = ATDDR1H,<br>0x0014 = ATDDR2H,<br>0x0016 = ATDDR3H |   | DDR1H,<br>DDR2H,            | 0x0018 = ATDDR4H,<br>0x001A = ATDDR5H,<br>0x001C = ATDDR6H,<br>0x001E = ATDDR7H |   | 0x0020 = ATDDR8H,<br>0x0022 = ATDDR9H,<br>0x0024 = ATDDR10H,<br>0x0026 = ATDDR11H |   | 0x0028 = ATDDR12H,<br>0x002A = ATDDR13H,<br>0x002C = ATDDR14H,<br>0x002E = ATDDR15H |       |

|-----------------------------------------------------------------------------------------------|---|-----------------------------|---------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------------|---|-------------------------------------------------------------------------------------|-------|

|                                                                                               | 7 | 6                           | 5                                                                               | 4 | 3                                                                                 | 2 | 1                                                                                   | 0     |

| R (10-BIT)                                                                                    | 0 | 0                           | 0                                                                               | 0 | 0                                                                                 | 0 | BIT 9 MSB                                                                           | BIT 8 |

| R (8-BIT)                                                                                     | 0 | 0                           | 0                                                                               | 0 | 0                                                                                 | 0 | 0                                                                                   | 0     |

| W                                                                                             |   |                             |                                                                                 |   |                                                                                   |   |                                                                                     |       |

| Reset                                                                                         | 0 | 0                           | 0                                                                               | 0 | 0                                                                                 | 0 | 0                                                                                   | 0     |

|                                                                                               |   | = Unimplemented or Reserved |                                                                                 |   |                                                                                   |   |                                                                                     |       |

Figure 6-20. Right Justified, ATD Conversion Result Register x, High Byte (ATDDRxH)

Figure 6-21. Right Justified, ATD Conversion Result Register x, Low Byte (ATDDRxL)

## 6.4 Functional Description

The ATD10B16C is structured in an analog and a digital sub-block.

## 6.4.1 Analog Sub-block

The analog sub-block contains all analog electronics required to perform a single conversion. Separate power supplies  $V_{DDA}$  and  $V_{SSA}$  allow to isolate noise of other MCU circuitry from the analog sub-block.

## 6.4.1.1 Sample and Hold Machine

The sample and hold (S/H) machine accepts analog signals from the external world and stores them as capacitor charge on a storage node.

The sample process uses a two stage approach. During the first stage, the sample amplifier is used to quickly charge the storage node. The second stage connects the input directly to the storage node to complete the sample for high accuracy.

#### Chapter 8 Serial Communication Interface (SCIV4) Block Description

flag by writing another byte to the transmitter buffer (SCIDRH/SCIDRL), while the shift register is shifting out the first byte.

To initiate an SCI transmission:

- 1. Configure the SCI:

- a) Select a baud rate. Write this value to the SCI baud registers (SCIBDH/L) to begin the baud rate generator. Remember that the baud rate generator is disabled when the baud rate is 0. Writing to the SCIBDH has no effect without also writing to SCIBDL.

- b) Write to SCICR1 to configure word length, parity, and other configuration bits (LOOPS, RSRC, M, WAKE, ILT, PE, and PT).

- c) Enable the transmitter, interrupts, receive, and wake up as required, by writing to the SCICR2 register bits (TIE, TCIE, RIE, ILIE, TE, RE, RWU, and SBK). A preamble or idle character will now be shifted out of the transmitter shift register.

- 2. Transmit procedure for each byte:

- a) Poll the TDRE flag by reading the SCISR1 or responding to the TDRE interrupt. Keep in mind that the TDRE bit resets to 1.

- b) If the TDRE flag is set, write the data to be transmitted to SCIDRH/L, where the ninth bit is written to the T8 bit in SCIDRH if the SCI is in 9-bit data format. A new transmission will not result until the TDRE flag has been cleared.

- 3. Repeat step 2 for each subsequent transmission.

#### NOTE

The TDRE flag is set when the shift register is loaded with the next data to be transmitted from SCIDRH/L, which happens, generally speaking, a little over half-way through the stop bit of the previous frame. Specifically, this transfer occurs 9/16ths of a bit time AFTER the start of the stop bit of the previous frame.

Writing the TE bit from 0 to a 1 automatically loads the transmit shift register with a preamble of 10 logic 1s (if M = 0) or 11 logic 1s (if M = 1). After the preamble shifts out, control logic transfers the data from the SCI data register into the transmit shift register. A logic 0 start bit automatically goes into the least significant bit position of the transmit shift register. A logic 1 stop bit goes into the most significant bit position.

Hardware supports odd or even parity. When parity is enabled, the most significant bit (MSB) of the data character is the parity bit.

The transmit data register empty flag, TDRE, in SCI status register 1 (SCISR1) becomes set when the SCI data register transfers a byte to the transmit shift register. The TDRE flag indicates that the SCI data register can accept new data from the internal data bus. If the transmit interrupt enable bit, TIE, in SCI control register 2 (SCICR2) is also set, the TDRE flag generates a transmitter interrupt request.

When the transmit shift register is not transmitting a frame, the TXD pin goes to the idle condition, logic 1. If at any time software clears the TE bit in SCI control register 2 (SCICR2), the transmitter enable signal goes low and the transmit signal goes idle.

## Chapter 10 Inter-Integrated Circuit (IICV2) Block Description

## 10.1 Introduction

The inter-IC bus (IIC) is a two-wire, bidirectional serial bus that provides a simple, efficient method of data exchange between devices. Being a two-wire device, the IIC bus minimizes the need for large numbers of connections between devices, and eliminates the need for an address decoder.

This bus is suitable for applications requiring occasional communications over a short distance between a number of devices. It also provides flexibility, allowing additional devices to be connected to the bus for further expansion and system development.

The interface is designed to operate up to 100 kbps with maximum bus loading and timing. The device is capable of operating at higher baud rates, up to a maximum of clock/20, with reduced bus loading. The maximum communication length and the number of devices that can be connected are limited by a maximum bus capacitance of 400 pF.

#### 10.1.1 Features

The IIC module has the following key features:

- Compatible with I2C bus standard

- Multi-master operation

- Software programmable for one of 256 different serial clock frequencies

- Software selectable acknowledge bit

- Interrupt driven byte-by-byte data transfer

- Arbitration lost interrupt with automatic mode switching from master to slave

- Calling address identification interrupt

- Start and stop signal generation/detection

- Repeated start signal generation

- Acknowledge bit generation/detection

- Bus busy detection

#### Chapter 10 Inter-Integrated Circuit (IICV2) Block Description

Table 10-5. IIC Divider and Hold Values (Sheet 2 of 5)

| IBC[7:0]<br>(hex) | SCL Divider<br>(clocks) | SDA Hold<br>(clocks) | SCL Hold<br>(start) | SCL Hold<br>(stop) |

|-------------------|-------------------------|----------------------|---------------------|--------------------|

| 11                | 56                      | 9                    | 22                  | 29                 |

| 12                | 64                      | 13                   | 26                  | 33                 |

| 13                | 72                      | 13                   | 30                  | 37                 |

| 14                | 80                      | 17                   | 34                  | 41                 |

| 15                | 88                      | 17                   | 38                  | 45                 |

| 16                | 104                     | 21                   | 46                  | 53                 |

| 17                | 128                     | 21                   | 58                  | 65                 |

| 18                | 80                      | 9                    | 38                  | 41                 |

| 19                | 96                      | 9                    | 46                  | 49                 |

| 1A                | 112                     | 17                   | 54                  | 57                 |

| 1B                | 128                     | 17                   | 62                  | 65                 |

| 1C                | 144                     | 25                   | 70                  | 73                 |

| 1D                | 160                     | 25                   | 78                  | 81                 |

| 1E                | 192                     | 33                   | 94                  | 97                 |

| 1F                | 240                     | 33                   | 118                 | 121                |

| 20                | 160                     | 17                   | 78                  | 81                 |

| 21                | 192                     | 17                   | 94                  | 97                 |

| 22                | 224                     | 33                   | 110                 | 113                |

| 23                | 256                     | 33                   | 126                 | 129                |

| 24                | 288                     | 49                   | 142                 | 145                |

| 25                | 320                     | 49                   | 158                 | 161                |

| 26                | 384                     | 65                   | 190                 | 193                |

| 27                | 480                     | 65                   | 238                 | 241                |

| 28                | 320                     | 33                   | 158                 | 161                |

| 29                | 384                     | 33                   | 190                 | 193                |

| 2A                | 448                     | 65                   | 222                 | 225                |

| 2B                | 512                     | 65                   | 254                 | 257                |

| 2C                | 576                     | 97                   | 286                 | 289                |

| 2D                | 640                     | 97                   | 318                 | 321                |

| 2E                | 768                     | 129                  | 382                 | 385                |

| 2F                | 960                     | 129                  | 478                 | 481                |

| 30                | 640                     | 65                   | 318                 | 321                |

| 31                | 768                     | 65                   | 382                 | 385                |

| 32                | 896                     | 129                  | 446                 | 449                |

| 33                | 1024                    | 129                  | 510                 | 513                |

| 34                | 1152                    | 193                  | 574                 | 577                |

| 35                | 1280                    | 193                  | 638                 | 641                |

| 36                | 1536                    | 257                  | 766                 | 769                |

| 37                | 1920                    | 257                  | 958                 | 961                |

| 38                | 1280                    | 129                  | 638                 | 641                |

| 39                | 1536                    | 129                  | 766                 | 769                |

| 3A                | 1792                    | 257                  | 894                 | 897                |

| 3B                | 2048                    | 257                  | 1022                | 1025               |

| 3C                | 2304                    | 385                  | 1150                | 1153               |

| 3D                | 2560                    | 385                  | 1278                | 1281               |

MC9S12E256 Data Sheet, Rev. 1.10

Table 12-5. PWMPRCLK Field Descriptions

| Field            | Description                                                                                                                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:5<br>PCKB[2:0] | <b>Prescaler Select for Clock B</b> — Clock B is 1 of two clock sources which can be used for channels 2 or 3. These three bits determine the rate of clock B, as shown in Table 12-6.        |

| 2:0<br>PCKA[2:0] | <b>Prescaler Select for Clock A</b> — Clock A is 1 of two clock sources which can be used for channels 0, 1, 4, or 5. These three bits determine the rate of clock A, as shown in Table 12-7. |

Table 12-6. Clock B Prescaler Selects

| PCKB2 | PCKB1 | PCKB0 | Value of Clock B |

|-------|-------|-------|------------------|

| 0     | 0     | 0     | Bus Clock        |

| 0     | 0     | 1     | Bus Clock / 2    |

| 0     | 1     | 0     | Bus Clock / 4    |

| 0     | 1     | 1     | Bus Clock / 8    |

| 1     | 0     | 0     | Bus Clock / 16   |

| 1     | 0     | 1     | Bus Clock / 32   |

| 1     | 1     | 0     | Bus Clock / 64   |

| 1     | 1     | 1     | Bus Clock / 128  |

**Table 12-7. Clock A Prescaler Selects**

| PCKA2 | PCKA1 | PCKA0 | Value of Clock A |

|-------|-------|-------|------------------|

| 0     | 0     | 0     | Bus Clock        |

| 0     | 0     | 1     | Bus Clock / 2    |

| 0     | 1     | 0     | Bus Clock / 4    |

| 0     | 1     | 1     | Bus Clock / 8    |

| 1     | 0     | 0     | Bus Clock / 16   |

| 1     | 0     | 1     | Bus Clock / 32   |

| 1     | 1     | 0     | Bus Clock / 64   |

| 1     | 1     | 1     | Bus Clock / 128  |

## 12.3.2.5 PWM Center Align Enable Register (PWMCAE)

The PWMCAE register contains six control bits for the selection of center aligned outputs or left aligned outputs for each PWM channel. If the CAEx bit is set to a 1, the corresponding PWM output will be center aligned. If the CAEx bit is cleared, the corresponding PWM output will be left aligned. Reference Section 12.4.2.5, "Left Aligned Outputs," and Section 12.4.2.6, "Center Aligned Outputs," for a more detailed description of the PWM output modes.

395

#### Chapter 12 Pulse-Width Modulator (PWM8B6CV1) Block Description

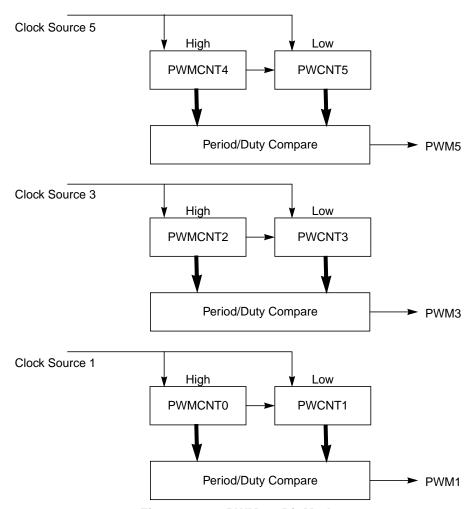

Figure 12-40. PWM 16-Bit Mode

When using the 16-bit concatenated mode, the clock source is determined by the low-order 8-bit channel clock select control bits. That is channel 5 when channels 4 and 5 are concatenated, channel 3 when channels 2 and 3 are concatenated, and channel 1 when channels 0 and 1 are concatenated. The resulting PWM is output to the pins of the corresponding low-order 8-bit channel as also shown in Figure 12-40. The polarity of the resulting PWM output is controlled by the PPOLx bit of the corresponding low-order 8-bit channel as well.

After concatenated mode is enabled (CONxx bits set in PWMCTL register), enabling/disabling the corresponding 16-bit PWM channel is controlled by the low-order PWMEx bit. In this case, the high-order bytes PWMEx bits have no effect and their corresponding PWM output is disabled.

In concatenated mode, writes to the 16-bit counter by using a 16-bit access or writes to either the low or high-order byte of the counter will reset the 16-bit counter. Reads of the 16-bit counter must be made by 16-bit access to maintain data coherency.

Either left aligned or center aligned output mode can be used in concatenated mode and is controlled by the low-order CAEx bit. The high-order CAEx bit has no effect.

Chapter 13 Timer (S12TIM16B4CV1) Block Description

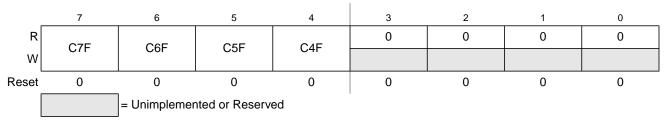

## 13.3.3.12 Main Timer Interrupt Flag 1 (TFLG1)

Module Base + 0x000E

Figure 13-14. Main Timer Interrupt Flag 1 (TFLG1)

Read anytime.

**Table 13-15. TFLG1 Field Descriptions**

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–4<br>C[7:4]F | Input Capture/Output Compare Channel Flag — These flags are set when an input capture or output compare event occurs. Flag set on a particular channel is cleared by writing a one to that corresponding CnF bit. Writing a zero to CnF bit has no effect on its status. When TFFCA bit in TSCR register is set, a read from an input capture or a write into an output compare channel will cause the corresponding channel flag CnF to be cleared.  O No event (Input Capture or Output Compare event) occurred.  Input Capture or Output Compare event occurred |

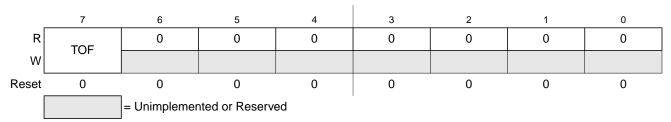

## 13.3.3.13 Main Timer Interrupt Flag 2 (TFLG2)

Module Base + 0x000F

Figure 13-15. Main Timer Interrupt Flag 2 (TFLG2)

Read anytime.

Table 13-16. TFLG2 Field Descriptions

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7<br>TOF | Timer Overflow Flag — The TFLG2 register indicates when an interrupt has occurred. Writing a one to the TOF bit will clear it. Any access to TCNT will clear TOF bit of TFLG2 register if the TFFCA bit in TSCR register is set.  0 Flag indicates an Interrupt has not occurred.  1 Flag indicates that an Interrupt has occurred (Set when 16-bit free-running timer counter overflows from \$FFFF to \$0000) |  |  |  |  |  |  |  |

MC9S12E256 Data Sheet, Rev. 1.10

sub-block, the type of breakpoint used determines if BDM becomes active before or after execution of the next instruction.

#### **NOTE**

If an attempt is made to activate BDM before being enabled, the CPU resumes normal instruction execution after a brief delay. If BDM is not enabled, any hardware BACKGROUND commands issued are ignored by the BDM and the CPU is not delayed.

In active BDM, the BDM registers and standard BDM firmware lookup table are mapped to addresses 0xFF00 to 0xFFFF. BDM registers are mapped to addresses 0xFF00 to 0xFF07. The BDM uses these registers which are readable anytime by the BDM. However, these registers are not readable by user programs.

#### 15.4.3 BDM Hardware Commands

Hardware commands are used to read and write target system memory locations and to enter active background debug mode. Target system memory includes all memory that is accessible by the CPU such as on-chip RAM, EEPROM, FLASH EEPROM, I/O and control registers, and all external memory.

Hardware commands are executed with minimal or no CPU intervention and do not require the system to be in active BDM for execution, although they can continue to be executed in this mode. When executing a hardware command, the BDM sub-block waits for a free CPU bus cycle so that the background access does not disturb the running application program. If a free cycle is not found within 128 clock cycles, the CPU is momentarily frozen so that the BDM can steal a cycle. When the BDM finds a free cycle, the operation does not intrude on normal CPU operation provided that it can be completed in a single cycle. However, if an operation requires multiple cycles the CPU is frozen until the operation is complete, even though the BDM found a free cycle.

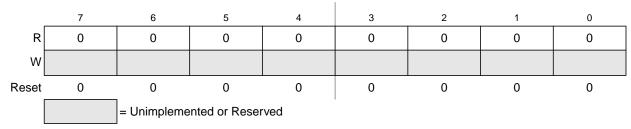

## 18.3.2.13 Reserved Register

Module Base + 0x000F

Starting address location affected by INITRG register setting.

Figure 18-17. Reserved Register

This register location is not used (reserved). All bits in this register return logic 0s when read. Writes to this register have no effect.

This register is not in the on-chip memory map in expanded and special peripheral modes. Therefore, these accesses will be echoed externally.

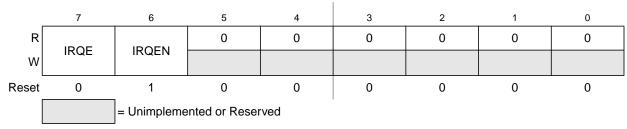

## 18.3.2.14 IRQ Control Register (IRQCR)

Module Base + 0x001E

Starting address location affected by INITRG register setting.

Figure 18-18. IRQ Control Register (IRQCR)

Read: See individual bit descriptions below

Write: See individual bit descriptions below

Table 18-12. IRQCR Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7<br>IRQE  | IRQ Select Edge Sensitive Only Special modes: read or write anytime Normal and Emulation modes: read anytime, write once 0 IRQ configured for low level recognition. 1 IRQ configured to respond only to falling edges. Falling edges on the IRQ pin will be detected anytime IRQE = 1 and will be cleared only upon a reset or the servicing of the IRQ interrupt. |  |  |  |  |  |  |  |

| 6<br>IRQEN | External IRQ Enable Normal, emulation, and special modes: read or write anytime 0 External IRQ pin is disconnected from interrupt logic. 1 External IRQ pin is connected to interrupt logic. Note: When IRQEN = 0, the edge detect latch is disabled.                                                                                                               |  |  |  |  |  |  |  |

## A.1.6 ESD Protection and Latch-up Immunity

All ESD testing is in conformity with CDF-AEC-Q100 Stress test qualification for Automotive Grade Integrated Circuits. During the device qualification ESD stresses were performed for the Human Body Model (HBM), the Machine Model (MM) and the Charge Device Model.

A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

Table A-2. ESD and Latch-up Test Conditions

| Model      | Description                               | Symbol | Value  | Unit |

|------------|-------------------------------------------|--------|--------|------|

| Human Body | Series Resistance                         | R1     | 1500   | Ohm  |

|            | Storage Capacitance                       | С      | 100    | pF   |

|            | Number of Pulse per pin positive negative |        | 3<br>3 |      |

| Machine    | Series Resistance                         | R1     | 0      | Ohm  |

|            | Storage Capacitance                       | С      | 200    | pF   |

|            | Number of Pulse per pin positive negative |        | 3<br>3 |      |

| Latch-up   | Minimum input voltage limit               | _      | -2.5   | V    |

|            | Maximum input voltage limit               | _      | 7.5    | V    |

Table A-3. ESD and Latch-Up Protection Characteristics

| Num | С | Rating                                      | Symbol           | Min          | Max    | Unit |

|-----|---|---------------------------------------------|------------------|--------------|--------|------|

| 1   | С | Human Body Model (HBM)                      | V <sub>HBM</sub> | 2000         | _      | V    |

| 2   | С | Machine Model (MM)                          | V <sub>MM</sub>  | 200          | _      | V    |

| 3   | С | Charge Device Model (CDM)                   | V <sub>CDM</sub> | 500          |        | V    |

| 4   | С | Latch-up Current at 125°C positive negative | I <sub>LAT</sub> | +100<br>-100 | _      | mA   |

| 5   | С | Latch-up Current at 27°C positive negative  | I <sub>LAT</sub> | +200<br>-200 | _<br>_ | mA   |

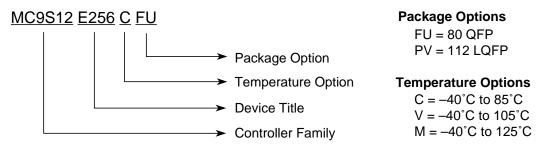

# Appendix B Ordering Information and Mechanical Drawings

Figure B-1. Order Part Number Coding

Table B-1 lists the part number coding based on the package and temperature.

Part Number

Temperature

Package

MC9S12E256CFU

-40°C, 85°C

80 QFP

MC9S12E256CPV

-40°C, 85°C

112 LQFP

MC9S12E256MFU

-40°C, 125°C

80 QFP

MC9S12E256MPV

-40°C, 125°C

112 LQFP

**Table B-1. Part Number Coding**

Table B-2 summarizes the package option and size configuration.

Table B-2. Package Option Summary

| Part<br>Number | Package | Temp. <sup>1</sup><br>Options | Flash | RAM | MEBI | ТІМ  | SCI | SPI | IIC | A/D | D/A | PWM | PMF | KWU | I/O <sup>2</sup> |

|----------------|---------|-------------------------------|-------|-----|------|------|-----|-----|-----|-----|-----|-----|-----|-----|------------------|

| MC9S12E256     | 112LQFP | M. C                          | 256K  | 16K | 1    | 12 3 | 2   | 3 1 | 1 1 | 16  | 2   | 6   | 6   | 16  | 92               |

|                | 80QFP   | IVI, C                        |       |     | 0    |      | 2 3 |     |     |     |     |     |     |     | 60               |

<sup>&</sup>lt;sup>1</sup> C:  $T_A = 85^{\circ}C$ , f = 25MHz. M:  $T_A = 125^{\circ}C$ , f = 25MHz

TIM is the number of channels.

A/D is the number of A/D channels.

D/A is the number of D/A channels.

PWM is the number of channels.

PMF is the number of channels.

KWU is the number of key wake up interrupt pins.

I/O is the sum of ports capable to act as digital input or output.

<sup>&</sup>lt;sup>2</sup> I/O is the sum of ports capable to act as digital input or output.