#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | H8/300L                                                                    |

| Core Size                  | 8-Bit                                                                      |

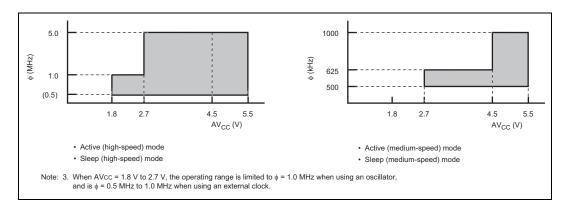

| Speed                      | 10MHz                                                                      |

| Connectivity               | SCI                                                                        |

| Peripherals                | LCD, POR, PWM, WDT                                                         |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df38124wv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com )

- Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

Rev. 8.00 Mar. 09, 2010 Page ii of xx REJ09B0042-0800

| Appendix G    | Specifications of Chip Form6 | 543 |

|---------------|------------------------------|-----|

| Appendix H    | Form of Bonding Pads         | 545 |

| Appendix I S  | pecifications of Chip Tray   | 546 |

| Main Revision | as for This Edition          | 549 |

## **1.3** Pin Arrangement and Functions

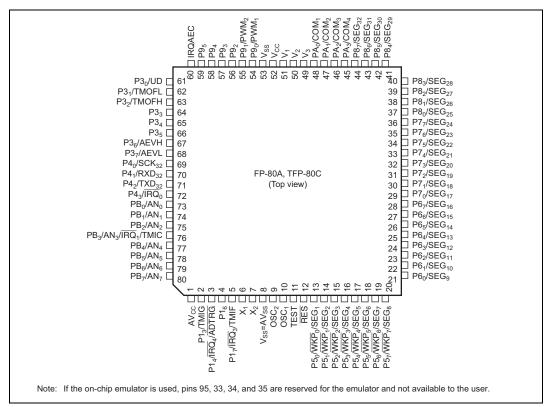

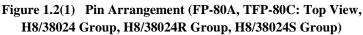

## 1.3.1 Pin Arrangement

The H8/38024 Group, H8/38024R Group, H8/38024S Group, and H8/38124 Group pin arrangements are shown in figures 1.2, 1.3, and 1.4. The bonding pad location diagram of the HCD64338024, HCD64338023, HCD64338022, HCD64338021, and HCD64338020 is shown in figure 1.5. The bonding pad coordinates of the HCD64338024, HCD64338023, HCD64338020, HCD64338021, and HCD64338020 are given in table 1.2. The bonding pad location diagram of the HCD64F38024, HCD64F38024, HCD64F38024R is shown in figure 1.6. The bonding pad coordinates of the HCD64F38024 are given in table 1.3. The bonding pad location diagram of the HCD64F3802A are given in table 1.3. The bonding pad location diagram of the HCD64F3802A, HCD64338022S, HCD64338021S, and HCD64338020S is shown in figure 1.7. The bonding pad coordinates of the HCD64F3802AS, HCD6433802AS, HCD6

Figure 1.5 Bonding Pad Location Diagram of HCD64338024, HCD64338023, HCD64338022, HCD64338021, and HCD64338020 (Top View)

(Unit: ms)

(Unit ms)

• When a oscillator is used

The table below gives settings for various operating frequencies. Set bits STS2 to STS0 for a wait time at least as long as the oscillation stabilization time.

| Table 5.4(1) | Clock Frequency and Stabilization Time (H8/38024, H8/38024S, |

|--------------|--------------------------------------------------------------|

|              | H8/38024R Group)                                             |

|      |      |      |                                                                |        | ()    |

|------|------|------|----------------------------------------------------------------|--------|-------|

| STS2 | STS1 | STS0 | Wait Time                                                      | 5 MHz  | 2 MHz |

| 0    | 0    | 0    | 8,192 states                                                   | 1.638  | 4.1   |

|      |      | 1    | 16,384 states                                                  | 3.277  | 8.2   |

|      | 1    | 0    | 1,024 states                                                   | 0.205  | 0.512 |

|      |      | 1    | 2,048 states                                                   | 0.410  | 1.024 |

| 1    | 0    | 0    | 4,096 states                                                   | 0.819  | 2.048 |

|      |      | 1    | 2 states<br>(Use prohibited with other than<br>external clock) | 0.0004 | 0.001 |

|      | 1    | 0    | 8 states                                                       | 0.002  | 0.004 |

|      |      | 1    | 16 states                                                      | 0.003  | 0.008 |

Table 5.4(2)

Clock Frequency and Stabilization Time (H8/38124 Group)

|      |      |      |                                                                |        | (Unit. his) |

|------|------|------|----------------------------------------------------------------|--------|-------------|

| STS2 | STS1 | STS0 | Wait Time                                                      | 5 MHz  | 2 MHz       |

| 0    | 0    | 0    | 8,192 states                                                   | 1.638  | 4.1         |

|      |      | 1    | 16,384 states                                                  | 3.277  | 8.2         |

|      | 1    | 0    | 32,768 states                                                  | 6.554  | 16.4        |

|      |      | 1    | 65,536 states                                                  | 13.108 | 32.8        |

| 1    | 0    | 0    | 131,072 states                                                 | 26.216 | 65.5        |

|      |      | 1    | 2 states<br>(Use prohibited with other than<br>external clock) | 0.0004 | 0.001       |

|      | 1    | 0    | 8 states                                                       | 0.002  | 0.004       |

|      |      | 1    | 16 states                                                      | 0.003  | 0.008       |

• When an external clock is used STS2 = 1, STS1 = 0, and STS0 = 1 should be set. Other values possible use, but CPU sometimes will start operation before wait time completion.

### 6.6.3 Erase Block Register (EBR)

| Bit           | 7 | 6 | 5 | 4   | 3   | 2   | 1   | 0   |

|---------------|---|---|---|-----|-----|-----|-----|-----|

|               |   |   | — | EB4 | EB3 | EB2 | EB1 | EB0 |

| Initial value | 0 | 0 | 0 | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | — | — | — | R/W | R/W | R/W | R/W | R/W |

EBR specifies the flash memory erase area block. EBR is initialized to H'00 when the SWE bit in FLMCR1 is 0. Do not set more than one bit at a time, as this will cause all the bits in EBR to be automatically cleared to 0. When each bit is set to 1 in EBR, the corresponding block can be erased. Other blocks change to the erase-protection state. See table 6.6 for the method of dividing blocks of the flash memory. When the whole bits are to be erased, erase them in turn in unit of a block.

| EBR | Bit Name | Block (Size)    | Address                                                   |

|-----|----------|-----------------|-----------------------------------------------------------|

| 0   | EB0      | EB0 (1 Kbyte)   | H'0000 to H'03FF                                          |

| 1   | EB1      | EB1 (1 Kbyte)   | H'0400 to H'07FF                                          |

| 2   | EB2      | EB2 (1 Kbyte)   | H'0800 to H'0BFF                                          |

| 3   | EB3      | EB3 (1 Kbyte)   | H'0C00 to H'0FFF                                          |

| 4   | EB4      | EB4 (12 Kbytes) | H'1000 to H'3FFF (HD64F38122)                             |

|     |          | EB4 (28 Kbytes) | H'1000 to H'7FFF (HD64F38124,<br>HD64F38024, HD64F38024R) |

## Table 6.6Division of Blocks to Be Erased

#### 6.6.4 Flash Memory Power Control Register (FLPWCR)

| Bit           | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------|-------|---|---|---|---|---|---|---|

|               | PDWND |   | — | — | _ |   | — | — |

| Initial value | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Read/Write    | R/W   | _ | _ | _ | _ | — | _ | _ |

FLPWCR enables or disables a transition to the flash memory power-down mode when the LSI switches to subactive mode. The power supply circuit can be read in the subactive mode, although it is partly halted in the power-down mode.

## Port Data Register 5 (PDR5)

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | P57 | P56 | P5₅ | P54 | P5₃ | P52 | P51 | P50 |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | R/W |

PDR5 is an 8-bit register that stores data for port 5 pins  $P5_7$  to  $P5_0$ . If port 5 is read while PCR5 bits are set to 1, the values stored in PDR5 are read, regardless of the actual pin states. If port 5 is read while PCR5 bits are cleared to 0, the pin states are read.

Upon reset, PDR5 is initialized to H'00.

## Port Control Register 5 (PCR5)

| Bit           | 7     | 6                 | 5     | 4                 | 3     | 2                 | 1     | 0     |

|---------------|-------|-------------------|-------|-------------------|-------|-------------------|-------|-------|

|               | PCR57 | PCR5 <sub>6</sub> | PCR55 | PCR5 <sub>4</sub> | PCR53 | PCR5 <sub>2</sub> | PCR51 | PCR50 |

| Initial value | 0     | 0                 | 0     | 0                 | 0     | 0                 | 0     | 0     |

| Read/Write    | W     | W                 | W     | W                 | W     | W                 | W     | W     |

PCR5 is an 8-bit register for controlling whether each of the port 5 pins  $P5_7$  to  $P5_0$  functions as an input pin or output pin. Setting a PCR5 bit to 1 makes the corresponding pin an output pin, while clearing the bit to 0 makes the pin an input pin. PCR5 and PDR5 settings are valid when the corresponding pins are designated for general-purpose input/output by PMR5 and bits SGS3 to SGS0 in LPCR.

Upon reset, PCR5 is initialized to H'00.

PCR5 is a write-only register, which is always read as all 1s.

#### Port Pull-Up Control Register 5 (PUCR5)

| Bit           | 7      | 6                  | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------------------|--------|--------|--------|--------|--------|--------|

|               | PUCR57 | PUCR5 <sub>6</sub> | PUCR55 | PUCR54 | PUCR53 | PUCR52 | PUCR51 | PUCR50 |

| Initial value | 0      | 0                  | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | R/W    | R/W                | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

PUCR5 controls whether the MOS pull-up of each of port 5 pins  $P5_7$  to  $P5_0$  is on or off. When a PCR5 bit is cleared to 0, setting the corresponding PUCR5 bit to 1 turns on the MOS pull-up for the corresponding pin, while clearing the bit to 0 turns off the MOS pull-up.

Upon reset, PUCR5 is initialized to H'00.

#### Port Mode Register 5 (PMR5)

| Bit           | 7                | 6                | 5       | 4                | 3                | 2                | 1                | 0                |

|---------------|------------------|------------------|---------|------------------|------------------|------------------|------------------|------------------|

|               | WKP <sub>7</sub> | WKP <sub>6</sub> | $WKP_5$ | WKP <sub>4</sub> | WKP <sub>3</sub> | WKP <sub>2</sub> | WKP <sub>1</sub> | WKP <sub>0</sub> |

| Initial value | 0                | 0                | 0       | 0                | 0                | 0                | 0                | 0                |

| Read/Write    | R/W              | R/W              | R/W     | R/W              | R/W              | R/W              | R/W              | R/W              |

PMR5 is an 8-bit read/write register, controlling the selection of pin functions for port 5 pins.

Upon reset, PMR5 is initialized to H'00.

## Bit n—P5<sub>n</sub>/ $\overline{WKP}_n$ /SEG<sub>n+1</sub> Pin Function Switch (WKPn)

When pin P5n/WKPn/SEGn+1 is not used as  $SEG_{n+1}$ , these bits select whether the pin is used as P5n or  $\overline{WKP}_n$ .

| Bit n<br>WKPn | Description                               |                 |

|---------------|-------------------------------------------|-----------------|

| 0             | Functions as P5n I/O pin                  | (initial value) |

| 1             | Functions as $\overline{WKP}_n$ input pin |                 |

(n = 7 to 0)

Note: For use as SEG<sub>n+1</sub>, see section 13.2.1, LCD Port Control Register (LPCR).

# 8.13 Application Note

## 8.13.1 The Management of the Un-Use Terminal

If an I/O pin not used by the user system is floating, pull it up or down.

- If an unused pin is an input pin, handle it in one of the following ways:

- Pull it up to  $V_{CC}$  with an on-chip pull-up MOS.

- Pull it up to  $V_{CC}$  with an external resistor of approximately 100 k $\Omega$ .

- Pull it down to  $V_{SS}$  with an external resistor of approximately 100 k $\Omega$ .

- For a pin also used by the A/D converter, pull it up to  $\mathrm{AV}_{\mathrm{CC}}.$

- If an unused pin is an output pin, handle it in one of the following ways:

- Set the output of the unused pin to high and pull it up to  $V_{CC}$  with an on-chip pull-up MOS.

- Set the output of the unused pin to high and pull it up to  $V_{CC}$  with an external resistor of approximately 100 k $\Omega$ .

- Set the output of the unused pin to low and pull it down to GND with an external resistor of approximately 100 k $\Omega$ .

# Renesas

## 9.2.4 Timer A Operation States

Table 9.3 summarizes the timer A operation states.

## Table 9.3 Timer A Operation States

| Oper | ation Mode      | Reset | Active    | Sleep     | Watch     | Sub-<br>active | Sub-<br>sleep | Standby  | Module<br>Standby |

|------|-----------------|-------|-----------|-----------|-----------|----------------|---------------|----------|-------------------|

| TCA  | Interval        | Reset | Functions | Functions | Halted    | Halted         | Halted        | Halted   | Halted            |

|      | Clock time base | Reset | Functions | Functions | Functions | Functions      | Functions     | Halted   | Halted            |

| TMA  |                 | Reset | Functions | Retained  | Retained  | Functions      | Retained      | Retained | Retained          |

Note: When the real-time clock time base function is selected as the internal clock of TCA in active mode or sleep mode, the internal clock is not synchronous with the system clock, so it is synchronized by a synchronizing circuit. This may result in a maximum error of 1/φ (s) in the count cycle.

# 9.2.5 Application Note

When bit 0 (TACKSTP) of the clock stop register 1 (CKSTPR1) is cleared to 0, bit 3 (TMA3) of the timer mode register A (TMA) cannot be rewritten.

Set bit 0 (TACKSTP) of the clock stop register 1 (CKSTPR1) to 1 before rewriting bit 3 (TMA3) of the timer mode register A (TMA).

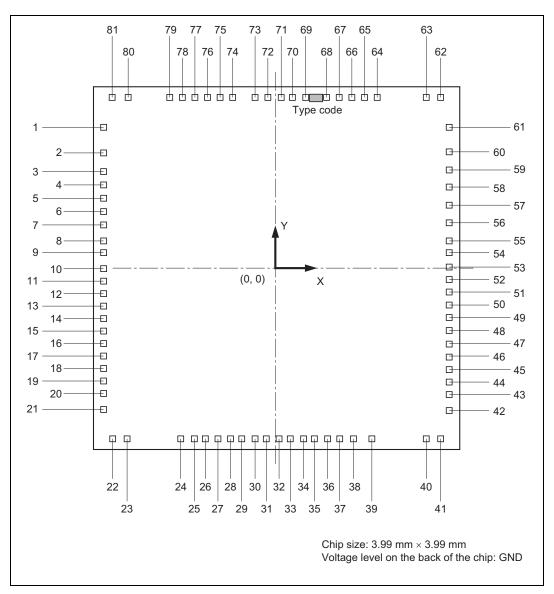

### 7. Relation between RDR reads and bit RDRF

In a receive operation, SCI3 continually checks the RDRF flag. If bit RDRF is cleared to 0 when reception of one frame ends, normal data reception is completed. If bit RDRF is set to 1, this indicates that an overrun error has occurred.

When the contents of RDR are read, bit RDRF is cleared to 0 automatically. Therefore, if bit RDR is read more than once, the second and subsequent read operations will be performed while bit RDRF is cleared to 0. Note that, when an RDR read is performed while bit RDRF is cleared to 0, if the read operation coincides with completion of reception of a frame, the next frame of data may be read. This is illustrated in figure 10.17.

Figure 10.17 Relation between RDR Read Timing and Data

In this case, only a single RDR read operation (not two or more) should be performed after first checking that bit RDRF is set to 1. If two or more reads are performed, the data read the first time should be transferred to RAM, etc., and the RAM contents used. Also, ensure that there is sufficient margin in an RDR read operation before reception of the next frame is completed. To be precise in terms of timing, the RDR read should be completed before bit 7 is transferred in synchronous mode, or before the STOP bit is transferred in asynchronous mode.

# Renesas

## 8. Transmit and receive operations when making a state transition

Make sure that transmit and receive operations have completely finished before carrying out state transition processing.

## 9. Switching SCK<sub>32</sub> function

If pin SCK<sub>32</sub> is used as a clock output pin by SCI3 in synchronous mode and is then switched to a general input/output pin (a pin with a different function), the pin outputs a low level signal for half a system clock ( $\phi$ ) cycle immediately after it is switched.

This can be prevented by either of the following methods according to the situation.

a. When an SCK $_{32}$  function is switched from clock output to non clock-output

When stopping data transfer, issue one instruction to clear bits TE and RE to 0 and to set bits CKE1 and CKE0 in SCR3 to 1 and 0, respectively. In this case, bit COM in SMR should be left 1. The above prevents SCK<sub>32</sub> from being used as a general input/output pin. To avoid an intermediate level of voltage from being applied to SCK<sub>32</sub>, the line connected to SCK<sub>32</sub> should be pulled up to the  $V_{CC}$  level via a resistor, or supplied with output from an external device.

- b. When an SCK<sub>32</sub> function is switched from clock output to general input/output When stopping data transfer,

- (i) Issue one instruction to clear bits TE and RE to 0 and to set bits CKE1 and CKE0 in SCR3 to 1 and 0, respectively.

- (ii) Clear bit COM in SMR to 0

- (iii) Clear bits CKE1 and CKE0 in SCR3 to 0

Note that special care is also needed here to avoid an intermediate level of voltage from being applied to  $SCK_{32}$ .

## 10. Set up at subactive or subsleep mode

At subactive or subsleep mode, SCI3 becomes possible use only at CPU clock is  $\phi w/2$ .

## 11. Oscillator use with serial communications interface (H8/38124 Group only)

When implementing the serial communications interface on the H8/38124 Group, the system clock oscillator must be used. The on-chip oscillator should not be used in this case. See on-chip oscillator selection method in section 4.2, System Clock Generator, for information on switching between the system clock oscillator and the on-chip oscillator.

# Section 11 10-Bit PWM

# 11.1 Overview

The H8/38024 Group is provided with two on-chip 10-bit PWMs (pulse width modulators), designated PWM1 and PWM2, with identical functions. The PWMs can be used as D/A converters by connecting a low-pass filter. In this section the suffix m (m = 1 or 2) is used with register names, etc., as in PWDRLm, which denotes the PWDRL registers for each PWM.

## 11.1.1 Features

Features of the 10-bit PWMs are as follows.

- Choice of four conversion periods Any of the following conversion periods can be chosen: 4,096/φ, with a minimum modulation width of 4/φ 2,048/φ, with a minimum modulation width of 2/φ 1,024/φ, with a minimum modulation width of 1/φ 512/φ, with a minimum modulation width of 1/2 φ

- Pulse division method for less ripple

- Use of module standby mode enables this module to be placed in standby mode independently when not used.

On the H8/38124 Group it is possible to select between two types of PWM output: pulse-division PWM and event counter PWM (PWM incorporating AEC). (The H8/38024 Group, H8/38024F-ZTAT Group, and H8/38024S Group can only produce pulse-division PWM output.) Refer to section 9.7, Asynchronous Event Counter, for information on event counter PWM.

# Renesas

## 14.1.3 Pin Description

The pins of the power-on reset circuit and low-voltage detection circuit are listed in table 14.1.

## Table 14.1 Pin Description

| Pin                                                                               | Symbol | I/O   | Function                                                                              |

|-----------------------------------------------------------------------------------|--------|-------|---------------------------------------------------------------------------------------|

| Low-voltage detection circuit reference voltage input pin                         | Vref   | Input | Reference voltage input for low-<br>voltage detection circuit                         |

| Low-voltage detection circuit power<br>supply drop detection voltage input<br>pin | extD   | Input | Power supply drop detection voltage<br>input pin for low-voltage detection<br>circuit |

| Low-voltage detection circuit power<br>supply rise detection voltage input<br>pin | extU   | Input | Power supply rise detection voltage<br>input pin for low-voltage detection<br>circuit |

## 14.1.4 Register Descriptions

The registers of the power-on reset circuit and low-voltage detection circuit are listed in table 14.2.

## Table 14.2 Register Descriptions

| Name                                   | Symbol | R/W | Initial Value | Address |

|----------------------------------------|--------|-----|---------------|---------|

| Low-voltage detection control register | LVDCR  | R/W | H'00          | H'FF86  |

| Low-voltage detection status register  | LVDSR  | R/W | H'00          | H'FF87  |

| Low-voltage detection counter          | LVDCNT | R   | H'00          | H'FFC3  |

## 14.2 Individual Register Descriptions

## 14.2.1 Low-Voltage Detection Control Register (LVDCR)

| Bit           | 7    | 6   | 5        | 4        | 3      | 2     | 1     | 0     |

|---------------|------|-----|----------|----------|--------|-------|-------|-------|

|               | LVDE | _   | VINTDSEL | VINTUSEL | LVDSEL | LVDRE | LVDDE | LVDUE |

| Initial value | 0*   | 0   | 0        | 0        | 0*     | 0*    | 0     | 0     |

| Read/Write    | R/W  | R/W | R/W      | R/W      | R/W    | R/W   | R/W   | R/W   |

Note: \* These bits are not initialized by resets trigged by LVDR. They are initialized by power-on resets and watchdog timer resets.

## Analog Power Supply Voltage and A/D Converter Operating Range

#### Section 16 Electrical Characteristics

|                                                |                     |                 | Values |     |      |                     |       |

|------------------------------------------------|---------------------|-----------------|--------|-----|------|---------------------|-------|

| Item                                           | Symbol              | Applicable Pins | Min    | Тур | Max  | Unit Test Condition | Notes |

| Allowable<br>output high<br>current<br>(total) | ∑ — I <sub>ОН</sub> | All output pins | _      | _   | 10.0 | mA                  |       |

### Notes: Connect the TEST pin to $V_{\mbox{\scriptsize SS}}.$

1. Pin states during current measurement.

| Mode                                                | RES<br>Pin      | Internal State                         | Other<br>Pins   | LCD Power<br>Supply | Oscillator Pins                                                                |

|-----------------------------------------------------|-----------------|----------------------------------------|-----------------|---------------------|--------------------------------------------------------------------------------|

| Active (high-speed)<br>mode (I <sub>OPE1</sub> )    | V <sub>cc</sub> | Operates                               | V <sub>cc</sub> | Halted              | System clock oscillator:<br>crystal                                            |

| Active (medium-<br>speed) mode (I <sub>OPE2</sub> ) | _               |                                        |                 |                     | Subclock oscillator:<br>Pin X <sub>1</sub> = GND                               |

| Sleep mode                                          | $V_{\text{CC}}$ | Only on-chip timers operate            | V <sub>cc</sub> | Halted              | _                                                                              |

| Subactive mode                                      | $V_{\text{CC}}$ | Operates                               | $V_{\text{CC}}$ | Halted              | System clock oscillator:                                                       |

| Subsleep mode                                       | V <sub>cc</sub> | Only on-chip timers operate, CPU stops | V <sub>cc</sub> | Halted              | crystal<br>Subclock oscillator:                                                |

| Watch mode                                          | V <sub>cc</sub> | Only time base operates, CPU stops     | V <sub>cc</sub> | Halted              | crystal                                                                        |

| Standby mode                                        | V <sub>cc</sub> | CPU and timers both stop               | V <sub>cc</sub> | Halted              | System clock oscillator:<br>crystal<br>Subclock oscillator:<br>Pin $X_1 = GND$ |

2. Excludes current in pull-up MOS transistors and output buffers.

|                                               |                 |                                              |                           | Value               | S        |      |                                                                                                                                              |                                                             |

|-----------------------------------------------|-----------------|----------------------------------------------|---------------------------|---------------------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| ltem                                          | Symbol          | Applicable Pins                              | Min                       | Тур                 | Мах      | Unit | Test Condition                                                                                                                               | Notes                                                       |

| Input<br>capaci-<br>tance                     | C <sub>in</sub> | All input pins<br>except power<br>supply pin | —                         | —                   | 15.0     | pF   | $\label{eq:f} \begin{split} f &= 1 \text{ MHz}, \\ V_{\text{IN}} &= 0.0 \text{ V}, \\ T_a &= 25^{\circ}\text{C} \end{split}$                 |                                                             |

| Active<br>mode<br>current<br>consump-<br>tion | IOPE1           | V <sub>CC</sub>                              | _                         | 0.6                 | _        | mA   | Active (high-speed)<br>mode<br>$V_{CC} = 2.7 V$ ,<br>$f_{OSC} = 2 MHz$                                                                       | *1 *3 *4<br>Approx.<br>max. value<br>= $1.1 \times$<br>Typ. |

|                                               |                 |                                              | _                         | 1.0                 | _        | _    | Active (high-speed)<br>mode<br>$V_{CC} = 5 V$ ,<br>$f_{OSC} = 2 MHz$<br>Active (high-speed)<br>mode<br>$V_{CC} = 5 V$ ,<br>$f_{OSC} = 4 MHz$ | *2 *3 *4<br>Approx.<br>max. value<br>= $1.1 \times$<br>Typ. |

|                                               |                 |                                              | _                         | 0.8                 | _        | _    |                                                                                                                                              | *1 *3 *4<br>Approx.<br>max. value<br>= 1.1 ×<br>Typ.        |

|                                               |                 |                                              | _                         | 1.5                 | _        | _    |                                                                                                                                              | *2 *3 *4<br>Approx.<br>max. value<br>= $1.1 \times$<br>Typ. |

|                                               |                 |                                              | _                         | 1.6                 | _        | _    |                                                                                                                                              | *1 *3 *4<br>Approx.<br>max. value<br>= 1.1 ×<br>Typ.        |

|                                               |                 |                                              | _                         | 2.0                 | —        | _    |                                                                                                                                              | *2 *3 *4                                                    |

|                                               |                 |                                              | - 3.3 7.0 Active (high-sp | Active (high-speed) | *1 *3 *4 |      |                                                                                                                                              |                                                             |

|                                               |                 |                                              | _                         | 4.0                 | 7.0      | _    | mode<br>V <sub>CC</sub> = 5 V,<br>f <sub>OSC</sub> = 10 MHz                                                                                  | *2 *3 *4                                                    |

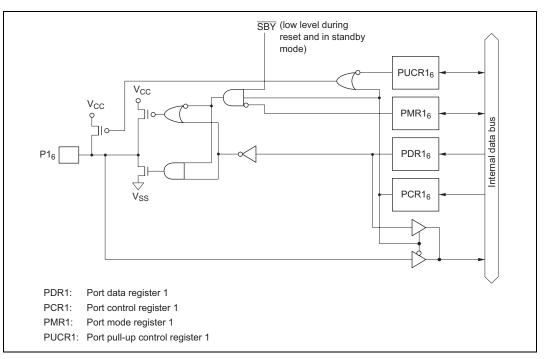

Figure C.1(b) Port 1 Block Diagram (Pin P1<sub>6</sub>, Products other than H8/38124 Group)

| Item                                    | Page | Revisi                | on (Se  | ee Manual                                                                                                | for De                     | tail  | s)                    |          |                                            |                                                                         |

|-----------------------------------------|------|-----------------------|---------|----------------------------------------------------------------------------------------------------------|----------------------------|-------|-----------------------|----------|--------------------------------------------|-------------------------------------------------------------------------|

| 16.8.2 DC<br>Characteristics            | 506  | Table a               | amenc   | led                                                                                                      |                            |       |                       |          |                                            |                                                                         |

| Table 16.22 DC                          |      | Item                  | Symbol  | Applicable Pins                                                                                          | Min                        | Value | Max                   |          | Test Condition                             | Notes                                                                   |

| Characteristics                         |      | Input high<br>voltage | VIH     | RES,<br>WKP <sub>0</sub> to WKP <sub>7</sub> ,<br>IRQ <sub>0</sub> , IRQ <sub>3</sub> , IRQ <sub>4</sub> | $V_{\text{CC}} \times 0.8$ |       | V <sub>cc</sub> + 0.3 | V        | $V_{cc} = 4.0 \text{ V to } 5.5 \text{ V}$ |                                                                         |

|                                         |      |                       |         | AEVL, AEVH,<br>TMIC, TMIF,<br>TMIG, ADTRG,<br>SCK <sub>32</sub>                                          |                            | —     | V <sub>CC</sub> + 0.3 | -        | Other than above                           |                                                                         |

|                                         |      |                       |         | IRQ <sub>1</sub>                                                                                         | $V_{\text{CC}} \times 0.8$ | —     | $AV_{CC}$ + 0.3       | V        | $V_{CC}$ = 4.0 V to 5.5 V                  | /                                                                       |

|                                         |      |                       |         |                                                                                                          | $V_{\text{CC}} \times 0.9$ | —     | $AV_{CC}$ + 0.3       | -        | Other than above                           | _                                                                       |

| 16.8.10 Power<br>Supply Characteristics | 525  | Newly                 | addec   |                                                                                                          |                            |       |                       |          |                                            |                                                                         |

| B.1 Addresses                           | 548  | Table a               | amenc   | led                                                                                                      |                            |       |                       |          |                                            |                                                                         |

|                                         |      | Lower Regi            | ster    |                                                                                                          |                            | Bit I | Names                 |          |                                            | _                                                                       |

|                                         |      | Address Nam           | e Bit 7 |                                                                                                          |                            |       | Bit 3 Bi              |          | Bit 1 Bit 0                                | Module Name                                                             |

|                                         |      | H'AA SCR<br>H'AC SSR  |         | RIE TE<br>E RDRF OE                                                                                      |                            |       | PER TE                | IE<br>ND | CKE1 CKE0                                  | SCI3                                                                    |

| B.2 Functions                           | 564  | Figure                | amen    | ded                                                                                                      |                            |       |                       |          |                                            |                                                                         |

|                                         |      | SMR—                  | Seria   | I Mode Reg                                                                                               | jister                     |       |                       | H'A      | 8                                          | SCI3                                                                    |

|                                         |      | Bit                   |         | 7 6                                                                                                      | 5                          | 4     | 3                     |          | 2 1                                        | 0                                                                       |

|                                         |      |                       | С       | OM CHR                                                                                                   | PE                         | PN    | A STO                 | P        | MP CKS1                                    | CKS0                                                                    |

|                                         |      | Initial value         |         | 0 0                                                                                                      | 0                          | 0     |                       |          | 0 0                                        | 0                                                                       |

|                                         |      | Read/Writ             | e R     | /W R/W                                                                                                   | R/W                        | R/\   | N R/W                 |          | R/W R/W                                    | R/W                                                                     |

|                                         |      |                       |         |                                                                                                          |                            |       |                       |          |                                            |                                                                         |

|                                         |      |                       |         |                                                                                                          |                            |       |                       |          | 0 1<br>1 0                                 | elect<br>φ clock<br>φ <sub>W</sub> /2 clock<br>φ/16 clock<br>φ/64 clock |

|                                         |      |                       |         |                                                                                                          |                            |       |                       | 1        | ommunication                               |                                                                         |

|                                         |      |                       |         |                                                                                                          |                            |       |                       | -        | its communication<br>its communication     |                                                                         |

| Item                                                                                                                                         | Page | Revision (See Manual for Details) |

|----------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------|

| Appendix F Package<br>Dimensions                                                                                                             | 642  | Figure replaced                   |

| Figure F.4 TLP-85V<br>Package Dimensions                                                                                                     |      |                                   |

| Appendix I<br>Specifications of Chip<br>Tray                                                                                                 | 648  | Figure replaced                   |

| Figure I.3<br>Specifications of Chip<br>Tray for the<br>HCD64338024S,<br>HCD64338023S,<br>HCD64338022S,<br>HCD64338021S, and<br>HCD64338020S |      |                                   |