Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | H8/300L                                                                     |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 10MHz                                                                       |

| Connectivity               | SCI                                                                         |

| Peripherals                | LCD, POR, PWM, WDT                                                          |

| Number of I/O              | 50                                                                          |

| Program Memory Size        | 32KB (32K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | •                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df38124wwv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                   |                              | Pin No.            |                    |                      |                          |                          |                          |        |                                                                                                                                                                                                                                                |

|-------------------|------------------------------|--------------------|--------------------|----------------------|--------------------------|--------------------------|--------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Туре              | Symbol                       | FP-80A<br>TFP-80C  | FP-80B             | TLP-85V              | Pad<br>No. <sup>*1</sup> | Pad<br>No. <sup>*2</sup> | Pad<br>No. <sup>*3</sup> | I/O    | Name and Functions                                                                                                                                                                                                                             |

| Clock             | OSC <sub>1</sub>             | 10                 | 12                 | F2                   | 11                       | 12                       | 10                       | Input  | These pins connect to a                                                                                                                                                                                                                        |

| pins              | OSC <sub>2</sub>             | 9                  | 11                 | E3                   | 10                       | 11                       | 9                        | Output | crystal or ceramic<br>oscillator, or can be used<br>to input an external clock.<br>See section 4, Clock<br>Pulse Generators, for a<br>typical connection<br>diagram.                                                                           |

|                   | X <sub>1</sub>               | 6                  | 8                  | D3                   | 6                        | 7                        | 6                        | Input  | These pins connect to a                                                                                                                                                                                                                        |

|                   | X <sub>2</sub>               | 7                  | 9                  | D2                   | 7                        | 8                        | 7                        | Output | <sup>-</sup> 32.768-kHz or 38.4-kHz <sup>*5</sup><br>crystal oscillator.<br>See section 4, Clock<br>Pulse Generators, for a<br>typical connection<br>diagram.                                                                                  |

| System control    | RES                          | 12                 | 14                 | F3                   | 13                       | 14                       | 12                       | Input  | <b>Reset:</b> When this pin is driven low, the chip is reset                                                                                                                                                                                   |

|                   | TEST                         | 11                 | 13                 | E2                   | 12                       | 13                       | 11                       | Input  | <b>Test pin:</b> This pin is<br>reserved and cannot be<br>used. It should be<br>connected to V <sub>SS</sub> .                                                                                                                                 |

| Interrupt<br>pins | IRQ₀<br>IRQ₁<br>IRQ₃<br>IRQ₄ | 72<br>76<br>5<br>3 | 74<br>78<br>7<br>5 | C5<br>B3<br>D1<br>B2 | 73<br>77<br>5<br>3       | 74<br>78<br>6<br>4       | 72<br>76<br>5<br>3       | Input  | IRQ interrupt request 0,<br>1, 3, and 4: These are<br>input pins for edge-<br>sensitive external<br>interrupts, with a selection<br>of rising or falling edge                                                                                  |

|                   | IRQAEC                       | 60                 | 62                 | C10                  | 61                       | 62                       | 60                       | Input  | Asynchronous event<br>counter event signal:<br>This is an interrupt input<br>pin for enabling<br>asynchronous event<br>input.                                                                                                                  |

|                   |                              |                    |                    |                      |                          |                          |                          |        | On the H8/38124 Group,<br>this must be fixed at $V_{CC}$<br>or GND because the<br>oscillator is selected by<br>the input level during<br>resets. Refer to section 4,<br>Clock Pulse Generators,<br>for information on the<br>selection method. |

Section 2 CPU

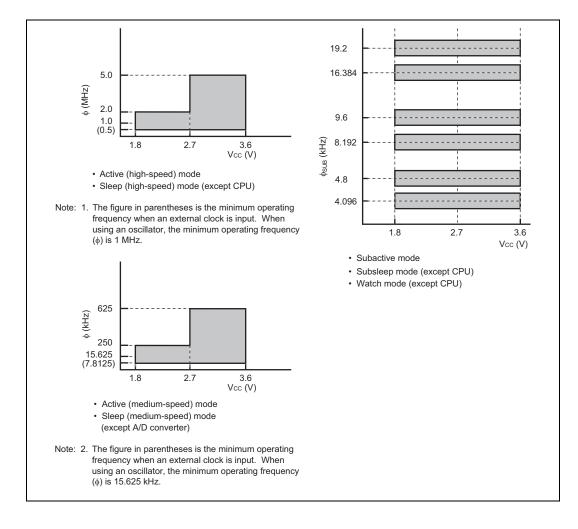

|   | 45      |                                    | 0 | 7 |           |          |    |     | 0 | BSET, BCLR, BNOT, B                                  | TST              |

|---|---------|------------------------------------|---|---|-----------|----------|----|-----|---|------------------------------------------------------|------------------|

|   | 15      | ор                                 | 8 | 7 | IMM       |          | rr | 1   | 0 | Operand: register direct<br>Bit No.: immediate (#2   | t (Rn)<br>xx:3)  |

|   | 15      |                                    | 8 | 7 |           |          |    |     | 0 |                                                      |                  |

|   | 15      | ор                                 |   |   | rm        |          | rr | n ' | 0 | Operand: register direct<br>Bit No.: register direct | t (Rn)<br>t (Rm) |

|   | 15      |                                    | 8 | 7 |           |          |    |     | 0 |                                                      | . ()             |

|   |         | ор                                 |   | , | rn        | 0        | 0  | 0   | 0 | Operand: register indire                             | ect (@Rn)        |

|   |         | ор                                 |   |   | IMM       | 0        | 0  | 0   | 0 | Bit No.: immediate (#2                               | xx:3)            |

|   | 15      |                                    | 8 | 7 |           |          |    |     | 0 |                                                      |                  |

|   |         | ор                                 | 1 | I | rn        | 0        | 0  | 0   | 0 | Operand: register indire                             | ect (@Rn)        |

|   |         | ор                                 |   |   | rm        | 0        | 0  | 0   | 0 | Bit No.: register direct                             | t (Rm)           |

|   | 15      |                                    | 8 | 7 |           |          |    |     | 0 |                                                      |                  |

|   |         | ор                                 |   | 1 | 1         | abs      | '  | I   |   | Operand: absolute (@a                                | a:8)             |

|   |         | ор                                 |   |   | IMM       | 0        | 0  | 0   | 0 | Bit No.: immediate (#2                               | xx:3)            |

|   | 15      |                                    | 8 | 7 |           |          |    |     | 0 |                                                      |                  |

|   |         | ор                                 |   | I | 1 1       | abs      |    | 1   |   | Operand: absolute (@a                                | a:8)             |

|   |         | ор                                 |   |   | rm        | 0        | 0  | 0   | 0 | Bit No.: register direct                             | t (Rm)           |

|   |         |                                    |   |   |           |          |    |     |   | BAND, BOR, BXOR, B                                   | LD, BST          |

| [ | 15      | ор                                 | 8 | 7 | IMM       |          | rr |     | 0 | Operand: register direct                             |                  |

| l |         | 00                                 |   |   |           |          |    | 1   |   | Bit No.: immediate (#                                | xx:3)            |

| [ | 15      |                                    | 8 | 7 |           | 0        | 0  | 0   | 0 | On anomaly an elisten in disc                        |                  |

|   |         | ор                                 |   |   | rn<br>IMM | 0        | 0  | 0   | 0 | Operand: register indire<br>Bit No.: immediate (#2   | (0)              |

| l |         | op                                 |   |   |           | 0        | 0  | 0   | 0 | Bit NO IIIIIIediate (#)                              | (X.3)            |

| [ | 15      |                                    | 8 | 7 |           | abs      |    |     | 0 | Onerendu abaaluta (@a                                | o. 9)            |

|   |         | ор                                 |   |   | IMM       | abs<br>0 | 0  | 0   | 0 | Operand: absolute (@a<br>Bit No.: immediate (#       |                  |

| l |         | 00                                 |   |   |           |          | 0  | 0   | 0 |                                                      | xx.3)            |

|   | [Legend |                                    |   |   |           |          |    |     |   |                                                      |                  |

|   | rm, rn: | Operation field<br>Register field  |   |   |           |          |    |     |   |                                                      |                  |

|   |         | Absolute address<br>Immediate data |   |   |           |          |    |     |   |                                                      |                  |

|   |         |                                    |   |   |           |          |    |     |   |                                                      |                  |

## Bit 4—IRQ<sub>4</sub> Edge Select (IEG4)

Bit 4 selects the input sensing of the  $\overline{IRQ}_4$  pin and  $\overline{ADTRG}$  pin.

| Bit 4 |                                                                                 |                 |

|-------|---------------------------------------------------------------------------------|-----------------|

| IEG4  | Description                                                                     |                 |

| 0     | Falling edge of $\overline{IRQ}_4$ and $\overline{ADTRG}$ pin input is detected | (initial value) |

| 1     | Rising edge of $\overline{IRQ}_4$ and $\overline{ADTRG}$ pin input is detected  |                 |

## Bit 3—IRQ<sub>3</sub> Edge Select (IEG3)

Bit 3 selects the input sensing of the  $\overline{IRQ}_3$  pin and TMIF pin.

| Bit 3<br>IEG3 | Description                                                              |                 |

|---------------|--------------------------------------------------------------------------|-----------------|

| 0             | Falling edge of $\overline{\text{IRQ}}_3$ and TMIF pin input is detected | (initial value) |

| 1             | Rising edge of $\overline{IRQ}_3$ and TMIF pin input is detected         |                 |

#### Bit 2—Reserved

Bit 2 is reserved: it can only be written with 0.

## Bit 1—IRQ1 Edge Select (IEG1)

Bit 1 selects the input sensing of the  $\overline{IRQ}_1$  pin and TMIC pin.

| Bit 1 |                                                                   |                 |

|-------|-------------------------------------------------------------------|-----------------|

| IEG1  | Description                                                       |                 |

| 0     | Falling edge of $\overline{IRQ}_1$ and TMIC pin input is detected | (initial value) |

| 1     | Rising edge of IRQ <sub>1</sub> and TMIC pin input is detected    |                 |

## Bit 0—IRQ<sub>0</sub> Edge Select (IEG0)

Bit 0 selects the input sensing of pin  $\overline{IRQ}_0$ .

| Bit 0<br>IEG0 | Description                                              |                 |

|---------------|----------------------------------------------------------|-----------------|

| 0             | Falling edge of $\overline{IRQ}_0$ pin input is detected | (initial value) |

| 1             | Rising edge of $\overline{IRQ}_0$ pin input is detected  |                 |

#### 3.3.6 Interrupt Response Time

Table 3.4 shows the number of wait states after an interrupt request flag is set until the first instruction of the interrupt handler is executed.

## Table 3.4 Interrupt Wait States

| Item                                                  | States  | Total    |

|-------------------------------------------------------|---------|----------|

| Waiting time for completion of executing instruction* | 1 to 13 | 15 to 27 |

| Saving of PC and CCR to stack                         | 4       |          |

| Vector fetch                                          | 2       |          |

| Instruction fetch                                     | 4       |          |

| Internal processing                                   | 4       |          |

|                                                       |         |          |

Note: \* Not including EEPMOV instruction.

| Bit 3 |                                               |                 |

|-------|-----------------------------------------------|-----------------|

| EV    | Description                                   |                 |

| 0     | Erase-verify mode is cancelled                | (initial value) |

| 1     | The flash memory changes to erase-verify mode |                 |

## Bit 2—Program-Verify (PV)

This bit is to set changing to or cancelling program-verify mode (do not set SWE, ESU, PSU, EV, E, and P bits at the same time).

| Bit 2<br>PV | Description                                     |                 |

|-------------|-------------------------------------------------|-----------------|

| 0           | Program-verify mode is cancelled                | (initial value) |

| 1           | The flash memory changes to program-verify mode |                 |

## Bit 1—Erase (E)

This bit is to set changing to or cancelling erase mode (do not set SWE, ESU, PSU, EV, PV, and P bits at the same time).

#### Bit 1

| E | Description                                                                                |                 |

|---|--------------------------------------------------------------------------------------------|-----------------|

| 0 | Erase mode is cancelled                                                                    | (initial value) |

| 1 | When this bit is set to 1, while the SWE = 1 and ESU = 1, the flash changes to erase mode. | memory          |

## Bit 0—Program (P)

This bit is to set changing to or cancelling program mode (do not set SWE, ESU, PSU, EV, PV, and E bits at the same time).

| Bit 0<br>P | Description                                                                                |                 |

|------------|--------------------------------------------------------------------------------------------|-----------------|

| 0          | Program mode is cancelled                                                                  | (initial value) |

| 1          | When this bit is set to 1, while the SWE = 1 and PSU = 1, the fla changes to program mode. | ash memory      |

This section only deals with the bits related to timer G and the watchdog timer. For the functions of the bits, see the descriptions of port 3 (POF1) and port 4 (IRQ0).

#### Bit 2—Watchdog Timer Source Clock (WDCKS)

This bit selects the watchdog timer source clock. Note that stabilization times for the H8/38024, H8/38024S, and H8/38024R Group and for the H8/38124 Group are different.

#### • H8/38024, H8/38024S, H8/38024R Group

| Bit 2<br>WDCKS | Description         |                 |

|----------------|---------------------|-----------------|

| 0              | Selects ø/8192      | (initial value) |

| 1              | Selects $\phi_W/32$ |                 |

#### • H8/38124 Group

| Bit 2<br>WDCKS | Description                                                              |                 |

|----------------|--------------------------------------------------------------------------|-----------------|

| 0              | Selects clock based on timer mode register W (TMW) setting $\!\!\!\!\!*$ | (initial value) |

| 1              | Selects $\phi_W/32$                                                      |                 |

Note: \* See section 9.6, Watchdog Timer, for details.

#### Bit 1—TMIG Noise Canceller Select (NCS)

This bit selects controls the noise cancellation circuit of the input capture input signal (TMIG).

| Bit 1 |                               |                 |

|-------|-------------------------------|-----------------|

| NCS   | Description                   |                 |

| 0     | No noise cancellation circuit | (initial value) |

| 1     | Noise cancellation circuit    |                 |

## Port Data Register 5 (PDR5)

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | P57 | P56 | P5₅ | P54 | P5₃ | P52 | P51 | P50 |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | R/W |

PDR5 is an 8-bit register that stores data for port 5 pins  $P5_7$  to  $P5_0$ . If port 5 is read while PCR5 bits are set to 1, the values stored in PDR5 are read, regardless of the actual pin states. If port 5 is read while PCR5 bits are cleared to 0, the pin states are read.

Upon reset, PDR5 is initialized to H'00.

## Port Control Register 5 (PCR5)

| Bit           | 7     | 6                 | 5     | 4                 | 3     | 2                 | 1     | 0     |

|---------------|-------|-------------------|-------|-------------------|-------|-------------------|-------|-------|

|               | PCR57 | PCR5 <sub>6</sub> | PCR55 | PCR5 <sub>4</sub> | PCR53 | PCR5 <sub>2</sub> | PCR51 | PCR50 |

| Initial value | 0     | 0                 | 0     | 0                 | 0     | 0                 | 0     | 0     |

| Read/Write    | W     | W                 | W     | W                 | W     | W                 | W     | W     |

PCR5 is an 8-bit register for controlling whether each of the port 5 pins  $P5_7$  to  $P5_0$  functions as an input pin or output pin. Setting a PCR5 bit to 1 makes the corresponding pin an output pin, while clearing the bit to 0 makes the pin an input pin. PCR5 and PDR5 settings are valid when the corresponding pins are designated for general-purpose input/output by PMR5 and bits SGS3 to SGS0 in LPCR.

Upon reset, PCR5 is initialized to H'00.

PCR5 is a write-only register, which is always read as all 1s.

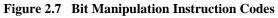

# 16-bit Output Compare Register (OCRF)8-bit Output Compare Register (OCRFH)8-bit Output Compare Register (OCRFL)

OCRF is a 16-bit read/write register composed of the two registers OCRFH and OCRFL. In addition to the use of OCRF as a 16-bit register with OCRFH as the upper 8 bits and OCRFL as the lower 8 bits, OCRFH and OCRFL can also be used as independent 8-bit registers.

OCRFH and OCRFL can be read and written by the CPU, but when they are used in 16-bit mode, data transfer to and from the CPU is performed via a temporary register (TEMP). For details of TEMP, see section 9.4.3, CPU Interface.

OCRFH and OCRFL are each initialized to H'FF upon reset.

a. 16-bit mode (OCRF)

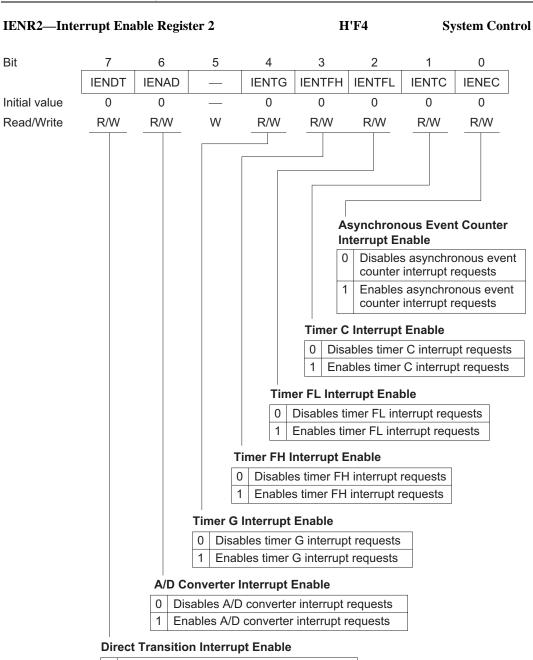

When CKSH2 is cleared to 0 in TCRF, OCRF operates as a 16-bit register. OCRF contents are constantly compared with TCF, and when both values match, CMFH is set to 1 in TCSRF. At the same time, IRRTFH is set to 1 in IRR2. If IENTFH in IENR2 is 1 at this time, an interrupt request is sent to the CPU.

Toggle output can be provided from the TMOFH pin by means of compare matches, and the output level can be set (high or low) by means of TOLH in TCRF.

b. 8-bit mode (OCRFH/OCRFL)

When CKSH2 is set to 1 in TCRF, OCRFH, and OCRFL operate as two independent 8-bit registers. OCRFH contents are compared with TCFH, and OCRFL contents are with TCFL. When the OCRFH (OCRFL) and TCFH (TCFL) values match, CMFH (CMFL) is set to 1 in TCSRF. At the same time, IRRTFH (IRRTFL) is set to 1 in IRR2. If IENTFH (IENTFL) in IENR2 is 1 at this time, an interrupt request is sent to the CPU.

Toggle output can be provided from the TMOFH pin (TMOFL pin) by means of compare matches, and the output level can be set (high or low) by means of TOLH (TOLL) in TCRF.

# Renesas

| Mode                                       | Maximum AEVH/AEVL Pin Input<br>Clock Frequency |                        |  |  |  |

|--------------------------------------------|------------------------------------------------|------------------------|--|--|--|

| Active (high-speed), sleep (high-speed)    | 16 MHz                                         |                        |  |  |  |

| Active (medium-speed), sleep (medium-speed | 2 • fosc                                       |                        |  |  |  |

|                                            | (ф/32)                                         | fosc                   |  |  |  |

|                                            | (\$/64)                                        | 1/2 • f <sub>OSC</sub> |  |  |  |

| $f_{OSC} = 1 \text{ MHz to 4 MHz}$         | (ቀ/128)                                        | 1/4 • f <sub>OSC</sub> |  |  |  |

| Watch, subactive, subsleep, standby        | (¢w/2)                                         | 1000 kHz               |  |  |  |

|                                            | (¢w/4)                                         | 500 kHz                |  |  |  |

| φw = 32.768 kHz or 38.4 kHz*               | (¢w/8)                                         | 250 kHz                |  |  |  |

Note: \* Does not apply to H8/38124 Group.

- 3. When using the clock in the 16-bit mode, set CUEH to 1 first, then set CRCH to 1 in ECCSR. Or, set CUEH and CRCH simultaneously before inputting the clock. After that, do not change the CUEH value while using in the 16-bit mode. Otherwise, an error counter increment may occur. Also, to reset the counter, clear CRCH and CRCL to 0 simultaneously or clear CRCL and CRCH to 0 sequentially, in that order.

- 4. When ECPWME in AEGSR is 1, event counter PWM is operating and therefore ECPWCRH, ECPWCRL, ECPWDRH, and ECPWDRL should not be modified. When changing the data, event counter PWM must be halted by clearing ECPWME to 0 in AEGSR before modifying these registers.

- 5. The event counter PWM data register and event counter PWM compare register must be set so that event counter PWM data register < event counter PWM compare register. If the settings do not satisfy this condition, do not set ECPWME to 1 in AEGSR.

- 6. As synchronization is established internally when an IRQAEC interrupt is generated, a maximum error of 1  $t_{cvc}$  will occur between clock halting and interrupt acceptance.

## Renesas

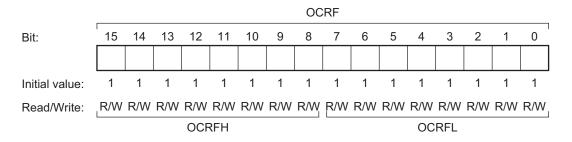

## 10.1.2 Block Diagram

External Internal clock ( $\phi/64$ ,  $\phi/16$ ,  $\phi_W/2$ ,  $\phi$ ) SCK<sub>32</sub> -Baud rate generator clock BRC BRR Clock SMR Internal data bus Transmit/receive SCR3 control circuit SSR TXD<sub>32</sub> O◄ TSR TDR SPCR RXD<sub>32</sub> O-RSR RDR Interrupt request (TEI, TXI, RXI, ERI) [Legend] RSR: Receive shift register RDR: Receive data register TSR: Transmit shift register Transmit data register TDR: Serial mode register SMR: SCR3: Serial control register 3 SSR: Serial status register Bit rate register BRR: Bit rate counter BRC: SPCR: Serial port control register

Figure 10.1 shows a block diagram of SCI3.

## 11.2.3 Clock Stop Register 2 (CKSTPR2)

| Bit           | 7         | 6 | 5 | 4        | 3       | 2       | 1        | 0       |

|---------------|-----------|---|---|----------|---------|---------|----------|---------|

|               | LVDCKSTP* | _ | — | PW2CKSTP | AECKSTP | WDCKSTP | PW1CKSTP | LDCKSTP |

| Initial value | 1         | 1 | 1 | 1        | 1       | 1       | 1        | 1       |

| Read/Write    | R/W       | _ | _ | R/W      | R/W     | R/W     | R/W      | R/W     |

Note: \* Bits 6 and 5 are also reserved on products other than the H8/38124 Group.

CKSTPR2 is an 8-bit read/write register that performs module standby mode control for peripheral modules. Only the bit relating to the PWM is described here. For details of the other bits, see the sections on the relevant modules.

#### Bits 4 and 1—PWM Module Standby Mode Control (PWmCKSTP)

Bits 4 and 1 control setting and clearing of module standby mode for the PWMm.

#### PWmCKSTP Description

| 0 | PWMm is set to module standby mode  |                 |

|---|-------------------------------------|-----------------|

| 1 | PWMm module standby mode is cleared | (initial value) |

## **12.2 Register Descriptions**

## 12.2.1 A/D Result Registers (ADRRH, ADRRL)

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | 7     | 6     | 5   | 4 | 3 | 2 | 1 | 0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-----|---|---|---|---|---|

|               | ADR9  | ADR8  | ADR7  | ADR6  | ADR5  | ADR4  | ADR3  | ADR2  | ADR1  | ADR0  | _   | _ | _ | _ | _ | _ |

| Initial value | Unde- | _   | _ | _ | _ |   | _ |

|               | fined |     |   |   |   |   |   |

| Read/Write    | R     | R     | R     | R     | R     | R     | R     | R     | R     | R     |     | _ | _ | _ | _ | _ |

|               |       |       |       |       | ~     |       |       |       | _     |       |     |   | ~ |   |   |   |

| ADRRH         |       |       |       |       |       |       |       |       |       | AD    | RRL |   |   |   |   |   |

ADRRH and ADRRL together comprise a 16-bit read-only register for holding the results of analog-to-digital conversion. The upper 8 bits of the data are held in ADRRH, and the lower 2 bits in ADRRL.

ADRRH and ADRRL can be read by the CPU at any time, but the ADRRH and ADRRL values during A/D conversion are not fixed. After A/D conversion is complete, the conversion result is stored as 10-bit data, and this data is held until the next conversion operation starts.

ADRRH and ADRRL are not cleared on reset.

## 12.2.2 A/D Mode Register (AMR)

| Bit           | 7   | 6    | 5 | 4 | 3   | 2   | 1   | 0   |

|---------------|-----|------|---|---|-----|-----|-----|-----|

|               | CKS | TRGE | _ |   | CH3 | CH2 | CH1 | CH0 |

| Initial value | 0   | 0    | 1 | 1 | 0   | 0   | 0   | 0   |

| Read/Write    | R/W | R/W  |   |   | R/W | R/W | R/W | R/W |

AMR is an 8-bit read/write register for specifying the A/D conversion speed, external trigger option, and the analog input pins.

Upon reset, AMR is initialized to H'30.

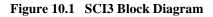

#### Power Supply Voltage and Operating Frequency Range

### **BRR**—Bit Rate Register

#### H'A9

SCI3

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------------|------|------|------|------|------|------|------|------|

|               | BRR7 | BRR6 | BRR5 | BRR4 | BRR3 | BRR2 | BRR1 | BRR0 |

| Initial value | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| Read/Write    | R/W  |

|               |      |      |      |      |      |      |      |      |

Serial transmit/receive bit rate

#### PMR5—Port Mode Register 5

| Bit           |                                                                                         | 7                                      | 6                                                                                                                     | 5                                                                                                                                           | 4                       | 3                | 2                | 1                | 0          |  |  |  |

|---------------|-----------------------------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------|------------------|------------------|------------|--|--|--|

|               | WH                                                                                      | ۲P <sub>7</sub>                        | WKP <sub>6</sub>                                                                                                      | WKP <sub>5</sub>                                                                                                                            | WKP <sub>4</sub>        | WKP <sub>3</sub> | WKP <sub>2</sub> | WKP <sub>1</sub> | WKP0       |  |  |  |

| Initial value | value 0 0 0                                                                             |                                        | 0                                                                                                                     | 0                                                                                                                                           | 0                       | 0                | 0                | 0                |            |  |  |  |

| Read/Write    | R/W                                                                                     |                                        | R/W                                                                                                                   | R/W                                                                                                                                         | R/W                     | R/W              | R/W              | R/W              | R/W        |  |  |  |

|               |                                                                                         |                                        |                                                                                                                       |                                                                                                                                             |                         |                  |                  |                  |            |  |  |  |

|               |                                                                                         |                                        |                                                                                                                       | P5./WK                                                                                                                                      | P./SEG.                 | ⊿ Pin Fun        | ction Swi        | tch              |            |  |  |  |

|               | P5n/WKPn/SEGn+1Pin Function Switch0Functions as P5n I/O pin1Functions as WKPn input pin |                                        |                                                                                                                       |                                                                                                                                             |                         |                  |                  |                  |            |  |  |  |

|               |                                                                                         |                                        |                                                                                                                       |                                                                                                                                             |                         |                  |                  |                  |            |  |  |  |

|               |                                                                                         |                                        |                                                                                                                       |                                                                                                                                             |                         |                  | (n = 7           | to 0)            |            |  |  |  |

|               |                                                                                         |                                        |                                                                                                                       |                                                                                                                                             |                         |                  |                  |                  |            |  |  |  |

| PWCR2—PV      | WM2                                                                                     | Cont                                   | rol Regis                                                                                                             | ter                                                                                                                                         |                         | H                |                  | 10-Bit PW        |            |  |  |  |

|               |                                                                                         |                                        |                                                                                                                       |                                                                                                                                             |                         |                  |                  |                  |            |  |  |  |

| Bit           |                                                                                         | 7                                      | 6                                                                                                                     | 5                                                                                                                                           | 4                       | 3                | 2                | 1                | 0          |  |  |  |

|               | -                                                                                       | -                                      | _                                                                                                                     | —                                                                                                                                           | —                       |                  | PWCR22           | PWCR21           | PWCR20     |  |  |  |

| Initial value |                                                                                         | 1                                      | 1                                                                                                                     | 1                                                                                                                                           | 1                       | 1                | +0               |                  | 0          |  |  |  |

| Read/Write    |                                                                                         |                                        | R/W                                                                                                                   | W                                                                                                                                           |                         |                  |                  |                  |            |  |  |  |

|               |                                                                                         |                                        |                                                                                                                       |                                                                                                                                             |                         |                  |                  |                  |            |  |  |  |

| Г             |                                                                                         |                                        |                                                                                                                       |                                                                                                                                             |                         |                  |                  |                  |            |  |  |  |

|               | С                                                                                       | lock                                   | Select —                                                                                                              |                                                                                                                                             |                         |                  |                  |                  |            |  |  |  |

|               |                                                                                         | 0 0                                    | The inp                                                                                                               | ut clock is                                                                                                                                 | $\phi (t\phi^{*1} = t)$ | 1/ø) The c       | onversion        | period is 5      | 512/φ,     |  |  |  |

|               |                                                                                         |                                        |                                                                                                                       | with a minimum modulation width of $1/2\phi$                                                                                                |                         |                  |                  |                  |            |  |  |  |

|               |                                                                                         | 1                                      | The input clock is $\phi/2$ (t $\phi^{*1} = 2/\phi$ ) The conversion period is 1,024/ $\phi$ , with a minimum method. |                                                                                                                                             |                         |                  |                  |                  |            |  |  |  |

|               |                                                                                         | with a minimum modulation width of 1/¢ |                                                                                                                       |                                                                                                                                             |                         |                  |                  |                  |            |  |  |  |

|               |                                                                                         | 1 0                                    |                                                                                                                       | The input clock is $\phi/4$ (t $\phi^{*1} = 4/\phi$ ) The conversion period is 2,048/ $\phi$ , with a minimum modulation width of 2/ $\phi$ |                         |                  |                  |                  |            |  |  |  |

|               | 1 The input clock is $\phi/8$ (t $\phi^{*1} = 8/\phi$ ) The conversion period is 4,0    |                                        |                                                                                                                       |                                                                                                                                             |                         |                  |                  |                  | s 4,096/φ, |  |  |  |

|               |                                                                                         |                                        |                                                                                                                       | ninimum m                                                                                                                                   |                         |                  |                  |                  |            |  |  |  |

H'CC

**I/O Port**

## PWH Output Select (H8/38124 Group only)

| 0 | 10-bit PWM        |

|---|-------------------|

| 1 | Event counter PWM |

- Notes: 1. to: Period of PWM2 input clock

- 2. 1 on products other than the H8/38124 Group

Note: \* Readable/writable reserved bit in the H8/38024S Group and H8/38124 Group.

- 0 Disables direct transition interrupt requests

- 1 Enables direct transition interrupt requests

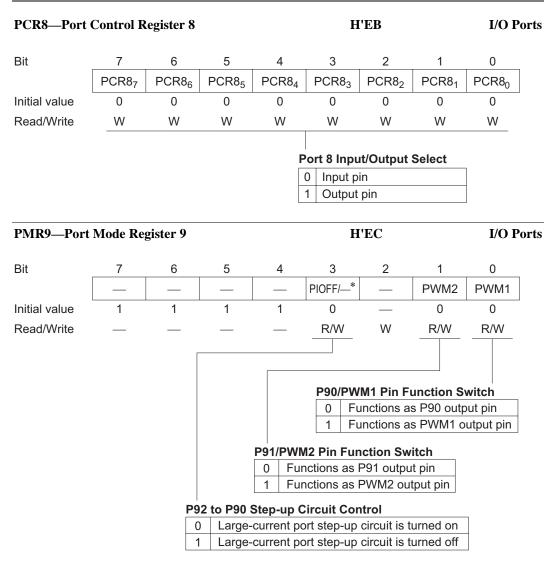

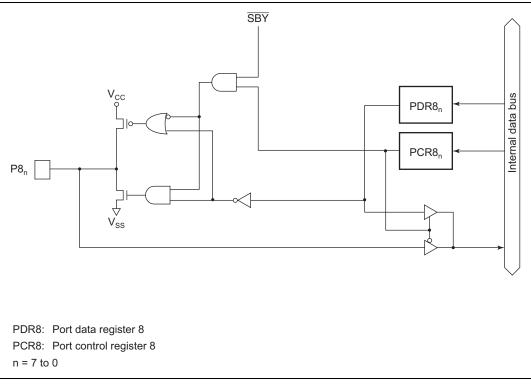

## C.7 Block Diagram of Port 8

Figure C.7 Port 8 Block Diagram

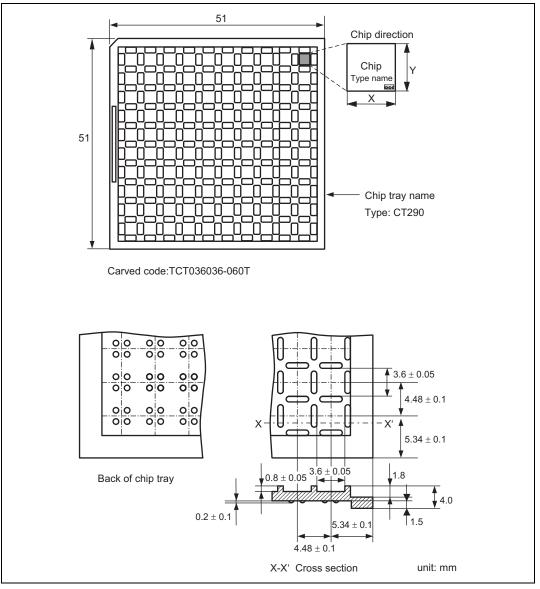

Figure I.3 Specifications of Chip Tray for the HCD64338024S, HCD64338023S, HCD64338022S, HCD64338021S, and HCD64338020S

| 16.6.2 DC       | <b>Page</b><br>492 | Revision (See Manual for Details) Table amended |                    |                 |     |             |           |          |                                                                                                                                             |                                |

|-----------------|--------------------|-------------------------------------------------|--------------------|-----------------|-----|-------------|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Characteristics | 432                |                                                 |                    |                 |     |             |           |          |                                                                                                                                             |                                |

| Table 16.16 DC  |                    | Item                                            | Symbol             | Applicable Pins | Min | Valu<br>Typ | es<br>Max | <br>Unit | Test Condition                                                                                                                              | Notes                          |

| Characteristics |                    | Subactive<br>mode<br>current<br>dissipation     | I <sub>SUB</sub>   | V <sub>cc</sub> | -   | 6.2         | _         | μΑ       | $V_{CC}$ = 1.8 V,<br>LCD on 32 kHz<br>External Clock<br>$(\phi_{SUB}=\phi_w/2)$                                                             | *1<br>*2<br>Reference          |

|                 |                    |                                                 |                    |                 | -   | 5.7         | -         | μΑ       | $V_{CC} = 1.8 \text{ V},$<br>LCD on 32 kHz<br>crystal resonator<br>$(\phi_{SUB}=\varphi_w/2)$                                               | _                              |

|                 |                    |                                                 |                    |                 | -   | 4.4         | _         | μΑ       | $\label{eq:Vcc} \begin{array}{l} V_{CC} = 2.7 \ V, \\ LCD \ on \ 32 \ kHz \\ crystal \ resonator \\ (\phi_{SUB} = \varphi_w/8) \end{array}$ |                                |

|                 |                    |                                                 |                    |                 | _   | 10          | 40        | μΑ       | $V_{CC}$ = 2.7 V,<br>LCD on 32 kHz<br>External Clock<br>$(\phi_{SUB}=\phi_w/2)$                                                             | *1<br>*2                       |

|                 |                    |                                                 |                    |                 | _   | 11          | 40        | μΑ       | $V_{CC}$ = 2.7 V,<br>LCD on 32 kHz<br>crystal resonator<br>( $\phi_{SUB}=\phi_w/2$ )                                                        |                                |

|                 |                    | Subsleep<br>mode<br>current<br>dissipation      | I <sub>SUBSP</sub> | V <sub>cc</sub> | _   | 4.8         | 16.0      | μΑ       | $V_{CC}$ = 2.7 V,<br>LCD on 32 kHz<br>External Clock<br>( $\phi_{SUB}=\phi_w/2$ )                                                           | *1<br>*2                       |

|                 |                    |                                                 |                    |                 | -   | 5.1         | 16.0      | μΑ       | $V_{CC}$ = 2.7 V,<br>LCD on 32 kHz<br>crystal resonator<br>( $\phi_{SUB}=\phi_w/2$ )                                                        | -                              |

|                 |                    | Watch<br>mode<br>current<br>dissipation         | Iwatch             | V <sub>cc</sub> | _   | 1.2         | -         | μΑ       | $V_{CC}$ = 1.8 V,<br>$T_a$ = 25°C<br>32 kHz crystal<br>oscillator<br>LCD not used                                                           | *1<br>*2<br>Reference<br>value |

|                 |                    |                                                 |                    |                 | _   | 2.0         | _         | μΑ       | $V_{CC} = 2.7 V,$<br>$T_a = 25^{\circ}C$<br>32  kHz External<br>Clock<br>LCD not used                                                       |                                |

#### Table amended

| Symbol             | Applicable Pins | Values |                                                                                       |                                                                                                                                           |                                                                                                                                                                             |                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------|-----------------|--------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |                 | Min    | Тур                                                                                   | Max                                                                                                                                       | Unit                                                                                                                                                                        | Test Condition                                                                                                                                                                                                 | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| I <sub>WATCH</sub> | V <sub>cc</sub> | _      | 2.3                                                                                   | _                                                                                                                                         | μA                                                                                                                                                                          | $V_{CC}$ = 2.7 V,<br>$T_a$ = 25°C<br>32 kHz crystal<br>resonator<br>LCD not used                                                                                                                               | *1<br>*2<br>Reference<br>value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                    |                 | -      | 2.0                                                                                   | 6.0                                                                                                                                       | μΑ                                                                                                                                                                          | V <sub>CC</sub> = 2.7 V,<br>32 kHz External<br>Clock<br>LCD not used                                                                                                                                           | *1<br>*2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    |                 | -      | 2.3                                                                                   | 6.0                                                                                                                                       | μΑ                                                                                                                                                                          | V <sub>CC</sub> = 2.7 V,<br>32 kHz crystal<br>resonator<br>LCD not used                                                                                                                                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    |                 | ,      | Symbol         Applicable Pins         Min           I <sub>WATCH</sub> Vcc         — | Symbol         Applicable Pins         Min         Тур           I <sub>WATCH</sub> V <sub>CC</sub> —         2.3           —         2.0 | Symbol         Applicable Pins         Min         Тур         Max           I <sub>WATCH</sub> V <sub>CC</sub> —         2.3         —           —         2.0         6.0 | Symbol         Applicable Pins         Min         Typ         Max         Unit           I <sub>WATCH</sub> V <sub>CC</sub> —         2.3         —         μA           —         2.0         6.0         μA | Symbol         Applicable Pins         Min         Typ         Max         Unit         Test Condition           I <sub>WATCH</sub> V <sub>CC</sub> —         2.3         —         µA         V <sub>CC</sub> = 2.7 V,<br>T <sub>s</sub> = 25°C<br>32 kHz crystal<br>resonator<br>LCD not used           —         2.0         6.0         µA         V <sub>CC</sub> = 2.7 V,<br>32 kHz crystal<br>resonator<br>LCD not used           —         2.0         6.0         µA         V <sub>CC</sub> = 2.7 V,<br>32 kHz crystal<br>resonator<br>LCD not used           —         2.3         6.0         µA         V <sub>CC</sub> = 2.7 V,<br>32 kHz crystal<br>resonator |