#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | H8/300L                                                                        |

| Core Size                  | 8-Bit                                                                          |

| Speed                      | 5MHz                                                                           |

| Connectivity               | SCI                                                                            |

| Peripherals                | LCD, PWM, WDT                                                                  |

| Number of I/O              | 51                                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                    |

| Data Converters            | A/D 8x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 80-BQFP                                                                        |

| Supplier Device Package    | 80-QFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd64f38024rdv |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The revision list can be viewed directly by clicking the title page. The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

# H8/38024, H8/38024S, H8/38024R, H8/38124 Group

Hardware Manual Renesas 8-Bit Single-Chip Microcomputer H8 Family/H8/300L Super Low Power Series

| H8/38024 Group  | H8/38024<br>H8/38023 | H8/38024R Group | H8/38024R |

|-----------------|----------------------|-----------------|-----------|

|                 | H8/38022             | H8/38124 Group  | H8/38124  |

|                 | H8/38021             |                 | H8/38123  |

|                 | H8/38020             |                 | H8/38122  |

| H8/38024S Group | H8/38024S            |                 | H8/38121  |

|                 | H8/38022S            |                 | H8/38120  |

|                 | H8/38021S            |                 |           |

|                 | H8/38020S            |                 |           |

|                 | H8/38000S            |                 |           |

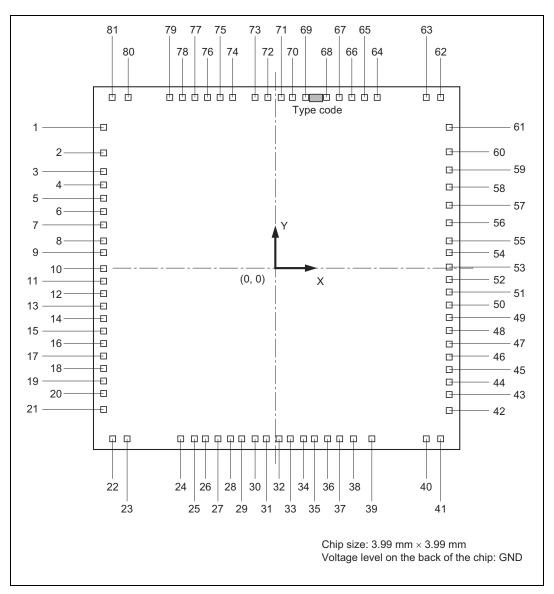

Figure 1.5 Bonding Pad Location Diagram of HCD64338024, HCD64338023, HCD64338022, HCD64338021, and HCD64338020 (Top View)

#### 2.3.1 Data Formats in General Registers

Data of all the sizes above can be stored in general registers as shown in figure 2.3.

| Data Type F                                                                               | Register            | No.       |      |          |      |        |        | 0        | Data     | Form     | at   |          |      |        |             |          |          |

|-------------------------------------------------------------------------------------------|---------------------|-----------|------|----------|------|--------|--------|----------|----------|----------|------|----------|------|--------|-------------|----------|----------|

| 1-bit data                                                                                | RnH                 | 7         | 6    | 5        | 4    | 3      | 2      | 1        | 0        | ]        |      |          | Don' | t care | •           |          |          |

| 1-bit data                                                                                | RnL                 |           |      |          | Don' | t care | )      |          |          | 7        | 6    | 5        | 4    | 3      | 2           | 1        | 0        |

| Byte data                                                                                 | RnH                 | 7<br>MSB  | 1    | 1        | 1    | 1      | 1      | 1        | 0<br>LSB | ]        |      |          | Don' | t care | •           |          |          |

| Byte data                                                                                 | RnL                 |           |      |          | Don' | t care | 9      |          |          | 7<br>MSB | 1    | 1        | 1    | 1      | 1           | 1        | 0<br>LSB |

| Word data                                                                                 | Rn                  | 15<br>MSB |      | 1        | 1    | 1      | 1      | 1        | 1        |          | 1    | 1        | 1    | 1      | 1           | 1        | 0<br>LSB |

| 4-bit BCD data                                                                            | RnH                 | 7         | Uppe | er digit | 4    | 3      | Lowe   | er digit | 0        | ]        |      |          | Don' | t care | • • • • • • |          |          |

| 4-bit BCD data                                                                            | RnL                 |           |      |          | Don' | t care | )<br>) |          |          | 7        | Uppe | er digit | 4    | 3      | Lowe        | er digit | 0        |

| [Legend]<br>RnH: Upper byte<br>RnL: Lower byte<br>MSB: Most signifi<br>LSB: Least signifi | of gene<br>cant bit | ral reg   |      |          |      |        |        |          |          |          |      |          |      |        |             |          |          |

Figure 2.3 Register Data Formats

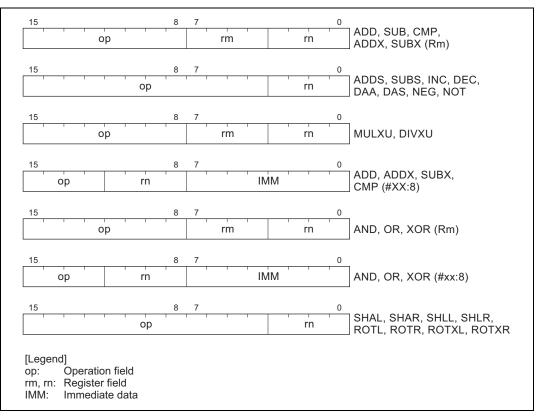

Figure 2.6 shows the instruction code format of arithmetic, logic, and shift instructions.

Figure 2.6 Arithmetic, Logic, and Shift Instruction Codes

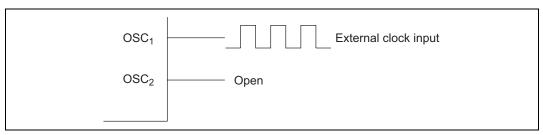

#### External Clock Input Method

Connect an external clock signal to pin  $OSC_1$ , and leave pin  $OSC_2$  open. Figure 4.7 shows a typical connection.

#### Figure 4.7 External Clock Input (Example)

| Frequency  | Oscillator Clock (¢osc) |  |  |  |  |  |

|------------|-------------------------|--|--|--|--|--|

| Duty cycle | 45% to 55%              |  |  |  |  |  |

#### **On-Chip Oscillator Selection Method (H8/38124 Group Only)**

The on-chip oscillator is selected by setting the IRQAEC pin input level during resets.\* Table 4.3 lists the methods for selecting the system clock oscillator and the on-chip oscillator. The IRQAEC pin input level set during resets must be fixed at  $V_{CC}$  or GND, based on the oscillator to be selected. It is not necessary to connect an oscillator to pins OSC1 and OSC2 if the on-chip oscillator is selected. In this case, pin OSC1 should be fixed at  $V_{CC}$  or GND.

- Note: The system clock oscillator must be selected in order to program or erase flash memory as part of operations such as on-board programming. Also, when using the on-chip emulator, an oscillator should be connected, or an external clock input, even if the on-chip oscillator is selected.

- \* Other than watchdog timer or low-voltage detect circuit reset.

#### Table 4.3 System Clock Oscillator and On-Chip Oscillator Selection Methods

| IRQAEC pin input level (during resets) | 0        | 1        |

|----------------------------------------|----------|----------|

| System clock oscillator                | Enabled  | Disabled |

| On-chip oscillator                     | Disabled | Enabled  |

On the H8/38124 Group, operates only when the on-chip oscillator is selected; otherwise stops and stands by. On the H8/38024, H8/38024S, and H8/38024R Group, stops and stands by.

#### 5.1.1 System Control Registers

The operation mode is selected using the system control registers described in table 5.3.

#### Table 5.3 System Control Registers

| Name                      | Abbreviation | R/W | Initial Value | Address |

|---------------------------|--------------|-----|---------------|---------|

| System control register 1 | SYSCR1       | R/W | H'07          | H'FFF0  |

| System control register 2 | SYSCR2       | R/W | H'F0          | H'FFF1  |

#### System Control Register 1 (SYSCR1)

| Bit           | 7    | 6    | 5    | 4    | 3    | 2 | 1   | 0   |

|---------------|------|------|------|------|------|---|-----|-----|

|               | SSBY | STS2 | STS1 | STS0 | LSON |   | MA1 | MA0 |

| Initial value | 0    | 0    | 0    | 0    | 0    | 1 | 1   | 1   |

| Read/Write    | R/W  | R/W  | R/W  | R/W  | R/W  |   | R/W | R/W |

SYSCR1 is an 8-bit read/write register for control of the power-down modes.

Upon reset, SYSCR1 is initialized to H'07.

#### Bit 7—Software Standby (SSBY)

This bit designates transition to standby mode or watch mode.

| Bit 7<br>SSBY | Description                                                                                               |

|---------------|-----------------------------------------------------------------------------------------------------------|

| 0             | • When a SLEEP instruction is executed in active mode, (initial value) a transition is made to sleep mode |

|               | • When a SLEEP instruction is executed in subactive mode, a transition is made to subsleep mode           |

| 1             | • When a SLEEP instruction is executed in active mode, a transition is made to standby mode or watch mode |

|               | When a SLEEP instruction is executed in subactive mode, a transition is made to watch mode                |

| Bit 2<br>MSON | Description                             |                 |

|---------------|-----------------------------------------|-----------------|

| 0             | Operation in active (high-speed) mode   | (initial value) |

| 1             | Operation in active (medium-speed) mode |                 |

#### Bits 1 and 0—Subactive Mode Clock Select (SA1, SA0)

These bits select the CPU clock rate ( $\phi_W/2$ ,  $\phi_W/4$ , or  $\phi_W/8$ ) in subactive mode. SA1 and SA0 cannot be modified in subactive mode.

| Bit 1<br>SA1 | Bit 0<br>SA0 | Description       |                 |

|--------------|--------------|-------------------|-----------------|

| 0            | 0            | φ <sub>W</sub> /8 | (initial value) |

| 0            | 1            | φ <sub>W</sub> /4 |                 |

| 1            | *            | φ <sub>W</sub> /2 |                 |

|              |              |                   | *: Don't care   |

5.2 Sleep Mode

#### 5.2.1 Transition to Sleep Mode

1. Transition to sleep (high-speed) mode

The system goes from active mode to sleep (high-speed) mode when a SLEEP instruction is executed while the SSBY and LSON bits in SYSCR1 are cleared to 0, the MSON and DTON bits in SYSCR2 are cleared to 0. In sleep mode CPU operation is halted but the on-chip peripheral functions. CPU register contents are retained.

2. Transition to sleep (medium-speed) mode

The system goes from active mode to sleep (medium-speed) mode when a SLEEP instruction is executed while the SSBY and LSON bits in SYSCR1 are cleared to 0, the MSON bit in SYSCR2 is set to 1, and the DTON bit in SYSCR2 is cleared to 0. In sleep (medium-speed) mode, as in sleep (high-speed) mode, CPU operation is halted but the on-chip peripheral functions are operational. The clock frequency in sleep (medium-speed) mode is determined by the MA1 and MA0 bits in SYSCR1. CPU register contents are retained.

Furthermore, it sometimes acts with half state early timing at the time of transition to sleep (medium-speed) mode.

## 5.5 Subsleep Mode

## 5.5.1 Transition to Subsleep Mode

The system goes from subactive mode to subsleep mode when a SLEEP instruction is executed while the SSBY bit in SYSCR1 is cleared to 0, LSON bit in SYSCR1 is set to 1, and TMA3 bit in TMA is set to 1. In subsleep mode, operation of on-chip peripheral modules other than the A/D converter and PWM is in active state. As long as a minimum required voltage is applied, the contents of CPU registers, the on-chip RAM and some registers of the on-chip peripheral modules are retained. I/O ports keep the same states as before the transition.

### 5.5.2 Clearing Subsleep Mode

Subsleep mode is cleared by an interrupt (timer A, timer C, timer F, timer G, asynchronous event counter, SCI3, IRQAEC, IRQ<sub>4</sub>, IRQ<sub>3</sub>, IRQ<sub>1</sub>, IRQ<sub>0</sub>, WKP<sub>7</sub> to WKP<sub>0</sub>) or by a low input at the  $\overline{\text{RES}}$  pin.

• Clearing by interrupt

When an interrupt is requested, subsleep mode is cleared and interrupt exception handling starts. Subsleep mode is not cleared if the I bit of CCR is set to 1 or the particular interrupt is disabled in the interrupt enable register.

To synchronize the interrupt request signal with the system clock, up to  $2/\phi_{SUB}(s)$  delay may occur after the interrupt request signal occurrence, before the interrupt exception handling start.

• Clearing by RES input

Clearing by  $\overline{\text{RES}}$  pin is the same as for standby mode; see Clearing by  $\overline{\text{RES}}$  pin in section 5.3.2, Clearing Standby Mode.

| Pin                                    | Pin Functions and Selection Method                                                                                                                           |                                          |                           |                |  |  |  |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------------------|----------------|--|--|--|--|--|

| PB <sub>1</sub> /AN <sub>1</sub> /extU | Switching is accomplished by combining CH3 to CH0 in AMR and VINTUSEL in LVDCR as shown below. Note that VINTUSEL is implemented on the H8/38124 Group only. |                                          |                           |                |  |  |  |  |  |

|                                        | VINTUSEL                                                                                                                                                     | (                                        | )                         | 1              |  |  |  |  |  |

|                                        | CH3 to CH0                                                                                                                                                   |                                          |                           | *              |  |  |  |  |  |

|                                        | Pin function                                                                                                                                                 |                                          |                           | extU input pin |  |  |  |  |  |

|                                        | Note: The extU pin                                                                                                                                           | is implemented on t                      | he H8/38124 Group         | only.          |  |  |  |  |  |

| PB <sub>0</sub> /AN <sub>0</sub> /extD | • •                                                                                                                                                          | lished by combining elow. Note that VINT |                           |                |  |  |  |  |  |

|                                        | VINTDSEL                                                                                                                                                     | (                                        | )                         | 1              |  |  |  |  |  |

|                                        | CH3 to CH0                                                                                                                                                   | Not B'0100                               | B'0100                    | *              |  |  |  |  |  |

|                                        | Pin function                                                                                                                                                 | PB <sub>0</sub> input pin                | AN <sub>0</sub> input pin | extD input pin |  |  |  |  |  |

|                                        | Note: The extD pin is implemented on the H8/38124 Group only.                                                                                                |                                          |                           |                |  |  |  |  |  |

\*: Don't care

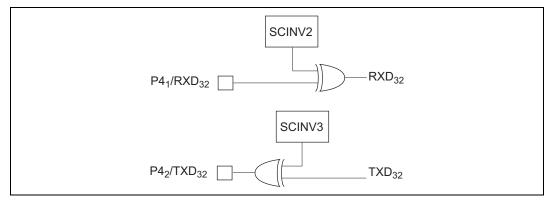

## 8.12 Input/Output Data Inversion Function

#### 8.12.1 Overview

With input pin RXD<sub>32</sub> and output pin TXD<sub>32</sub>, the data can be handled in inverted form.

Figure 8.11 Input/Output Data Inversion Function

#### 9.2.4 Timer A Operation States

Table 9.3 summarizes the timer A operation states.

## Table 9.3 Timer A Operation States

| Oper | ation Mode      | Reset | Active    | Sleep     | Watch     | Sub-<br>active | Sub-<br>sleep | Standby  | Module<br>Standby |

|------|-----------------|-------|-----------|-----------|-----------|----------------|---------------|----------|-------------------|

| TCA  | Interval        | Reset | Functions | Functions | Halted    | Halted         | Halted        | Halted   | Halted            |

|      | Clock time base | Reset | Functions | Functions | Functions | Functions      | Functions     | Halted   | Halted            |

| TMA  |                 | Reset | Functions | Retained  | Retained  | Functions      | Retained      | Retained | Retained          |

Note: When the real-time clock time base function is selected as the internal clock of TCA in active mode or sleep mode, the internal clock is not synchronous with the system clock, so it is synchronized by a synchronizing circuit. This may result in a maximum error of 1/φ (s) in the count cycle.

## 9.2.5 Application Note

When bit 0 (TACKSTP) of the clock stop register 1 (CKSTPR1) is cleared to 0, bit 3 (TMA3) of the timer mode register A (TMA) cannot be rewritten.

Set bit 0 (TACKSTP) of the clock stop register 1 (CKSTPR1) to 1 before rewriting bit 3 (TMA3) of the timer mode register A (TMA).

#### **10.1.3** Pin Configuration

Table 10.1 shows the SCI3 pin configuration.

#### Table 10.1 Pin Configuration

| Name                      | Abbr.             | I/O    | Function                  |

|---------------------------|-------------------|--------|---------------------------|

| SCI3 clock                | SCK <sub>32</sub> | I/O    | SCI3 clock input/output   |

| SCI3 receive data input   | RXD <sub>32</sub> | Input  | SCI3 receive data input   |

| SCI3 transmit data output | TXD <sub>32</sub> | Output | SCI3 transmit data output |

#### 10.1.4 Register Configuration

Table 10.2 shows the SCI3 register configuration.

#### Table 10.2 Registers

| Name                         | Abbr.   | R/W       | Initial Value | Address |

|------------------------------|---------|-----------|---------------|---------|

| Serial mode register         | SMR     | R/W       | H'00          | H'FFA8  |

| Bit rate register            | BRR     | R/W       | H'FF          | H'FFA9  |

| Serial control register 3    | SCR3    | R/W       | H'00          | H'FFAA  |

| Transmit data register       | TDR     | R/W       | H'FF          | H'FFAB  |

| Serial status register       | SSR     | R/W       | H'84          | H'FFAC  |

| Receive data register        | RDR     | R         | H'00          | H'FFAD  |

| Transmit shift register      | TSR     | Protected |               | _       |

| Receive shift register       | RSR     | Protected | —             | _       |

| Bit rate counter             | BRC     | Protected | _             | _       |

| Clock stop register 1        | CKSTPR1 | R/W       | H'FF          | H'FFFA  |

| Serial port control register | SPCR    | R/W       | _             | H'FF91  |

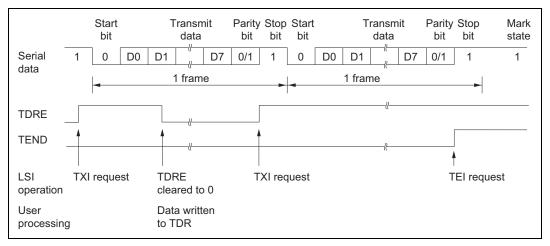

SCI3 operates as follows when transmitting data.

SCI3 monitors bit TDRE in SSR, and when it is cleared to 0, recognizes that data has been written to TDR and transfers data from TDR to TSR. It then sets bit TDRE to 1 and starts transmitting. If bit TIE in SCR3 is set to 1 at this time, a TXI request is made.

Serial data is transmitted from the  $TXD_{32}$  pin using the relevant data transfer format in table 10.11. When the stop bit is sent, SCI3 checks bit TDRE. If bit TDRE is cleared to 0, SCI3 transfers data from TDR to TSR, and when the stop bit has been sent, starts transmission of the next frame. If bit TDRE is set to 1, bit TEND in SSR bit is set to 1 the mark state, in which 1s are transmitted, is established after the stop bit has been sent. If bit TEIE in SCR3 is set to 1 at this time, a TEI request is made.

Figure 10.7 shows an example of the operation when transmitting in asynchronous mode.

Figure 10.7 Example of Operation when Transmitting in Asynchronous Mode (8-bit data, parity, 1 stop bit)

## Renesas

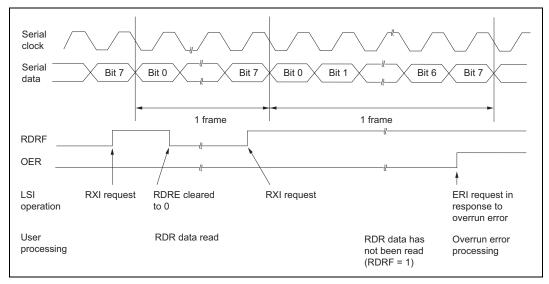

SCI3 operates as follows when receiving data.

SCI3 performs internal synchronization and begins reception in synchronization with the serial clock input or output.

The received data is placed in RSR in LSB-to-MSB order.

After the data has been received, SCI3 checks that bit RDRF is set to 0, indicating that the receive data can be transferred from RSR to RDR.

If this check shows that there is no overrun error, bit RDRF is set to 1, and the receive data is stored in RDR. If bit RIE is set to 1 in SCR3, an RXI interrupt is requested. If the check identifies an overrun error, bit OER is set to 1.

Bit RDRF remains set to 1. If bit RIE is set to 1 in SCR3, an ERI interrupt is requested.

See table 10.12 for the conditions for detecting a receive error, and receive data processing.

Note: No further receive operations are possible while a receive error flag is set. Bits OER, FER, PER, and RDRF must therefore be cleared to 0 before resuming reception.

Figure 10.14 shows an example of the operation when receiving in synchronous mode.

Figure 10.14 Example of Operation when Receiving in Synchronous Mode

| Section 16 | <b>Electrical Characteristics</b> |

|------------|-----------------------------------|

|------------|-----------------------------------|

|                              |                                             |                                                 |                            | Value                  | es                       |                 |        |                     |                                            |             |

|------------------------------|---------------------------------------------|-------------------------------------------------|----------------------------|------------------------|--------------------------|-----------------|--------|---------------------|--------------------------------------------|-------------|

| em                           | Symbol                                      | Applicable Pins                                 | Min                        | Тур                    | Мах                      | [               | Unit   | Test C              | Condition                                  | Notes       |

| llowable                     | <u> </u>                                    | All output pins                                 | _                          | _                      | 15.0                     |                 | mA     | V <sub>CC</sub> = 4 | 4.0 V to 5.5 V                             |             |

| utput hig<br>urrent<br>otal) | Jh                                          |                                                 | _                          | _                      | 10.0                     |                 |        | Excep               | t the above                                |             |

| lotes: C                     | Connect the                                 | TEST pin to V                                   | ss.                        |                        |                          |                 |        |                     |                                            |             |

| 1                            | 1. Applies t                                | o the Mask RO                                   | M products                 | S.                     |                          |                 |        |                     |                                            |             |

| 2                            | 2. Applies t                                | to the HD64738                                  | 024.                       |                        |                          |                 |        |                     |                                            |             |

| 3                            | <ol><li>Pin state</li></ol>                 | es during curren                                | t measurer                 | ment.                  |                          |                 |        |                     |                                            |             |

|                              |                                             | RES                                             |                            |                        | (                        | Other           | LCD    | Power               |                                            |             |

| 1                            | Mode                                        | Pin                                             | Internal St                | ate                    |                          | Pins            | Supp   | ly                  | Oscillator F                               | Pins        |

|                              | Active (high-s<br>mode (I <sub>OPE1</sub> ) | speed) $V_{cc}$                                 | Operates                   |                        | ,                        | V <sub>cc</sub> | Halte  | Ł                   | System cloo<br>crystal                     | k oscillato |

|                              | Active (mediu<br>speed) mode                |                                                 | _                          |                        |                          |                 |        |                     | Subclock oscil<br>Pin X <sub>1</sub> = GND |             |

| 5                            | Sleep mode                                  | V <sub>cc</sub>                                 | Only timers                | operat                 | e '                      | V <sub>cc</sub> | Halte  | d                   | _                                          |             |

| Ś                            | Subactive mo                                | ode V <sub>cc</sub>                             | Operates                   |                        | '                        | V <sub>cc</sub> | Halte  | b                   | System cloc                                | k oscillato |

| Ś                            | Subsleep mo                                 | de V <sub>cc</sub>                              | Only timers                | Only timers operate, V |                          |                 | Halte  | b                   | crystal                                    |             |

|                              |                                             |                                                 | CPU stops                  |                        |                          |                 |        |                     | Subclock os                                | scillator:  |

| Ň                            | Watch mode                                  | V <sub>cc</sub>                                 | Only time b<br>operates, C |                        |                          | V <sub>cc</sub> | Halte  | d                   | crystal                                    |             |

| \$                           | Standby mod                                 | andby mode V <sub>CC</sub> CPU and time<br>stop |                            | mers bo                | ers both V <sub>cc</sub> |                 | Halted |                     | System cloc<br>crystal                     | k oscillato |

|                              |                                             |                                                 |                            |                        |                          |                 |        |                     | Subclock os<br>Pin $X_1 = GN$              |             |

- 4. Excludes current in pull-up MOS transistors and output buffers.

- 5. When the PIOFF bit in the port mode register 9 is 0.

- 6. When the PIOFF bit in the port mode register 9 is 1.

|                                    |                 |                                                                                                                                                                                                                                                |     | Valu | es   |      |                                                                                                                                            |       |

|------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Item                               | Symbol          | Applicable Pins                                                                                                                                                                                                                                | Min | Тур  | Max  | Unit | Test Condition                                                                                                                             | Notes |

| Output low<br>voltage              | Vol             | $\begin{array}{c} P1_3, P1_4, \\ P1_6, P1_7, \\ P3_0 \mbox{ to } P3_7, \\ P4_0 \mbox{ to } P4_2, \\ P5_0 \mbox{ to } P5_7, \\ P6_0 \mbox{ to } P6_7, \\ P7_0 \mbox{ to } P6_7, \\ P8_0 \mbox{ to } P8_7, \\ PA_0 \mbox{ to } PA_3 \end{array}$ | _   |      | 0.5  | V    | I <sub>OL</sub> = 0.4 mA                                                                                                                   |       |

|                                    |                 | P9 <sub>0</sub> to P9 <sub>2</sub>                                                                                                                                                                                                             | _   | _    | 0.5  | V    | I <sub>OL</sub> = 25 mA                                                                                                                    | *1    |

|                                    |                 |                                                                                                                                                                                                                                                |     |      |      |      | I <sub>OL</sub> = 10 mA                                                                                                                    | *2    |

|                                    |                 | P9 <sub>3</sub> to P9 <sub>5</sub>                                                                                                                                                                                                             | —   | —    | 0.5  | V    | I <sub>OL</sub> = 10 mA                                                                                                                    |       |

| Input/output<br>leakage<br>current | I <sub>IL</sub> | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                                                                                                                                                          |     | _    | 1.0  | μA   | $V_{IN} = 0.5 V to$<br>$V_{CC} - 0.5 V$                                                                                                    |       |

|                                    |                 | $PB_0$ to $PB_7$                                                                                                                                                                                                                               | _   |      | 1.0  | μA   | $V_{IN} = 0.5 \text{ V to}$<br>AV <sub>CC</sub> - 0.5 V                                                                                    |       |

| Pull-up<br>MOS<br>current          | −I <sub>p</sub> | P1 <sub>3</sub> , P1 <sub>4</sub> ,<br>P1 <sub>6</sub> , P1 <sub>7</sub> ,<br>P3 <sub>0</sub> to P3 <sub>7</sub> ,<br>P5 <sub>0</sub> to P5 <sub>7</sub> ,<br>P6 <sub>0</sub> to P6 <sub>7</sub>                                               | 30  | _    | 180  | μA   | $\label{eq:Vcc} \begin{array}{l} V_{CC}=3~V,\\ V_{IN}=0~V \end{array}$                                                                     |       |

| Input<br>capacitance               | C <sub>IN</sub> | All input pins<br>except power<br>supply and<br>IRQAEC                                                                                                                                                                                         | _   | _    | 15.0 | pF   | $\label{eq:relation} \begin{split} f &= 1 \text{ MHz}, \\ V_{\text{IN}} &= 0 \text{ V}, \\ T_{\text{a}} &= 25^{\circ}\text{C} \end{split}$ |       |

|                                    |                 | IRQAEC                                                                                                                                                                                                                                         | _   | —    | 30.0 | pF   | -                                                                                                                                          |       |

## Table A.2 Operation Code Map

|      | 2.<br>7.<br>7. |            |        | × . |         |        |             | <i></i> |      | 4 | · |    | <br>2        |     |

|------|----------------|------------|--------|-----|---------|--------|-------------|---------|------|---|---|----|--------------|-----|

|      | 1000 A         |            |        |     |         |        | 1<br>2<br>3 |         |      |   |   |    |              |     |

|      |                |            |        |     | 10      |        |             |         |      |   |   |    |              |     |

| 2    | 12             |            |        |     | 170     |        | 9<br>9      |         |      |   |   |    |              |     |

| 7    | 944            | <i>?</i> : |        |     | 200     | 1000   |             |         |      |   |   |    |              |     |

| <br> |                | 1227       |        |     | 000     |        |             |         |      |   |   |    |              |     |

| 2    | 0000           | ių.        |        |     |         | 2      |             |         |      |   |   |    |              |     |

| · .  |                |            |        |     |         |        |             |         |      |   |   |    | Ż            | 9   |

| 17   | 22             | 14<br>17   | ,<br>, |     |         |        |             | 000     | 2000 |   | 之 | 1. | <br>-<br>- 2 | 200 |

| ÷.   | - 0            | 4          |        |     | 77      |        | N.<br>X.    |         |      |   |   |    |              |     |

| 1    | Ż              | 22         |        |     | 100     |        |             |         |      |   |   |    |              |     |

| ×.   |                | 0000       |        |     | AN.     |        |             |         |      |   |   |    |              |     |

| 4    |                | 6          |        |     | - 22    |        |             |         |      |   |   |    |              |     |

| \$   | 100            | - 1970     |        |     |         |        |             |         |      |   |   |    |              |     |

| ç.   | 1000           |            |        |     |         | 2<br>2 |             |         |      |   |   |    |              |     |

| .*.  | 194<br>194     | 12         |        |     | 97<br>4 |        | 2           |         |      |   |   |    |              |     |

| Instruction | Mnemonic                               | Instruction<br>Fetch<br>I | Branch<br>Addr. Read<br>J | Stack<br>Operation<br>K | Byte Data<br>Access<br>L | Word Data<br>Access<br>M | Internal<br>Operation<br>N |

|-------------|----------------------------------------|---------------------------|---------------------------|-------------------------|--------------------------|--------------------------|----------------------------|

| MOV         | MOV.W Rs, @Rd                          | 1                         | J                         | n                       | L                        | 1                        | N                          |

| IVIO V      | MOV.W Rs, @Ru<br>MOV.W Rs, @(d:16, Rd) | 2                         |                           |                         |                          | 1                        |                            |

|             | MOV.W Rs, @(d. 10, Rd)                 | 2                         |                           |                         |                          | 1                        | 2                          |

|             | MOV.W Rs, @-Ru<br>MOV.W Rs, @aa:16     | 2                         |                           |                         |                          | 1                        | 2                          |

| MULXU       | MULXU.B Rs, Rd                         | 1                         |                           |                         |                          | 1                        | 12                         |

| NEG         | NEG.B Rd                               | 1                         |                           |                         |                          |                          | 12                         |

| NOP         | NOP                                    | 1                         |                           |                         |                          |                          |                            |

| NOF         | NOF<br>NOT.B Rd                        | 1                         |                           |                         |                          |                          |                            |

| OR          | OR.B #xx:8, Rd                         | 1                         |                           |                         |                          |                          |                            |

| UK          | OR.B #XX.0, Ru<br>OR.B Rs, Rd          | 1                         |                           |                         |                          |                          |                            |

| ORC         |                                        |                           |                           |                         |                          |                          |                            |

|             | ORC #xx:8, CCR                         | 1                         |                           |                         |                          |                          |                            |

| ROTL        | ROTL.B Rd                              | 1                         |                           |                         |                          |                          |                            |

| ROTR        | ROTR.B Rd                              | 1                         |                           |                         |                          |                          |                            |

| ROTXL       | ROTXL.B Rd                             | 1                         |                           |                         |                          |                          |                            |

| ROTXR       | ROTXR.B Rd                             | 1                         |                           |                         |                          |                          |                            |

| RTE         | RTE                                    | 2                         |                           | 2                       |                          |                          | 2                          |

| RTS         | RTS                                    | 2                         |                           | 1                       |                          |                          | 2                          |

| SHAL        | SHAL.B Rd                              | 1                         |                           |                         |                          |                          |                            |

| SHAR        | SHAR.B Rd                              | 1                         |                           |                         |                          |                          |                            |

| SHLL        | SHLL.B Rd                              | 1                         |                           |                         |                          |                          |                            |

| SHLR        | SHLR.B Rd                              | 1                         |                           |                         |                          |                          |                            |

| SLEEP       | SLEEP                                  | 1                         |                           |                         |                          |                          |                            |

| STC         | STC CCR, Rd                            | 1                         |                           |                         |                          |                          |                            |

| SUB         | SUB.B Rs, Rd                           | 1                         |                           |                         |                          |                          |                            |

|             | SUB.W Rs, Rd                           | 1                         |                           |                         |                          |                          |                            |

| SUBS        | SUBS.W #1, Rd                          | 1                         |                           |                         |                          |                          |                            |

|             | SUBS.W #2, Rd                          | 1                         |                           |                         |                          |                          |                            |

| POP         | POP Rd                                 | 1                         |                           | 1                       |                          |                          | 2                          |

| PUSH        | PUSH Rs                                | 1                         |                           | 1                       |                          |                          | 2                          |

| SUBX        | SUBX.B #xx:8, Rd                       | 1                         |                           |                         |                          |                          |                            |

|             | SUBX.B Rs, Rd                          | 1                         |                           |                         |                          |                          |                            |

| XOR         | XOR.B #xx:8, Rd                        | 1                         |                           |                         |                          |                          |                            |

|             | XOR.B Rs, Rd                           | 1                         |                           |                         |                          |                          |                            |

| XORC        | XORC #xx:8, CCR                        | 1                         |                           |                         |                          |                          |                            |

## Appendix B Internal I/O Registers

## B.1 Addresses

#### Upper Address: H'F0

| Lower   | Register | Bit Names |       |       |       |       |       |       |       |             |  |  |

|---------|----------|-----------|-------|-------|-------|-------|-------|-------|-------|-------------|--|--|

| Address |          | Bit 7     | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Module Name |  |  |

| H'20    | FLMCR1   |           | SWE   | ESU   | PSU   | EV    | PV    | E     | Р     | ROM         |  |  |

| H'21    | FLMCR2   | FLER      | _     | _     | _     | _     | _     | _     | _     |             |  |  |

| H'22    | FLPWCR   | PDWND     | _     | —     | —     | _     | _     | _     | _     |             |  |  |

| H'23    | EBR      | _         | _     | _     | EB4   | EB3   | EB2   | EB1   | EB0   |             |  |  |

| H'24    |          |           |       |       |       |       |       |       |       |             |  |  |

| H'25    |          |           |       |       |       |       |       |       |       |             |  |  |

| H'26    |          |           |       |       |       |       |       |       |       |             |  |  |

| H'27    |          |           |       |       |       |       |       |       |       |             |  |  |

| H'28    |          |           |       |       |       |       |       |       |       |             |  |  |

| H'29    |          |           |       |       |       |       |       |       |       |             |  |  |

| H'2A    |          |           |       |       |       |       |       |       |       |             |  |  |

| H'2B    | FENR     | FLSHE     | _     | —     | —     | _     | _     | _     | _     |             |  |  |

| H'2C    |          |           |       |       |       |       |       |       |       |             |  |  |

| H'2D    |          |           |       |       |       |       |       |       |       |             |  |  |

| H'2E    |          |           |       |       |       |       |       |       |       |             |  |  |

| H'2F    |          |           |       |       |       |       |       |       |       |             |  |  |

#### Appendix B Internal I/O Registers

| Lower RegisterBit Names |         |           |           |           |           |           |           |           |           |             |

|-------------------------|---------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-------------|

| Address                 | Name    | Bit 7     | Bit 6     | Bit 5     | Bit 4     | Bit 3     | Bit 2     | Bit 1     | Bit 0     | Module Name |

| H'A0                    |         |           |           |           |           |           |           |           |           |             |

| H'A1                    |         |           |           |           |           |           |           |           |           | -           |

| H'A2                    |         |           |           |           |           |           |           |           |           | -           |

| H'A3                    |         |           |           |           |           |           |           |           |           | -           |

| H'A4                    |         |           |           |           |           |           |           |           |           | -           |

| H'A5                    |         |           |           |           |           |           |           |           |           | =           |

| H'A6                    |         |           |           |           |           |           |           |           |           | -           |

| H'A7                    |         |           |           |           |           |           |           |           |           | -           |

| H'A8                    | SMR     | COM       | CHR       | PE        | PM        | STOP      | MP        | CKS1      | CKS0      | SCI3        |

| H'A9                    | BRR     | BRR7      | BRR6      | BRR5      | BRR4      | BRR3      | BRR2      | BRR1      | BRR0      | =           |

| H'AA                    | SCR3    | TIE       | RIE       | TE        | RE        | _         | TEIE      | CKE1      | CKE0      | _           |

| H'AB                    | TDR     | TDR7      | TDR6      | TDR5      | TDR4      | TDR3      | TDR2      | TDR1      | TDR0      | =           |

| H'AC                    | SSR     | TDRE      | RDRF      | OER       | FER       | PER       | TEND      | _         | _         | =           |

| H''AD                   | RDR     | RDR7      | RDR6      | RDR5      | RDR4      | RDR3      | RDR2      | RDR1      | RDR0      | =           |

| H'AE                    |         |           |           |           |           |           |           |           |           | =           |

| H'AF                    |         |           |           |           |           |           |           |           |           | _           |

| H'B0                    | TMA     | _         | _         | _         | _         | TMA3      | TMA2      | TMA1      | TMA0      | Timer A     |

| H'B1                    | TCA     | TCA7      | TCA6      | TCA5      | TCA4      | TCA3      | TCA2      | TCA1      | TCA0      |             |

| H'B2                    | TCSRW   | B6WI      | TCWE      | B4WI      | TCSRWE    | B2WI      | WDON      | BOWI      | WRST      | Watchdog    |

| H'B3                    | TCW     | TCW7      | TCW6      | TCW5      | TCW4      | TCW3      | TCW2      | TCW1      | TCW0      | timer       |

| H'B4                    | TMC     | TMC7      | TMC6      | TMC5      | _         | _         | TMC2      | TMC1      | TMC0      | Timer C     |

| H'B5                    | TCC/TLC | TCC7/TLC7 | TCC6/TLC6 | TCC5/TLC5 | TCC4/TLC4 | TCC3/TLC3 | TCC2/TLC2 | TCC1/TLC1 | TCC0/TLC0 |             |

| H'B6                    | TCRF    | TOLH      | CKSH2     | CKSH1     | CKSH0     | TOLL      | CKSL2     | CKSL1     | CKSL0     | Timer F     |

| H'B7                    | TCSRF   | OVFH      | CMFH      | OVIEH     | CCLRH     | OVFL      | CMFL      | OVIEL     | CCLRL     | _           |

| H'B8                    | TCFH    | TCFH7     | TCFH6     | TCFH5     | TCFH4     | TCFH3     | TCFH2     | TCFH1     | TCFH0     | _           |

| H'B9                    | TCFL    | TCFL7     | TCFL6     | TCFL5     | TCFL4     | TCFL3     | TCFL2     | TCFL1     | TCFL0     | _           |

| H'BA                    | OCRFH   | OCRFH7    | OCRFH6    | OCRFH5    | OCRFH4    | OCRFH3    | OCRFH2    | OCRFH1    | OCRFH0    | _           |

| H'BB                    | OCRFL   | OCRFL7    | OCRFL6    | OCRFL5    | OCRFL4    | OCRFL3    | OCRFL2    | OCRFL1    | OCRFL0    |             |

| H'BC                    | TMG     | OVFH      | OVFL      | OVIE      | IIEGS     | CCLR1     | CCLR0     | CKS1      | CKS0      | Timer G     |

| H'BD                    | ICRGF   | ICRGF7    | ICRGF6    | ICRGF5    | ICRGF4    | ICRGF3    | ICRGF2    | ICRGF1    | ICRGF0    | _           |

| H'BE                    | ICRGR   | ICRGR7    | ICRGR6    | ICRGR5    | ICRGR4    | ICRGR3    | ICRGR2    | ICRGR1    | ICRGR0    |             |

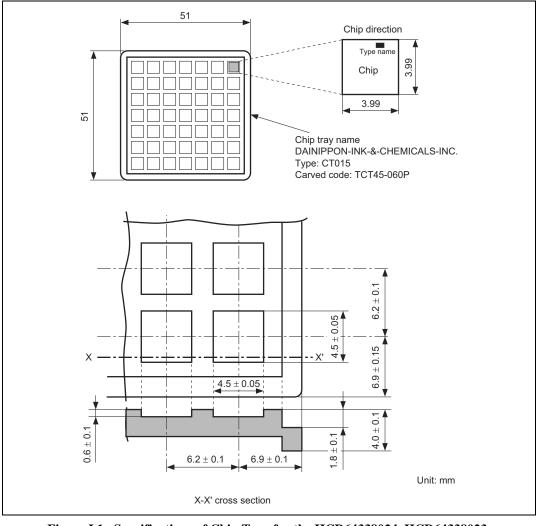

# Appendix I Specifications of Chip Tray

The specifications of the chip tray for the HCD64338024, HCD64338023, HCD64338022, HCD64338021, and HCD64338020 are shown in figure I.1. The specifications of the chip tray for the HCD64F38024 and HCD64F38024R are shown in figure I.2. The specifications of the chip tray for the HCD64338024S, HCD64338023S, HCD64338022S, HCD64338021S, and HCD64338020S are shown in figure I.3.

Rev. 8.00 Mar. 09, 2010 Page 646 of 658 REJ09B0042-0800