# E·XFL

## Renesas - HD64F38024RWV Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | H8/300L                                                                        |

| Core Size                  | 8-Bit                                                                          |

| Speed                      | 10MHz                                                                          |

| Connectivity               | SCI, UART/USART                                                                |

| Peripherals                | LCD, PWM, WDT                                                                  |

| Number of I/O              | 51                                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                    |

| Data Converters            | A/D 8x10b SAR                                                                  |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 80-TQFP                                                                        |

| Supplier Device Package    | 80-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd64f38024rwv |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                         | 14.3.1 | Power-On Reset Circuit                                                | 439  |

|-------------------------|--------|-----------------------------------------------------------------------|------|

|                         | 14.3.2 | Low-Voltage Detection Circuit                                         | 440  |

|                         |        | -                                                                     |      |

| Secti                   | on 15  | Power Supply Circuit (H8/38124 Group Only)                            | .447 |

| 15.1                    |        | Jsing Internal Power Supply Step-Down Circuit                         |      |

| 15.2                    |        | Not Using Internal Power Supply Step-Down Circuit                     |      |

| <b>C</b> 4 <sup>2</sup> | 16     | Electrical Characteristics                                            | 4.40 |

|                         |        | Electrical Characteristics                                            | .449 |

| 16.1                    |        | 24 Group ZTAT Version and Mask ROM Version Absolute Maximum           | 4.40 |

| 16.0                    | U      |                                                                       |      |

| 16.2                    |        | 24 Group ZTAT Version and Mask ROM Version Electrical Characteristics |      |

|                         |        | Power Supply Voltage and Operating Range                              |      |

|                         |        | DC Characteristics                                                    |      |

|                         |        | AC Characteristics                                                    |      |

|                         |        | A/D Converter Characteristics                                         |      |

| 16.0                    |        | LCD Characteristics                                                   | 464  |

| 16.3                    |        | 24 Group F-ZTAT Version and H8/38024R Group F-ZTAT Version Absolute   |      |

|                         |        | um Ratings                                                            | 465  |

| 16.4                    |        | 24 Group F-ZTAT Version and H8/38024R Group F-ZTAT Version Electrical | 1.00 |

|                         |        | teristics                                                             |      |

|                         |        | Power Supply Voltage and Operating Range                              |      |

|                         |        | DC Characteristics                                                    |      |

|                         |        | AC Characteristics                                                    |      |

|                         |        | A/D Converter Characteristics                                         |      |

|                         |        | LCD Characteristics                                                   |      |

|                         |        | Flash Memory Characteristics                                          |      |

|                         |        | Power Supply Characteristics                                          |      |

| 16.5                    |        | 24S Group Mask ROM Version Absolute Maximum Ratings                   |      |

| 16.6                    |        | 24S Group Mask ROM Version Electrical Characteristics                 |      |

|                         |        | Power Supply Voltage and Operating Range                              |      |

|                         |        | DC Characteristics                                                    |      |

|                         |        | AC Characteristics                                                    |      |

|                         |        | A/D Converter Characteristics                                         |      |

|                         |        | LCD Characteristics                                                   | 500  |

| 16.7                    |        | te Maximum Ratings of H8/38124 Group F-ZTAT Version and Mask ROM      |      |

|                         |        | 1                                                                     | 501  |

| 16.8                    |        | cal Characteristics of H8/38124 Group F-ZTAT Version and Mask ROM     |      |

|                         |        | 1                                                                     |      |

|                         |        | Power Supply Voltage and Operating Ranges                             |      |

|                         | 16.8.2 | DC Characteristics                                                    | 506  |

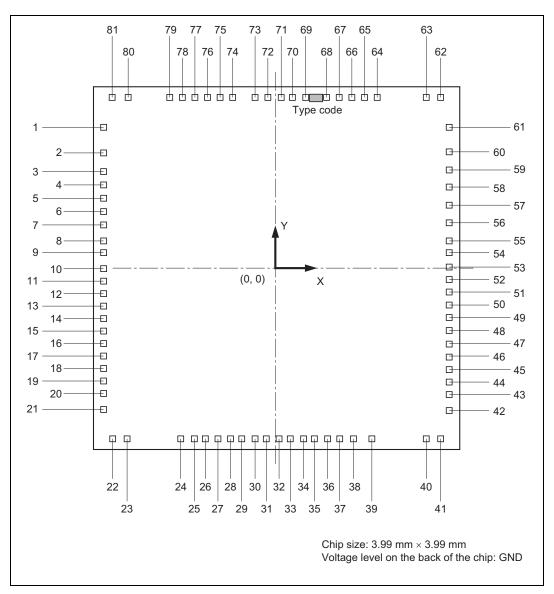

Figure 1.5 Bonding Pad Location Diagram of HCD64338024, HCD64338023, HCD64338022, HCD64338021, and HCD64338020 (Top View)

## 2.4 Addressing Modes

## 2.4.1 Addressing Modes

The H8/300L CPU supports the eight addressing modes listed in table 2.1. Each instruction uses a subset of these addressing modes.

#### Table 2.1 Addressing Modes

| No. | Address Modes                                                                 | Symbol          |

|-----|-------------------------------------------------------------------------------|-----------------|

| 1   | Register direct                                                               | Rn              |

| 2   | Register indirect                                                             | @Rn             |

| 3   | Register indirect with displacement                                           | @(d:16, Rn)     |

| 4   | Register indirect with post-increment<br>Register indirect with pre-decrement | @Rn+<br>@-Rn    |

| 5   | Absolute address                                                              | @aa:8 or @aa:16 |

| 6   | Immediate                                                                     | #xx:8 or #xx:16 |

| 7   | Program-counter relative                                                      | @(d:8, PC)      |

| 8   | Memory indirect                                                               | @@aa:8          |

**Register Direct—Rn:** The register field of the instruction specifies an 8- or 16-bit general register containing the operand.

Only the MOV.W, ADD.W, SUB.W, CMP.W, ADDS, SUBS, MULXU (8 bits  $\times$  8 bits), and DIVXU (16 bits  $\div$  8 bits) instructions have 16-bit operands.

**Register Indirect**—@**Rn:** The register field of the instruction specifies a 16-bit general register containing the address of the operand in memory.

**Register Indirect with Displacement**—@(**d:16, Rn**): The instruction has a second word (bytes 3 and 4) containing a displacement which is added to the contents of the specified general register to obtain the operand address in memory.

This mode is used only in MOV instructions. For the MOV.W instruction, the resulting address must be even.

#### 2.5.1 Data Transfer Instructions

Table 2.4 describes the data transfer instructions. Figure 2.5 shows their object code formats.

| Instructio | n     | Size*        | Function                                                                                                                                                                |

|------------|-------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOV        |       | B/W          | $(EAs) \rightarrow Rd, Rs \rightarrow (EAd)$                                                                                                                            |

|            |       |              | Moves data between two general registers or between a general register and memory, or moves immediate data to a general register.                                       |

|            |       |              | The Rn, @Rn, @(d:16, Rn), @aa:16, #xx:16, @-Rn, and @Rn+<br>addressing modes are available for word data. The @aa:8<br>addressing mode is available for byte data only. |

|            |       |              | The @–R7 and @R7+ modes require word operands. Do not specify byte size for these two modes.                                                                            |

| POP        |       | W            | @SP+ → Rn                                                                                                                                                               |

|            |       |              | Pops a 16-bit general register from the stack. Equivalent to MOV.W @SP+, Rn.                                                                                            |

| PUSH       |       | W            | $Rn \rightarrow @-SP$                                                                                                                                                   |

|            |       |              | Pushes a 16-bit general register onto the stack. Equivalent to MOV.W Rn, @-SP.                                                                                          |

| Note: *    | Size: | Operand size | )                                                                                                                                                                       |

|            | B:    | Byte         |                                                                                                                                                                         |

|            | W:    | Word         |                                                                                                                                                                         |

#### Table 2.4 Data Transfer Instructions

Certain precautions are required in data access. See section 2.9.1, Notes on Data Access, for details.

Figure 2.7 lists the format of the bit manipulation instructions.

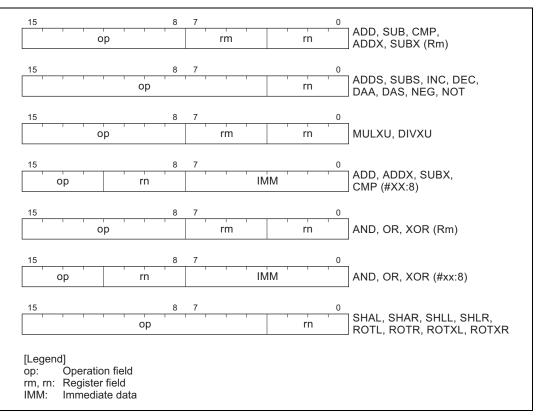

Figure 2.6 shows the instruction code format of arithmetic, logic, and shift instructions.

Figure 2.6 Arithmetic, Logic, and Shift Instruction Codes

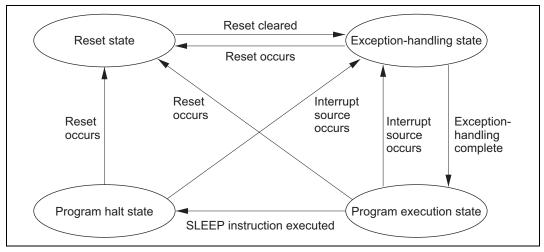

Figure 2.15 State Transitions

## 2.7.2 Program Execution State

In the program execution state the CPU executes program instructions in sequence.

There are three modes in this state, two active modes (high speed and medium speed) and one subactive mode. Operation is synchronized with the system clock in active mode (high speed and medium speed), and with the subclock in subactive mode. See section 5, Power-Down Modes for details on these modes.

## 2.7.3 Program Halt State

In the program halt state there are five modes: two sleep modes (high speed and medium speed), standby mode, watch mode, and subsleep mode. See section 5, Power-Down Modes for details on these modes.

## 2.7.4 Exception-Handling State

The exception-handling state is a transient state occurring when exception handling is started by a reset or interrupt and the CPU changes its normal processing flow. In exception handling caused by an interrupt, SP (R7) is referenced and the PC and CCR values are saved on the stack.

For details on interrupt handling, see section 3.3, Interrupts.

## Renesas

#### 8.5.4 Pin States

Table 8.13 shows the port 5 pin states in each operating mode.

| Pins                                                                                                               | Reset              | Sleep                        | Subsleep | Standby                         | Watch | Subactive  | Active     |

|--------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------|----------|---------------------------------|-------|------------|------------|

| P5 <sub>7</sub> /WKP <sub>7</sub> /<br>SEG <sub>8</sub> to P5 <sub>0</sub> /<br>WKP <sub>0</sub> /SEG <sub>1</sub> | High-<br>impedance | Retains<br>previous<br>state |          | High-<br>impedance <sup>*</sup> |       | Functional | Functional |

Note: \* A high-level signal is output when the MOS pull-up is in the on state. In the HD64F38024 the previous pin state is retained.

#### 8.5.5 MOS Input Pull-Up

Port 5 has a built-in MOS input pull-up function that can be controlled by software. When a PCR5 bit is cleared to 0, setting the corresponding PUCR5 bit to 1 turns on the MOS pull-up for that pin. The MOS pull-up function is in the off state after a reset.

| PCR5n              | 0   | 0  | 1   |  |

|--------------------|-----|----|-----|--|

| PUCR5 <sub>n</sub> | 0   | 1  | *   |  |

| MOS input pull-up  | Off | On | Off |  |

(n = 7 to 0)

\*: Don't care

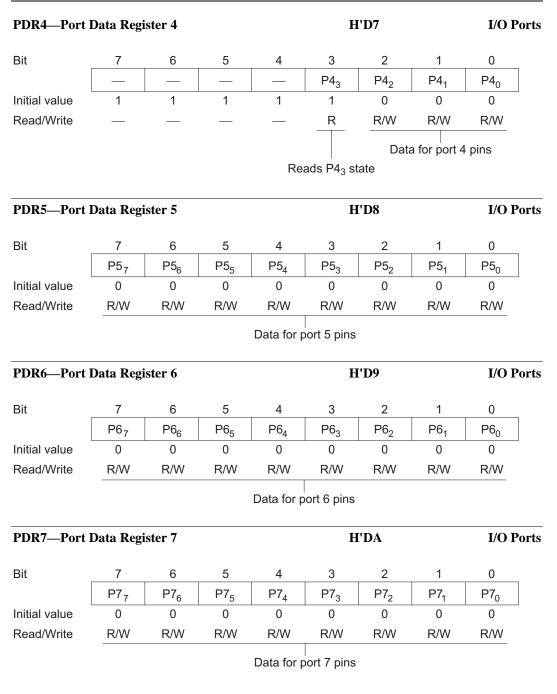

#### Port Data Register 6 (PDR6)

| Bit           | 7   | 6               | 5               | 4   | 3   | 2               | 1               | 0   |

|---------------|-----|-----------------|-----------------|-----|-----|-----------------|-----------------|-----|

|               | P67 | P6 <sub>6</sub> | P6 <sub>5</sub> | P64 | P63 | P6 <sub>2</sub> | P6 <sub>1</sub> | P60 |

| Initial value | 0   | 0               | 0               | 0   | 0   | 0               | 0               | 0   |

| Read/Write    | R/W | R/W             | R/W             | R/W | R/W | R/W             | R/W             | R/W |

PDR6 is an 8-bit register that stores data for port 6 pins P67 to P60.

If port 6 is read while PCR6 bits are set to 1, the values stored in PDR6 are read, regardless of the actual pin states. If port 6 is read while PCR6 bits are cleared to 0, the pin states are read.

Upon reset, PDR6 is initialized to H'00.

#### Port Control Register 6 (PCR6)

| Bit           | 7     | 6                 | 5                 | 4                 | 3                 | 2                 | 1                 | 0     |

|---------------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

|               | PCR67 | PCR6 <sub>6</sub> | PCR6 <sub>5</sub> | PCR6 <sub>4</sub> | PCR6 <sub>3</sub> | PCR6 <sub>2</sub> | PCR6 <sub>1</sub> | PCR60 |

| Initial value | 0     | 0                 | 0                 | 0                 | 0                 | 0                 | 0                 | 0     |

| Read/Write    | W     | W                 | W                 | W                 | W                 | W                 | W                 | W     |

PCR6 is an 8-bit register for controlling whether each of the port 6 pins  $P6_7$  to  $P6_0$  functions as an input pin or output pin.

Setting a PCR6 bit to 1 makes the corresponding pin  $(P6_7 \text{ to } P6_0)$  an output pin, while clearing the bit to 0 makes the pin an input pin. PCR6 and PDR6 settings are valid when the corresponding pins are designated for general-purpose input/output by bits SGS3 to SGS0 in LPCR.

Upon reset, PCR6 is initialized to H'00.

PCR6 is a write-only register, which is always read as all 1s.

## Renesas

| <b>Table 10.4</b> | Relation | between r | and Clock |

|-------------------|----------|-----------|-----------|

|                   |          |           |           |

|   |                                      | SMR Setting |      |  |  |

|---|--------------------------------------|-------------|------|--|--|

| n | Clock                                | CKS1        | CKS0 |  |  |

| 0 | ф                                    | 0           | 0    |  |  |

| 0 | φw/2 <sup>*1</sup> /φw <sup>*2</sup> | 0           | 1    |  |  |

| 2 | ф <b>/16</b>                         | 1           | 0    |  |  |

| 3 | ф/64                                 | 1           | 1    |  |  |

Notes: 1.  $\phi$  w/2 clock in active (medium-speed/high-speed) mode and sleep mode

2.  $\phi$  w clock in subactive mode and subsleep mode

In subactive or subsleep mode, SCI3 can be operated when CPU clock is  $\phi w/2$  only.

Table 10.5 shows the maximum bit rate for each frequency. The values shown are for active (high-speed) mode.

| Table 10.5 Maximum bit Kate for Each Frequency (Asynchronous Mode | <b>Table 10.5</b> | Maximum Bit Rate for Each Frequency (Asynchronous Mode) |

|-------------------------------------------------------------------|-------------------|---------------------------------------------------------|

|-------------------------------------------------------------------|-------------------|---------------------------------------------------------|

|           |         | Maximum Bit Rate | Setting |   |  |

|-----------|---------|------------------|---------|---|--|

| OSC (MHz) | φ (MHz) | (bit/s)          | n       | Ν |  |

| 0.0384*   | 0.0192  | 600              | 0       | 0 |  |

| 2         | 1       | 31250            | 0       | 0 |  |

| 2.4576    | 1.2288  | 38400            | 0       | 0 |  |

| 4         | 2       | 62500            | 0       | 0 |  |

| 10        | 5       | 156250           | 0       | 0 |  |

| 16        | 8       | 250000           | 0       | 0 |  |

| 20        | 10      | 312500           | 0       | 0 |  |

Note: \* When SMR is set up to CKS1 = 0, CKS0 = 1.

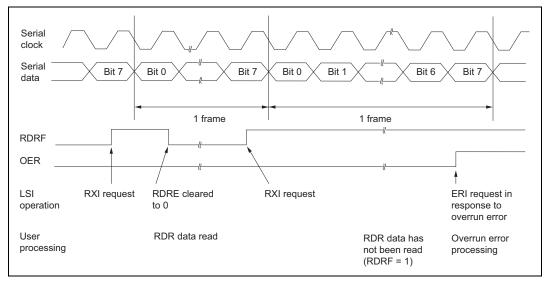

SCI3 operates as follows when receiving data.

SCI3 performs internal synchronization and begins reception in synchronization with the serial clock input or output.

The received data is placed in RSR in LSB-to-MSB order.

After the data has been received, SCI3 checks that bit RDRF is set to 0, indicating that the receive data can be transferred from RSR to RDR.

If this check shows that there is no overrun error, bit RDRF is set to 1, and the receive data is stored in RDR. If bit RIE is set to 1 in SCR3, an RXI interrupt is requested. If the check identifies an overrun error, bit OER is set to 1.

Bit RDRF remains set to 1. If bit RIE is set to 1 in SCR3, an ERI interrupt is requested.

See table 10.12 for the conditions for detecting a receive error, and receive data processing.

Note: No further receive operations are possible while a receive error flag is set. Bits OER, FER, PER, and RDRF must therefore be cleared to 0 before resuming reception.

Figure 10.14 shows an example of the operation when receiving in synchronous mode.

Figure 10.14 Example of Operation when Receiving in Synchronous Mode

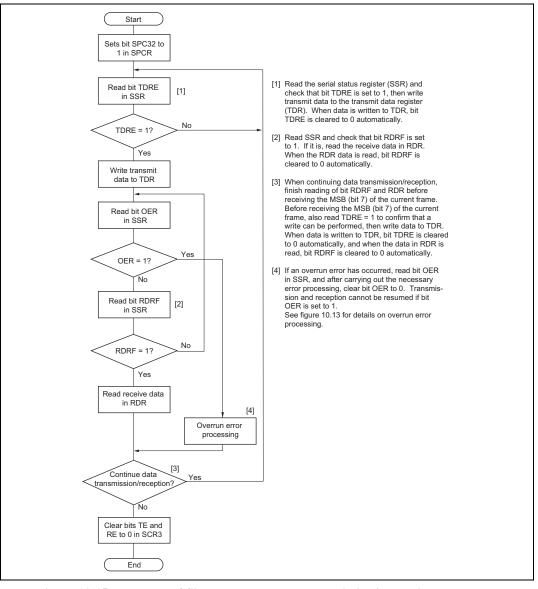

• Simultaneous transmit/receive

Figure 10.15 shows an example of a flowchart for a simultaneous transmit/receive operation. This procedure should be followed for simultaneous transmission/reception after initializing SCI3.

## Section 11 10-Bit PWM

## 11.1 Overview

The H8/38024 Group is provided with two on-chip 10-bit PWMs (pulse width modulators), designated PWM1 and PWM2, with identical functions. The PWMs can be used as D/A converters by connecting a low-pass filter. In this section the suffix m (m = 1 or 2) is used with register names, etc., as in PWDRLm, which denotes the PWDRL registers for each PWM.

#### 11.1.1 Features

Features of the 10-bit PWMs are as follows.

- Choice of four conversion periods Any of the following conversion periods can be chosen: 4,096/φ, with a minimum modulation width of 4/φ 2,048/φ, with a minimum modulation width of 2/φ 1,024/φ, with a minimum modulation width of 1/φ 512/φ, with a minimum modulation width of 1/2 φ

- Pulse division method for less ripple

- Use of module standby mode enables this module to be placed in standby mode independently when not used.

On the H8/38124 Group it is possible to select between two types of PWM output: pulse-division PWM and event counter PWM (PWM incorporating AEC). (The H8/38024 Group, H8/38024F-ZTAT Group, and H8/38024S Group can only produce pulse-division PWM output.) Refer to section 9.7, Asynchronous Event Counter, for information on event counter PWM.

## Renesas

#### Bits 7 to 2—Reserved/Bits 7 to 3—Reserved\*

Bits 7 to 2 are reserved; they are always read as 1, and cannot be modified.

Note: \* Implemented on H8/38124 Group only.

#### Bit 2—Output Format Select (PWCRm2)\*

This bit selects the format of the output from the PWMm output pin.

This bit is write-only. Reading it always returns 1.

| Bit 2<br>PWCRm2 | Description        |                 |

|-----------------|--------------------|-----------------|

| 0               | Pulse-division PWM | (initial value) |

| 1               | Event counter PWM  |                 |

Note: \* Implemented on H8/38124 Group only.

#### Bits 1 and 0—Clock Select 1 and 0 (PWCRm1, PWCRm0)

Bits 1 and 0 select the clock supplied to the 10-bit PWM. These bits are write-only bits; they are always read as 1.

| Bit 1<br>PWCRm1 | Bit 0<br>PWCRm0 | Description                                                                                                                                    |                 |

|-----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 0               | 0               | The input clock is $\phi$ (t $\phi^*$ = 1/ $\phi$ )<br>The conversion period is 512/ $\phi$ , with a minimum modulation<br>width of 1/2 $\phi$ | (initial value) |

| 0               | 1               | The input clock is $\phi/2$ (t $\phi^* = 2/\phi$ )<br>The conversion period is 1,024/ $\phi$ , with a minimum<br>modulation width of 1/ $\phi$ |                 |

| 1               | 0               | The input clock is $\phi/4$ (t $\phi^* = 4/\phi$ )<br>The conversion period is 2,048/ $\phi$ , with a minimum<br>modulation width of 2/ $\phi$ |                 |

| 1               | 1               | The input clock is $\phi/8$ (t $\phi^* = 8/\phi$ )<br>The conversion period is 4,096/ $\phi$ , with a minimum<br>modulation width of 4/ $\phi$ |                 |

Note: \* Period of PWM input clock.

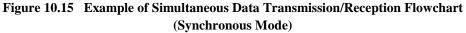

Figure 13.4 LCD RAM Map (1/3 Duty)

Table 14.3 shows the relationship between LVDCR settings and function selections. Refer to table 14.3 when making settings to LVDCR.

|      | LVDC   | R Setting | j Value |       |                   | Low-Voltage        | Low-Voltage<br>Detection  | Low-Voltage<br>Detection  |

|------|--------|-----------|---------|-------|-------------------|--------------------|---------------------------|---------------------------|

| LVDE | LVDSEL | LVDRE     | LVDDE   | LVDUE | Power-on<br>Reset | Detection<br>Reset | Voltage Drop<br>Interrupt | Voltage Rise<br>Interrupt |

| 0    | *      | *         | *       | *     | 0                 | _                  | _                         | _                         |

| 1    | 1      | 1         | 0       | 0     | 0                 | 0                  | _                         | _                         |

| 1    | 0      | 0         | 1       | 0     | 0                 | _                  | 0                         | _                         |

| 1    | 0      | 0         | 1       | 1     | 0                 | _                  | 0                         | 0                         |

| 1    | 0      | 1         | 1       | 1     | 0                 | 0                  | 0                         | 0                         |

#### Table 14.3 LVDCR Settings and Function Selections

Note: Setting values marked with an asterisk (\*) are invalid.

#### 14.2.2 Low-Voltage Detection Status Register (LVDSR)

| Bit           | 7   | 6   | 5   | 4   | 3       | 2   | 1     | 0     |

|---------------|-----|-----|-----|-----|---------|-----|-------|-------|

|               | OVF | _   | —   |     | VREFSEL | _   | LVDDF | LVDUF |

| Initial value | 0*  | 0   | 0   | 0   | 0       | 0   | 0*    | 0*    |

| Read/Write    | R/W | R/W | R/W | R/W | R/W     | R/W | R/W   | R/W   |

Note: \* These bits initialized by resets trigged by LVDR.

LVDSR is an 8-bit read/write register. It is used to control external input selection, indicates when the reference voltage is stable, and indicates if the power supply voltage goes below or above a specified range.

#### Bit 7—LVD Reference Voltage Stabilized Flag (OVF)

This bit indicates when the low-voltage detection counter (LVDCNT) overflows.

| Bit 7<br>OVF | Description                                                                      |                 |

|--------------|----------------------------------------------------------------------------------|-----------------|

| 0            | [Clearing condition]<br>When 0 is written after reading 1                        | (initial value) |

| 1            | [Setting condition]<br>When the low-voltage detection counter (LVDCNT) overflows |                 |

#### 16.4.6 Flash Memory Characteristics

Table 16.13 lists the flash memory characteristics.

## **Table 16.13 Flash Memory Characteristics**

$AV_{CC} = 2.7 V$  to 3.6 V,  $V_{SS} = AV_{SS} = 0.0 V$ ,  $V_{CC} = 2.7 V$  to 3.6 V (operating voltage range in reading),  $V_{CC} = 3.0 V$  to 3.6 V (operating voltage range in programming/erasing),  $T_a = -20$  to  $+75^{\circ}C$  (operating temperature range in programming/erasing)

| Item           |                                                |                  |                   | Values      | 5    |       | Test                       |

|----------------|------------------------------------------------|------------------|-------------------|-------------|------|-------|----------------------------|

|                |                                                | Symbol           | Min               | Тур         | Мах  | Unit  | Condition                  |

| Programming    | t₽                                             | _                | 7                 | 200         | ms   |       |                            |

| Erase time (pe |                                                | t <sub>E</sub>   |                   | 100         | 1200 | ms    |                            |

| Maximum num    | ber of reprogrammings                          | $N_{WEC}$        | 1000<br>*8 *11    | 10000<br>*9 | —    | Times |                            |

|                |                                                |                  | 100<br>*8 *12     | 10000<br>*9 | —    |       |                            |

| Data retention | time                                           | t <sub>DRP</sub> | 10 <sup>*10</sup> |             | _    | Years |                            |

| Programming    | Wait time after SWE bit setting*1              | х                | 1                 |             |      | μs    |                            |

|                | Wait time after PSU bit setting*1              | у                | 50                |             |      | μs    |                            |

|                | Wait time after P bit setting <sup>*1 *4</sup> | z1               | 28                | 30          | 32   | μs    | $1 \le n \le 6$            |

|                |                                                | z2               | 198               | 200         | 202  | μs    | $7 \le n \le 1000$         |

|                |                                                | z3               | 8                 | 10          | 12   | μs    | Additional-<br>programming |

|                | Wait time after P bit clear*1                  | α                | 5                 |             |      | μs    |                            |

|                | Wait time after PSU bit clear*1                | β                | 5                 | _           | _    | μs    |                            |

|                | Wait time after PV bit setting*1               | γ                | 4                 | _           | _    | μs    |                            |

|                | Wait time after dummy write*1                  | 3                | 2                 | _           | _    | μs    |                            |

|                | Wait time after PV bit clear*1                 | η                | 2                 | _           | _    | μs    |                            |

|                | Wait time after SWE bit clear*1                | θ                | 100               | _           | _    | μs    |                            |

|                | Maximum programming count*1 *4                 | *5N              | _                 | _           | 1000 | Times |                            |

| Erase          | Wait time after SWE bit setting*1              | х                | 1                 |             |      | μs    |                            |

|                | Wait time after ESU bit setting*1              | у                | 100               |             | _    | μs    |                            |

|                | Wait time after E bit setting <sup>*1 *6</sup> | Z                | 10                | _           | 100  | ms    |                            |

|                | Wait time after E bit clear*1                  | α                | 10                |             | _    | μs    |                            |

|                | Wait time after ESU bit clear*1                | β                | 10                | _           | _    | μs    |                            |

|                | Wait time after EV bit setting <sup>*1</sup>   | γ                | 20                |             | _    | μs    |                            |

|                | Wait time after dummy write*1                  | 3                | 2                 | _           |      | μs    |                            |

|                | Wait time after EV bit clear*1                 | η                | 4                 | _           |      | μs    |                            |

|                | Wait time after SWE bit clear*1                | θ                | 100               | _           | _    | μs    |                            |

|                | Maximum erase count <sup>*1 *6 *7</sup>        | Ν                | _                 | _           | 120  | Times |                            |

#### Table 16.30 Power Supply Voltage Detection Circuit Characteristics (3)

Using on-chip reference voltage and detect voltage external input (VREFSEL = 0, VINTDSEL and VINTUSEL = 1)

|                                           |                                            |      | Ra   | ted Values                                                                |      |                         |  |

|-------------------------------------------|--------------------------------------------|------|------|---------------------------------------------------------------------------|------|-------------------------|--|

| Item                                      | Symbol                                     | Min  | Тур  | Max                                                                       | Unit | <b>Test Condition</b>   |  |

| extD/extU interrupt detection level       | Vexd                                       | 0.80 | 1.20 | 1.60                                                                      | V    |                         |  |

| extD/extU pin input voltage <sup>*2</sup> | VextD <sup>*1</sup><br>VextU <sup>*1</sup> | -0.3 | _    | V <sub>CC</sub> + 0.3 or AV <sub>CC</sub><br>+ 0.3, whichever is<br>lower | V    | $V_{CC}$ = 2.7 to 3.3 V |  |

|                                           |                                            | -0.3 | _    | 3.6 or AV <sub>CC</sub> + 0.3, whichever is lower                         | V    | $V_{CC}$ = 3.3 to 5.5 V |  |

Notes: 1. The VextD voltage must always be greater than the VextU voltage.

2. The maximum input voltage of the extD and extU pins is 3.6 V.

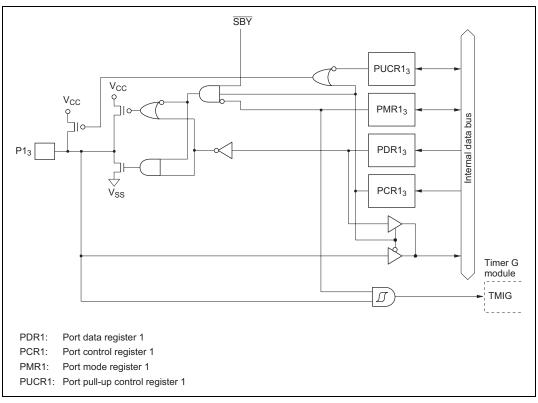

Figure C.1(c) Port 1 Block Diagram (Pin P1<sub>3</sub>)

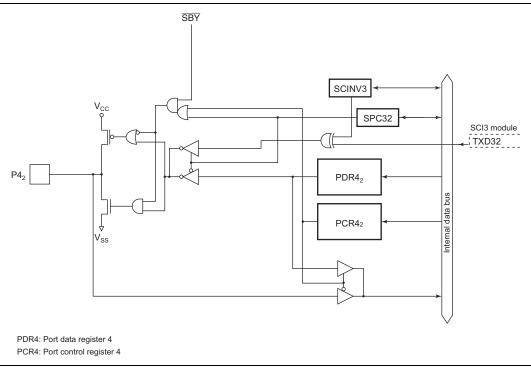

Figure C.3(b) Port 4 Block Diagram (Pin P4<sub>2</sub>)