Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                    |

| Core Processor             | ARM® Cortex®-M3                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 32MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT      |

| Number of I/O              | 53                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 4K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.85V ~ 3.8V                                                           |

| Data Converters            | A/D 8x12b; D/A 1x12b                                                   |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-TQFP                                                                |

| Supplier Device Package    | 64-TQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32tg842f32-qfp64t |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **1 Ordering Information**

Table 1.1 (p. 2) shows the available EFM32TG842 devices.

#### Table 1.1. Ordering Information

| Ordering Code       | Flash (kB) | RAM (kB) | Max<br>Speed<br>(MHz) | Supply<br>Voltage<br>(V) | Temperature<br>(ºC) | Package |

|---------------------|------------|----------|-----------------------|--------------------------|---------------------|---------|

| EFM32TG842F8-QFP64  | 8          | 2        | 32                    | 1.98 - 3.8               | -40 - 85            | TQFP64  |

| EFM32TG842F16-QFP64 | 16         | 4        | 32                    | 1.98 - 3.8               | -40 - 85            | TQFP64  |

| EFM32TG842F32-QFP64 | 32         | 4        | 32                    | 1.98 - 3.8               | -40 - 85            | TQFP64  |

Visit **www.silabs.com** for information on global distributors and representatives.

### 2.1.19 Voltage Comparator (VCMP)

The Voltage Supply Comparator is used to monitor the supply voltage from software. An interrupt can be generated when the supply falls below or rises above a programmable threshold. Response time and thereby also the current consumption can be configured by altering the current supply to the comparator.

### 2.1.20 Analog to Digital Converter (ADC)

The ADC is a Successive Approximation Register (SAR) architecture, with a resolution of up to 12 bits at up to one million samples per second. The integrated input mux can select inputs from 8 external pins and 6 internal signals.

### 2.1.21 Digital to Analog Converter (DAC)

The Digital to Analog Converter (DAC) can convert a digital value to an analog output voltage. The DAC is fully differential rail-to-rail, with 12-bit resolution. It has one single ended output buffer connected to channel 0. The DAC may be used for a number of different applications such as sensor interfaces or sound output.

### 2.1.22 Operational Amplifier (OPAMP)

The EFM32TG842 features 3 Operational Amplifiers. The Operational Amplifier is a versatile general purpose amplifier with rail-to-rail differential input and rail-to-rail single ended output. The input can be set to pin, DAC or OPAMP, whereas the output can be pin, OPAMP or ADC. The current is programmable and the OPAMP has various internal configurations such as unity gain, programmable gain using internal resistors etc.

### 2.1.23 Low Energy Sensor Interface (LESENSE)

The Low Energy Sensor Interface (LESENSE<sup>TM</sup>), is a highly configurable sensor interface with support for up to 8 individually configurable sensors. By controlling the analog comparators and DAC, LESENSE is capable of supporting a wide range of sensors and measurement schemes, and can for instance measure LC sensors, resistive sensors and capacitive sensors. LESENSE also includes a programmable FSM which enables simple processing of measurement results without CPU intervention. LESENSE is available in energy mode EM2, in addition to EM0 and EM1, making it ideal for sensor monitoring in applications with a strict energy budget.

### 2.1.24 Advanced Encryption Standard Accelerator (AES)

The AES accelerator performs AES encryption and decryption with 128-bit or 256-bit keys. Encrypting or decrypting one 128-bit data block takes 52 HFCORECLK cycles with 128-bit keys and 75 HFCORECLK cycles with 256-bit keys. The AES module is an AHB slave which enables efficient access to the data and key registers. All write accesses to the AES module must be 32-bit operations, i.e. 8- or 16-bit operations are not supported.

### 2.1.25 General Purpose Input/Output (GPIO)

In the EFM32TG842, there are 53 General Purpose Input/Output (GPIO) pins, which are divided into ports with up to 16 pins each. These pins can individually be configured as either an output or input. More advanced configurations like open-drain, filtering and drive strength can also be configured individually for the pins. The GPIO pins can also be overridden by peripheral pin connections, like Timer PWM outputs or USART communication, which can be routed to several locations on the device. The GPIO supports up to 16 asynchronous external pin interrupts, which enables interrupts from any pin on the device. Also, the input value of a pin can be routed through the Peripheral Reflex System to other peripherals.

## **3.4 Current Consumption**

### Table 3.3. Current Consumption

| Symbol           | Parameter                                                     | Condition                                                                                                          | Min | Тур  | Мах   | Unit       |

|------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|------|-------|------------|

|                  |                                                               | 32 MHz HFXO, all peripheral clocks disabled, V <sub>DD</sub> = 3.0 V                                               |     | 157  |       | μΑ/<br>MHz |

|                  |                                                               | 28 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 150  | 170   | µA/<br>MHz |

|                  | EM0 current. No prescaling. Running                           | 21 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 153  | 172   | µA/<br>MHz |

| I <sub>EM0</sub> | prime number cal-<br>culation code from<br>Flash. (Production | 14 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 155  | 175   | µA/<br>MHz |

|                  | test condition = 14<br>MHz)                                   | 11 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 157  | 178   | µA/<br>MHz |

|                  |                                                               | 6.6 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                    |     | 162  | 183   | μΑ/<br>MHz |

|                  |                                                               | 1.2 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                    |     | 200  | 240   | μΑ/<br>MHz |

|                  |                                                               | 32 MHz HFXO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                      |     | 53   |       | μΑ/<br>MHz |

|                  |                                                               | 28 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 51   | 57    | μΑ/<br>MHz |

|                  |                                                               | 21 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 55   | 59    | µA/<br>MHz |

| I <sub>EM1</sub> | EM1 current (Pro-<br>duction test condi-<br>tion = 14 MHz)    | 14 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 56   | 61    | µA/<br>MHz |

|                  | ,                                                             | 11 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                     |     | 58   | 63    | µA/<br>MHz |

|                  |                                                               | 6.6 MHz HFRCO, all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                    |     | 63   | 68    | μΑ/<br>MHz |

|                  |                                                               | 1.2 MHz HFRCO. all peripheral clocks disabled, $V_{DD}$ = 3.0 V                                                    |     | 100  | 122   | µA/<br>MHz |

|                  | EM2 ourrest                                                   | EM2 current with RTC<br>prescaled to 1 Hz, 32.768<br>kHz LFRCO, $V_{DD}$ = 3.0 V,<br>$T_{AMB}$ =25°C               |     | 1.0  | 1.2   | μA         |

| I <sub>EM2</sub> | EM2 current                                                   | EM2 current with RTC<br>prescaled to 1 Hz, 32.768<br>kHz LFRCO, V <sub>DD</sub> = 3.0 V,<br>T <sub>AMB</sub> =85°C |     | 2.4  | 5.0   | μA         |

| Inno             | EM3 current                                                   | V <sub>DD</sub> = 3.0 V, T <sub>AMB</sub> =25°C                                                                    |     | 0.59 | 1.0   | μA         |

| I <sub>EM3</sub> |                                                               | V <sub>DD</sub> = 3.0 V, T <sub>AMB</sub> =85°C                                                                    |     | 2.0  | 4.5   | μA         |

| I <sub>EM4</sub> | EM4 current                                                   | V <sub>DD</sub> = 3.0 V, T <sub>AMB</sub> =25°C                                                                    |     | 0.02 | 0.055 | μA         |

| 'EM4             |                                                               | V <sub>DD</sub> = 3.0 V, T <sub>AMB</sub> =85°C                                                                    |     | 0.25 | 0.70  | μA         |

## 3.7 Flash

#### Table 3.6. Flash

| Symbol               | Parameter                                           | Condition               | Min   | Тур  | Max            | Unit   |

|----------------------|-----------------------------------------------------|-------------------------|-------|------|----------------|--------|

| EC <sub>FLASH</sub>  | Flash erase cycles before failure                   |                         | 20000 |      |                | cycles |

|                      |                                                     | T <sub>AMB</sub> <150°C | 10000 |      |                | h      |

| RET <sub>FLASH</sub> | Flash data retention                                | T <sub>AMB</sub> <85°C  | 10    |      |                | years  |

|                      |                                                     | T <sub>AMB</sub> <70°C  | 20    |      |                | years  |

| t <sub>W_PROG</sub>  | Word (32-bit) pro-<br>gramming time                 |                         | 20    |      |                | μs     |

| t <sub>P_ERASE</sub> | Page erase time                                     |                         | 20    | 20.4 | 20.8           | ms     |

| t <sub>D_ERASE</sub> | Device erase time                                   |                         | 40    | 40.8 | 41.6           | ms     |

| I <sub>ERASE</sub>   | Erase current                                       |                         |       |      | 7 <sup>1</sup> | mA     |

| I <sub>WRITE</sub>   | Write current                                       |                         |       |      | 7 <sup>1</sup> | mA     |

| V <sub>FLASH</sub>   | Supply voltage dur-<br>ing flash erase and<br>write |                         | 1.98  |      | 3.8            | V      |

<sup>1</sup>Measured at 25°C

## **3.8 General Purpose Input Output**

#### Table 3.7. GPIO

| Symbol            | Parameter                                                                     | Condition                                                                       | Min                 | Тур                 | Max                 | Unit |

|-------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------|---------------------|---------------------|------|

| V <sub>IOIL</sub> | Input low voltage                                                             |                                                                                 |                     |                     | 0.30V <sub>DD</sub> | V    |

| V <sub>IOIH</sub> | Input high voltage                                                            |                                                                                 | 0.70V <sub>DD</sub> |                     |                     | V    |

|                   |                                                                               | Sourcing 0.1 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOWEST |                     | 0.80V <sub>DD</sub> |                     | V    |

|                   |                                                                               | Sourcing 0.1 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOWEST  |                     | 0.90V <sub>DD</sub> |                     | V    |

|                   |                                                                               | Sourcing 1 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOW      |                     | 0.85V <sub>DD</sub> |                     | V    |

| V <sub>IOOH</sub> | Output high volt-<br>age (Production test<br>condition = 3.0V,<br>DRIVEMODE = | Sourcing 1 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOW       |                     | 0.90V <sub>DD</sub> |                     | V    |

|                   | STANDARD)                                                                     | Sourcing 6 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= STANDARD | 0.75V <sub>DD</sub> |                     |                     | V    |

|                   |                                                                               | Sourcing 6 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= STANDARD  | 0.85V <sub>DD</sub> |                     |                     | V    |

|                   |                                                                               | Sourcing 20 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= HIGH    | 0.60V <sub>DD</sub> |                     |                     | V    |

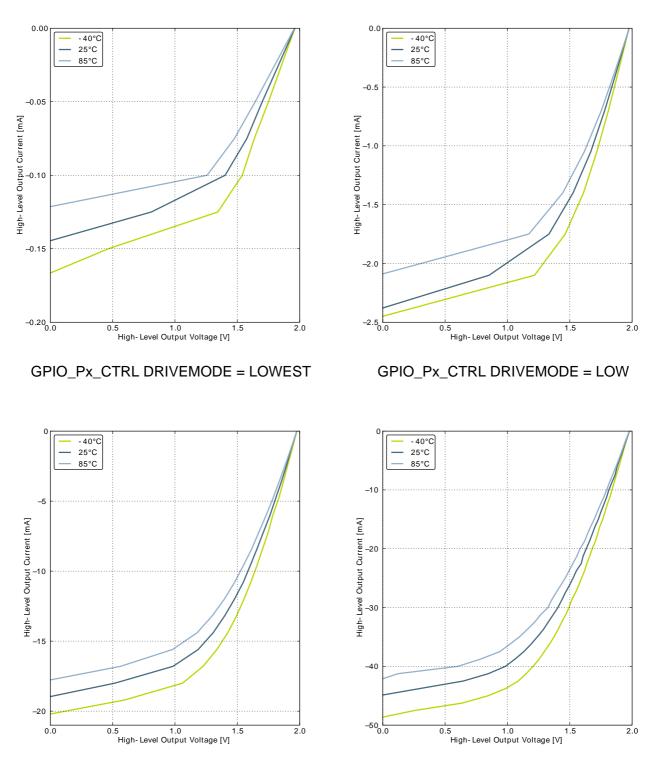

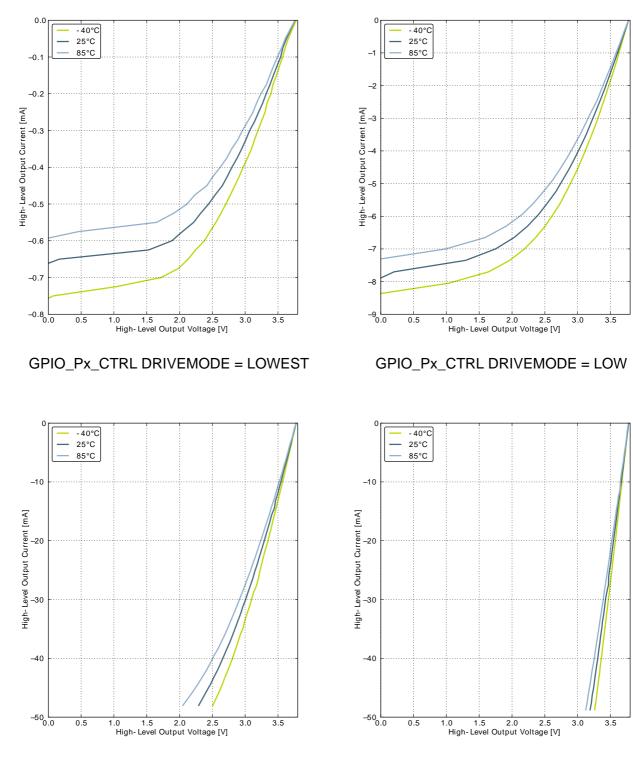

### Figure 3.5. Typical High-Level Output Current, 2V Supply Voltage

GPIO\_Px\_CTRL DRIVEMODE = STANDARD

GPIO\_Px\_CTRL DRIVEMODE = HIGH

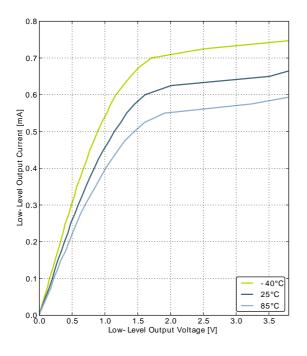

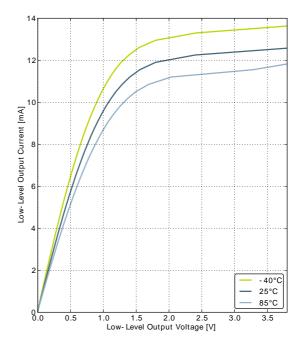

### Figure 3.8. Typical Low-Level Output Current, 3.8V Supply Voltage

GPIO\_Px\_CTRL DRIVEMODE = LOWEST

GPIO\_Px\_CTRL DRIVEMODE = STANDARD

GPIO\_Px\_CTRL DRIVEMODE = LOW

GPIO\_Px\_CTRL DRIVEMODE = HIGH

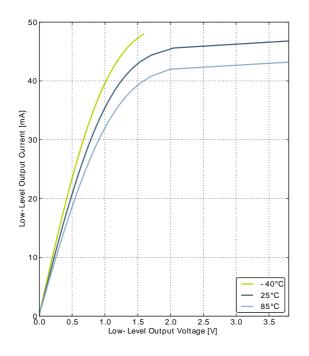

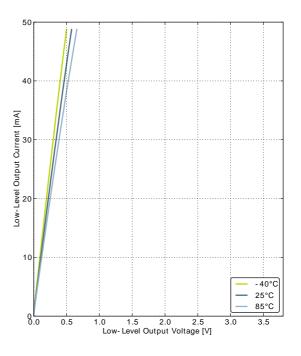

### Figure 3.9. Typical High-Level Output Current, 3.8V Supply Voltage

GPIO\_Px\_CTRL DRIVEMODE = STANDARD

GPIO\_Px\_CTRL DRIVEMODE = HIGH

| Symbol                         | Parameter                                           | Condition                    | Min | Тур              | Max | Unit |

|--------------------------------|-----------------------------------------------------|------------------------------|-----|------------------|-----|------|

|                                |                                                     | f <sub>HFRCO</sub> = 14 MHz  |     | 104              | 120 | μA   |

|                                |                                                     | f <sub>HFRCO</sub> = 11 MHz  |     | 94               | 110 | μA   |

|                                |                                                     | f <sub>HFRCO</sub> = 6.6 MHz |     | 63               | 90  | μA   |

|                                |                                                     | f <sub>HFRCO</sub> = 1.2 MHz |     | 22               | 32  | μA   |

| TUNESTEP <sub>H-</sub><br>FRCO | Frequency step<br>for LSB change in<br>TUNING value |                              |     | 0.3 <sup>3</sup> |     | %    |

<sup>1</sup>For devices with prod. rev. < 19, Typ = 7MHz and Min/Max values not applicable.

$^{2}$ For devices with prod. rev. < 19, Typ = 1MHz and Min/Max values not applicable.

<sup>3</sup>The TUNING field in the CMU\_HFRCOCTRL register may be used to adjust the HFRCO frequency. There is enough adjustment range to ensure that the frequency bands above 7 MHz will always have some overlap across supply voltage and temperature. By using a stable frequency reference such as the LFXO or HFXO, a firmware calibration routine can vary the TUNING bits and the frequency band to maintain the HFRCO frequency at any arbitrary value between 7 MHz and 28 MHz across operating conditions.

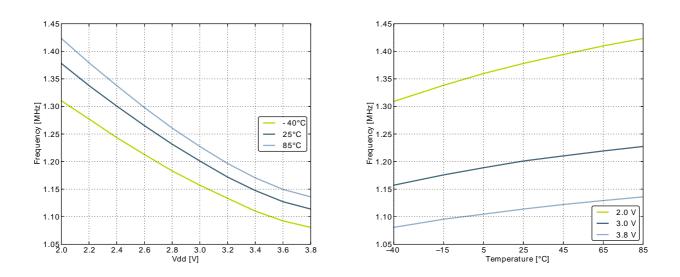

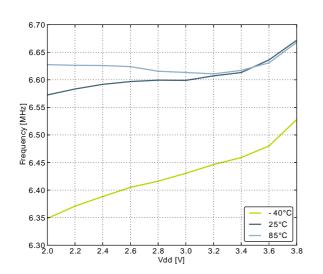

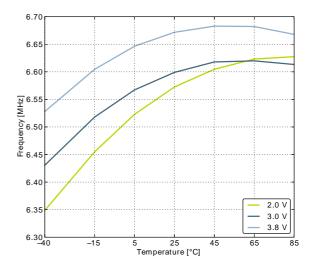

Figure 3.11. Calibrated HFRCO 1 MHz Band Frequency vs Supply Voltage and Temperature

Figure 3.12. Calibrated HFRCO 7 MHz Band Frequency vs Supply Voltage and Temperature

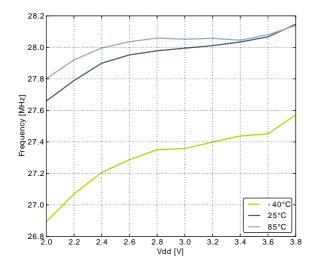

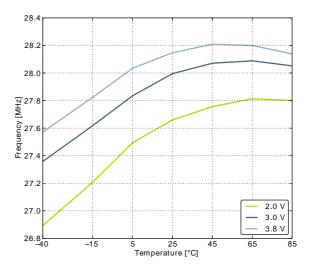

#### Figure 3.16. Calibrated HFRCO 28 MHz Band Frequency vs Supply Voltage and Temperature

### 3.9.5 AUXHFRCO

#### Table 3.12. AUXHFRCO

| Symbol                              | Parameter                                              | Condition                      | Min               | Тур               | Max               | Unit   |

|-------------------------------------|--------------------------------------------------------|--------------------------------|-------------------|-------------------|-------------------|--------|

|                                     |                                                        | 28 MHz frequency band          | 27.16             | 28.0              | 28.84             | MHz    |

|                                     |                                                        | 21 MHz frequency band          | 20.37             | 21.0              | 21.63             | MHz    |

| f                                   | Oscillation frequen-                                   | 14 MHz frequency band          | 13.58             | 14.0              | 14.42             | MHz    |

| † <sub>AUXHFRCO</sub>               | су, V <sub>DD</sub> = 3.0 V,<br>Т <sub>АМВ</sub> =25°С | 11 MHz frequency band          | 10.67             | 11.0              | 11.33             | MHz    |

|                                     |                                                        | 7 MHz frequency band           | 6.40 <sup>1</sup> | 6.60 <sup>1</sup> | 6.80 <sup>1</sup> | MHz    |

|                                     |                                                        | 1 MHz frequency band           | 1.16 <sup>2</sup> | 1.20 <sup>2</sup> | 1.24 <sup>2</sup> | MHz    |

| t <sub>AUXHFRCO_settlir</sub>       | gSettling time after start-up                          | f <sub>AUXHFRCO</sub> = 14 MHz |                   | 0.6               |                   | Cycles |

| TUNESTEP <sub>AU&gt;</sub><br>HFRCO | Frequency step<br>for LSB change in<br>TUNING value    |                                |                   | 0.3 <sup>3</sup>  |                   | %      |

<sup>1</sup>For devices with prod. rev. < 19, Typ = 7MHz and Min/Max values not applicable.

$^{2}$ For devices with prod. rev. < 19, Typ = 1MHz and Min/Max values not applicable.

<sup>3</sup>The TUNING field in the CMU\_AUXHFRCOCTRL register may be used to adjust the AUXHFRCO frequency. There is enough adjustment range to ensure that the frequency bands above 7 MHz will always have some overlap across supply voltage and temperature. By using a stable frequency reference such as the LFXO or HFXO, a firmware calibration routine can vary the TUNING bits and the frequency band to maintain the AUXHFRCO frequency at any arbitrary value between 7 MHz and 28 MHz across operating conditions.

### 3.9.6 ULFRCO

#### Table 3.13. ULFRCO

| Symbol               | Parameter                       | Condition | Min  | Тур   | Мах  | Unit |

|----------------------|---------------------------------|-----------|------|-------|------|------|

| fulfrco              | Oscillation frequen-<br>cy      | 25°C, 3V  | 0.70 |       | 1.75 | kHz  |

| TC <sub>ULFRCO</sub> | Temperature coeffi-<br>cient    |           |      | 0.05  |      | %/°C |

| VC <sub>ULFRCO</sub> | Supply voltage co-<br>efficient |           |      | -18.2 |      | %/V  |

| Symbol                 | Parameter                                              | Condition                                                                | Min                 | Тур               | Мах                | Unit                |

|------------------------|--------------------------------------------------------|--------------------------------------------------------------------------|---------------------|-------------------|--------------------|---------------------|

|                        |                                                        | 1 MSamples/s, 12 bit, single<br>ended, V <sub>DD</sub> reference         |                     | 73                |                    | dBc                 |

|                        |                                                        | 1 MSamples/s, 12 bit, differen-<br>tial, internal 1.25V reference        |                     | 66                |                    | dBc                 |

|                        |                                                        | 1 MSamples/s, 12 bit, differen-<br>tial, internal 2.5V reference         |                     | 77                |                    | dBc                 |

|                        |                                                        | 1 MSamples/s, 12 bit, differential, $V_{DD}$ reference                   |                     | 76                |                    | dBc                 |

|                        |                                                        | 1 MSamples/s, 12 bit, differen-<br>tial, 2xV <sub>DD</sub> reference     |                     | 75                |                    | dBc                 |

|                        |                                                        | 1 MSamples/s, 12 bit, differen-<br>tial, 5V reference                    |                     | 69                |                    | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, sin-<br>gle ended, internal 1.25V refer-<br>ence |                     | 75                |                    | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, single<br>ended, internal 2.5V reference         |                     | 75                |                    | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, single ended, V <sub>DD</sub> reference          | 68                  | 76                |                    | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, differ-<br>ential, internal 1.25V reference      |                     | 79                |                    | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, differ-<br>ential, internal 2.5V reference       |                     | 79                |                    | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, differ-<br>ential, 5V reference                  |                     | 78                |                    | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, differential, $V_{\text{DD}}$ reference          |                     | 79                |                    | dBc                 |

|                        |                                                        | 200 kSamples/s, 12 bit, differential, $2xV_{DD}$ reference               |                     | 79                |                    | dBc                 |

| M                      | Offect veltage                                         | After calibration, single ended                                          | -4                  | 0.3               | 4                  | mV                  |

| VADCOFFSET             | Offset voltage                                         | After calibration, differential                                          |                     | 0.3               |                    | mV                  |

|                        |                                                        |                                                                          |                     | -1.92             |                    | mV/°C               |

| TGRAD <sub>ADCTH</sub> | Thermometer out-<br>put gradient                       |                                                                          |                     | -6.3              |                    | ADC<br>Codes/<br>°C |

| DNL <sub>ADC</sub>     | Differential non-lin-<br>earity (DNL)                  | V <sub>DD</sub> = 3.0 V, external 2.5V reference                         | -1                  | ±0.7              | 4                  | LSB                 |

| INL <sub>ADC</sub>     | Integral non-linear-<br>ity (INL), End point<br>method | V <sub>DD</sub> = 3.0 V, external 2.5V reference                         |                     | ±1.2              | ±3                 | LSB                 |

| MC <sub>ADC</sub>      | No missing codes                                       |                                                                          | 11.999 <sup>1</sup> | 12                |                    | bits                |

|                        |                                                        | 1.25V reference                                                          |                     | 0.01 <sup>2</sup> | 0.033 <sup>3</sup> | %/°C                |

| GAIN <sub>ED</sub>     | Gain error drift                                       | 2.5V reference                                                           |                     | 0.01 <sup>2</sup> | 0.03 <sup>3</sup>  | %/°C                |

| 055057                 | or                                                     | 1.25V reference                                                          |                     | 0.2 <sup>2</sup>  | 0.7 <sup>3</sup>   | LSB/°C              |

| OFFSET <sub>ED</sub>   | Offset error drift                                     | 2.5V reference                                                           |                     | 0.2 <sup>2</sup>  | 0.62 <sup>3</sup>  | LSB/°C              |

<sup>1</sup>On the average every ADC will have one missing code, most likely to appear around  $2048 \pm n*512$  where n can be a value in the set {-3, -2, -1, 1, 2, 3}. There will be no missing code around 2048, and in spite of the missing code the ADC will be monotonic

### 3.10.1 Typical performance

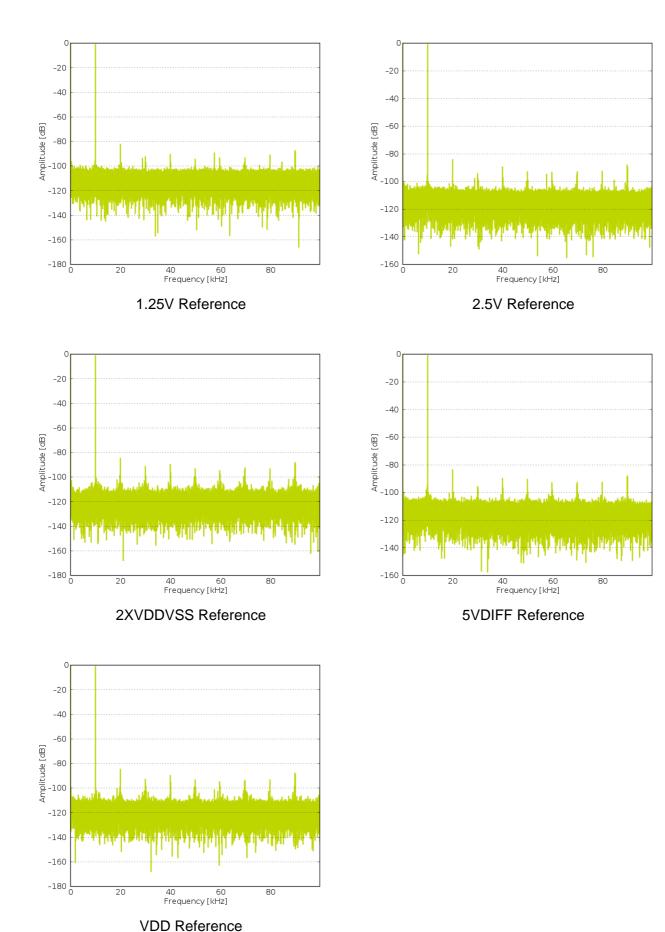

#### Figure 3.19. ADC Frequency Spectrum, Vdd = 3V, Temp = 25°C

| Symbol                    | Parameter                     | Condition                                                                            | Min             | Тур   | Мах                  | Unit  |

|---------------------------|-------------------------------|--------------------------------------------------------------------------------------|-----------------|-------|----------------------|-------|

|                           |                               | OPA0/OPA1 BIASPROG=0xF,<br>HALFBIAS=0x0                                              |                 | 16.36 |                      | MHz   |

|                           |                               | OPA0/OPA1 BIASPROG=0x7,<br>HALFBIAS=0x1                                              |                 | 0.81  |                      | MHz   |

|                           | Gain Bandwidth                | OPA0/OPA1 BIASPROG=0x0,<br>HALFBIAS=0x1                                              |                 | 0.11  |                      | MHz   |

| GBW <sub>OPAMP</sub>      | Product                       | OPA2 BIASPROG=0xF,<br>HALFBIAS=0x0                                                   |                 | 2.11  |                      | MHz   |

|                           |                               | OPA2 BIASPROG=0x7,<br>HALFBIAS=0x1                                                   |                 | 0.72  |                      | MHz   |

|                           |                               | OPA2 BIASPROG=0x0,<br>HALFBIAS=0x1                                                   |                 | 0.09  |                      | MHz   |

|                           |                               | BIASPROG=0xF,<br>HALFBIAS=0x0, C <sub>L</sub> =75 pF                                 |                 | 64    |                      | o     |

| PM <sub>OPAMP</sub>       | Phase Margin                  | BIASPROG=0x7,<br>HALFBIAS=0x1, C <sub>L</sub> =75 pF                                 |                 | 58    |                      | 0     |

|                           |                               | BIASPROG=0x0,<br>HALFBIAS=0x1, C <sub>L</sub> =75 pF                                 |                 | 58    |                      | o     |

| R <sub>INPUT</sub>        | Input Resistance              |                                                                                      |                 | 100   |                      | Mohm  |

| 5                         | Load Resistance               | OPA0/OPA1                                                                            | 200             |       |                      | Ohm   |

| R <sub>LOAD</sub>         |                               | OPA2                                                                                 | 2000            |       |                      | Ohm   |

|                           | Load Current                  | OPA0/OPA1                                                                            |                 |       | 11                   | mA    |

| I <sub>LOAD_DC</sub>      |                               | OPA2                                                                                 |                 |       | 1.5                  | mA    |

| M                         |                               | OPAxHCMDIS=0                                                                         | V <sub>SS</sub> |       | V <sub>DD</sub>      | V     |

| V <sub>INPUT</sub>        | Input Voltage                 | OPAxHCMDIS=1                                                                         | V <sub>SS</sub> |       | V <sub>DD</sub> -1.2 | V     |

| V <sub>OUTPUT</sub>       | Output Voltage                |                                                                                      | V <sub>SS</sub> |       | V <sub>DD</sub>      | V     |

| М                         | Input Offect Veltage          | Unity Gain, V <sub>SS</sub> <v<sub>in<v<sub>DD,<br/>OPAxHCMDIS=0</v<sub></v<sub>     |                 | 6     |                      | mV    |

| V <sub>OFFSET</sub>       | Input Offset Voltage          | Unity Gain, V <sub>SS</sub> <v<sub>in<v<sub>DD-1.2,<br/>OPAxHCMDIS=1</v<sub></v<sub> |                 | 1     |                      | mV    |

| V <sub>OFFSET_DRIFT</sub> | Input Offset Voltage<br>Drift |                                                                                      |                 |       | 0.02                 | mV/°C |

|                           |                               | OPA0/OPA1 BIASPROG=0xF,<br>HALFBIAS=0x0                                              |                 | 46.11 |                      | V/µs  |

|                           |                               | OPA0/OPA1 BIASPROG=0x7,<br>HALFBIAS=0x1                                              |                 | 1.21  |                      | V/µs  |

| <b>CD</b>                 |                               | OPA0/OPA1 BIASPROG=0x0,<br>HALFBIAS=0x1                                              |                 | 0.16  |                      | V/µs  |

| SR <sub>OPAMP</sub>       | Slew Rate                     | OPA2 BIASPROG=0xF,<br>HALFBIAS=0x0                                                   |                 | 4.43  |                      | V/µs  |

|                           |                               | OPA2 BIASPROG=0x7,<br>HALFBIAS=0x1                                                   |                 | 1.30  |                      | V/µs  |

|                           |                               | OPA2 BIASPROG=0x0,<br>HALFBIAS=0x1                                                   |                 | 0.16  |                      | V/µs  |

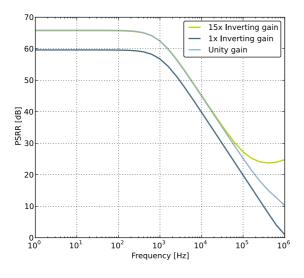

Figure 3.25. OPAMP Positive Power Supply Rejection Ratio

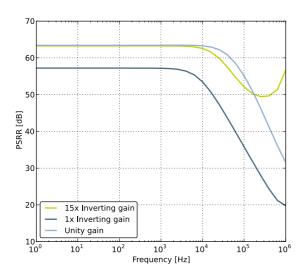

Figure 3.26. OPAMP Negative Power Supply Rejection Ratio

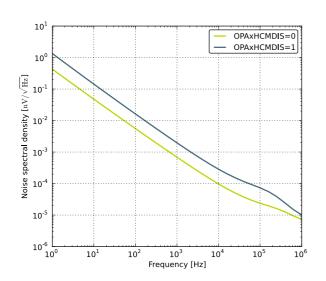

Figure 3.27. OPAMP Voltage Noise Spectral Density (Unity Gain) Vout=1V

## 3.14 Voltage Comparator (VCMP)

#### Table 3.18. VCMP

| Symbol                  | Parameter                             | Condition                                                             | Min | Тур             | Мах | Unit |

|-------------------------|---------------------------------------|-----------------------------------------------------------------------|-----|-----------------|-----|------|

| V <sub>VCMPIN</sub>     | Input voltage range                   |                                                                       |     | V <sub>DD</sub> |     | V    |

| V <sub>VCMPCM</sub>     | VCMP Common<br>Mode voltage range     |                                                                       |     | V <sub>DD</sub> |     | V    |

|                         | Active current                        | BIASPROG=0b0000 and<br>HALFBIAS=1 in VCMPn_CTRL<br>register           |     | 0.3             | 0.6 | μA   |

| IVCMP                   | Active current                        | BIASPROG=0b1111 and<br>HALFBIAS=0 in VCMPn_CTRL<br>register. LPREF=0. |     | 22              | 30  | μA   |

| t <sub>VCMPREF</sub>    | Startup time refer-<br>ence generator | NORMAL                                                                |     | 10              |     | μs   |

| M                       | Offect veltage                        | Single ended                                                          |     | 10              |     | mV   |

| V <sub>VCMPOFFSET</sub> | Offset voltage                        | Differential                                                          |     | 10              |     | mV   |

| V <sub>VCMPHYST</sub>   | VCMP hysteresis                       |                                                                       |     | 17              |     | mV   |

| t <sub>VCMPSTART</sub>  | Startup time                          |                                                                       |     |                 | 10  | μs   |

The  $V_{DD}$  trigger level can be configured by setting the TRIGLEVEL field of the VCMP\_CTRL register in accordance with the following equation:

VCMP Trigger Level as a Function of Level Setting

V<sub>DD Trigger Level</sub>=1.667V+0.034 ×TRIGLEVEL

(3.2)

|       | QFP64 Pin#<br>and Name |                                                | Pin Alternate Functio                          | onality / Description                         |                                            |

|-------|------------------------|------------------------------------------------|------------------------------------------------|-----------------------------------------------|--------------------------------------------|

| Pin # | Pin Name               | Analog                                         | Timers                                         | Communication                                 | Other                                      |

| 32    | PD4                    | ADC0_CH4<br>OPAMP_P2                           |                                                | LEU0_TX #0                                    |                                            |

| 33    | PD5                    | ADC0_CH5<br>OPAMP_OUT2 #0                      |                                                | LEU0_RX #0                                    |                                            |

| 34    | PD6                    | ADC0_CH6<br>DAC0_P1 /<br>OPAMP_P1              | TIM1_CC0 #4<br>LETIM0_OUT0 #0<br>PCNT0_S0IN #3 | US1_RX #2<br>I2C0_SDA #1                      | LES_ALTEX0 #0<br>ACMP0_O #2                |

| 35    | PD7                    | ADC0_CH7<br>DAC0_N1 /<br>OPAMP_N1              | TIM1_CC1 #4<br>LETIM0_OUT1 #0<br>PCNT0_S1IN #3 | US1_TX #2<br>I2C0_SCL #1                      | CMU_CLK0 #2<br>LES_ALTEX1 #0<br>ACMP1_O #2 |

| 36    | PD8                    |                                                |                                                |                                               | CMU_CLK1 #1                                |

| 37    | PC6                    | ACMP0_CH6                                      |                                                | I2C0_SDA #2                                   | LES_CH6 #0                                 |

| 38    | PC7                    | ACMP0_CH7                                      |                                                | I2C0_SCL #2                                   | LES_CH7 #0                                 |

| 39    | VDD_DREG               | Power supply for on-chip voltage               | ge regulator.                                  | 1                                             | 1                                          |

| 40    | DECOUPLE               | Decouple output for on-chip vo                 | Itage regulator. An external capa              | acitance of size C <sub>DECOUPLE</sub> is rec | quired at this pin.                        |

| 41    | PE4                    | LCD_COM0                                       |                                                | US0_CS #1                                     |                                            |

| 42    | PE5                    | LCD_COM1                                       |                                                | US0_CLK #1                                    |                                            |

| 43    | PE6                    | LCD_COM2                                       |                                                | US0_RX #1                                     |                                            |

| 44    | PE7                    | LCD_COM3                                       |                                                | US0_TX #1                                     |                                            |

| 45    | PC12                   | ACMP1_CH4<br>DAC0_OUT1ALT #0/<br>OPAMP_OUT1ALT |                                                |                                               | CMU_CLK0 #1<br>LES_CH12 #0                 |

| 46    | PC13                   | ACMP1_CH5<br>DAC0_OUT1ALT #1/<br>OPAMP_OUT1ALT | TIM1_CC0 #0<br>TIM1_CC2 #4<br>PCNT0_S0IN #0    |                                               | LES_CH13 #0                                |

| 47    | PC14                   | ACMP1_CH6<br>DAC0_OUT1ALT #2/<br>OPAMP_OUT1ALT | TIM1_CC1 #0<br>PCNT0_S1IN #0                   | US0_CS #3                                     | LES_CH14 #0                                |

| 48    | PC15                   | ACMP1_CH7<br>DAC0_OUT1ALT #3/<br>OPAMP_OUT1ALT | TIM1_CC2 #0                                    | US0_CLK #3                                    | LES_CH15 #0<br>DBG_SWO #1                  |

| 49    | PF0                    |                                                | TIM0_CC0 #5<br>LETIM0_OUT0 #2                  | US1_CLK #2<br>LEU0_TX #3<br>I2C0_SDA #5       | DBG_SWCLK #0/1                             |

| 50    | PF1                    |                                                | TIM0_CC1 #5<br>LETIM0_OUT1 #2                  | US1_CS #2<br>LEU0_RX #3<br>I2C0_SCL #5        | DBG_SWDIO #0/1<br>GPIO_EM4WU3              |

| 51    | PF2                    | LCD_SEG0                                       | TIM0_CC2 #5                                    | LEU0_TX #4                                    | ACMP1_O #0<br>DBG_SWO #0<br>GPIO_EM4WU4    |

| 52    | PF3                    | LCD_SEG1                                       |                                                |                                               | PRS_CH0 #1                                 |

| 53    | PF4                    | LCD_SEG2                                       |                                                |                                               | PRS_CH1 #1                                 |

| 54    | PF5                    | LCD_SEG3                                       |                                                |                                               | PRS_CH2 #1                                 |

| 55    | IOVDD_5                | Digital IO power supply 5.                     |                                                | 1                                             | 1                                          |

| 56    | VSS                    | Ground.                                        |                                                |                                               |                                            |

| 57    | PE8                    | LCD_SEG4                                       |                                                |                                               | PRS_CH3 #1                                 |

| 58    | PE9                    | LCD_SEG5                                       |                                                |                                               |                                            |

| 59    | PE10                   | LCD_SEG6                                       | TIM1_CC0 #1                                    | US0_TX #0                                     | BOOT_TX                                    |

| 60    | PE11                   | LCD_SEG7                                       | TIM1_CC1 #1                                    | US0_RX #0                                     | LES_ALTEX5 #0<br>BOOT_RX                   |

### **EFM°32**

### ...the world's most energy friendly microcontrollers

| Alternate                       | LOCATION |      |      |      |     |     |      |                                                                                                                                                                     |

|---------------------------------|----------|------|------|------|-----|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality                   | 0        | 1    | 2    | 3    | 4   | 5   | 6    | Description                                                                                                                                                         |

| CMU_CLK1                        | PA1      | PD8  | PE12 |      |     |     |      | Clock Management Unit, clock output number 1.                                                                                                                       |

| DAC0_N0 /<br>OPAMP_N0           | PC5      |      |      |      |     |     |      | Operational Amplifier 0 external negative input.                                                                                                                    |

| DAC0_N1 /<br>OPAMP_N1           | PD7      |      |      |      |     |     |      | Operational Amplifier 1 external negative input.                                                                                                                    |

| OPAMP_N2                        | PD3      |      |      |      |     |     |      | Operational Amplifier 2 external negative input.                                                                                                                    |

| DAC0_OUT0 /<br>OPAMP_OUT0       | PB11     |      |      |      |     |     |      | Digital to Analog Converter DAC0_OUT0 / OPAMP output channel number 0.                                                                                              |

| DAC0_OUT0ALT /<br>OPAMP_OUT0ALT |          |      |      |      | PD0 |     |      | Digital to Analog Converter DAC0_OUT0ALT / OPAMP alternative output for channel 0.                                                                                  |

| DAC0_OUT1ALT /<br>OPAMP_OUT1ALT | PC12     | PC13 | PC14 | PC15 | PD1 |     |      | Digital to Analog Converter DAC0_OUT1ALT / OPAMP alternative output for channel 1.                                                                                  |

| OPAMP_OUT2                      | PD5      | PD0  |      |      |     |     |      | Operational Amplifier 2 output.                                                                                                                                     |

| DAC0_P0 /<br>OPAMP_P0           | PC4      |      |      |      |     |     |      | Operational Amplifier 0 external positive input.                                                                                                                    |

| DAC0_P1 /<br>OPAMP_P1           | PD6      |      |      |      |     |     |      | Operational Amplifier 1 external positive input.                                                                                                                    |

| OPAMP_P2                        | PD4      |      |      |      |     |     |      | Operational Amplifier 2 external positive input.                                                                                                                    |

|                                 |          |      |      |      |     |     |      | Debug-interface Serial Wire clock input.                                                                                                                            |

| DBG_SWCLK                       | PF0      | PF0  |      |      |     |     |      | Note that this function is enabled to pin out of reset, and has a built-in pull down.                                                                               |

|                                 | PF1      | PF1  |      |      |     |     |      | Debug-interface Serial Wire data input / output.                                                                                                                    |

| DBG_SWDIO                       |          |      |      |      |     |     |      | Note that this function is enabled to pin out of reset, and has a built-in pull up.                                                                                 |

|                                 |          |      |      |      |     |     |      | Debug-interface Serial Wire viewer Output.                                                                                                                          |

| DBG_SWO                         | PF2      | PC15 |      |      |     |     |      | Note that this function is not enabled after reset, and must be<br>enabled by software to be used.                                                                  |

| GPIO_EM4WU0                     | PA0      |      |      |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                      |

| GPIO_EM4WU3                     | PF1      |      |      |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                      |

| GPIO_EM4WU4                     | PF2      |      |      |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                      |

| GPIO_EM4WU5                     | PE13     |      |      |      |     |     |      | Pin can be used to wake the system up from EM4                                                                                                                      |

| HFXTAL_N                        | PB14     |      |      |      |     |     |      | High Frequency Crystal negative pin. Also used as external optional clock input pin.                                                                                |

| HFXTAL_P                        | PB13     |      |      |      |     |     |      | High Frequency Crystal positive pin.                                                                                                                                |

| I2C0_SCL                        | PA1      | PD7  | PC7  |      |     | PF1 | PE13 | I2C0 Serial Clock Line input / output.                                                                                                                              |

| I2C0_SDA                        | PA0      | PD6  | PC6  |      |     | PF0 | PE12 | I2C0 Serial Data input / output.                                                                                                                                    |

| LCD_BCAP_N                      | PA13     |      |      |      |     |     |      | LCD voltage booster (optional), boost capacitor, negative pin.<br>If using the LCD voltage booster, connect a 22 nF capacitor<br>between LCD_BCAP_N and LCD_BCAP_P. |

| LCD_BCAP_P                      | PA12     |      |      |      |     |     |      | LCD voltage booster (optional), boost capacitor, positive pin.<br>If using the LCD voltage booster, connect a 22 nF capacitor<br>between LCD_BCAP_N and LCD_BCAP_P. |

| LCD_BEXT                        | PA14     |      |      |      |     |     |      | LCD voltage booster (optional), boost output. If using the LCD voltage booster, connect a 1 uF capacitor between this pin and VSS.                                  |

|                                 |          |      |      |      |     |     |      | An external LCD voltage may also be applied to this pin if the booster is not enabled.                                                                              |

|                                 |          |      |      |      |     |     |      | If AVDD is used directly as the LCD supply voltage, this pin may be left unconnected or used as a GPIO.                                                             |

| LCD_COM0                        | PE4      |      |      |      |     |     |      | LCD driver common line number 0.                                                                                                                                    |

| LCD_COM1                        | PE5      |      |      |      |     |     |      | LCD driver common line number 1.                                                                                                                                    |

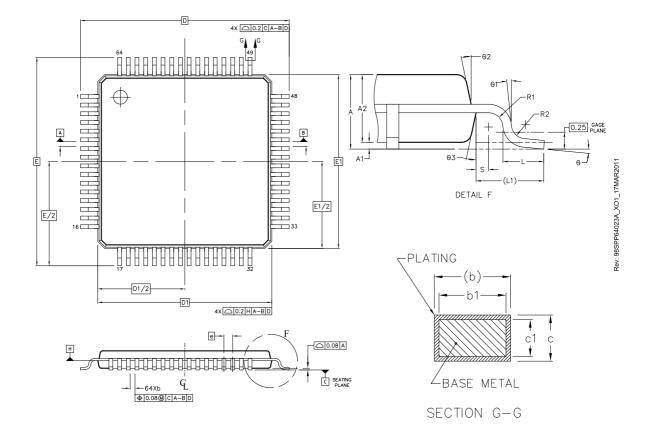

## 4.5 TQFP64 Package

#### Figure 4.3. TQFP64

#### Note:

- 1. All dimensions & tolerancing confirm to ASME Y14.5M-1994.

- 2. The top package body size may be smaller than the bottom package body size.

- 3. Datum 'A,B', and 'B' to be determined at datum plane 'H'.

- 4. To be determined at seating place 'C'.

- 5. Dimension 'D1' and 'E1' do not include mold protrusions. Allowable protrusion is 0.25mm per side. 'D1' and 'E1' are maximum plastic body size dimension including mold mismatch. Dimension 'D1' and 'E1' shall be determined at datum plane 'H'.

- 6. Detail of Pin 1 indicatifier are option all but must be located within the zone indicated.

- 7. Dimension 'b' does not include dambar protrusion. Allowable dambar protrusion shall not cause the lead width to exceed the maximum 'b' dimension by more than 0.08 mm. Dambar can not be located on the lower radius or the foot. Minimum space between protrusion and an adjacent lead is 0.07 mm

- 8. Exact shape of each corner is optional.

- 9. These dimension apply to the flat section of the lead between 0.10 mm and 0.25 mm from the lead tip. 10All dimensions are in millimeters.

| DIM | MIN  | NOM  | MAX  | DIM | MIN  | NOM | MAX  |

|-----|------|------|------|-----|------|-----|------|

| A   | -    | 1.10 | 1.20 | L1  |      | -   | -    |

| A1  | 0.05 | -    | 0.15 | R1  | 0.08 | -   | -    |

| A2  | 0.95 | 1.00 | 1.05 | R2  | 0.08 | -   | 0.20 |

#### Table 4.4. QFP64 (Dimensions in mm)

Added link to Environmental and Quality information.

Re-added missing DAC-data.

## 7.4 Revision 1.20

September 30th, 2013

Added I2C characterization data.

Corrected GPIO operating voltage from 1.8 V to 1.85 V.

Corrected the ADC gain and offset measurement reference voltage from 2.25 to 2.5V.

Corrected the ADC resolution from 12, 10 and 6 bit to 12, 8 and 6 bit.

Document changed status from "Preliminary".

Updated Environmental information.

Updated trademark, disclaimer and contact information.

Other minor corrections.

## 7.5 Revision 1.10

June 28th, 2013

Updated power requirements in the Power Management section.

Removed minimum load capacitance figure and table. Added reference to application note.

Other minor corrections.

### 7.6 Revision 1.00

September 11th, 2012

Updated the HFRCO 1 MHz band typical value to 1.2 MHz.

Updated the HFRCO 7 MHz band typical value to 6.6 MHz.

Added GPIO\_EM4WU3, GPIO\_EM4WU4 and GPIO\_EM4WU5 pins and removed GPIO\_EM4WU1 in the Alternate functionality overview table.

Other minor corrections.

### 7.7 Revision 0.96

May 4th, 2012

Corrected PCB footprint figures and tables.

## 7.8 Revision 0.95

February 27th, 2012

Corrected operating voltage from 1.8 V to 1.85 V.

Added rising POR level and corrected Thermometer output gradient in Electrical Characteristics section.

Updated Minimum Load Capacitance (C<sub>LFXOL</sub>) Requirement For Safe Crystal Startup.

Added Gain error drift and Offset error drift to ADC table.

Added reference to errata document.

### 7.9 Revision 0.92

July 22nd, 2011

Updated current consumption numbers from latest device characterization data.

Updated OPAMP electrical characteristics.

Made ADC plots render properly in Adobe Reader.

Corrected number of DAC channels available.

## 7.10 Revision 0.90

June 30th, 2011

Initial preliminary release.

# List of Equations

| 3.1. Total ACMP Active Current                                      | 40 |

|---------------------------------------------------------------------|----|

| 3.2. VCMP Trigger Level as a Function of Level Setting              | 42 |

| 3.3. Total LCD Current Based on Operational Mode and Internal Boost |    |