Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 49                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f65j50t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name             | Pin Number        | Pin     | Buffer     | Description                                    |  |  |  |  |

|----------------------|-------------------|---------|------------|------------------------------------------------|--|--|--|--|

| Pin Name             | 80-TQFP           | Туре    | Туре       | Description                                    |  |  |  |  |

|                      |                   |         |            | PORTE is a bidirectional I/O port (continued). |  |  |  |  |

| RE6/AD14/PMA10/P1B   | 74                |         |            |                                                |  |  |  |  |

| RE6                  |                   | I/O     | ST         | Digital I/O.                                   |  |  |  |  |

| AD14                 |                   | I/O     | TTL        | External memory address/data 14.               |  |  |  |  |

| PMA10                |                   | 0       | —          | Parallel Master Port address.                  |  |  |  |  |

| P1B <sup>(3)</sup>   |                   | 0       | —          | ECCP1 PWM output B.                            |  |  |  |  |

| RE7/AD15/PMA9/       | 73                |         |            |                                                |  |  |  |  |

| ECCP2/P2A            |                   |         |            |                                                |  |  |  |  |

| RE7                  |                   | I/O     | ST         | Digital I/O.                                   |  |  |  |  |

| AD15                 |                   | I/O     | TTL        | External memory address/data 15.               |  |  |  |  |

| PMA9                 |                   | 0       | —          | Parallel Master Port address.                  |  |  |  |  |

| ECCP2 <sup>(4)</sup> |                   | I/O     | ST         | Capture 2 input/Compare 2 output/PWM2 output.  |  |  |  |  |

| P2A <sup>(4)</sup>   |                   | 0       | —          | ECCP2 PWM output A.                            |  |  |  |  |

| Legend: TTL = TTL co | ompatible input   |         |            | CMOS = CMOS compatible input or output         |  |  |  |  |

| ST = Schmi           | itt Trigger input | with CN | IOS levels | s Analog = Analog input                        |  |  |  |  |

#### TABLE 1-4: PIC18F8XJ5X PINOUT I/O DESCRIPTIONS (CONTINUED)

P = Power OD = Open-Drain (no P diode to VDD)

Note 1: Alternate assignment for ECCP2/P2A when CCP2MX Configuration bit is cleared (Extended Microcontroller mode).

0

= Output

2: Default assignment for ECCP2/P2A for all devices in all operating modes (CCP2MX is set).

3: Default assignments for P1B/P1C/P3B/P3C (ECCPMX Configuration bit is set).

4: Alternate assignment for ECCP2/P2A when CCP2MX is cleared (Microcontroller mode).

5: Alternate assignments for P1B/P1C/P3B/P3C (ECCPMX Configuration bit is cleared).

- **6:** Pin placement when PMPMX = 1.

- **7:** Pin placement when PMPMX = 0.

= Input

Т

8: RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

| TABLE 4-2: |                  | ION CONDITIO | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |                                                                            |                                 |  |  |  |  |  |  |  |

|------------|------------------|--------------|---------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|--|--|

| Register   | Applicab         | le Devices   | Power-on Reset,<br>Brown-out Reset                      | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |  |  |  |  |  |  |

| ADRESH     | DRESH Feature1 P |              | XXXX XXXX                                               | นนนน นนนน                                                                  | นนนน นนนน                       |  |  |  |  |  |  |  |

| ADRESL     | Feature1         | PIC18F8XJ5X  | XXXX XXXX                                               | սսսս սսսս                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| ADCON0     | Feature1         | PIC18F8XJ5X  | 0000 0000                                               | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| ADCON1     | Feature1         | PIC18F8XJ5X  | 0000 0000                                               | 0000 0000                                                                  | սսսս սսսս                       |  |  |  |  |  |  |  |

| ANCON0     | Feature1         | PIC18F8XJ5X  | 00 0000                                                 | uu uuuu                                                                    | uu uuuu                         |  |  |  |  |  |  |  |

| ANCON1     | Feature1         | PIC18F8XJ5X  | 0000 00                                                 | uuuu uu                                                                    | uuuu uu                         |  |  |  |  |  |  |  |

| WDTCON     | Feature1         | PIC18F8XJ5X  | 0x-00                                                   | 0x-u0                                                                      | ux-uu                           |  |  |  |  |  |  |  |

| ECCP1AS    | Feature1         | PIC18F8XJ5X  | 0000 0000                                               | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| ECCP1DEL   | Feature1         | PIC18F8XJ5X  | 0000 0000                                               | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| CCPR1H     | Feature1         | PIC18F8XJ5X  | XXXX XXXX                                               | սսսս սսսս                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| CCPR1L     | Feature1         | PIC18F8XJ5X  | XXXX XXXX                                               | սսսս սսսս                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| CCP1CON    | Feature1         | PIC18F8XJ5X  | 0000 0000                                               | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| ECCP2AS    | Feature1         | PIC18F8XJ5X  | 0000 0000                                               | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| ECCP2DEL   | Feature1         | PIC18F8XJ5X  | 0000 0000                                               | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| CCPR2H     | Feature1         | PIC18F8XJ5X  | XXXX XXXX                                               | սսսս սսսս                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| CCPR2L     | Feature1         | PIC18F8XJ5X  | XXXX XXXX                                               | սսսս սսսս                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| CCP2CON    | Feature1         | PIC18F8XJ5X  | 0000 0000                                               | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| ECCP3AS    | Feature1         | PIC18F8XJ5X  | 0000 0000                                               | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| ECCP3DEL   | Feature1         | PIC18F8XJ5X  | 0000 0000                                               | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| CCPR3H     | Feature1         | PIC18F8XJ5X  | XXXX XXXX                                               | սսսս սսսս                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| CCPR3L     | Feature1         | PIC18F8XJ5X  | XXXX XXXX                                               | սսսս սսսս                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| CCP3CON    | Feature1         | PIC18F8XJ5X  | 0000 0000                                               | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| SPBRG1     | Feature1         | PIC18F8XJ5X  | 0000 0000                                               | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| RCREG1     | Feature1         | PIC18F8XJ5X  | 0000 0000                                               | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| TXREG1     | Feature1         | PIC18F8XJ5X  | XXXX XXXX                                               | սսսս սսսս                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| TXSTA1     | Feature1         | PIC18F8XJ5X  | 0000 0010                                               | 0000 0010                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| RCSTA1     | Feature1         | PIC18F8XJ5X  | 0000 000x                                               | x000 0000x                                                                 | uuuu uuuu                       |  |  |  |  |  |  |  |

| SPBRG2     | Feature1         | PIC18F8XJ5X  | 0000 0000                                               | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| RCREG2     | Feature1         | PIC18F8XJ5X  | 0000 0000                                               | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| TXREG2     | Feature1         | PIC18F8XJ5X  | 0000 0000                                               | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| TXSTA2     | Feature1         | PIC18F8XJ5X  | 0000 0010                                               | 0000 0010                                                                  | uuuu uuuu                       |  |  |  |  |  |  |  |

| EECON2     | Feature1         | PIC18F8XJ5X  |                                                         |                                                                            |                                 |  |  |  |  |  |  |  |

| EECON1     | Feature1         | PIC18F8XJ5X  | 00 x00-                                                 | 00 u00-                                                                    | 00 u00-                         |  |  |  |  |  |  |  |

### TABLE 4-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- **4:** See Table 4-1 for Reset value for specific condition.

| PMMODEH         Feature1         PIC18F8XJ5X         0000         0000         0000         0000         uuuu         uuuu           PMMODEL         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu | TABLE 4-2: | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |             |           |                                                |           |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------|-------------|-----------|------------------------------------------------|-----------|--|--|--|--|

| PMMODEH         Feature1         PIC18F8XJ5X         0000         0000         0000         0000         uuuu         uuuu           PMMODEL         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu | Register   | Applicable Devices                                      |             |           | WDT Reset<br>RESET Instruction<br>Stack Resets |           |  |  |  |  |

| PMMODEL         Feature1         PIC18F8XJ5X         0000         0000         0000         0000         uuuu         uuuu           PMDOUT2H         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMDOUT2H         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMDOUT2L         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMDIN2H         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMDIN2L         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMEH         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMEL         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMSTATH         Feature1         PIC18F8XJ5X         00         0000         00         uu         uuuu                                                                                                                       | PMCONL     | Feature1                                                | PIC18F8XJ5X | 0000 0000 | 0000 0000                                      | uuuu uuuu |  |  |  |  |

| PMDOUT2H         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMDOUT2L         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMDOUT2L         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMDIN2H         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMDIN2L         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMEH         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMEL         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMSTATH         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu                                                                                                                                                                                                                                                      | PMMODEH    | Feature1                                                | PIC18F8XJ5X | 0000 0000 | 0000 0000                                      | นนนน นนนน |  |  |  |  |

| PMDOUT2L         Feature1         PIC18F8XJ5X         0000         0000         0000         0000         uuuu         uuuu           PMDIN2H         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMDIN2L         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMDIN2L         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMEH         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMEL         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMSTATH         Feature1         PIC18F8XJ5X         00         0000         00         uuuu                                                                                                                                                                                                                                                                                                                                                                                    | PMMODEL    | Feature1                                                | PIC18F8XJ5X | 0000 0000 | 0000 0000                                      | սսսս սսսս |  |  |  |  |

| PMDIN2H         Feature1         PIC18F8XJ5X         0000         0000         0000         0000         uuuu         uuuu           PMDIN2L         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMEH         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMEL         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMSTATH         Feature1         PIC18F8XJ5X         00         0000         00         uuuu         uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PMDOUT2H   | Feature1                                                | PIC18F8XJ5X | 0000 0000 | 0000 0000                                      | սսսս սսսս |  |  |  |  |

| PMDIN2L         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMEH         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMEL         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu         uuuu           PMSTATH         Feature1         PIC18F8XJ5X         00         0000         00         uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PMDOUT2L   | Feature1                                                | PIC18F8XJ5X | 0000 0000 | 0000 0000                                      | սսսս սսսս |  |  |  |  |

| PMEH         Feature1         PIC18F8XJ5X         0000 0000         0000 0000         uuuu uuuu           PMEL         Feature1         PIC18F8XJ5X         0000 0000         0000 0000         uuuu uuuu           PMSTATH         Feature1         PIC18F8XJ5X         00 0000         00 0000         uu uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PMDIN2H    | Feature1                                                | PIC18F8XJ5X | 0000 0000 | 0000 0000                                      | uuuu uuuu |  |  |  |  |

| PMEL         Feature1         PIC18F8XJ5X         0000         0000         0000         uuuu           PMSTATH         Feature1         PIC18F8XJ5X         00         0000         00         0000         uuuu           PMSTATH         Feature1         PIC18F8XJ5X         00         0000         00         0000         uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PMDIN2L    | Feature1                                                | PIC18F8XJ5X | 0000 0000 | 0000 0000                                      | uuuu uuuu |  |  |  |  |

| PMSTATH         Feature1         PIC18F8XJ5X         00         0000         00         0000         uu         uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PMEH       | Feature1                                                | PIC18F8XJ5X | 0000 0000 | 0000 0000                                      | นนนน นนนน |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PMEL       | Feature1                                                | PIC18F8XJ5X | 0000 0000 | 0000 0000                                      | นนนน นนนน |  |  |  |  |

| PMSTATL         Feature1         PIC18F8XJ5X         10         1111         10         1111         uu         uuuu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PMSTATH    | Feature1                                                | PIC18F8XJ5X | 00 0000   | 00 0000                                        | uu uuuu   |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PMSTATL    | Feature1                                                | PIC18F8XJ5X | 10 1111   | 10 1111                                        | uu uuuu   |  |  |  |  |

# TABLE 4-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

4: See Table 4-1 for Reset value for specific condition.

# 10.5 PORTD, TRISD and LATD Registers

PORTD is an 8-bit wide, bidirectional port. All pins on PORTD are digital only and tolerate voltages up to 5.5V.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

| Note: | These pins are configured as digital inputs |

|-------|---------------------------------------------|

|       | on any device Reset.                        |

On 80-pin devices, PORTD is multiplexed with the system bus as part of the external memory interface. I/O port and other functions are only available when the interface is disabled by setting the EBDIS bit (MEMCON<7>). When the interface is enabled, PORTD is the low-order byte of the multiplexed address/data bus (AD7:AD0). The TRISD bits are also overridden.

PORTD can also be configured to function as an 8-bit wide Parallel Master Port data. In this mode, Parallel Master Port takes priority over the other digital I/O (but not the external memory interface). This multiplexing is available when PMPMX = 1. When the Parallel Master Port is active, the input buffers are TTL. For more information, refer to **Section 11.0 "Parallel Master Port"**

Each of the PORTD pins has a weak internal pull-up. The pull-ups are provided to keep the inputs at a known state for the external memory interface while powering up. A single control bit can turn off all the pull-ups. This is performed by clearing bit, RDPU (PORTG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on all device Resets.

| EXAMPLE 10-4: | INITIALIZING PORTD |

|---------------|--------------------|

|               |                    |

| CLRF PORTD  | ; Initialize PORTD by ; clearing output |

|-------------|-----------------------------------------|

|             | ; data latches                          |

| CLRF LATD   | ; Alternate method to clear             |

|             | ; output data latches                   |

| MOVLW OCFh  | ; Value used to initialize              |

|             | ; data direction                        |

| MOVWF TRISD | ; Set RD<3:0> as inputs                 |

|             | ; RD<5:4> as outputs                    |

|             | ; RD<7:6> as inputs                     |

|             |                                         |

| Pin Name   | Function            | TRIS<br>Setting | I/O                          | I/O<br>Type | Description                                                                                                                                                  |  |  |  |  |

|------------|---------------------|-----------------|------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RE0/AD8/   | RE0                 | 0               | 0                            | DIG         | LATE<0> data output.                                                                                                                                         |  |  |  |  |

| PMRD/P2D   |                     | 1               | I                            | ST          | PORTE<0> data input.                                                                                                                                         |  |  |  |  |

|            | AD8 <sup>(3)</sup>  | х               | 0                            | DIG         | External memory interface, address/data bit 8 output. <sup>(2)</sup>                                                                                         |  |  |  |  |

|            |                     | х               | I                            | TTL         | External memory interface, data bit 8 input. <sup>(2)</sup>                                                                                                  |  |  |  |  |

|            | PMRD <sup>(5)</sup> | х               | 0                            | DIG         | Parallel Master Port read strobe pin.                                                                                                                        |  |  |  |  |

|            |                     | х               | I                            | TTL         | Parallel Master Port read pin.                                                                                                                               |  |  |  |  |

|            | P2D                 | 0               | 0                            | DIG         | ECCP2 Enhanced PWM output, channel D; takes priority over port<br>and PMP data. May be configured for tri-state during Enhanced PWM<br>shutdown events.      |  |  |  |  |

| RE1/AD9/   | RE1                 | 0               | 0 O DIG LATE<1> data output. |             |                                                                                                                                                              |  |  |  |  |

| PMWR/P2C   |                     | 1               | I                            | ST          | STPORTE<1> data input.DIGExternal memory interface, address/data bit 9 output. <sup>(2)</sup> TTLExternal memory interface, data bit 9 input. <sup>(2)</sup> |  |  |  |  |

|            | AD9 <sup>(3)</sup>  | х               | 0                            | DIG         | External memory interface, address/data bit 9 output. <sup>(2)</sup>                                                                                         |  |  |  |  |

|            |                     | х               | I                            | TTL         | External memory interface, data bit 9 input. <sup>(2)</sup>                                                                                                  |  |  |  |  |

|            | PMWR <sup>(5)</sup> | х               | 0                            | DIG         | Parallel Master Port write strobe pin.                                                                                                                       |  |  |  |  |

|            |                     | х               | I                            | TTL         | Parallel Master Port write pin.                                                                                                                              |  |  |  |  |

|            | P2C                 | 0               | 0                            | DIG         | ECCP2 Enhanced PWM output, channel C; takes priority over port<br>and PMP data. May be configured for tri-state during Enhanced PWM<br>shutdown events.      |  |  |  |  |

| RE2/AD10/  | RE2                 | 0               | 0                            | DIG         | LATE<2> data output.                                                                                                                                         |  |  |  |  |

| PMBE/P2B   |                     | 1               | I                            | ST          | PORTE<2> data input.                                                                                                                                         |  |  |  |  |

|            | AD10 <sup>(3)</sup> | х               | 0                            | DIG         | External memory interface, address/data bit 10 output. <sup>(2)</sup>                                                                                        |  |  |  |  |

|            |                     | х               | I                            | TTL         | External memory interface, data bit 10 input. <sup>(2)</sup>                                                                                                 |  |  |  |  |

|            | PMBE <sup>(5)</sup> | х               | 0                            | DIG         | Parallel Master Port byte enable.                                                                                                                            |  |  |  |  |

|            | P2B                 | 0               | 0                            | DIG         | ECCP2 Enhanced PWM output, channel B; takes priority over port and PMP data. May be configured for tri-state during Enhanced PWM shutdown events.            |  |  |  |  |

| RE3/AD11/  | RE3                 | 0               | 0                            | DIG         | LATE<3> data output.                                                                                                                                         |  |  |  |  |

| PMA13/P3C/ |                     | 1               | I                            | ST          | PORTE<3> data input.                                                                                                                                         |  |  |  |  |

| REFO       | AD11 <sup>(3)</sup> | х               | 0                            | DIG         | External memory interface, address/data bit 11 output. <sup>(2)</sup>                                                                                        |  |  |  |  |

|            |                     | х               | I                            | TTL         | External memory interface, data bit 11 input. <sup>(2)</sup>                                                                                                 |  |  |  |  |

|            | PMA13               | х               | 0                            | DIG         | Parallel Master Port address.                                                                                                                                |  |  |  |  |

|            | P3C <sup>(1)</sup>  | 0               | 0                            | DIG         | ECCP3 Enhanced PWM output, channel C; takes priority over port<br>and PMP data. May be configured for tri-state during Enhanced PWM<br>shutdown events.      |  |  |  |  |

|            | REFO                | х               | 0                            | DIG         | Reference output clock.                                                                                                                                      |  |  |  |  |

| RE4/AD12/  | RE4                 | 0               | 0                            | DIG         | LATE<4> data output.                                                                                                                                         |  |  |  |  |

| PMA12/P3B  |                     | 1               | I                            | ST          | PORTE<4> data input.                                                                                                                                         |  |  |  |  |

|            | AD12 <sup>(3)</sup> | х               | 0                            | DIG         | External memory interface, address/data bit 12 output. <sup>(2)</sup>                                                                                        |  |  |  |  |

|            |                     | х               | Ι                            | TTL         | External memory interface, data bit 12 input. <sup>(2)</sup>                                                                                                 |  |  |  |  |

|            | PMA12               | x               | 0                            | DIG         | Parallel Master Port address.                                                                                                                                |  |  |  |  |

|            | P3B <sup>(1)</sup>  | 0               | 0                            | DIG         | ECCP3 Enhanced PWM output, channel B; takes priority over port and PMP data. May be configured for tri-state during Enhanced PWM shutdown events.            |  |  |  |  |

TABLE 10-12 PORTE FUNCTIONS

x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Default assignments for P1B/P1C and P3B/P3C when ECCPMX Configuration bit is set (80-pin devices only).

2: External memory interface I/O takes priority over all other digital and PMP I/O.

3: Available on 80-pin devices only.

4: Alternate assignment for ECCP2/P2A when ECCP2MX Configuration bit is cleared (all devices in Microcontroller mode).

**5:** Default configuration for PMP (PMPMX Configuration bit = 1).

| Pin Name                                                                 | Function            | TRIS<br>Setting                                                                        | I/O | l/O<br>Type | Description                                                                                                        |  |  |

|--------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------|-----|-------------|--------------------------------------------------------------------------------------------------------------------|--|--|

| RF2/PMA5/                                                                | RF2                 | 0                                                                                      | 0   | DIG         | LATF<2> data output; not affected by analog input.                                                                 |  |  |

| AN7/C2INB                                                                |                     | 1                                                                                      | Ι   | ST          | PORTF<2> data input; disabled when analog input enabled.                                                           |  |  |

|                                                                          | PMA5                | х                                                                                      | 0   | DIG         | Parallel Master Port address.                                                                                      |  |  |

|                                                                          | AN7                 | 1                                                                                      | Ι   | ANA         | A/D input channel 7. Default configuration on POR.                                                                 |  |  |

|                                                                          | C2INB               | х                                                                                      | Ι   | ANA         | Comparator 2 input B.                                                                                              |  |  |

| RF3/D-                                                                   | RF3                 | 1                                                                                      |     | ST          | PORTF<3> data input; disabled when analog input enabled.                                                           |  |  |

| D-<br>I XVCR USB bus differential minus line output (internal transceive |                     |                                                                                        |     |             |                                                                                                                    |  |  |

|                                                                          |                     |                                                                                        | Ι   | XVCR        | USB bus differential minus line input (internal transceiver).                                                      |  |  |

| RF4/D+                                                                   | RF4                 | 1                                                                                      |     | ST          |                                                                                                                    |  |  |

|                                                                          | D+                  |                                                                                        | 0   | XVCR        | USB bus differential plus line output (internal transceiver).                                                      |  |  |

|                                                                          |                     |                                                                                        | I   | XVCR        | USB bus differential plus line input (internal transceiver).                                                       |  |  |

| AN10/C1INB/ CVREF output enabled.                                        |                     | LATF<5> data output; not affected by analog input. Disabled when CVREF output enabled. |     |             |                                                                                                                    |  |  |

| CVREF                                                                    |                     | 1                                                                                      | I   | ST          | PORTF<5> data input; disabled when analog input enabled. Disabled when CVREF output enabled.                       |  |  |

|                                                                          | PMD2 <sup>(1)</sup> | х                                                                                      | 0   | DIG         | Parallel Master Port data out.                                                                                     |  |  |

|                                                                          |                     | х                                                                                      | I   | TTL         | Parallel Master Port data input.                                                                                   |  |  |

|                                                                          | AN10                | 1                                                                                      | I   | ANA         | A/D input channel 10 and Comparator C1+ input. Default input configuration on POR.                                 |  |  |

|                                                                          | C1INB               | х                                                                                      | Ι   | ANA         | Comparator 1 input B.                                                                                              |  |  |

|                                                                          | CVREF               | х                                                                                      | 0   | ANA         | Comparator voltage reference output. Enabling this feature disables digital I/O.                                   |  |  |

| RF6/PMD1/                                                                | RF6                 | 0                                                                                      | 0   | DIG         | LATF<6> data output; not affected by analog input.                                                                 |  |  |

| AN11/C1INA                                                               |                     | 1                                                                                      | Ι   |             |                                                                                                                    |  |  |

|                                                                          | PMD1 <sup>(1)</sup> | х                                                                                      | 0   | DIG         | Parallel Master Port data out.                                                                                     |  |  |

|                                                                          |                     | х                                                                                      | I   | TTL         | Parallel Master Port data input.                                                                                   |  |  |

|                                                                          | AN11                | 1                                                                                      | I   | ANA         | A/D input channel 11 and Comparator C1- input. Default input configuration on POR; does not affect digital output. |  |  |

|                                                                          | C1INA               | х                                                                                      | I   | ANA         | Comparator 1 input A.                                                                                              |  |  |

| RF7/PMD0/                                                                | RF7                 | 0                                                                                      | 0   | DIG         | LATF<7> data output.                                                                                               |  |  |

| SS1/C1OUT                                                                |                     | 1                                                                                      | Ι   | ST          | PORTF<7> data input.                                                                                               |  |  |

|                                                                          | PMD0 <sup>(1)</sup> | х                                                                                      | 0   | DIG         | Parallel Master Port data out.                                                                                     |  |  |

|                                                                          |                     | х                                                                                      | I   | TTL         | Parallel Master Port data input.                                                                                   |  |  |

|                                                                          | SS1                 | 1                                                                                      | I   | TTL         | Slave select input for MSSP1.                                                                                      |  |  |

|                                                                          | C10UT               | х                                                                                      | 0   | DIG         | Comparator 1 output.                                                                                               |  |  |

# TABLE 10-14: PORTF FUNCTIONS

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input, XVCR = USB Transceiver, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

Note 1: Alternate PMP configuration when the PMPMX Configuration bit = 0; available on 80-pin devices only.

# 12.0 TIMER0 MODULE

The Timer0 module incorporates the following features:

- Software selectable operation as a timer or counter in both 8-bit or 16-bit modes

- · Readable and writable registers

- Dedicated 8-bit, software programmable

prescaler

- Selectable clock source (internal or external)

- Edge select for external clock

- · Interrupt-on-overflow

The T0CON register (Register 12-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

A simplified block diagram of the Timer0 module in 8-bit mode is shown in Figure 12-1. Figure 12-2 shows a simplified block diagram of the Timer0 module in 16-bit mode.

### REGISTER 12-1: T0CON: TIMER0 CONTROL REGISTER

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMR00N | T08BIT | TOCS  | TOSE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |       |       |       |       | bit 0 |

| Legend:    |                      |                                       |                               |                    |

|------------|----------------------|---------------------------------------|-------------------------------|--------------------|

| R = Reada  | ble bit              | W = Writable bit                      | U = Unimplemented bit         | , read as '0'      |

| -n = Value | at POR               | '1' = Bit is set                      | '0' = Bit is cleared          | x = Bit is unknown |

|            |                      |                                       |                               |                    |

| bit 7      | TMR0ON               | I: Timer0 On/Off Control bit          |                               |                    |

|            |                      | les Timer0                            |                               |                    |

|            | 0 = Stops            |                                       |                               |                    |

| bit 6      | T08BIT: <sup>-</sup> | Timer0 8-Bit/16-Bit Control bi        | it                            |                    |

|            |                      | r0 is configured as an 8-bit ti       |                               |                    |

|            | 0 <b>= Time</b>      | r0 is configured as a 16-bit ti       | mer/counter                   |                    |

| bit 5      | TOCS: Ti             | mer0 Clock Source Select bi           | t                             |                    |

|            | 1 = Trans            | sition on T0CKI pin                   |                               |                    |

|            | 0 = Interr           | nal instruction cycle clock (Cl       | _KO)                          |                    |

| bit 4      | TOSE: Ti             | mer0 Source Edge Select bit           |                               |                    |

|            | 1 = Incre            | ment on high-to-low transitio         | n on T0CKI pin                |                    |

|            | 0 = Incre            | ment on low-to-high transitio         | n on T0CKI pin                |                    |

| bit 3      | PSA: Tim             | ner0 Prescaler Assignment b           | it                            |                    |

|            | 1 = TIme             | r0 prescaler is not assigned.         | Timer0 clock input bypasses p | orescaler.         |

|            | 0 = Time             | r0 prescaler is assigned. Tim         | er0 clock input comes from pr | escaler output.    |

| bit 2-0    | T0PS2:T              | 0PS0: Timer0 Prescaler Sele           | ect bits                      |                    |

|            | 111 <b>= 1</b> :2    | 256 Prescale value                    |                               |                    |

|            |                      | 128 Prescale value                    |                               |                    |

|            |                      | 64 Prescale value                     |                               |                    |

|            |                      | 32 Prescale value                     |                               |                    |

|            |                      | 16 Prescale value<br>B Prescale value |                               |                    |

|            |                      | 4 Prescale value                      |                               |                    |

|            |                      | 2 Prescale value                      |                               |                    |

# 15.0 TIMER3 MODULE

The Timer3 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR3H and TMR3L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Module Reset on ECCP Special Event Trigger

A simplified block diagram of the Timer3 module is shown in Figure 15-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 15-2.

The Timer3 module is controlled through the T3CON register (Register 15-1). It also selects the clock source options for the CCP and ECCP modules; see **Section 17.1.1 "CCP Modules and Timer Resources"** for more information.

### REGISTER 15-1: T3CON: TIMER3 CONTROL REGISTER

| R/W-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|--------|---------|---------|--------|--------|--------|--------|

| RD16  | T3CCP2 | T3CKPS1 | T3CKPS0 | T3CCP1 | T3SYNC | TMR3CS | TMR3ON |

| bit 7 |        |         |         |        |        |        | bit 0  |

| Legend:           |                                    |                                                                                                                                                                                                    |                                                                                                          |                                     |  |  |  |  |

|-------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|--|--|

| R = Reada         | ble bit                            | W = Writable bit                                                                                                                                                                                   | U = Unimplemented bit                                                                                    | t, read as '0'                      |  |  |  |  |

| -n = Value at POR |                                    | '1' = Bit is set                                                                                                                                                                                   | '0' = Bit is cleared                                                                                     | x = Bit is unknown                  |  |  |  |  |

|                   |                                    |                                                                                                                                                                                                    |                                                                                                          |                                     |  |  |  |  |

| bit 7             |                                    | RD16: 16-Bit Read/Write Mode Enable bit                                                                                                                                                            |                                                                                                          |                                     |  |  |  |  |

|                   |                                    | bles register read/write of Time<br>bles register read/write of Time                                                                                                                               |                                                                                                          |                                     |  |  |  |  |

| bit 6,3           | T3CCP2                             | :T3CCP1: Timer3 and Timer1                                                                                                                                                                         | I to ECCPx/CCPx Enable bits                                                                              | 3                                   |  |  |  |  |

|                   | 10 = Tim<br>Tim<br>01 = Tim<br>Tim | her3 and Timer4 are the clock<br>her3 and Timer4 are the clock<br>her1 and Timer2 are the clock<br>her3 and Timer4 are the clock<br>her1 and Timer2 are the clock<br>her1 and Timer2 are the clock | sources for ECCP3, CCP4 a<br>sources for ECCP1 and ECC<br>sources for ECCP2, ECCP3,<br>sources for ECCP1 | nd CCP5;<br>CP2<br>, CCP4 and CCP5; |  |  |  |  |

| bit 5-4           | T3CKPS                             | T3CKPS1:T3CKPS0: Timer3 Input Clock Prescale Select bits                                                                                                                                           |                                                                                                          |                                     |  |  |  |  |

|                   | 10 = 1:4<br>01 = 1:2               | Prescale value<br>Prescale value<br>Prescale value<br>Prescale value                                                                                                                               |                                                                                                          |                                     |  |  |  |  |

| bit 2             |                                    | <b>T3SYNC:</b> Timer3 External Clock Input Synchronization Control bit (Not usable if the device clock comes from Timer1/Timer3.)                                                                  |                                                                                                          |                                     |  |  |  |  |

|                   | 1 = Do n<br>0 = Sync               | <u>MR3CS = 1:</u><br>ot synchronize external clock<br>hronize external clock input                                                                                                                 | input                                                                                                    |                                     |  |  |  |  |

|                   |                                    | <u>/IR3CS = 0:</u><br>s ignored. Timer3 uses the int                                                                                                                                               | ternal clock when TMR3CS =                                                                               | 0.                                  |  |  |  |  |

| bit 1             | TMR3CS                             | : Timer3 Clock Source Selec                                                                                                                                                                        | t bit                                                                                                    |                                     |  |  |  |  |

|                   | fallir                             | ernal clock input from Timer1 (<br>ng edge)<br>mal clock (Fosc/4)                                                                                                                                  | oscillator or T13CKI (on the ri                                                                          | sing edge after the first           |  |  |  |  |

| bit 0             |                                    | I: Timer3 On bit                                                                                                                                                                                   |                                                                                                          |                                     |  |  |  |  |

|                   |                                    | oles Timer3                                                                                                                                                                                        |                                                                                                          |                                     |  |  |  |  |

# 19.3.2 OPERATION

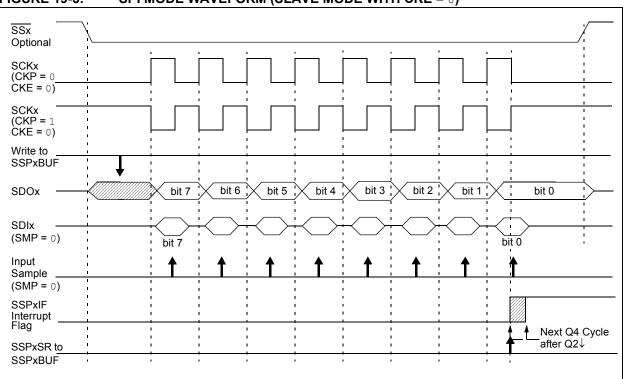

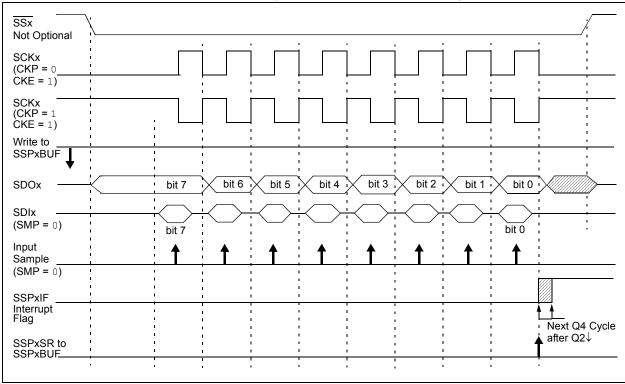

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPxCON1<5:0> and SSPxSTAT<7:6>). These control bits allow the following to be specified:

- · Master mode (SCKx is the clock output)

- Slave mode (SCKx is the clock input)

- Clock Polarity (Idle state of SCKx)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCKx)

- Clock Rate (Master mode only)

- Slave Select mode (Slave mode only)

Each MSSP module consists of a transmit/receive shift register (SSPxSR) and a buffer register (SSPxBUF). The SSPxSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPxSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full detect bit, BF (SSPxSTAT<0>) and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received. Any write to the SSPxBUF register during transmission/reception of data will be ignored and the Write Collision Detect bit, WCOL (SSPxCON1<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPxBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPxBUF should be read before the next byte of data to transfer is written to the SSPxBUF. The

Buffer Full bit, BF (SSPxSTAT<0>), indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 19-1 shows the loading of the SSPxBUF (SSPxSR) for data transmission.

The SSPxSR is not directly readable or writable and can only be accessed by addressing the SSPxBUF register. Additionally, the SSPxSTAT register indicates the various status conditions.

# 19.3.3 OPEN-DRAIN OUTPUT OPTION

The drivers for the SDOx output and SCKx clock pins can be optionally configured as open-drain outputs. This feature allows the voltage level on the pin to be pulled to a higher level through an external pull-up resistor, and allows the output to communicate with external circuits without the need for additional level shifters. For more information, see **Section 10.1.4 "Open-Drain Outputs"**.

The open-drain output option is controlled by the SPI2OD and SPI1OD bits (ODCON3<1:0>. Setting an SPIxOD bit configures both SDO and SCK pins for the corresponding open-drain operation.

The ODCON3 register shares the same address as the T1CON register. The ODCON3 register is accessed by setting the ADSHR bit in the WDTCON register (WDTCON<4>).

| LOOP | BTFSS<br>BRA<br>MOVF | LOOP                 | ;Has data been received (transmit complete)?<br>;No<br>;WREG reg = contents of SSP1BUF |

|------|----------------------|----------------------|----------------------------------------------------------------------------------------|

|      | MOVWF                | RXDATA               | ;Save in user RAM, if data is meaningful                                               |

|      | MOVF<br>MOVWF        | TXDATA, W<br>SSP1BUF | ;W reg = contents of TXDATA<br>;New data to xmit                                       |

EXAMPLE 19-1: LOADING THE SSP1BUF (SSP1SR) REGISTER

### FIGURE 19-5: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0)

### FIGURE 19-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

#### **REGISTER 19-4:** SSPxCON1: MSSPx CONTROL REGISTER 1 (I<sup>2</sup>C<sup>™</sup> MODE) R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 WCOL SSPEN<sup>(1)</sup> SSPM3<sup>(2)</sup> SSPM2<sup>(2)</sup> SSPM1<sup>(2)</sup> SSPM0<sup>(2)</sup> SSPOV CKP bit 7 bit 0 Legend: R = Readable bit U = Unimplemented bit, read as '0' W = Writable bit -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 7 WCOL: Write Collision Detect bit In Master Transmit mode: 1 = A write to the SSPxBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started (must be cleared in software) 0 = No collisionIn Slave Transmit mode: 1 = The SSPxBUF register is written while it is still transmitting the previous word (must be cleared in software) 0 = No collision In Receive mode (Master or Slave modes): This is a "don't care" bit. SSPOV: Receive Overflow Indicator bit bit 6 In Receive mode: 1 = A byte is received while the SSPxBUF register is still holding the previous byte (must be cleared in software) 0 = No overflow In Transmit mode: This is a "don't care" bit in Transmit mode. bit 5 SSPEN: Master Synchronous Serial Port Enable bit<sup>(1)</sup> 1 = Enables the serial port and configures the SDAx and SCLx pins as the serial port pins 0 = Disables serial port and configures these pins as I/O port pins CKP: SCKx Release Control bit bit 4 In Slave mode: 1 = Releases clock 0 = Holds clock low (clock stretch), used to ensure data setup time In Master mode: Unused in this mode. bit 3-0 SSPM3:SSPM0: Master Synchronous Serial Port Mode Select bits<sup>(2)</sup> 1111 = $I^2C$ Slave mode, 10-bit address with Start and Stop bit interrupts enabled $1110 = I^2C$ Slave mode, 7-bit address with Start and Stop bit interrupts enabled $1011 = I^2C$ Firmware Controlled Master mode (Slave Idle) 1001 = Load SSPMSK register at SSPADD SFR address<sup>(3,4)</sup> $1000 = I^2C$ Master mode, clock = Fosc/(4 \* (SSPxADD + 1)) $0111 = I^2C$ Slave mode, 10-bit address $0110 = I^2C$ Slave mode, 7-bit address **Note 1:** When enabled, the SDAx and SCLx pins must be configured as inputs. 2: Bit combinations not specifically listed here are either reserved or implemented in SPI mode only. 3: When SSPM3:SSPM0 = 1001, any reads or writes to the SSPxADD SFR address actually accesses the SSPMSK register.

**4:** This mode is only available when 7-bit Address Masking mode is selected (MSSPMSK Configuration bit is '1').

### 22.2.5 USB ADDRESS REGISTER (UADDR)

The USB Address register contains the unique USB address that the peripheral will decode when active. UADDR is reset to 00h when a USB Reset is received, indicated by URSTIF, or when a Reset is received from the microcontroller. The USB address must be written by the microcontroller during the USB setup phase (enumeration) as part of the Microchip USB firmware support.

### 22.2.6 USB FRAME NUMBER REGISTERS (UFRMH:UFRML)

The Frame Number registers contain the 11-bit frame number. The low-order byte is contained in UFRML, while the three high-order bits are contained in UFRMH. The register pair is updated with the current frame number whenever a SOF token is received. For the microcontroller, these registers are read-only. The Frame Number registers are primarily used for isochronous transfers. The contents of the UFRMH and UFRML registers are only valid when the 48 MHz SIE clock is active (i.e., contents are inaccurate when SUSPND (UCON<1>) bit = 1).

# 22.3 USB RAM

USB data moves between the microcontroller core and the SIE through a memory space known as the USB RAM. This is a special dual access memory that is mapped into the normal data memory space in Banks 0 through 15 (60h to F3Fh) for a total of 3.9 Kbyte (Figure 22-4).

Bank 4 (400h through 4FFh) is used specifically for endpoint buffer control, while Banks 0 through Bank3 and Banks 5 through Bank15 are available for USB data. Depending on the type of buffering being used, all but 8 bytes of Bank 4 may also be available for use as USB buffer space.