Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 49                                                                          |

| Program Memory Size        | 96KB (48K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f66j55t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC18F87J50 FAMILY

|             | MSSP                            |                                | P   | F                  | ors                   |   | Bus | ٩                           |        |             |                    |            |         |

|-------------|---------------------------------|--------------------------------|-----|--------------------|-----------------------|---|-----|-----------------------------|--------|-------------|--------------------|------------|---------|

| Device      | Flash Program<br>Memory (bytes) | SRAM Data<br>Memory<br>(bytes) | I/O | 10-Bit<br>A/D (ch) | CCP/<br>ECCP<br>(PWM) |   | SPI | Master<br>I <sup>2</sup> C™ | EUSART | Comparators | Timers<br>8/16-Bit | External E | dSd/dWd |

| PIC18F65J50 | 32K                             | 3904*                          | 49  | 8                  | 2/3                   | 2 | Y   | Y                           | 2      | 2           | 2/3                | Ν          | Y       |

| PIC18F66J50 | 64K                             | 3904*                          | 49  | 8                  | 2/3                   | 2 | Y   | Y                           | 2      | 2           | 2/3                | Ν          | Y       |

| PIC18F66J55 | 96K                             | 3904*                          | 49  | 8                  | 2/3                   | 2 | Y   | Y                           | 2      | 2           | 2/3                | Ν          | Y       |

| PIC18F67J50 | 128K                            | 3904*                          | 49  | 8                  | 2/3                   | 2 | Y   | Y                           | 2      | 2           | 2/3                | Ν          | Y       |

| PIC18F85J50 | 32K                             | 3904*                          | 65  | 12                 | 2/3                   | 2 | Y   | Y                           | 2      | 2           | 2/3                | Y          | Y       |

| PIC18F86J50 | 64K                             | 3904*                          | 65  | 12                 | 2/3                   | 2 | Y   | Y                           | 2      | 2           | 2/3                | Y          | Y       |

| PIC18F86J55 | 96K                             | 3904*                          | 65  | 12                 | 2/3                   | 2 | Y   | Y                           | 2      | 2           | 2/3                | Y          | Y       |

| PIC18F87J50 | 128K                            | 3904*                          | 65  | 12                 | 2/3                   | 2 | Y   | Y                           | 2      | 2           | 2/3                | Y          | Y       |

\* Includes the dual access RAM used by the USB module which is shared with data memory.

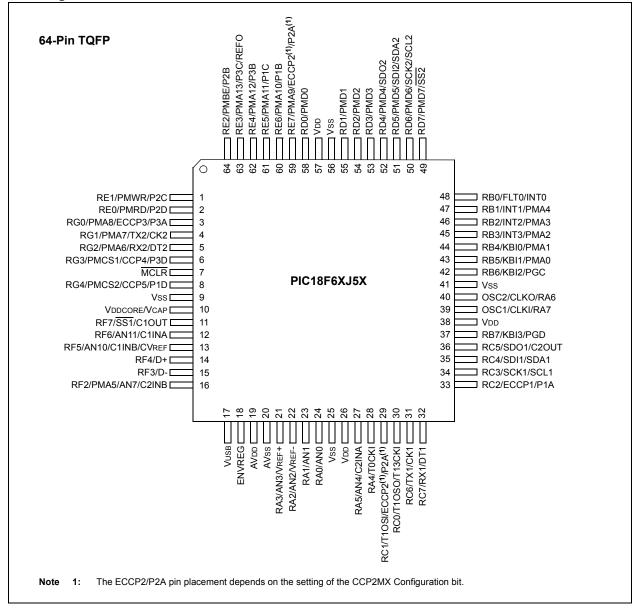

#### **Pin Diagrams**

| Dis No.           | Pin Number           | Pin      | Buffer   | Description                            |  |  |  |  |

|-------------------|----------------------|----------|----------|----------------------------------------|--|--|--|--|

| Pin Name          | 64-TQFP              | Туре     | Туре     | Description                            |  |  |  |  |

|                   |                      |          |          | PORTA is a bidirectional I/O port.     |  |  |  |  |

| RA0/AN0           | 24                   |          |          |                                        |  |  |  |  |

| RA0               |                      | I/O      | TTL      | Digital I/O.                           |  |  |  |  |

| AN0               |                      | I        | Analog   | Analog input 0.                        |  |  |  |  |

| RA1/AN1           | 23                   |          |          |                                        |  |  |  |  |

| RA1               |                      | I/O      | TTL      | Digital I/O.                           |  |  |  |  |

| AN1               |                      | I        | Analog   | Analog input 1.                        |  |  |  |  |

| RA2/AN2/VREF-     | 22                   |          |          |                                        |  |  |  |  |

| RA2               |                      | I/O      | TTL      | Digital I/O.                           |  |  |  |  |

| AN2               |                      | I        | Analog   | Analog input 2.                        |  |  |  |  |

| VREF-             |                      | I        | Analog   | A/D reference voltage (low) input.     |  |  |  |  |

| RA3/AN3/VREF+     | 21                   |          |          |                                        |  |  |  |  |

| RA3               |                      | I/O      | TTL      | Digital I/O.                           |  |  |  |  |

| AN3               |                      | I.       | Analog   | Analog input 3.                        |  |  |  |  |

| VREF+             |                      | I        | Analog   | A/D reference voltage (high) input.    |  |  |  |  |

| RA4/T0CKI         | 28                   |          |          |                                        |  |  |  |  |

| RA4               |                      | I/O      | ST       | Digital I/O.                           |  |  |  |  |

| TOCKI             |                      | I        | ST       | Timer0 external clock input.           |  |  |  |  |

| RA5/AN4/C2INA     | 27                   |          |          |                                        |  |  |  |  |

| RA5               |                      | I/O      | TTL      | Digital I/O.                           |  |  |  |  |

| AN4               |                      | I        | Analog   | Analog input 4.                        |  |  |  |  |

| C2INA             |                      |          | Analog   | Comparator 2 input A                   |  |  |  |  |

| RA6               | —                    | —        | -        | See the OSC2/CLKO/RA6 pin.             |  |  |  |  |

| RA7               | _                    | _        | _        | See the OSC1/CLKI/RA7 pin.             |  |  |  |  |

| Legend: TTL = TTL | compatible input     |          |          | CMOS = CMOS compatible input or output |  |  |  |  |

| ST = Sch          | mitt Trigger input w | vith CMC | S levels | Analog = Analog input                  |  |  |  |  |

| l = Inpu          |                      |          |          | O = Output                             |  |  |  |  |

| P = Pow           | -                    |          |          | OD = Open-Drain (no P diode to VDD)    |  |  |  |  |

| TABLE 1-3: PIC18F6XJ5X PINOUT I/O DESCRIPT | IONS (CONTINUED) |

|--------------------------------------------|------------------|

|--------------------------------------------|------------------|

Note 1: Default assignment for ECCP2/P2A when CCP2MX Configuration bit is set.

2: Alternate assignment for ECCP2/P2A when CCP2MX Configuration bit is cleared.

3: RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

| File Name | Bit 7         | Bit 6                            | Bit 5                 | Bit 4         | Bit 3          | Bit 2          | Bit 1           | Bit 0          | Value on<br>POR, BOR | Details<br>on<br>Page: |

|-----------|---------------|----------------------------------|-----------------------|---------------|----------------|----------------|-----------------|----------------|----------------------|------------------------|

| TOSU      | _             | _                                | _                     | Top-of-Stack  | Upper Byte (   | TOS<20:16>)    |                 |                | 0 0000               | 61, 73                 |

| TOSH      | Top-of-Stack  | High Byte (TC                    | )S<15:8>)             |               |                |                |                 |                | 0000 0000            | 61, 73                 |

| TOSL      | Top-of-Stack  | Low Byte (TO                     | S<7:0>)               |               |                |                |                 |                | 0000 0000            | 61, 73                 |

| STKPTR    | STKFUL        | STKUNF                           | —                     | SP4           | SP3            | SP2            | SP1             | SP0            | 00-0 0000            | 61, 74                 |

| PCLATU    | _             | _                                | bit 21 <sup>(1)</sup> | Holding Reg   | ister for PC<2 | 0:16>          |                 |                | 0 0000               | 61, 73                 |

| PCLATH    | Holding Regi  | ster for PC<15                   | 5:8>                  |               |                |                |                 |                | 0000 0000            | 61, 73                 |

| PCL       | PC Low Byte   | (PC<7:0>)                        |                       |               |                |                |                 |                | 0000 0000            | 61, 73                 |

| TBLPTRU   | —             | —                                | bit 21                | Program Me    | mory Table Po  | ointer Upper B | yte (TBLPTR∢    | <20:16>)       | 00 0000              | 61, 106                |

| TBLPTRH   | Program Mer   | mory Table Po                    | inter High Byt        | e (TBLPTR<1   | 5:8>)          |                |                 |                | 0000 0000            | 61, 106                |

| TBLPTRL   | Program Mer   | mory Table Po                    | inter Low Byte        | e (TBLPTR<7   | :0>)           |                |                 |                | 0000 0000            | 61, 106                |

| TABLAT    | Program Mer   | mory Table Lat                   | ch                    |               |                |                |                 |                | 0000 0000            | 61, 106                |

| PRODH     | Product Reg   | ister High Byte                  | •                     |               |                |                |                 |                | XXXX XXXX            | 61, 119                |

| PRODL     | Product Reg   | ister Low Byte                   |                       |               |                |                |                 |                | XXXX XXXX            | 61, 119                |

| INTCON    | GIE/GIEH      | PEIE/GIEL                        | TMR0IE                | INT0IE        | RBIE           | TMR0IF         | INT0IF          | RBIF           | 0000 000x            | 61, 123                |

| INTCON2   | RBPU          | INTEDG0                          | INTEDG1               | INTEDG2       | INTEDG3        | TMR0IP         | INT3IP          | RBIP           | 1111 1111            | 61, 123                |

| INTCON3   | INT2IP        | INT1IP                           | INT3IE                | INT2IE        | INT1IE         | INT3IF         | INT2IF          | INT1IF         | 1100 0000            | 61, 123                |

| INDF0     | Uses content  | ts of FSR0 to a                  | address data i        | memory – valu | ue of FSR0 no  | t changed (no  | t a physical re | gister)        | N/A                  | 61, 91                 |

| POSTINC0  | Uses content  | ts of FSR0 to a                  | address data i        | memory – valu | ue of FSR0 po  | st-incremente  | d (not a physi  | cal register)  | N/A                  | 61, 92                 |

| POSTDEC0  | Uses content  | ts of FSR0 to a                  | address data i        | memory – valu | ue of FSR0 po  | st-decremente  | ed (not a phys  | ical register) | N/A                  | 61, 92                 |

| PREINC0   | Uses content  | ts of FSR0 to a                  | address data i        | memory – valu | ue of FSR0 pre | e-incremented  | (not a physic   | al register)   | N/A                  | 61, 92                 |

| PLUSW0    |               | ts of FSR0 to a<br>0 offset by W | address data i        | memory – valu | ue of FSR0 pre | e-incremented  | (not a physic   | al register) – | N/A                  | 61, 92                 |

| FSR0H     | _             | _                                | _                     | _             | Indirect Data  | Memory Add     | ress Pointer 0  | High Byte      | xxxx                 | 61, 91                 |

| FSR0L     | Indirect Data | Memory Addr                      | ess Pointer 0         | Low Byte      |                |                |                 |                | XXXX XXXX            | 61, 91                 |

| WREG      | Working Reg   | ister                            |                       |               |                |                |                 |                | XXXX XXXX            | 61, 75                 |

| INDF1     | Uses content  | ts of FSR1 to a                  | address data i        | memory – valu | ue of FSR1 no  | t changed (no  | t a physical re | egister)       | N/A                  | 61, 91                 |

| POSTINC1  | Uses content  | ts of FSR1 to a                  | address data i        | memory – valu | ue of FSR1 po  | st-incremente  | d (not a physi  | cal register)  | N/A                  | 61, 92                 |

| POSTDEC1  | Uses content  | ts of FSR1 to a                  | address data i        | memory – valu | ue of FSR1 po  | st-decremente  | ed (not a phys  | ical register) | N/A                  | 61, 92                 |

| PREINC1   | Uses content  | ts of FSR1 to a                  | address data i        | memory – valu | ue of FSR1 pre | e-incremented  | (not a physic   | al register)   | N/A                  | 61, 92                 |

| PLUSW1    |               | ts of FSR1 to a<br>1 offset by W | address data i        | memory – valu | ue of FSR1 pre | e-incremented  | (not a physic   | al register) – | N/A                  | 61, 92                 |

| FSR1H     | _             | _                                | _                     | _             | Indirect Data  | Memory Add     | ress Pointer 1  | High Byte      | xxxx                 | 61, 91                 |

| FSR1L     | Indirect Data | Memory Addr                      | ess Pointer 1         | Low Byte      |                |                |                 |                | XXXX XXXX            | 61, 91                 |

| BSR       | _             | _                                | _                     | _             | Bank Select    | Register       |                 |                | 0000                 | 61, 78                 |

| INDF2     | Uses content  | ts of FSR2 to a                  | address data i        | memory – valu | ue of FSR2 no  | t changed (no  | t a physical re | egister)       | N/A                  | 62, 91                 |

| POSTINC2  | Uses content  | ts of FSR2 to a                  | address data i        | memory – valu | ue of FSR2 po  | st-incremente  | d (not a physi  | cal register)  | N/A                  | 62, 92                 |

| POSTDEC2  | Uses content  | ts of FSR2 to a                  | address data i        | memory - valu | ue of FSR2 po  | st-decremente  | ed (not a phys  | ical register) | N/A                  | 62, 92                 |

| PREINC2   | Uses content  | ts of FSR2 to a                  | address data i        | memory – valu | ue of FSR2 pre | e-incremented  | (not a physic   | al register)   | N/A                  | 62, 92                 |

| PLUSW2    |               | ts of FSR2 to a<br>2 offset by W | address data i        | memory – valu | ue of FSR2 pro | e-incremented  | (not a physic   | al register) – | N/A                  | 62, 92                 |

| FSR2H     | _             | _                                | _                     | _             | Indirect Data  | Memory Add     | ress Pointer 2  | High Byte      | xxxx                 | 62, 91                 |

| IADLE 3-3. REGISTER FILE SUIVIVIART (FICTORO/JSU FAIVILT | TABLE 5-5: | REGISTER FILE SUMMARY (PIC18F87J50 FAMILY) |

|----------------------------------------------------------|------------|--------------------------------------------|

|----------------------------------------------------------|------------|--------------------------------------------|

Legend: Note 1

d: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition. Bold indicates shared-access SFRs.

Bit 21 of the PC is only available in Serial Programming modes.

**2:** Default (legacy) SFR at this address, available when WDTCON<4> = 0.

3: Configuration SFR, overlaps with default SFR at this address; available only when WDTCON<4> = 1.

**4:** Reset value is '0' when Two-Speed Start-up is enabled and '1' if disabled.

5: The SSPxMSK registers are only accessible when SSPxCON2<3:0> = 1001.

6: Alternate names and definitions for these bits when the MSSP module is operating in I<sup>2</sup>C™ Slave mode. See Section 19.4.3.2 "Address Masking Modes" for details

7: These bits and/or registers are only available in 80-pin devices; otherwise, they are unimplemented and read as '0'. Reset values are shown for 80-pin devices.

8: The PMADDRH/PMDOUT1H and PMADDRL/PMDOUT1L register pairs share the physical registers and addresses, but have different functions determined by the module's operating mode. See Section 11.1.2 "Data Registers" for more information.

| File Name | Bit 7        | Bit 6                                   | Bit 5           | Bit 4            | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Details<br>on<br>Page: |  |

|-----------|--------------|-----------------------------------------|-----------------|------------------|---------|---------|---------|---------|----------------------|------------------------|--|

| ECCP1AS   | ECCP1ASE     | ECCP1AS2                                | ECCP1AS1        | ECCP1AS0         | PSS1AC1 | PSS1AC0 | PSS1BD1 | PSS1BD0 | 0000 0000            | 63, 232                |  |

| ECCP1DEL  | P1RSEN       | P1DC6                                   | P1DC5           | P1DC4            | P1DC3   | P1DC2   | P1DC1   | P1DC0   | 0000 0000            | 63, 232                |  |

| CCPR1H    | Capture/Corr | apture/Compare/PWM Register 1 HIgh Byte |                 |                  |         |         |         |         |                      |                        |  |

| CCPR1L    | Capture/Corr | apture/Compare/PWM Register 1 Low Byte  |                 |                  |         |         |         |         |                      |                        |  |

| CCP1CON   | P1M1         | P1M0                                    | DC1B1           | DC1B0            | CCP1M3  | CCP1M2  | CCP1M1  | CCP1M0  | 0000 0000            | 63, 232                |  |

| ECCP2AS   | ECCP2ASE     | ECCP2AS2                                | ECCP2AS1        | ECCP2AS0         | PSS2AC1 | PSS2AC0 | PSS2BD1 | PSS2BD0 | 0000 0000            | 63, 232                |  |

| ECCP2DEL  | P2RSEN       | P2DC6                                   | P2DC5           | P2DC4            | P2DC3   | P2DC2   | P2DC1   | P2DC0   | 0000 0000            | 63, 232                |  |

| CCPR2H    | Capture/Corr | pare/PWM Re                             | egister 2 High  | Byte             |         |         |         |         | XXXX XXXX            | 63, 232                |  |

| CCPR2L    | Capture/Corr | pare/PWM Re                             | egister 2 Low   | Byte             |         |         |         |         | XXXX XXXX            | 63, 232                |  |

| CCP2CON   | P2M1         | P2M0                                    | DC2B1           | DC2B0            | CCP2M3  | CCP2M2  | CCP2M1  | CCP2M0  | 0000 0000            | 63, 232                |  |

| ECCP3AS   | ECCP3ASE     | ECCP3AS2                                | ECCP3AS1        | ECCP3AS0         | PSS3AC1 | PSS3AC0 | PSS3BD1 | PSS3BD0 | 0000 0000            | 63, 232                |  |

| ECCP3DEL  | P3RSEN       | P3DC6                                   | P3DC5           | P3DC4            | P3DC3   | P3DC2   | P3DC1   | P3DC0   | 0000 0000            | 63, 232                |  |

| CCPR3H    | Capture/Corr | pare/PWM Re                             | egister 3 High  | Byte             | •       | •       | •       | •       | XXXX XXXX            | 63, 232                |  |

| CCPR3L    | Capture/Corr | pare/PWM Re                             | egister 3 Low   | Byte             |         |         |         |         | XXXX XXXX            | 63, 232                |  |

| CCP3CON   | P3M1         | P3M0                                    | DC3B1           | DC3B0            | CCP3M3  | CCP3M2  | CCP3M1  | CCP3M0  | 0000 0000            | 63, 232                |  |

| SPBRG1    | EUSART1 Ba   | aud Rate Gen                            | erator Registe  | r Low Byte       | •       | •       | •       | •       | 0000 0000            | 63, 283                |  |

| RCREG1    | EUSART1 R    | EUSART1 Receive Register                |                 |                  |         |         |         |         |                      |                        |  |

| TXREG1    | EUSART1 Tr   | ansmit Regist                           | er              |                  |         |         |         |         | XXXX XXXX            | 63, 289,<br>290        |  |

| TXSTA1    | CSRC         | TX9                                     | TXEN            | SYNC             | SENDB   | BRGH    | TRMT    | TX9D    | 0000 0010            | 63, 289                |  |

| RCSTA1    | SPEN         | RX9                                     | SREN            | CREN             | ADDEN   | FERR    | OERR    | RX9D    | 0000 000x            | 63, 291                |  |

| SPBRG2    | EUSART2 Ba   | aud Rate Gen                            | erator Registe  | er Low Byte      |         |         |         |         | 0000 0000            | 63, 283                |  |

| RCREG2    | EUSART2 R    | eceive Registe                          | er              |                  |         |         |         |         | 0000 0000            | 63, 291,<br>292        |  |

| TXREG2    | EUSART2 Tr   | ansmit Regist                           | er              |                  |         |         |         |         | 0000 0000            | 63, 289,<br>290        |  |

| TXSTA2    | CSRC         | TX9                                     | TXEN            | SYNC             | SENDB   | BRGH    | TRMT    | TX9D    | 0000 0010            | 63, 289                |  |

| EECON2    | Program Mer  | mory Control F                          | Register 2 (not | t a physical reg | gister) |         |         |         |                      | 63, 98                 |  |

| EECON1    | _            | _                                       | WPROG           | FREE             | WRERR   | WREN    | WR      |         | 00 x00-              | 63, 98                 |  |

| IPR3      | SSP2IP       | BCL2IP                                  | RC2IP           | TX2IP            | TMR4IP  | CCP5IP  | CCP4IP  | CCP3IP  | 1111 1111            | 64, 132                |  |

| PIR3      | SSP2IF       | BCL2IF                                  | RC2IF           | TX2IF            | TMR4IF  | CCP5IF  | CCP4IF  | CCP3IF  | 0000 0000            | 64, 126                |  |

| PIE3      | SSP2IE       | BCL2IE                                  | RC2IE           | TX2IE            | TMR4IE  | CCP5IE  | CCP4IE  | CCP3IE  | 0000 0000            | 64, 129                |  |

| IPR2      | OSCFIP       | CM2IP                                   | CM1IP           | USBIP            | BCL1IP  | LVDIP   | TMR3IP  | CCP2IP  | 1111 1111            | 64, 132                |  |

| PIR2      | OSCFIF       | CM2IF                                   | CM1IF           | USBIF            | BCL1IF  | LVDIF   | TMR3IF  | CCP2IF  | 0000 0000            | 64, 126                |  |

| PIE2      | OSCFIE       | CM2IE                                   | CM1IE           | USBIE            | BCL1IE  | LVDIE   | TMR3IE  | CCP2IE  | 0000 0000            | 64, 129                |  |

| IPR1      | PMPIP        | ADIP                                    | RC1IP           | TX1IP            | SSP1IP  | CCP1IP  | TMR2IP  | TMR1IP  | 1111 1111            | 64, 132                |  |

| PIR1      | PMPIF        | ADIF                                    | RC1IF           | TX1IF            | SSP1IF  | CCP1IF  | TMR2IF  | TMR1IF  | 0000 0000            | 64, 126                |  |

| PIE1      | PMPIE        | ADIE                                    | RC1IE           | TX1IE            | SSP1IE  | CCP1IE  | TMR2IE  | TMR1IE  | 0000 0000            | 64, 129                |  |

| 1 1 - 1   |              |                                         |                 |                  |         | 1       | -       |         |                      |                        |  |

| RCSTA2    | SPEN         | RX9                                     | SREN            | CREN             | ADDEN   | FERR    | OERR    | RX9D    | 0000 000x            | 64, 291                |  |

#### TABLE 5-5: REGISTER FILE SUMMARY (PIC18F87J50 FAMILY) (CONTINUED)

Legend:

nd: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition. Bold indicates shared-access SFRs.

**Note** 1: Bit 21 of the PC is only available in Serial Programming modes.

**2:** Default (legacy) SFR at this address, available when WDTCON<4> = 0.

3: Configuration SFR, overlaps with default SFR at this address; available only when WDTCON<4> = 1.

**4:** Reset value is '0' when Two-Speed Start-up is enabled and '1' if disabled.

5: The SSPxMSK registers are only accessible when SSPxCON2<3:0> = 1001.

6: Alternate names and definitions for these bits when the MSSP module is operating in I<sup>2</sup>C™ Slave mode. See Section 19.4.3.2 "Address Masking Modes" for details

7: These bits and/or registers are only available in 80-pin devices; otherwise, they are unimplemented and read as '0'. Reset values are shown for 80-pin devices.

8: The PMADDRH/PMDOUT1H and PMADDRL/PMDOUT1L register pairs share the physical registers and addresses, but have different functions determined by the module's operating mode. See Section 11.1.2 "Data Registers" for more information.

#### 5.3.6 STATUS REGISTER

The STATUS register, shown in Register 5-4, contains the arithmetic status of the ALU. The STATUS register can be the operand for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC, C, OV or N bits, then the write to these five bits is disabled.

These bits are set or cleared according to the device logic. Therefore, the result of an instruction with the STATUS register as destination may be different than intended. For example, CLRF STATUS will set the Z bit but leave the other bits unchanged. The STATUS

register then reads back as '000u u1uu'. It is recommended, therefore, that only BCF, BSF, SWAPF, MOVFF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C, DC, OV or N bits in the STATUS register.

For other instructions not affecting any Status bits, see the instruction set summaries in Table 26-2 and Table 26-3.

Note: The C and DC bits operate as a borrow and digit borrow bit respectively, in subtraction.

#### REGISTER 5-4: STATUS REGISTER

| U-0       | U-0         | U-0                                                                                                                                                         | R/W-x          | R/W-x              | R/W-x           | R/W-x              | R/W-x            |  |  |  |  |

|-----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------|-----------------|--------------------|------------------|--|--|--|--|

| _         | —           | —                                                                                                                                                           | Ν              | OV                 | Z               | DC <sup>(1)</sup>  | C <sup>(2)</sup> |  |  |  |  |

| bit 7     |             |                                                                                                                                                             |                |                    |                 |                    | bit (            |  |  |  |  |

| Legend:   |             |                                                                                                                                                             |                |                    |                 |                    |                  |  |  |  |  |

| R = Read  |             | W = Writable I                                                                                                                                              | oit            | U = Unimplem       | nented bit, rea | ad as '0'          |                  |  |  |  |  |

| -n = Valu | e at POR    | '1' = Bit is set                                                                                                                                            |                | '0' = Bit is clea  | ared            | x = Bit is unkn    | iown             |  |  |  |  |

| bit 7-5   | Unimplem    | ented: Read as '0                                                                                                                                           | )'             |                    |                 |                    |                  |  |  |  |  |

| bit 4     | N: Negative | e bit                                                                                                                                                       |                |                    |                 |                    |                  |  |  |  |  |

|           |             | used for signed ari<br>LU MSB = 1).                                                                                                                         | thmetic (2's c | omplement). It i   | ndicates whe    | ther the result wa | as               |  |  |  |  |

|           |             | was negative<br>was positive                                                                                                                                |                |                    |                 |                    |                  |  |  |  |  |

| bit 3     | OV: Overflo | OV: Overflow bit                                                                                                                                            |                |                    |                 |                    |                  |  |  |  |  |

|           |             | This bit is used for signed arithmetic (2's complement). It indicates an overflow of the 7-bit magnitude which causes the sign bit (bit 7) to change state. |                |                    |                 |                    |                  |  |  |  |  |

|           |             | w occurred for sig                                                                                                                                          | ned arithmeti  | c (in this arithme | etic operation  | )                  |                  |  |  |  |  |

| bit 2     | Z: Zero bit | Z: Zero bit                                                                                                                                                 |                |                    |                 |                    |                  |  |  |  |  |

|           |             | sult of an arithmet<br>sult of an arithmet                                                                                                                  |                |                    | 0               |                    |                  |  |  |  |  |

| bit 1     |             | arry/ <del>borrow</del> bit <sup>(1)</sup><br>, ADDLW, SUBL                                                                                                 | w and SUBWF    | instructions:      |                 |                    |                  |  |  |  |  |

|           |             | -out from the 4th I<br>y-out from the 4th                                                                                                                   |                |                    | urred           |                    |                  |  |  |  |  |

| bit 0     | C: Carry/bo | prrow bit <sup>(2)</sup>                                                                                                                                    |                |                    |                 |                    |                  |  |  |  |  |

|           |             | , ADDLW, SUBL                                                                                                                                               |                |                    |                 |                    |                  |  |  |  |  |

|           |             | -out from the Mos<br>y-out from the Mo                                                                                                                      | U U            |                    |                 |                    |                  |  |  |  |  |

| Note 1:   |             | polarity is reverse<br>otate (RRF, RLF)                                                                                                                     |                |                    |                 | •                  |                  |  |  |  |  |

| 2:        |             | polarity is reverse<br>otate (RRF, RLF)                                                                                                                     |                |                    |                 |                    |                  |  |  |  |  |

#### REGISTER 6-1: EECON1: EEPROM CONTROL REGISTER 1

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-x                | R/W-0 | R/S-0 | U-0   |

|-------|-----|-------|-------|----------------------|-------|-------|-------|

| —     | —   | WPROG | FREE  | WRERR <sup>(1)</sup> | WREN  | WR    | —     |

| bit 7 |     |       |       |                      |       |       | bit 0 |

| Legend:           | S = Settable only bit (can | S = Settable only bit (cannot be cleared in software) |                    |  |  |  |  |

|-------------------|----------------------------|-------------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bi                                  | t, read as '0'     |  |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared                                  | x = Bit is unknown |  |  |  |  |

| bit 7-6 | 6 Unimplemented: Read as '0'                                                                                                                                                                                                                                                      |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | WPROG: One Word-Wide Program bit                                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = Program 2 bytes on the next WR command</li> <li>0 = Program 64 bytes on the next WR command</li> </ul>                                                                                                                                                               |

| bit 4   | FREE: Flash Row Erase Enable bit                                                                                                                                                                                                                                                  |

|         | <ul> <li>1 = Erase the program memory row addressed by TBLPTR on the next WR command<br/>(cleared by completion of erase operation)</li> <li>0 = Perform write only</li> </ul>                                                                                                    |

| bit 3   | WRERR: Flash Program Error Flag bit <sup>(1)</sup>                                                                                                                                                                                                                                |

|         | <ul> <li>1 = A write operation is prematurely terminated (any Reset during self-timed programming in normal operation, or an improper write attempt)</li> <li>0 = The write operation completed</li> </ul>                                                                        |

| bit 2   | WREN: Flash Program Write Enable bit                                                                                                                                                                                                                                              |

|         | <ul> <li>1 = Allows write cycles to Flash program memory</li> <li>0 = Inhibits write cycles to Flash program memory</li> </ul>                                                                                                                                                    |

| bit 1   | WR: Write Control bit                                                                                                                                                                                                                                                             |

|         | <ul> <li>1 = Initiates a program memory erase cycle or write cycle         (The operation is self-timed and the bit is cleared by hardware once write is complete.         The WR bit can only be set (not cleared) in software.)</li> <li>0 = Write cycle is complete</li> </ul> |

| bit 0   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                        |

| Nata    | 4. When a WOEDD second the EEDOD and OEOO bits are not closed. This allows to size of the second                                                                                                                                                                                  |

**Note 1:** When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error condition.

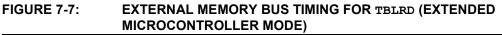

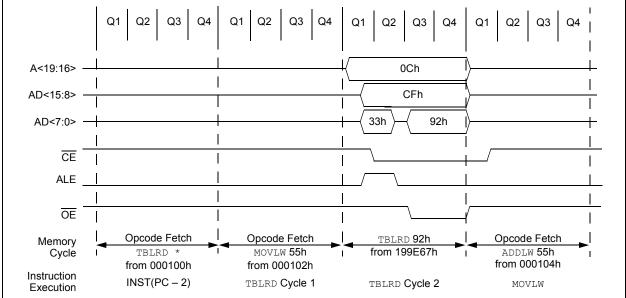

#### 7.7.1 8-BIT MODE TIMING

The presentation of control signals on the External Memory Bus is different for the various operating modes. Typical signal timing diagrams are shown in Figure 7-7 and Figure 7-8.

### FIGURE 7-8: EXTERNAL MEMORY BUS TIMING FOR SLEEP (EXTENDED MICROCONTROLLER MODE)

## PIC18F87J50 FAMILY

#### REGISTER 11-4: PMMODEL: PARALLEL PORT MODE REGISTER LOW BYTE

| R/W-0                   | R/W-0                                                                                                                                                                                                                                                                                                          | R/W-0            | R/W-0        | R/W-0             | R/W-0                        | R/W-0                 | R/W-0                 |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|-------------------|------------------------------|-----------------------|-----------------------|--|--|--|

| WAITB1 <sup>(1)</sup>   | WAITB0 <sup>(1)</sup>                                                                                                                                                                                                                                                                                          | WAITM3           | WAITM2       | WAITM1            | WAITM0                       | WAITE1 <sup>(1)</sup> | WAITE0 <sup>(1)</sup> |  |  |  |

| bit 7                   |                                                                                                                                                                                                                                                                                                                |                  |              | ·                 |                              |                       | bit 0                 |  |  |  |

| Logond:                 |                                                                                                                                                                                                                                                                                                                |                  |              |                   |                              |                       |                       |  |  |  |

| Legend:<br>R = Readable | hit                                                                                                                                                                                                                                                                                                            | W = Writable     | hit          | II – Unimplon     | nented bit, read             | d ac '0'              |                       |  |  |  |

|                         |                                                                                                                                                                                                                                                                                                                |                  | UIL          | -                 |                              |                       |                       |  |  |  |

| -n = Value at           | POR                                                                                                                                                                                                                                                                                                            | '1' = Bit is set |              | '0' = Bit is clea | ared                         | x = Bit is unknown    |                       |  |  |  |

| bit 5-2                 | <ul> <li>10 = Data wait of 3 TCY; multiplexed address phase of 3 TCY</li> <li>01 = Data wait of 2 TCY; multiplexed address phase of 2 TCY</li> <li>00 = Data wait of 1 TCY; multiplexed address phase of 1 TCY</li> <li>5-2 WAITM3:WAITM0: Read to Byte Enable Strobe Wait State Configuration bits</li> </ul> |                  |              |                   |                              |                       |                       |  |  |  |

|                         | 1111 = Wait of additional 15 Tcy                                                                                                                                                                                                                                                                               |                  |              |                   |                              |                       |                       |  |  |  |

|                         | <br>0001 = Wait of additional 1 Tcy<br>0000 = No additional wait cycles (operation forced into one Tcy)                                                                                                                                                                                                        |                  |              |                   |                              |                       |                       |  |  |  |

| bit 1-0                 | WAITE1:WAI                                                                                                                                                                                                                                                                                                     | TE0: Data Hold   | After Strobe | Wait State Conf   | iguration bits <sup>(1</sup> | )                     |                       |  |  |  |

|                         | 11 = Wait of 4 Tcy                                                                                                                                                                                                                                                                                             |                  |              |                   |                              |                       |                       |  |  |  |

|                         | 10 = Wait of 3                                                                                                                                                                                                                                                                                                 |                  |              |                   |                              |                       |                       |  |  |  |

|                         | 01 = Wait of 2                                                                                                                                                                                                                                                                                                 |                  |              |                   |                              |                       |                       |  |  |  |

|                         | 00 = Wait of 1                                                                                                                                                                                                                                                                                                 | IICY             |              |                   |                              |                       |                       |  |  |  |

**Note 1:** WAITB and WAITE bits are ignored whenever WAITM3:WAITM0 = 0000.

#### REGISTER 11-5: PMEH: PARALLEL PORT ENABLE REGISTER HIGH BYTE

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|--------|--------|--------|--------|--------|--------|-------|-------|

| PTEN15 | PTEN14 | PTEN13 | PTEN12 | PTEN11 | PTEN10 | PTEN9 | PTEN8 |

| bit 7  |        |        |        |        |        |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-6 | PTEN15:PTEN14: PMCSx Strobe Enable bits                                                                                                          |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = PMA15 and PMA14 function as either PMA&lt;15:14&gt; or PMCS2 and PMCS1</li> <li>0 = PMA15 and PMA14 function as port I/O</li> </ul> |

| bit 5-0 | PTEN13:PTEN8: PMP Address Port Enable bits                                                                                                       |

|         | <ul> <li>1 = PMA&lt;13:8&gt; function as PMP address lines</li> <li>0 = PMA&lt;13:8&gt; function as port I/O</li> </ul>                          |

#### 18.0 ENHANCED CAPTURE/ COMPARE/PWM (ECCP) MODULE

In the PIC18F87J10 family of devices, three of the CCP modules are implemented as standard CCP modules with Enhanced PWM capabilities. These include the provision for 2 or 4 output channels, user-selectable polarity, dead-band control and automatic shutdown and restart. The Enhanced features are discussed in detail in **Section 18.4 "Enhanced PWM Mode"**. Capture, Compare and single-output PWM functions of the ECCP module are the same as described for the standard CCP module.

The control register for the Enhanced CCP module is shown in Register 18-1. It differs from the CCP4CON/ CCP5CON registers in that the two Most Significant bits are implemented to control PWM functionality.

In addition to the expanded range of modes available through the Enhanced CCPxCON register, the ECCP modules each have two additional registers associated with Enhanced PWM operation and auto-shutdown features. They are:

- ECCPxDEL (ECCPx PWM Delay)

- ECCPxAS (ECCPx Auto-Shutdown Control)

| REGISTER 18-1: | CCPxCON: ECCPx CONTROL REGISTER (ECCP1/ECCP2/ECCP3) |

|----------------|-----------------------------------------------------|

|                |                                                     |

| R/W-0        | R/W-0                                                                                                                                                                                  | R/W-0                                                                                                                                                   | R/W-0         | R/W-0             | R/W-0                  | R/W-0                     | R/W-0  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|------------------------|---------------------------|--------|--|--|--|--|

| PxM1         | PxM0                                                                                                                                                                                   | DCxB1                                                                                                                                                   | DCxB0         | CCPxM3            | CCPxM2                 | CCPxM1                    | CCPxM0 |  |  |  |  |

| bit 7        |                                                                                                                                                                                        |                                                                                                                                                         |               |                   |                        |                           | bit C  |  |  |  |  |

|              |                                                                                                                                                                                        |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

| Legend:      |                                                                                                                                                                                        |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

| R = Readab   | le bit                                                                                                                                                                                 | W = Writable I                                                                                                                                          | oit           | U = Unimplem      | nented bit, read       | d as '0'                  |        |  |  |  |  |

| -n = Value a | It POR                                                                                                                                                                                 | '1' = Bit is set                                                                                                                                        |               | '0' = Bit is clea | ared                   | x = Bit is unkr           | nown   |  |  |  |  |

|              |                                                                                                                                                                                        |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

| bit 7-6      | PxM1:PxM0:                                                                                                                                                                             | Enhanced PWM                                                                                                                                            | Output Config | uration bits      |                        |                           |        |  |  |  |  |

|              |                                                                                                                                                                                        | <u>CPxM2 = 00, 01,</u><br>signed as Captur                                                                                                              |               | ut/output: DvD F  |                        | and an part pipe          |        |  |  |  |  |

|              | If CCPxM3:C                                                                                                                                                                            | •                                                                                                                                                       | e/Compare inp | иі/оцриі, Рхв, г  | -xc, FxD assig         | led as port pins          |        |  |  |  |  |

|              |                                                                                                                                                                                        |                                                                                                                                                         | lulated; PxB, | PxC, PxD assig    | ned as port pir        | IS                        |        |  |  |  |  |

|              |                                                                                                                                                                                        | 00 = Single output: PxA modulated; PxB, PxC, PxD assigned as port pins<br>01 = Full-bridge output forward: P1D modulated; P1A active; P1B, P1C inactive |               |                   |                        |                           |        |  |  |  |  |

|              | 10 = Half-bridge output: P1A, P1B modulated with dead-band control; P1C, P1D assigned as port pins                                                                                     |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

|              | 11 = Full-bridge output reverse: P1B modulated; P1C active; P1A, P1D inactive                                                                                                          |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

| bit 5-4      | DCxB1:DCxB0: PWM Duty Cycle bit 1 and bit 0                                                                                                                                            |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

|              | <u>Capture mode:</u><br>Unused.                                                                                                                                                        |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

|              | Compare mode:                                                                                                                                                                          |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

|              | Unused.                                                                                                                                                                                |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

|              | <u>PWM mode:</u><br>These bits are the two LSbs of the 10-bit PWM duty cycle. The eight MSbs of the duty cycle are found in CCPRxL.                                                    |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

| bit 3-0      | CCPxM3:CCPxM0: ECCPx Module Mode Select bits                                                                                                                                           |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

|              | 0000 = Capture/Compare/PWM off (resets ECCPx module)                                                                                                                                   |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

|              | 0001 = Reserved                                                                                                                                                                        |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

|              | 0010 = Compare mode: toggle output on match                                                                                                                                            |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

|              | 0011 = Capture mode<br>0100 = Capture mode: every falling edge                                                                                                                         |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

|              | 0101 = Capture mode: every rising edge                                                                                                                                                 |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

|              | 0110 = Capture mode: every 4th rising edge<br>0111 = Capture mode, every 16th rising edge                                                                                              |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

|              | 1000 = Compare mode: initialize ECCPx pin low; set output on compare match (set CCPxIF)                                                                                                |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

|              | 1001 = Compare mode: initialize ECCPx pin high; clear output on compare match (set CCPxIF)                                                                                             |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

|              | 1010 = Compare mode: generate software interrupt only; ECCPx pin reverts to I/O state<br>1011 = Compare mode: trigger special event (ECCPx resets TMR1 or TMR3, sets CCPxIF bit, ECCP2 |                                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

|              | trigge                                                                                                                                                                                 | er also starts A/D                                                                                                                                      | conversion if | A/D module is en  | nabled) <sup>(1)</sup> | -, - <b>0 0 0 0 1</b> All | ,      |  |  |  |  |

|              |                                                                                                                                                                                        | 1 mode: PxA, Px0<br>1 mode: PxA, Px0                                                                                                                    |               |                   |                        |                           |        |  |  |  |  |

|              |                                                                                                                                                                                        | 1 mode: PxA, Px0                                                                                                                                        |               |                   |                        |                           |        |  |  |  |  |

|              |                                                                                                                                                                                        | 1 mode: PxA, Px                                                                                                                                         |               |                   |                        |                           |        |  |  |  |  |

Note 1: Implemented only for ECCP1 and ECCP2; same as '1010' for ECCP3.

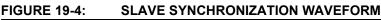

#### 19.3.7 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCKx. When the last bit is latched, the SSPxIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCKx pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device can be configured to wake-up from Sleep.

#### 19.3.8 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SSx}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with the  $\overline{SSx}$  pin control enabled (SSPxCON1<3:0> = 04h). When the  $\overline{SSx}$  pin is low, transmission and reception are enabled and the SDOx pin is driven. When the  $\overline{SSx}$  pin goes high, the SDOx pin is no longer driven, even if in the middle of a

transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When   | the       | SPI       | is   | in    | Slave     | mode    |

|---------|--------|-----------|-----------|------|-------|-----------|---------|

|         | with   | SSx       | pin       | C    | contr | ol e      | nabled  |

|         | (SSPx  | CON1      | <3:0>     | = 0  | 100   | ), the    | SPI     |

|         | module | e will re | set if th | ne S | Sx p  | in is set | to VDD. |

|         |        |           |           |      |       |           |         |

2: If the SPI is used in Slave mode with CKE set, then the SSx pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SSx pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDOx pin can be connected to the SDIx pin. When the SPI needs to operate as a receiver, the SDOx pin can be configured as an input. This disables transmissions from the SDOx. The SDIx can always be left as an input (SDIx function) since it cannot create a bus conflict.

#### 19.4.3.5 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and the SDAx line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit, BF (SSPxSTAT<0>), is set or bit, SSPOV (SSPxCON1<6>), is set.

An MSSP interrupt is generated for each data transfer byte. The interrupt flag bit, SSPxIF, must be cleared in software. The SSPxSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPxCON2<0> = 1), SCLx will be held low (clock stretch) following each data transfer. The clock must be released by setting bit, CKP (SSPxCON1<4>). See **Section 19.4.4** "Clock **Stretching**" for more details.

#### 19.4.3.6 Transmission

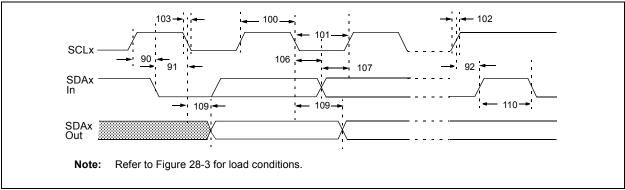

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register. The ACK pulse will be sent on the ninth bit and pin SCLx is held low regardless of SEN (see **Section 19.4.4 "Clock Stretching"** for more details). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPxBUF register which also loads the SSPxSR register. Then, pin SCLx should be enabled by setting bit, CKP (SSPxCON1<4>). The eight data bits are shifted out on the falling edge of the SCLx input. This ensures that the SDAx signal is valid during the SCLx high time (Figure 19-10).

The ACK pulse from the master-receiver is latched on the rising edge of the <u>ninth</u> SCLx input pulse. If the SDAx line is high (not ACK), then the data transfer is complete. In this case, when the ACK is latched by the slave, the slave logic is reset (resets the SSPxSTAT register) and the slave monitors for another occurrence of the Start bit. If the SDAx line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, pin SCLx must be enabled by setting bit, CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared in software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

#### 19.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDAx while SCLx outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the  $R/\overline{W}$  bit. In this case, the  $R/\overline{W}$  bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address, followed by a '1' to indicate the receive bit. Serial data is received via SDAx, while SCLx outputs the serial clock. Serial data is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

The Baud Rate Generator, used for the SPI mode operation, is used to set the SCLx clock frequency for either 100 kHz, 400 kHz or 1 MHz  $I^2C$  operation. See **Section 19.4.7 "Baud Rate"** for more details.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start Enable bit, SEN (SSPxCON2<0>).

- SSPxIF is set. The MSSP module will wait the required start time before any other operation takes place.

- 3. The user loads the SSPxBUF with the slave address to transmit.

- 4. Address is shifted out the SDAx pin until all 8 bits are transmitted.

- 5. The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPxCON2 register (SSPxCON2<6>).

- The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 7. The user loads the SSPxBUF with eight bits of data.

- 8. Data is shifted out the SDAx pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPxCON2 register (SSPxCON2<6>).

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 11. The user generates a Stop condition by setting the Stop Enable bit, PEN (SSPxCON2<2>).

- 12. Interrupt is generated once the Stop condition is complete.

#### 22.5.2 USB INTERRUPT ENABLE REGISTER (UIE)

The USB Interrupt Enable register (Register 22-8) contains the enable bits for the USB status interrupt sources. Setting any of these bits will enable the respective interrupt source in the UIR register.

The values in this register only affect the propagation of an interrupt condition to the microcontroller's interrupt logic. The flag bits are still set by their interrupt conditions, allowing them to be polled and serviced without actually generating an interrupt.

#### REGISTER 22-8: UIE: USB INTERRUPT ENABLE REGISTER

| U-0   | R/W-0 | R/W-0   | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|--------|-------|--------|--------|--------|

| —     | SOFIE | STALLIE | IDLEIE | TRNIE | ACTVIE | UERRIE | URSTIE |

| bit 7 |       |         |        |       |        |        | bit 0  |

| Legend:                           |                  |                       |                                    |  |  |