Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                     |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 49                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f67j50-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 64/80-Pin High-Performance, 1-Mbit Flash USB Microcontrollers with nanoWatt Technology

#### **Universal Serial Bus Features:**

- USB V2.0 Compliant SIE

- Low Speed (1.5 Mb/s) and Full Speed (12 Mb/s)

- Supports Control, Interrupt, Isochronous and Bulk Transfers

- Supports up to 32 Endpoints (16 bidirectional)

- 3.9-Kbyte Dual Access RAM for USB

- On-Chip USB Transceiver

#### Flexible Oscillator Structure:

- High-Precision PLL for USB

- Two External Clock modes, up to 48 MHz

- Internal 31 kHz Oscillator, Tunable Internal Oscillator, 31 kHz to 8 MHz

- Secondary Oscillator using Timer1 @ 32 kHz

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if any clock stops

#### **Peripheral Highlights:**

- High-Current Sink/Source 25 mA/25mA (PORTB and PORTC)

- Four Programmable External Interrupts

- · Four Input Change Interrupts

- Two Capture/Compare/PWM (CCP) modules

- Three Enhanced Capture/Compare/PWM (ECCP) modules:

- One, two or four PWM outputs

- Selectable polarity

- Programmable dead time

- Auto-shutdown and auto-restart

- Two Master Synchronous Serial Port (MSSP) modules supporting 3-Wire SPI (all 4 modes) and I<sup>2</sup>C<sup>™</sup> Master and Slave modes

- 8-Bit Parallel Master Port/Enhanced Parallel Slave Port with 16 Address Lines

- Dual Analog Comparators with Input Multiplexing

#### Peripheral Highlights (continued):

- 10-Bit, up to 12-Channel Analog-to-Digital (A/D) Converter module:

- Auto-acquisition capability

- Conversion available during Sleep

- Two Enhanced USART modules:

- Supports RS-485, RS-232 and LIN 1.2

- Auto-wake-up on Start bit

- Auto-Baud Detect

## External Memory Bus (80-pin devices only):

- · Address Capability of up to 2 Mbytes

- · 8-Bit or 16-Bit Interface

- · 12-Bit, 16-Bit and 20-Bit Addressing modes

#### **Special Microcontroller Features:**

- 5.5V Tolerant Inputs (digital-only pins)

- Low-Power, High-Speed CMOS Flash Technology

- C Compiler Optimized Architecture for Re-Entrant Code

- Power Management Features:

- Run: CPU on, peripherals on

- Idle: CPU off, peripherals on

- Sleep: CPU off, peripherals off

- · Priority Levels for Interrupts

- Self-Programmable under Software Control

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 131s

- Single-Supply In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- In-Circuit Debug (ICD) with 3 Breakpoints via Two Pins

- Operating Voltage Range of 2.0V to 3.6V

- On-Chip 2.5V Regulator

- Flash Program Memory of 10000 Erase/Write Cycles and 20-Year Data Retention

#### 2.2.5.1 OSCTUNE Register

The internal oscillator's output has been calibrated at the factory but can be adjusted in the user's application. This is done by writing to the OSCTUNE register (Register 2-1). The tuning sensitivity is constant throughout the tuning range.

When the OSCTUNE register is modified, the INTOSC and INTRC frequencies will begin shifting to the new frequency. The INTRC clock will reach the new frequency within 8 clock cycles (approximately,  $8 * 32 \ \mu s = 256 \ \mu s$ ). The INTOSC clock will stabilize within 1 ms. Code execution continues during this shift. There is no indication that the shift has occurred.

The OSCTUNE register also contains the INTSRC bit. The INTSRC bit allows users to select which internal oscillator provides the clock source when the 31 kHz frequency option is selected. This is covered in greater detail in **Section 2.4.1 "Oscillator Control Register"**.

The PLLEN bit, contained in the OSCTUNE register, can be used to enable or disable the internal 96 MHz PLL when running in one of the PLL type oscillator modes (e.g., INTOSCPLL). Oscillator modes that do not contain "PLL" in their name cannot be used with the PLL. In these modes, the PLL is always disabled regardless of the setting of the PLLEN bit.

When configured for one of the PLL enabled modes, setting the PLLEN bit does not immediately switch the device clock to the PLL output. The PLL requires up to two milliseconds to start up and lock during which time the device continues to be clocked. Once the PLL output is ready, the microcontroller core will automatically switch to the PLL derived frequency.

#### 2.2.5.2 Internal Oscillator Output Frequency and Drift

The internal oscillator block is calibrated at the factory to produce an INTOSC output frequency of 8.0 MHz. However, this frequency may drift as VDD or temperature changes, which can affect the controller operation in a variety of ways.

The low-frequency INTRC oscillator operates independently of the INTOSC source. Any changes in INTOSC across voltage and temperature are not necessarily reflected by changes in INTRC and vice versa.

#### 2.2.5.3 Compensating for INTOSC Drift

It is possible to adjust the INTOSC frequency by modifying the value in the OSCTUNE register. This has no effect on the INTRC clock source frequency.

Tuning the INTOSC source requires knowing when to make the adjustment, in which direction it should be made and in some cases, how large a change is needed. When using the EUSART, for example, an adjustment may be required when it begins to generate framing errors or receives data with errors while in Asynchronous mode. Framing errors indicate that the device clock frequency is too high; to adjust for this, decrement the value in OSCTUNE to reduce the clock frequency. On the other hand, errors in data may suggest that the clock speed is too low; to compensate, increment OSCTUNE to increase the clock frequency.

It is also possible to verify device clock speed against a reference clock. Two timers may be used: one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the Timer1 oscillator. Both timers are cleared but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value is greater than expected, then the internal oscillator block is running too fast. To adjust for this, decrement the OSCTUNE register.

Finally, a CCP module can use free-running Timer1 (or Timer3), clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded for use later. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

If the measured time is much greater than the calculated time, the internal oscillator block is running too fast; to compensate, decrement the OSCTUNE register. If the measured time is much less than the calculated time, the internal oscillator block is running too slow; to compensate, increment the OSCTUNE register.

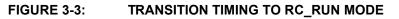

#### 3.2.3 RC\_RUN MODE

In RC\_RUN mode, the CPU and peripherals are clocked from the internal oscillator; the primary clock is shut down. This mode provides the best power conservation of all the Run modes while still executing code. It works well for user applications which are not highly timing sensitive or do not require high-speed clocks at all times.

This mode is entered by setting the SCS1:SCS0 bits (OSCCON<1:0>) to '11'. When the clock source is switched to the internal oscillator block (see Figure 3-3), the primary oscillator is shut down and the OSTS bit is cleared.

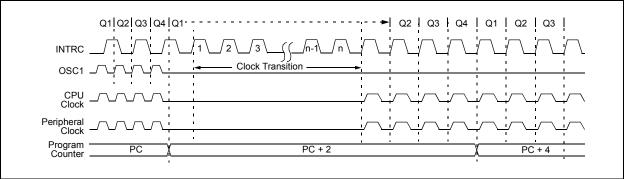

On transitions from RC\_RUN mode to PRI\_RUN mode, the device continues to be clocked from the INTOSC block while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 3-4). When the clock switch is complete, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCS bits are not affected by the switch. The INTRC block source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

#### FIGURE 3-4: TRANSITION TIMING FROM RC\_RUN MODE TO PRI\_RUN MODE

#### 3.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block. This mode allows for controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then clear the SCS bits and execute SLEEP. When the clock source is switched to the INTOSC block, the primary oscillator is shut down and the OSTS bit is cleared.

When a wake event occurs, the peripherals continue to be clocked from the internal oscillator block. After a delay of TCSD following the wake event, the CPU begins executing code being clocked by the INTRC. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

#### 3.5 Exiting Idle and Sleep Modes

An exit from Sleep mode, or any of the Idle modes, is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes sections (see Section 3.2 "Run Modes", Section 3.3 "Sleep Mode" and Section 3.4 "Idle Modes").

#### 3.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle mode, or the Sleep mode, to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

On all exits from Idle or Sleep modes by interrupt, code execution branches to the interrupt vector if the GIE/GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see Section 9.0 "Interrupts").

A fixed delay of interval, TCSD, following the wake event is required when leaving Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

#### 3.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 3.2 "Run Modes" and Section 3.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 25.2 "Watchdog Timer (WDT)").

The Watchdog Timer and postscaler are cleared by one of the following events:

- Executing a SLEEP or CLRWDT instruction

- The loss of a currently selected clock source (if the Fail-Safe Clock Monitor is enabled)

#### 3.5.3 EXIT BY RESET

Exiting an Idle or Sleep mode by Reset automatically forces the device to run from the INTRC.

#### 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode, where the primary clock source is not stopped; and

- the primary clock source is either the EC or ECPLL mode.

In these instances, the primary clock source either does not require an oscillator start-up delay, since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (EC). However, a fixed delay of interval, TCSD, following the wake event is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

#### 5.1.6.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 5-2) contains the Stack Pointer value, the STKFUL (Stack Full) status bit and the STKUNF (Stack Underflow) status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off the stack. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a POR.

The action that takes place when the stack becomes full depends on the state of the STVREN (Stack Overflow Reset Enable) Configuration bit. (Refer to **Section 25.1 "Configuration Bits**" for a description of the device Configuration bits.) If STVREN is set (default), the 31st push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31st push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31st push and the STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return a value of zero to the PC and set the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

| Note: | Returning a value of zero to the PC on an<br>underflow has the effect of vectoring the<br>program to the Reset vector, where the<br>stack conditions can be verified and<br>appropriate actions can be taken. This is<br>not the same as a Reset, as the contents |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | of the SFRs are not affected.                                                                                                                                                                                                                                     |

#### 5.1.6.3 PUSH and POP Instructions

Since the Top-of-Stack is readable and writable, the ability to push values onto the stack and pull values off the stack, without disturbing normal program execution, is a desirable feature. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

x = Bit is unknown

#### R/C-0 R/C-0 R/W-0 R/W-0 R/W-0 R/W-0 U-0 R/W-0 STKFUL<sup>(1)</sup> STKUNF<sup>(1)</sup> SP4 SP3 SP2 SP1 SP0 bit 7 bit 0 Legend: C = Clearable only bit R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

'0' = Bit is cleared

#### REGISTER 5-2: STKPTR: STACK POINTER REGISTER

'1' = Bit is set

bit 7STKFUL: Stack Full Flag bit<sup>(1)</sup>1 = Stack became full or overflowed0 = Stack has not become full or overflowedbit 6STKUNF: Stack Underflow Flag bit<sup>(1)</sup>1 = Stack underflow occurred0 = Stack underflow did not occurbit 5Unimplemented: Read as '0'bit 4-0SP4:SP0: Stack Pointer Location bits

**Note 1:** Bit 7 and bit 6 are cleared by user software or by a POR.

-n = Value at POR

| R/W-1         | R/W-1             | R/W-0                             | R/W-0            | R/W-0            | R/W-0           | R/W-0            | R/W-0       |

|---------------|-------------------|-----------------------------------|------------------|------------------|-----------------|------------------|-------------|

| INT2IP        | INT1IP            | INT3IE                            | INT2IE           | INT1IE           | INT3IF          | INT2IF           | INT1IF      |

| bit 7         |                   |                                   | ·                |                  | ·               |                  | bit (       |

| Legend:       |                   |                                   |                  |                  |                 |                  |             |

| R = Readabl   | e bit             | W = Writable                      | bit              | U = Unimpler     | nented bit, rea | d as '0'         |             |

| -n = Value at | POR               | '1' = Bit is set                  |                  | '0' = Bit is cle | ared            | x = Bit is unkr  | nown        |

| bit 7         | INT2IP: INT2      | External Interr                   | upt Priority bit |                  |                 |                  |             |

|               | 1 = High prio     | ority                             |                  |                  |                 |                  |             |

|               | 0 = Low prior     | rity                              |                  |                  |                 |                  |             |

| bit 6         | INT1IP: INT1      | External Interr                   | upt Priority bit |                  |                 |                  |             |

|               | 1 = High pric     |                                   |                  |                  |                 |                  |             |

|               | 0 = Low prior     | •                                 |                  |                  |                 |                  |             |

| bit 5         |                   | External Interr                   | •                |                  |                 |                  |             |

|               |                   | the INT3 extern                   |                  |                  |                 |                  |             |

| L:1 4         |                   | the INT3 exter                    | •                |                  |                 |                  |             |

| bit 4         |                   | External Interr                   | •                |                  |                 |                  |             |

|               |                   | the INT2 exterr<br>the INT2 exter |                  |                  |                 |                  |             |

| bit 3         |                   | External Interr                   | •                |                  |                 |                  |             |

| bit o         |                   | the INT1 extern                   | •                |                  |                 |                  |             |

|               |                   | the INT1 exter                    |                  |                  |                 |                  |             |

| bit 2         | INT3IF: INT3      | External Interro                  | upt Flag bit     |                  |                 |                  |             |

|               | 1 = The INT       | 3 external interr                 | upt occurred (   | must be cleare   | d in software)  |                  |             |

|               | 0 = The INT3      | 3 external interr                 | upt did not oc   | cur              |                 |                  |             |

| bit 1         | INT2IF: INT2      | External Interre                  | upt Flag bit     |                  |                 |                  |             |

|               |                   |                                   |                  | must be cleare   | d in software)  |                  |             |

|               | 0 = The INT2      | 2 external interr                 | upt did not oc   | cur              |                 |                  |             |

| bit 0         | INT1IF: INT1      | External Interre                  | upt Flag bit     |                  |                 |                  |             |

|               |                   |                                   |                  | must be cleare   | d in software)  |                  |             |

|               | 0 = 1 he INT      | l external interr                 | upt did not oc   | cur              |                 |                  |             |

|               |                   |                                   |                  |                  |                 |                  |             |

| Note: In      | terrupt flag bits | are set when                      | an interrupt co  | ondition occurs  | regardless of   | the state of its | correspondi |

#### REGISTER 9-3: INTCON3: INTERRUPT CONTROL REGISTER 3

**Note:** Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### 11.3.5 CHIP SELECT FEATURES

Up to two chip select lines, PMCS1 and PMCS2, are available for the Master modes of the PMP. The two chip select lines are multiplexed with the Most Significant bits of the address bus (PMADDRH<6> and PMADDRH<7>). When a pin is configured as a chip select, it is not included in any address auto-increment/ decrement. The function of the chip select signals is configured using the chip select function bits (PMCONL<7:6>).

#### 11.3.6 AUTO-INCREMENT/DECREMENT

While the module is operating in one of the Master modes, the INCM bits (PMMODEH<3:4>) control the behavior of the address value. The address can be made to automatically increment or decrement after each read and write operation. The address increments once each operation is completed and the BUSY bit goes to '0'. If the chip select signals are disabled and configured as address bits, the bits will participate in the increment and decrement operations; otherwise, the CS2 and CS1 bit values will be unaffected.

#### 11.3.7 WAIT STATES

In Master mode, the user has control over the duration of the read, write and address cycles by configuring the module wait states. Three portions of the cycle, the beginning, middle and end, are configured using the corresponding WAITBx, WAITMx and WAITEx bits in the PMMODEL register.

The WAITB bits (PMMODEL<7:6>) set the number of wait cycles for the data setup prior to the PMRD/PMWT strobe in Mode 10, or prior to the PMENB strobe in Mode 11. The WAITM bits (PMMODEL<5:2>) set the number of wait cycles for the PMRD/PMWT strobe in Mode 10, or for the PMENB strobe in Mode 11. When this wait state setting is 0 then WAITB and WAITE have no effect. The WAITE bits (PMMODEL<1:0>) define the number of wait cycles for the data hold time after the PMRD/PMWT strobe in Mode 10, or after the PMENB strobe in Mode 11.

#### 11.3.8 READ OPERATION

To perform a read on the Parallel Master Port, the user reads the PMDIN1L register. This causes the PMP to output the desired values on the chip select lines and the address bus. Then the read line (PMRD) is strobed. The read data is placed into the PMDIN1L register. If the 16-bit mode is enabled (MODE16 = 1), the read of the low byte of the PMDIN1L register will initiate two bus reads. The first read data byte is placed into the PMDIN1L register, and the second read data is placed into the PMDIN1H.

Note that the read data obtained from the PMDIN1L register is actually the read value from the previous read operation. Hence, the first user read will be a dummy read to initiate the first bus read and fill the read register. Also, the requested read value will not be ready until after the BUSY bit is observed low. Thus, in a back-to-back read operation, the data read from the register will be the same for both reads. The next read of the register will yield the new value.

#### 11.3.9 WRITE OPERATION

To perform a write onto the parallel bus, the user writes to the PMDIN1L register. This causes the module to first output the desired values on the chip select lines and the address bus. The write data from the PMDIN1L register is placed onto the PMD<7:0> data bus. Then the write line (PMWR) is strobed. If the 16-bit mode is enabled (MODE16 = 1), the write to the PMDIN1L register will initiate two bus writes. First write will consist of the data contained in PMDIN1L and the second write will contain the PMDIN1H.

#### 11.3.10 PARALLEL MASTER PORT STATUS

#### 11.3.10.1 The BUSY Bit

In addition to the PMP interrupt, a BUSY bit is provided to indicate the status of the module. This bit is only used in Master mode. While any read or write operation is in progress, the BUSY bit is set for all but the very last CPU cycle of the operation. In effect, if a single-cycle read or write operation is requested, the BUSY bit will never be active. This allows back-to-back transfers. While the bit is set, any request by the user to initiate a new operation will be ignored (i.e., writing or reading the lower byte of the PMDIN1L register will not initiate either a read nor a write).

#### 11.3.10.2 INTERRUPTS

When the PMP module interrupt is enabled for Master mode, the module will interrupt on every completed read or write cycle; otherwise, the BUSY bit is available to query the status of the module.

### 13.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt on overflow

- Reset on CCP Special Event Trigger

- Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 13-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 13-2.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 13-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

#### REGISTER 13-1: T1CON: TIMER1 CONTROL REGISTER<sup>(1)</sup>

| R/W-0 | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| RD16  | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

| Legend:      |                                                          |                                                                                                                     |                                                              |                    |

|--------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------|

| R = Readab   | le bit                                                   | W = Writable bit                                                                                                    | U = Unimplemented bit,                                       | , read as '0'      |

| -n = Value a | t POR                                                    | '1' = Bit is set                                                                                                    | '0' = Bit is cleared                                         | x = Bit is unknown |

| bit 7        | <b>RD16:</b> 16                                          | 6-Bit Read/Write Mode Enab                                                                                          | ble bit                                                      |                    |

|              |                                                          | bles register read/write of TI<br>bles register read/write of Ti                                                    | mer1 in one 16-bit operation<br>mer1 in two 8-bit operations |                    |

| bit 6        | T1RUN:                                                   | Timer1 System Clock Status                                                                                          | s bit                                                        |                    |

|              | -                                                        | ce clock is derived from Tim<br>ce clock is derived from and                                                        |                                                              |                    |

| bit 5-4      | 11 = 1:8<br>10 = 1:4<br>01 = 1:2                         | 1:T1CKPS0: Timer1 Input C<br>Prescale value<br>Prescale value<br>Prescale value<br>Prescale value                   | Clock Prescale Select bits                                   |                    |

| bit 3        | 1 = Time<br>0 = Time                                     | N: Timer1 Oscillator Enable<br>r1 oscillator is enabled<br>r1 oscillator is shut off<br>lator inverter and feedback | bit<br>resistor are turned off to elimina                    | ate power drain.   |

| bit 2        | <u>When TN</u><br>1 = Do n<br>0 = Sync<br><u>When TN</u> | <u>MR1CS = 1:</u><br>ot synchronize external cloc<br>hronize external clock input<br><u>MR1CS = 0:</u>              |                                                              | 0.                 |

| bit 1        | 1 = Exte                                                 | Timer1 Clock Source Sele<br>rnal clock from pin RC0/T10<br>nal clock (Fosc/4)                                       | ct bit<br>DSO/T13CKI (on the rising edge                     | e)                 |

| bit 0        | TMR10N                                                   | I: Timer1 On bit<br>bles Timer1                                                                                     |                                                              |                    |

| Note 1.      | -                                                        |                                                                                                                     | ailable when WDTCON<4> = 0                                   |                    |

Note 1: Default (legacy) SFR at this address, available when WDTCON<4> = 0.

#### 15.2 Timer3 16-Bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes (see Figure 15-2). When the RD16 control bit (T3CON<7>) is set, the address for TMR3H is mapped to a buffer register for the high byte of Timer3. A read from TMR3L will load the contents of the high byte of Timer3 into the Timer3 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3 must also take place through the TMR3H Buffer register. The Timer3 high byte is updated with the contents of TMR3H when a write occurs to TMR3L. This allows a user to write all 16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or writable in this mode. All reads and writes must take place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler. The prescaler is only cleared on writes to TMR3L.

#### 15.3 Using the Timer1 Oscillator as the Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. To use it as the Timer3 clock source, the TMR3CS bit must also be set. As previously noted, this also configures Timer3 to increment on every rising edge of the oscillator source.

The Timer1 oscillator is described in Section 13.0 "Timer1 Module".

#### 15.4 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled or disabled by setting or clearing the Timer3 Interrupt Enable bit, TMR3IE (PIE2<1>).

#### 15.5 Resetting Timer3 Using the ECCP Special Event Trigger

If ECCP1 or ECCP2 is configured to use Timer3 and to generate a Special Event Trigger in Compare mode (CCPxM3:CCPxM0 = 1011), this signal will reset Timer3. The trigger from ECCP2 will also start an A/D conversion if the A/D module is enabled (see **Section 18.2.1 "Special Event Trigger"** for more information).

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPRxH:CCPRxL register pair effectively becomes a period register for Timer3.

If Timer3 is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timer3 coincides with a Special Event Trigger from an ECCP module, the write will take precedence.

Note: The Special Event Triggers from the ECCPx module will not set the TMR3IF interrupt flag bit (PIR1<0>).

| TADLE 13             | I. KLOI                   | STERS AS  | SUCIATE |         | WERJ AJ |        | SOUNTER |        |                             |

|----------------------|---------------------------|-----------|---------|---------|---------|--------|---------|--------|-----------------------------|

| Name                 | Bit 7                     | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0  | Reset<br>Values<br>on Page: |

| INTCON               | GIE/GIEH                  | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF  | RBIF   | 61                          |

| PIR2                 | OSCFIF                    | CM2IF     | CM1IF   | USBIF   | BCL1IF  | LVDIF  | TMR3IF  | CCP2IF | 64                          |

| PIE2                 | OSCFIE                    | CM2IE     | CM1IE   | USBIE   | BCL1IE  | LVDIE  | TMR3IE  | CCP2IE | 64                          |

| IPR2                 | OSCFIP                    | CM2IP     | CM1IP   | USBIP   | BCL1IP  | LVDIP  | TMR3IP  | CCP2IP | 64                          |

| TMR3L                | Timer3 Register Low Byte  |           |         |         |         |        |         |        | 65                          |

| TMR3H                | Timer3 Register High Byte |           |         |         |         |        |         | 65     |                             |

| T1CON <sup>(1)</sup> | RD16                      | T1RUN     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS  | TMR10N | 62                          |

| T3CON                | RD16                      | T3CCP2    | T3CKPS1 | T3CKPS0 | T3CCP1  | T3SYNC | TMR3CS  | TMR3ON | 65                          |

TABLE 15-1:

REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

**Note 1:** Default (legacy) SFR at this address, available when WDTCON<4> = 0.

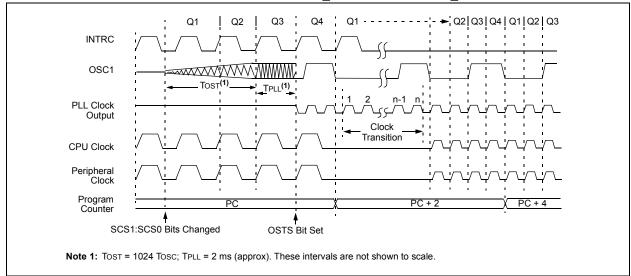

#### 18.4.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The PWM duty cycle is calculated by the following equation:

#### EQUATION 18-2:

PWM Duty Cycle = (CCPR1L:CCP1CON<5:4>) • Tosc • (TMR2 Prescale Value)

CCPR1L and CCP1CON<5:4> can be written to at any time but the duty cycle value is not copied into CCPR1H until a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation. When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or two bits of the TMR2 prescaler, the ECCP1 pin is cleared. The maximum PWM resolution (bits) for a given PWM frequency is given by the equation:

#### EQUATION 18-3:

Note: If the PWM duty cycle value is longer than the PWM period, the ECCP1 pin will not be cleared.

#### 18.4.3 PWM OUTPUT CONFIGURATIONS

The P1M1:P1M0 bits in the CCP1CON register allow one of four configurations:

- Single Output

- Half-Bridge Output

- · Full-Bridge Output, Forward mode

- Full-Bridge Output, Reverse mode

The Single Output mode is the standard PWM mode discussed in **Section 18.4 "Enhanced PWM Mode"**. The Half-Bridge and Full-Bridge Output modes are covered in detail in the sections that follow.

The general relationship of the outputs in all configurations is summarized in Figure 18-2.

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh      | FFh      | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8          | 7          | 6.58       |

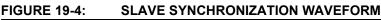

#### 19.3.7 SLAVE MODE

In Slave mode, the data is transmitted and received as the external clock pulses appear on SCKx. When the last bit is latched, the SSPxIF interrupt flag bit is set.

While in Slave mode, the external clock is supplied by the external clock source on the SCKx pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in Sleep mode, the slave can transmit/receive data. When a byte is received, the device can be configured to wake-up from Sleep.

#### 19.3.8 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SSx}$  pin allows a Synchronous Slave mode. The SPI must be in Slave mode with the  $\overline{SSx}$  pin control enabled (SSPxCON1<3:0> = 04h). When the  $\overline{SSx}$  pin is low, transmission and reception are enabled and the SDOx pin is driven. When the  $\overline{SSx}$  pin goes high, the SDOx pin is no longer driven, even if in the middle of a

transmitted byte and becomes a floating output. External pull-up/pull-down resistors may be desirable depending on the application.

| Note 1: | When   | the       | SPI       | is   | in    | Slave     | mode    |

|---------|--------|-----------|-----------|------|-------|-----------|---------|

|         | with   | SSx       | pin       | C    | contr | ol e      | nabled  |

|         | (SSPx  | CON1      | <3:0>     | = 0  | 100   | ), the    | SPI     |

|         | module | e will re | set if th | ne S | Sx p  | in is set | to VDD. |

|         |        |           |           |      |       |           |         |

2: If the SPI is used in Slave mode with CKE set, then the SSx pin control must be enabled.

When the SPI module resets, the bit counter is forced to '0'. This can be done by either forcing the SSx pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDOx pin can be connected to the SDIx pin. When the SPI needs to operate as a receiver, the SDOx pin can be configured as an input. This disables transmissions from the SDOx. The SDIx can always be left as an input (SDIx function) since it cannot create a bus conflict.

#### 22.2 USB Status and Control

The operation of the USB module is configured and managed through three control registers. In addition, a total of 22 registers are used to manage the actual USB transactions. The registers are:

- USB Control register (UCON)

- USB Configuration register (UCFG)

- USB Transfer Status register (USTAT)

- USB Device Address register (UADDR)

- Frame Number registers (UFRMH:UFRML)

- Endpoint Enable registers 0 through 15 (UEPn)

#### 22.2.1 USB CONTROL REGISTER (UCON)

The USB Control register (Register 22-1) contains bits needed to control the module behavior during transfers. The register contains bits that control the following:

- Main USB Peripheral Enable

- Ping-Pong Buffer Pointer Reset

- Control of the Suspend mode

- Packet Transfer Disable

#### REGISTER 22-1: UCON: USB CONTROL REGISTER

In addition, the USB Control register contains a status bit, SE0 (UCON<5>), which is used to indicate the occurrence of a single-ended zero on the bus. When the USB module is enabled, this bit should be monitored to determine whether the differential data lines have come out of a single-ended zero condition. This helps to differentiate the initial power-up state from the USB Reset signal.

The overall operation of the USB module is controlled by the USBEN bit (UCON<3>). Setting this bit activates the module and resets all of the PPBI bits in the Buffer Descriptor Table to '0'. This bit also activates the internal pull-up resistors, if they are enabled. Thus, this bit can be used as a soft attach/detach to the USB. Although all status and control bits are ignored when this bit is clear, the module needs to be fully preconfigured prior to setting this bit. This bit cannot be set until the USB module is supplied with an active clock source. If the PLL is being used, it should be enabled at least two milliseconds (enough time for the PLL to lock) before attempting to set the USBEN bit.

| U-0   | R/W-0  | R-x | R/C-0  | R/W-0                | R/W-0  | R/W-0  | U-0   |

|-------|--------|-----|--------|----------------------|--------|--------|-------|

| —     | PPBRST | SE0 | PKTDIS | USBEN <sup>(1)</sup> | RESUME | SUSPND | —     |

| bit 7 |        |     |        |                      |        |        | bit 0 |

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0'                                                                                                                                                                                            |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | PPBRST: Ping-Pong Buffers Reset bit                                                                                                                                                                                   |

|       | <ul> <li>1 = Reset all Ping-Pong Buffer Pointers to the Even Buffer Descriptor (BD) banks</li> <li>0 = Ping-Pong Buffer Pointers not being reset</li> </ul>                                                           |

| bit 5 | SE0: Live Single-Ended Zero Flag bit                                                                                                                                                                                  |

|       | <ul><li>1 = Single-ended zero active on the USB bus</li><li>0 = No single-ended zero detected</li></ul>                                                                                                               |

| bit 4 | PKTDIS: Packet Transfer Disable bit                                                                                                                                                                                   |

|       | <ul> <li>1 = SIE token and packet processing disabled, automatically set when a SETUP token is received</li> <li>0 = SIE token and packet processing enabled</li> </ul>                                               |

| bit 3 | USBEN: USB Module Enable bit <sup>(1)</sup>                                                                                                                                                                           |

|       | <ul> <li>1 = USB module and supporting circuitry enabled (device attached)</li> <li>0 = USB module and supporting circuitry disabled (device detached)</li> </ul>                                                     |

| bit 2 | RESUME: Resume Signaling Enable bit                                                                                                                                                                                   |

|       | <ul><li>1 = Resume signaling activated</li><li>0 = Resume signaling disabled</li></ul>                                                                                                                                |

| bit 1 | SUSPND: Suspend USB bit                                                                                                                                                                                               |

|       | <ul> <li>1 = USB module and supporting circuitry in Power Conserve mode, SIE clock inactive</li> <li>0 = USB module and supporting circuitry in normal operation, SIE clock clocked at the configured rate</li> </ul> |

| bit 0 | Unimplemented: Read as '0'                                                                                                                                                                                            |

|       |                                                                                                                                                                                                                       |

Note 1: This bit cannot be set if the USB module does not have an appropriate clock source.

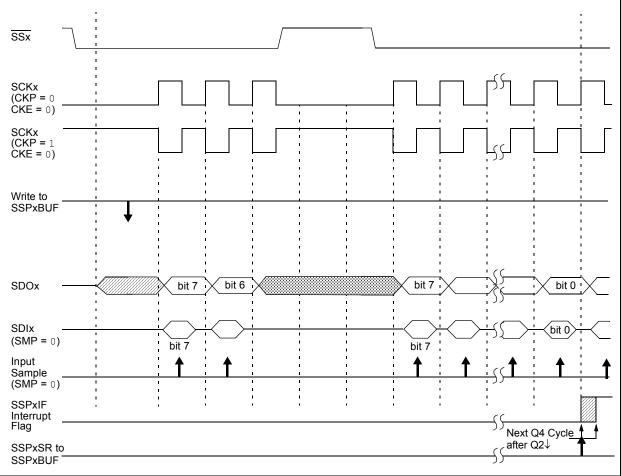

FIGURE 25-5: FSCM TIMING DIAGRAM

#### 25.5.2 EXITING FAIL-SAFE OPERATION

The fail-safe condition is terminated by either a device Reset or by entering a power-managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 2H (with any required start-up delays that are required for the oscillator mode, such as OST or PLL timer). The INTRC oscillator provides the device clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The Fail-Safe Clock Monitor then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTRC oscillator. The OSCCON register will remain in its Reset state until a power-managed mode is entered.

#### 25.5.3 FSCM INTERRUPTS IN POWER-MANAGED MODES

By entering a power-managed mode, the clock multiplexor selects the clock source selected by the OSCCON register. Fail-Safe Clock Monitoring of the power-managed clock source resumes in the power-managed mode.

If an oscillator failure occurs during power-managed operation, the subsequent events depend on whether or not the oscillator failure interrupt is enabled. If enabled (OSCFIF = 1), code execution will be clocked by the INTRC multiplexor. An automatic transition back to the failed clock source will not occur.

If the interrupt is disabled, subsequent interrupts while in Idle mode will cause the CPU to begin executing instructions while being clocked by the INTRC source.

#### 25.5.4 POR OR WAKE-UP FROM SLEEP

The FSCM is designed to detect oscillator failure at any point after the device has exited Power-on Reset (POR) or low-power Sleep mode. When the primary device clock is either the EC or INTRC modes, monitoring can begin immediately following these events.

For HS or HSPLL modes, the situation is somewhat different. Since the oscillator may require a start-up time considerably longer than the FSCM sample clock time, a false clock failure may be detected. To prevent this, the internal oscillator block is automatically configured as the device clock and functions until the primary clock is stable (the OST and PLL timers have timed out). This is identical to Two-Speed Start-up mode. Once the primary clock is stable, the INTRC returns to its role as the FSCM source.

| Note: | The same logic that prevents false oscilla-      |  |  |

|-------|--------------------------------------------------|--|--|

|       | tor failure interrupts on POR, or wake from      |  |  |

|       | Sleep, will also prevent the detection of        |  |  |

|       | the oscillator's failure to start at all follow- |  |  |

|       | ing these events. This can be avoided by         |  |  |

|       | monitoring the OSTS bit and using a              |  |  |

|       | timing routine to determine if the oscillator    |  |  |

|       | is taking too long to start. Even so, no         |  |  |

|       | oscillator failure interrupt will be flagged.    |  |  |

As noted in **Section 25.4.1 "Special Considerations for Using Two-Speed Start-up"**, it is also possible to select another clock configuration and enter an alternate power-managed mode while waiting for the primary clock to become stable. When the new power-managed mode is selected, the primary clock is disabled.

| ax:            |                                                                                                                                                          | Unconditional Branch                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                | BRA n                                                                                                                                                    | BRA n                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| ands:          | -1024 ≤ n ≤                                                                                                                                              | $-1024 \le n \le 1023$                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| ation:         | (PC) + 2 + 2                                                                                                                                             | $2n \rightarrow PC$                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| s Affected:    | None                                                                                                                                                     | None                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| ding:          | 1101                                                                                                                                                     | 0nnn                                                                                                                                                                                                                                                                           | nnn                                                                                                                                                                                                                                                                                                                                                                                                                    | n nnnn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| ription:       | the PC. Sin<br>incrementer<br>instruction,<br>PC + 2 + 2r                                                                                                | Add the 2's complement number '2n' to<br>the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is a<br>two-cycle instruction.                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| s:             | 1                                                                                                                                                        | 1                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| es:            | 2                                                                                                                                                        | 2                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| ycle Activity: |                                                                                                                                                          |                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Q1             | Q2                                                                                                                                                       | Q3                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                        | Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Decode         | Read literal<br>'n'                                                                                                                                      |                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                        | Write to<br>PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| No             | No                                                                                                                                                       | No                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                        | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| operation      | operation                                                                                                                                                | operati                                                                                                                                                                                                                                                                        | on                                                                                                                                                                                                                                                                                                                                                                                                                     | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| PC             | = ad                                                                                                                                                     | dress (H                                                                                                                                                                                                                                                                       | HERE)                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                | s Affected:<br>ding:<br>ription:<br>s:<br>s:<br>ycle Activity:<br>Q1<br>Decode<br>No<br>operation<br>hple:<br>Before Instruct<br>PC<br>After Instruction | s Affected: None<br>ding: 1101<br>ription: Add the 2's<br>the PC. Sin<br>incrementer<br>instruction,<br>PC + 2 + 2r<br>two-cycle in<br>s: 1<br>es: 2<br>ycle Activity:<br>Q1 Q2<br>Decode Read literal<br>'n'<br>No No<br>operation Operation<br>PC = add<br>After Instruction | s Affected: None<br>ding: <u>1101 0nnn</u><br>ription: Add the 2's complen<br>the PC. Since the PC<br>incremented to fetch<br>instruction, the new<br>PC + 2 + 2n. This inst<br>two-cycle instruction<br>s: 1<br>es: 2<br>ycle Activity:<br><u>Q1 Q2 Q3</u><br><u>Decode Read literal Proce</u><br><u>'n' Data</u><br><u>No No No No</u><br><u>operation operation</u><br><u>pc = address (Fe</u><br>After Instruction | s Affected: None<br>ding: <u>1101 0nnn nnn</u><br>ription: Add the 2's complement n<br>the PC. Since the PC will b<br>incremented to fetch the n<br>instruction, the new address<br>PC + 2 + 2n. This instruction<br>two-cycle instruction.<br>s: 1<br>es: 2<br>ycle Activity:<br><u>Q1 Q2 Q3</u><br><u>Decode Read literal Process</u><br>'n' <u>Data</u><br><u>No No No operation</u><br><u>uple: HERE BRA Jump</u><br>Before Instruction<br>PC = address (HERE)<br>After Instruction |  |  |  |

| BSF                                | Bit Set f                                                                                           | Bit Set f                                                                                                          |                                                     |                                                  |  |  |  |

|------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------|--|--|--|

| Syntax:                            | BSF f, b {                                                                                          | BSF f, b {,a}                                                                                                      |                                                     |                                                  |  |  |  |

| Operands:                          | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$                  | $0 \le b \le 7$                                                                                                    |                                                     |                                                  |  |  |  |

| Operation:                         | $1 \rightarrow \text{f}$                                                                            |                                                                                                                    |                                                     |                                                  |  |  |  |