Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART, USB                            |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 65                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f86j50-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 64/80-Pin High-Performance, 1-Mbit Flash USB Microcontrollers with nanoWatt Technology

#### **Universal Serial Bus Features:**

- USB V2.0 Compliant SIE

- Low Speed (1.5 Mb/s) and Full Speed (12 Mb/s)

- Supports Control, Interrupt, Isochronous and Bulk Transfers

- Supports up to 32 Endpoints (16 bidirectional)

- 3.9-Kbyte Dual Access RAM for USB

- On-Chip USB Transceiver

#### Flexible Oscillator Structure:

- High-Precision PLL for USB

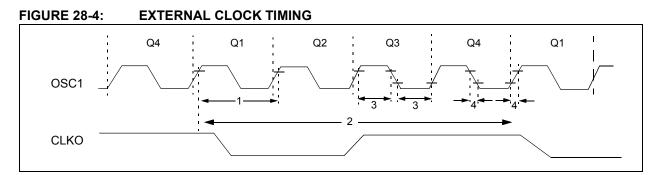

- Two External Clock modes, up to 48 MHz

- Internal 31 kHz Oscillator, Tunable Internal Oscillator, 31 kHz to 8 MHz

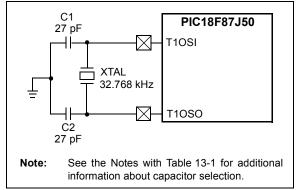

- Secondary Oscillator using Timer1 @ 32 kHz

- Fail-Safe Clock Monitor:

- Allows for safe shutdown if any clock stops

#### **Peripheral Highlights:**

- High-Current Sink/Source 25 mA/25mA (PORTB and PORTC)

- Four Programmable External Interrupts

- · Four Input Change Interrupts

- Two Capture/Compare/PWM (CCP) modules

- Three Enhanced Capture/Compare/PWM (ECCP) modules:

- One, two or four PWM outputs

- Selectable polarity

- Programmable dead time

- Auto-shutdown and auto-restart

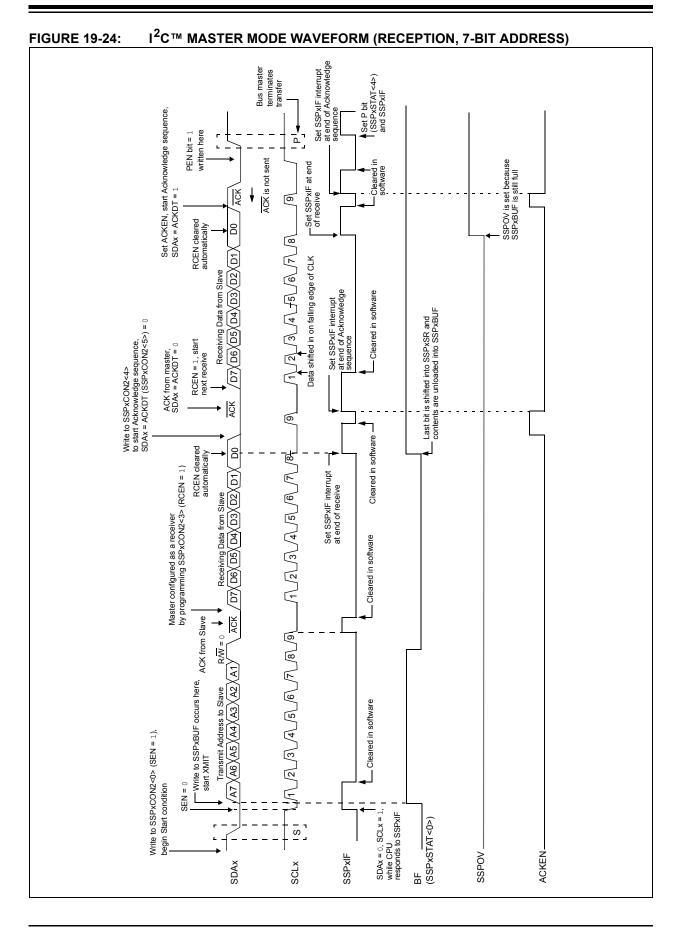

- Two Master Synchronous Serial Port (MSSP) modules supporting 3-Wire SPI (all 4 modes) and I<sup>2</sup>C<sup>™</sup> Master and Slave modes

- 8-Bit Parallel Master Port/Enhanced Parallel Slave Port with 16 Address Lines

- Dual Analog Comparators with Input Multiplexing

#### Peripheral Highlights (continued):

- 10-Bit, up to 12-Channel Analog-to-Digital (A/D) Converter module:

- Auto-acquisition capability

- Conversion available during Sleep

- Two Enhanced USART modules:

- Supports RS-485, RS-232 and LIN 1.2

- Auto-wake-up on Start bit

- Auto-Baud Detect

## External Memory Bus (80-pin devices only):

- · Address Capability of up to 2 Mbytes

- · 8-Bit or 16-Bit Interface

- · 12-Bit, 16-Bit and 20-Bit Addressing modes

#### **Special Microcontroller Features:**

- 5.5V Tolerant Inputs (digital-only pins)

- · Low-Power, High-Speed CMOS Flash Technology

- C Compiler Optimized Architecture for Re-Entrant Code

- Power Management Features:

- Run: CPU on, peripherals on

- Idle: CPU off, peripherals on

- Sleep: CPU off, peripherals off

- · Priority Levels for Interrupts

- Self-Programmable under Software Control

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 131s

- Single-Supply In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- In-Circuit Debug (ICD) with 3 Breakpoints via Two Pins

- Operating Voltage Range of 2.0V to 3.6V

- On-Chip 2.5V Regulator

- Flash Program Memory of 10000 Erase/Write Cycles and 20-Year Data Retention

| Features                                 | PIC18F65J50                       | PIC18F66J50                                                                     | PIC18F66J55 | PIC18F67J50 |

|------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------|-------------|-------------|

| Operating Frequency                      | DC – 48 MHz                       | DC – 48 MHz                                                                     | DC – 48 MHz | DC – 48 MHz |

| Program Memory (Bytes)                   | 32K                               | 64K                                                                             | 96K         | 128K        |

| Program Memory (Instructions)            | 16384                             | 32768                                                                           | 49152       | 65536       |

| Data Memory (Bytes)                      | 3904                              | 3904                                                                            | 3904        | 3904        |

| Interrupt Sources                        |                                   | 3                                                                               | 60          |             |

| I/O Ports                                | Ports A, B, C, D, E, F, G         |                                                                                 |             |             |

| Timers                                   |                                   | 5                                                                               |             |             |

| Capture/Compare/PWM Modules              | 2                                 |                                                                                 |             |             |

| Enhanced Capture/<br>Compare/PWM Modules | 3                                 |                                                                                 |             |             |

| Serial Communications                    | MSSP (2), Enhanced USART (2), USB |                                                                                 |             |             |

| Parallel Communications (PMP)            |                                   | Y                                                                               | es          |             |

| 10-Bit Analog-to-Digital Module          |                                   | 8 Input (                                                                       | Channels    |             |

| Resets (and Delays)                      | POR, BOR, RES                     | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCLR, WDT (PWRT, OST) |             |             |

| Instruction Set                          | 75 Instru                         | 75 Instructions, 83 with Extended Instruction Set Enabled                       |             |             |

| Packages                                 |                                   | 64-Pin TQFP                                                                     |             |             |

#### TABLE 1-1: DEVICE FEATURES FOR THE PIC18F6XJ5X (64-PIN DEVICES)

#### TABLE 1-2: DEVICE FEATURES FOR THE PIC18F8XJ5X (80-PIN DEVICES)

| Features                                 | PIC18F85J50                                               | PIC18F86J50                                                                     | PIC18F86J55      | PIC18F87J50 |  |

|------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------|------------------|-------------|--|

| Operating Frequency                      | DC – 48 MHz                                               | DC – 48 MHz                                                                     | DC – 48 MHz      | DC – 48 MHz |  |

| Program Memory (Bytes)                   | 32K                                                       | 64K                                                                             | 96K              | 128K        |  |

| Program Memory (Instructions)            | 16384                                                     | 32768                                                                           | 49152            | 65536       |  |

| Data Memory (Bytes)                      | 3904                                                      | 3904                                                                            | 3904             | 3904        |  |

| Interrupt Sources                        |                                                           |                                                                                 | 60               |             |  |

| I/O Ports                                |                                                           | Ports A, B, C,                                                                  | D, E, F, G, H, J |             |  |

| Timers                                   |                                                           | 5                                                                               |                  |             |  |

| Capture/Compare/PWM Modules              |                                                           | 2                                                                               |                  |             |  |

| Enhanced Capture/<br>Compare/PWM Modules | 3                                                         |                                                                                 |                  |             |  |

| Serial Communications                    | MSSP (2), Enhanced USART (2), USB                         |                                                                                 |                  |             |  |

| Parallel Communications (PMP)            |                                                           | Y                                                                               | es               |             |  |

| 10-Bit Analog-to-Digital Module          |                                                           | 12 Input Channels                                                               |                  |             |  |

| Resets (and Delays)                      | POR, BOR, RES                                             | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCLR, WDT (PWRT, OST) |                  |             |  |

| Instruction Set                          | 75 Instructions, 83 with Extended Instruction Set Enabled |                                                                                 |                  |             |  |

| Packages                                 |                                                           | 80-Pin TQFP                                                                     |                  |             |  |

| Pin Number                                                  | Fill Buller Description                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 64-TQFP                                                     | Туре                                                                      | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|                                                             |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PORTD is a bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 58                                                          |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                                             | I/O                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Digital I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                                                             | I/O                                                                       | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Parallel Master Port data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 55                                                          |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                                             | I/O                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Digital I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                                                             | I/O                                                                       | IIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Parallel Master Port data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 54                                                          |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                                             | -                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Digital I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                                                             | 1/0                                                                       | IIL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Parallel Master Port data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 53                                                          |                                                                           | OT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                                             |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Digital I/O.<br>Parallel Master Port data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 50                                                          | 1/0                                                                       | 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 52                                                          | 1/0                                                                       | ет                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Digital I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                                                             | -                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Parallel Master Port data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                                             | 0                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SPI data out.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 51                                                          |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 01                                                          | I/O                                                                       | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Digital I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                                                             | I/O                                                                       | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Parallel Master Port data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                                             | I                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SPI data in.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                                                             | I/O                                                                       | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I <sup>2</sup> C™ data I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 50                                                          |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                                             | -                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Digital I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                                                             |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Parallel Master Port data.<br>Synchronous serial clock input/output for SPI mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                                                             |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Synchronous serial clock input/output for I <sup>2</sup> C mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 49                                                          |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|                                                             | I/O                                                                       | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Digital I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                                                             | I/O                                                                       | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Parallel Master Port data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                                                             | Ι                                                                         | TTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SPI slave select input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                                             |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CMOS = CMOS compatible input or output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Trigger input w                                             | Analog = Analog input                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |