Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 65                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f86j50t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, PIC<sup>32</sup> logo, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC18F65J50 PIC18F85J50

- PIC18F66J50 PIC18F86J50

- PIC18F66J55

PIC18F86J55

- PIC18F67J50 PIC18F87J50

This family introduces a new line of low-voltage USB microcontrollers with the main traditional advantage of all PIC18 microcontrollers – namely, high computational performance and a rich feature set – at an extremely competitive price point. These features make the PIC18F87J10 family a logical choice for many high-performance applications, where cost is a primary consideration.

### 1.1 Core Features

### 1.1.1 nanoWatt TECHNOLOGY

All of the devices in the PIC18F87J10 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal RC oscillator, power consumption during code execution can be reduced by as much as 90%.

- **Multiple Idle Modes:** The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements.

- On-the-Fly Mode Switching: The power-managed modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application's software design.

### 1.1.2 UNIVERSAL SERIAL BUS (USB)

Devices in the PIC18F87J10 family incorporate a fully-featured Universal Serial Bus communications module with a built-in transceiver that is compliant with the USB Specification Revision 2.0. The module supports both low-speed and full-speed communication for all supported data transfer types.

## 1.1.3 OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F87J10 family offer five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes, using crystals or ceramic resonators.

- Two External Clock modes, offering the option of a divide-by-4 clock output.

- An internal oscillator block which provides an 8 MHz clock and an INTRC source (approximately 31 kHz, stable over temperature and VDD), as well as a range of 6 user-selectable clock frequencies, between 125 kHz to 4 MHz, for a total of 8 clock frequencies. This option frees an oscillator pin for use as an additional general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier, available to the high-speed crystal, external oscillator and internal oscillator, providing a clock speed up to 48 MHz.

- Dual clock operation, allowing the USB module to run from a high-frequency oscillator while the rest of the microcontroller is clocked at a different frequency.

The internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the internal oscillator. If a clock failure occurs, the controller is switched to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or wake-up from Sleep mode, until the primary clock source is available.

### 1.1.4 EXPANDED MEMORY

The PIC18F87J10 family provides ample room for application code, from 32 Kbytes to 128 Kbytes of code space. The Flash cells for program memory are rated to last in excess of 10000 erase/write cycles. Data retention without refresh is conservatively estimated to be greater than 20 years.

The Flash program memory is readable and writable during normal operation. The PIC18F87J10 family also provides plenty of room for dynamic application data with up to 3904 bytes of data RAM.

| Din Norra                                                                         | Pin Number       | Pin                    | Buffer              | Decemintion                                                                                                                                                                        |

|-----------------------------------------------------------------------------------|------------------|------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                          | 80-TQFP          | Туре                   | Туре                | Description                                                                                                                                                                        |

|                                                                                   |                  |                        |                     | PORTE is a bidirectional I/O port.                                                                                                                                                 |

| RE0/AD8/PMRD/P2D<br>RE0<br>AD8<br>PMRD <sup>(6)</sup><br>P2D                      | 4                | I/O<br>I/O<br>I/O<br>O | ST<br>TTL<br>—      | Digital I/O.<br>External memory address/data 8.<br>Parallel Master Port read strobe.<br>ECCP2 PWM output D.                                                                        |

| RE1/AD9/PMWR/P2C<br>RE1<br>AD9<br>PMWR <sup>(6)</sup><br>P2C                      | 3                | I/O<br>I/O<br>I/O<br>O | ST<br>TTL<br>—      | Digital I/O.<br>External memory address/data 9.<br>Parallel Master Port write strobe.<br>ECCP2 PWM output C.                                                                       |

| RE2/AD10/PMBE/P2B<br>RE2<br>AD10<br>PMBE <sup>(6)</sup><br>P2B                    | 78               | I/O<br>I/O<br>O<br>O   | ST<br>TTL<br>—      | Digital I/O.<br>External memory address/data 10.<br>Parallel Master Port byte enable.<br>ECCP2 PWM output B.                                                                       |

| RE3/AD11/PMA13/<br>P3C/REFO<br>RE3<br>AD11<br>PMA13<br>P3C <sup>(3)</sup><br>REFO | 77               | I/O<br>I/O<br>O<br>O   | ST<br>TTL<br>—<br>— | Digital I/O.<br>External memory address/data 11.<br>Parallel Master Port address.<br>ECCP3 PWM output C.<br>Reference Clock out.                                                   |

| RE4/AD12/PMA12/P3B<br>RE4<br>AD12<br>PMA12<br>P3B <sup>(3)</sup>                  | 76               | I/O<br>I/O<br>O        | ST<br>TTL<br>—      | Digital I/O.<br>External memory address/data 12.<br>Parallel Master Port address.<br>ECCP3 PWM output B.                                                                           |

| RE5/AD13/PMA11/P1C<br>RE5<br>AD13<br>PMA11<br>P1C <sup>(3)</sup>                  | 75               | I/O<br>I/O<br>O        | ST<br>TTL<br>—      | Digital I/O.<br>External memory address/data 13.<br>Parallel Master Port address.<br>ECCP1 PWM output C.                                                                           |

| I = Input<br>P = Power                                                            | tt Trigger input | with CN                |                     | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)<br>2MX Configuration bit is cleared (Extended Microcontroller |

### TABLE 1-4: PIC18F8XJ5X PINOUT I/O DESCRIPTIONS (CONTINUED)

2: Default assignment for ECCP2/P2A for all devices in all operating modes (CCP2MX is set).

3: Default assignments for P1B/P1C/P3B/P3C (ECCPMX Configuration bit is set).

4: Alternate assignment for ECCP2/P2A when CCP2MX is cleared (Microcontroller mode).

5: Alternate assignments for P1B/P1C/P3B/P3C (ECCPMX Configuration bit is cleared).

**6:** Pin placement when PMPMX = 1.

**7:** Pin placement when PMPMX = 0.

8: RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.

## 3.0 POWER-MANAGED MODES

The PIC18F87J10 family devices provide the ability to manage power consumption by simply managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. For the sake of managing power in an application, there are three primary modes of operation:

- Run mode

- Idle mode

- · Sleep mode

These modes define which portions of the device are clocked and at what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block); the Sleep mode does not use a clock source.

The power-managed modes include several power-saving features offered on previous PIC<sup>®</sup> devices. One is the clock switching feature, offered in other PIC18 devices, allowing the controller to use the Timer1 oscillator in place of the primary oscillator. Also included is the Sleep mode, offered by all PIC devices, where all device clocks are stopped.

### 3.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions: if the CPU is to be clocked or not and which clock source is to be used. The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS1:SCS0 bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 3-1.

### 3.1.1 CLOCK SOURCES

The SCS1:SCS0 bits allow the selection of one of three clock sources for power-managed modes. They are:

- The primary clock source, as defined by the FOSC2:FOSC0 Configuration bits

- The Timer1 clock (provided by the secondary oscillator)

- The postscaled internal clock (derived from the internal oscillator block)

### 3.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS1:SCS0 bits select the clock source and determine which Run or Idle mode is to be used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These are discussed in **Section 3.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| Mada     | OSC                  | CON<7,1:0> | Module ClockingCPUPeripherals |         | Available Cleak and Casillater Source                                                          |  |  |  |  |

|----------|----------------------|------------|-------------------------------|---------|------------------------------------------------------------------------------------------------|--|--|--|--|

| Mode     | IDLEN <sup>(1)</sup> | SCS1:SCS0  |                               |         | Available Clock and Oscillator Source                                                          |  |  |  |  |

| Sleep    | 0                    | N/A        | Off                           | Off     | None – All clocks are disabled                                                                 |  |  |  |  |

| PRI_RUN  | N/A                  | 00         | Clocked                       | Clocked | Primary clock source (defined by FOSC2:FOSC0);<br>this is the normal full-power execution mode |  |  |  |  |

| SEC_RUN  | N/A                  | 01         | Clocked                       | Clocked | Secondary – Timer1 oscillator                                                                  |  |  |  |  |

| RC_RUN   | N/A                  | 11         | Clocked                       | Clocked | Postscaled internal clock                                                                      |  |  |  |  |

| PRI_IDLE | 1                    | 00         | Off                           | Clocked | Primary clock source (defined by FOSC2:FOSC0)                                                  |  |  |  |  |

| SEC_IDLE | 1                    | 01         | Off                           | Clocked | Secondary – Timer1 oscillator                                                                  |  |  |  |  |

| RC_IDLE  | 1                    | 11         | Off                           | Clocked | Postscaled internal clock                                                                      |  |  |  |  |

TABLE 3-1: POWER-MANAGED MODES

**Note 1:** IDLEN reflects its value when the **SLEEP** instruction is executed.

NOTES:

| TABLE 5-5: REGISTER FILE SUMMARY (PIC18F87J50 FAMIL) | () | (CONTINUED) |

|------------------------------------------------------|----|-------------|

|------------------------------------------------------|----|-------------|

| File Name | Bit 7                                      | Bit 6         | Bit 5          | Bit 4   | Bit 3    | Bit 2   | Bit 1  | Bit 0   | Value on<br>POR, BOR | Details<br>on<br>Page: |

|-----------|--------------------------------------------|---------------|----------------|---------|----------|---------|--------|---------|----------------------|------------------------|

| UEP7      | —                                          | —             | —              | EPHSHK  | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 66, 317                |

| UEP6      | —                                          | _             | _              | EPHSHK  | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 66, 317                |

| UEP5      | —                                          | —             | —              | EPHSHK  | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 66, 317                |

| UEP4      | —                                          | —             | —              | EPHSHK  | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 66, 317                |

| UEP3      | —                                          | —             | —              | EPHSHK  | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 66, 317                |

| UEP2      | —                                          | —             | —              | EPHSHK  | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 66, 317                |

| UEP1      | —                                          | _             | _              | EPHSHK  | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 66, 317                |

| UEP0      | —                                          | —             | —              | EPHSHK  | EPCONDIS | EPOUTEN | EPINEN | EPSTALL | 0 0000               | 66, 317                |

| PMCONH    | PMPEN                                      | —             | PSIDL          | ADRMUX1 | ADRMUX0  | PTBEEN  | PTWREN | PTRDEN  | 0-00 0000            | 66, 168                |

| PMCONL    | CSF1                                       | CSF0          | ALP            | CS2P    | CS1P     | BEP     | WRSP   | RDSP    | 0000 0000            | 67, 169                |

| PMMODEH   | BUSY                                       | IRQM1         | IRQM0          | INCM1   | INCM0    | MODE16  | MODE1  | MODE0   | 0000 0000            | 67, 170                |

| PMMODEL   | WAITB1                                     | WAITB0        | WAITM3         | WAITM2  | WAITM1   | WAITM0  | WAITE1 | WAITE0  | 0000 0000            | 67, 171                |

| PMDOUT2H  | Parallel Port                              | Out Data High | Byte (Buffer   | 3)      |          |         |        |         | 0000 0000            | 67, 174                |

| PMDOUT2L  | Parallel Port                              | Out Data Low  | Byte (Buffer 2 | 2)      |          |         |        |         | 0000 0000            | 67, 174                |

| PMDIN2H   | Parallel Port In Data High Byte (Buffer 3) |               |                |         |          |         |        |         | 0000 0000            | 67, 174                |

| PMDIN2L   | Parallel Port                              | In Data Low B | yte (Buffer 2) |         |          |         |        |         | 0000 0000            | 67, 174                |

| PMEH      | PTEN15                                     | PTEN14        | PTEN13         | PTEN12  | PTEN11   | PTEN10  | PTEN9  | PTEN8   | 0000 0000            | 67, 171                |

| PMEL      | PTEN7                                      | PTEN6         | PTEN5          | PTEN4   | PTEN3    | PTEN2   | PTEN1  | PTEN0   | 0000 0000            | 67, 172                |

| PMSTATH   | IBF                                        | IBOV          | _              | _       | IB3F     | IB2F    | IB1F   | IB0F    | 00 0000              | 67, 172                |

| PMSTATL   | OBE                                        | OBUF          | _              | _       | OB3E     | OB2E    | OB1E   | OB0E    | 10 1111              | 67, 173                |

Legend: Note 1

d: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition. Bold indicates shared-access SFRs.

1: Bit 21 of the PC is only available in Serial Programming modes.

2: Default (legacy) SFR at this address, available when WDTCON<4> = 0.

3: Configuration SFR, overlaps with default SFR at this address; available only when WDTCON<4> = 1.

4: Reset value is '0' when Two-Speed Start-up is enabled and '1' if disabled.

5: The SSPxMSK registers are only accessible when SSPxCON2<3:0> = 1001.

6: Alternate names and definitions for these bits when the MSSP module is operating in I<sup>2</sup>C™ Slave mode. See Section 19.4.3.2 "Address Masking Modes" for details

7: These bits and/or registers are only available in 80-pin devices; otherwise, they are unimplemented and read as '0'. Reset values are shown for 80-pin devices.

8: The PMADDRH/PMDOUT1H and PMADDRL/PMDOUT1L register pairs share the physical registers and addresses, but have different functions determined by the module's operating mode. See Section 11.1.2 "Data Registers" for more information.

| R/W-1                  | R/W-1                                                           | R/W-1                              | R/W-1            | R/W-1                             | R/W-1         | R/W-1           | R/W-1 |  |

|------------------------|-----------------------------------------------------------------|------------------------------------|------------------|-----------------------------------|---------------|-----------------|-------|--|

| RBPU                   | INTEDG0                                                         | INTEDG1                            | INTEDG2          | INTEDG3                           | TMR0IP        | INT3IP          | RBIP  |  |

| bit 7                  |                                                                 |                                    |                  |                                   |               |                 | bit   |  |

|                        |                                                                 |                                    |                  |                                   |               |                 |       |  |

| Legend:<br>R = Readabl | le hit                                                          | W = Writable                       | hit              | U = Unimplem                      | ented hit rea | d as 'O'        |       |  |

| -n = Value at          |                                                                 | '1' = Bit is set                   | υn               | $0^{\circ} = \text{Bit is clear}$ |               | x = Bit is unkn | own   |  |

|                        |                                                                 | 1 - Dit 13 301                     |                  |                                   |               |                 |       |  |

| bit 7                  | <b>RBPU</b> : PORT                                              | B Pull-up Enal                     | ole bit          |                                   |               |                 |       |  |

|                        | 1 = All PORT                                                    | B pull-ups are                     | disabled         |                                   |               |                 |       |  |

|                        | 0 = PORTB p                                                     | oull-ups are ena                   | abled by individ | lual port latch v                 | alues         |                 |       |  |

| bit 6                  | INTEDG0: Ex                                                     | ternal Interrupt                   | 0 Edge Select    | t bit                             |               |                 |       |  |

|                        |                                                                 | on rising edge                     |                  |                                   |               |                 |       |  |

|                        | •                                                               | on falling edge                    |                  |                                   |               |                 |       |  |

| bit 5                  |                                                                 | ternal Interrupt                   | 1 Edge Select    | t bit                             |               |                 |       |  |

|                        |                                                                 | on rising edge<br>on falling edge  |                  |                                   |               |                 |       |  |

| bit 4                  |                                                                 |                                    | 2 Edge Solod     | t hit                             |               |                 |       |  |

| DIL 4                  |                                                                 | ternal Interrupt<br>on rising edge | z Euge Seleci    |                                   |               |                 |       |  |

|                        |                                                                 | on falling edge                    |                  |                                   |               |                 |       |  |

| bit 3                  | INTEDG3: Ex                                                     | ternal Interrupt                   | 3 Edge Select    | t bit                             |               |                 |       |  |

|                        | 1 = Interrupt                                                   | on rising edge                     |                  |                                   |               |                 |       |  |

|                        | 0 = Interrupt                                                   | on falling edge                    |                  |                                   |               |                 |       |  |

| bit 2                  | TMR0IP: TMF                                                     | R0 Overflow Int                    | errupt Priority  | bit                               |               |                 |       |  |

|                        | 1 = High prio                                                   | ,                                  |                  |                                   |               |                 |       |  |

|                        | 0 = Low prior                                                   | 5                                  |                  |                                   |               |                 |       |  |

| bit 1                  |                                                                 | External Interr                    | upt Priority bit |                                   |               |                 |       |  |

|                        | <ul> <li>1 = High priority</li> <li>0 = Low priority</li> </ul> |                                    |                  |                                   |               |                 |       |  |

| bit 0                  | <b>RBIP:</b> RB Port Change Interrupt Priority bit              |                                    |                  |                                   |               |                 |       |  |

|                        | 1 = High priority                                               |                                    |                  |                                   |               |                 |       |  |

|                        | 0 = Low prior                                                   | ity                                |                  |                                   |               |                 |       |  |

|                        |                                                                 |                                    |                  |                                   |               |                 |       |  |

| Note: In               |                                                                 |                                    |                  |                                   |               |                 |       |  |

### REGISTER 9-2: INTCON2: INTERRUPT CONTROL REGISTER 2

**Note:** Interrupt flag bits are set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

## 9.3 PIE Registers

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Enable registers (PIE1, PIE2, PIE3). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

### REGISTER 9-7: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|--------|--------|--------|--------|

| PMPIE | ADIE  | RC1IE | TX1IE | SSP1IE | CCP1IE | TMR2IE | TMR1IE |

| bit 7 |       |       |       |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7 | PMPIE: Parallel Master Port Read/Write Interrupt Enable bit                |

|-------|----------------------------------------------------------------------------|

|       | 1 = Enables the PM read/write interrupt                                    |

|       | 0 = Disables the PM read/write interrupt                                   |

| bit 6 | ADIE: A/D Converter Interrupt Enable bit                                   |

|       | 1 = Enables the A/D interrupt                                              |

|       | 0 = Disables the A/D interrupt                                             |

| bit 5 | RC1IE: EUSART1 Receive Interrupt Enable bit                                |

|       | 1 = Enables the EUSART1 receive interrupt                                  |

|       | 0 = Disables the EUSART1 receive interrupt                                 |

| bit 4 | TX1IE: EUSART1 Transmit Interrupt Enable bit                               |

|       | 1 = Enables the EUSART1 transmit interrupt                                 |

|       | 0 = Disables the EUSART1 transmit interrupt                                |

| bit 3 | SSP1IE: Master Synchronous Serial Port Interrupt Enable bit (MSSP1 module) |

|       | 1 = Enables the MSSP1 interrupt                                            |

|       | 0 = Disables the MSSP1 interrupt                                           |

| bit 2 | CCP1IE: ECCP1 Interrupt Enable bit                                         |

|       | 1 = Enables the ECCP1 interrupt                                            |

|       | 0 = Disables the ECCP1 interrupt                                           |

| bit 1 | TMR2IE: TMR2 to PR2 Match Interrupt Enable bit                             |

|       | 1 = Enables the TMR2 to PR2 match interrupt                                |

|       | 0 = Disables the TMR2 to PR2 match interrupt                               |

| bit 0 | TMR1IE: TMR1 Overflow Interrupt Enable bit                                 |

|       | 1 = Enables the TMR1 overflow interrupt                                    |

|       | 0 = Disables the TMR1 overflow interrupt                                   |

|       |                                                                            |

## 10.3 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISB. All pins on PORTB are digital only and tolerate voltages up to 5.5V.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit, RBPU (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of the PORTB pins (RB7:RB4) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from power-managed modes. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB (except with the MOVFF (ANY), PORTB instruction). This will end the mismatch condition.

- b) Clear flag bit, RBIF.

A mismatch condition will continue to set flag bit, RBIF. Reading PORTB will end the mismatch condition and allow flag bit, RBIF, to be cleared. The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

For 80-pin devices, RB3 can be configured as the alternate peripheral pin for the ECCP2 module and Enhanced PWM output 2A by clearing the CCP2MX Configuration bit. This applies only to 80-pin devices operating in Extended Microcontroller mode. If the device is in Microcontroller mode, the alternate assignment for ECCP2 is RE7. As with other ECCP2 configurations, the user must ensure that the TRISB<3> bit is set appropriately for the intended operation. Ports, RB1, RB2, RB3, RB4 and RB5, are multiplexed with the Parallel Master Port address.

EXAMPLE 10-2: INITIALIZING PORTB

| CLRF PORTB  | ; Initialize PORTB by<br>; clearing output |

|-------------|--------------------------------------------|

|             | ; crearing output                          |

|             | ; data latches                             |

| CLRF LATB   | ; Alternate method to clear                |

|             | ; output data latches                      |

| MOVLW 0CFh  | ; Value used to initialize                 |

|             | ; data direction                           |

| MOVWF TRISB | ; Set RB<3:0> as inputs                    |

|             | ; RB<5:4> as outputs                       |

|             | ; RB<7:6> as inputs                        |

|             |                                            |

## 10.9 PORTH, LATH and TRISH Registers

| Note: | PORTH    | is | available | only | on | 80-pin |

|-------|----------|----|-----------|------|----|--------|

|       | devices. |    |           |      |    |        |

PORTH is an 8-bit wide, bidirectional I/O port. PORTH pins <3:0> are digital only and tolerate voltages up to 5.5V.

All pins on PORTH are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

When the external memory interface is enabled, four of the PORTH pins function as the high-order address lines for the interface. The address output from the interface takes priority over other digital I/O. The corresponding TRISH bits are also overridden. PORTH pins, RH4 through RH7, are multiplexed with analog converter inputs. The operation of these pins as analog inputs is selected by clearing or setting the corresponding bits in the ANCON1 register. RH3 to RH6 is multiplexed with Parallel Master Port and RH4 to RH6 are multiplexed as comparator pins. PORTH can also be configured as the alternate Enhanced PWM output channels B and C for the ECCP1 and ECCP3 modules. This is done by clearing the ECCPMX Configuration bit.

#### EXAMPLE 10-8: INITIALIZING PORTH

| CLRF  | PORTH ;        | Initialize PORTH by      |

|-------|----------------|--------------------------|

|       | ;              | clearing output          |

|       | ;              | data latches             |

| CLRF  | LATH ;         | Alternate method to      |

|       | ;              | clear output latches     |

| BSF   | WDTCON, ADSHR; | Enable write/read to     |

|       | ;              | the shared SFR           |

| MOVLW | FOh ;          | Configure PORTH as       |

| MOVWF | ANCON1 ;       | digital I/O              |

| BCF   | WDTCON, ADSHR; | Disable write/read to    |

|       | ;              | the shared SFR           |

| MOVLW | OCFh ;         | Value used to initialize |

|       | ;              | data direction           |

| MOVWF | TRISH ;        | Set RH3:RH0 as inputs    |

|       | ;              | RH5:RH4 as outputs       |

|       | ;              | RH7:RH6 as inputs        |

|       |                |                          |

## REGISTER 19-6: SSPxCON2: MSSPx CONTROL REGISTER 2 (I<sup>2</sup>C<sup>™</sup> SLAVE MODE)

|                                   | -n = Value at POR |        |        | '0' = Bit is clea                  | ared   | x = Bit is unknown |       |  |

|-----------------------------------|-------------------|--------|--------|------------------------------------|--------|--------------------|-------|--|

| R = Readable bit W = Writable bit |                   |        |        | U = Unimplemented bit, read as '0' |        |                    |       |  |

| Legend:                           |                   |        |        |                                    |        |                    |       |  |

| bit 7                             |                   |        |        |                                    |        |                    | bit 0 |  |

| GCEN                              | ACKSTAT           | ADMSK5 | ADMSK4 | ADMSK3                             | ADMSK2 | ADMSK1             | SEN   |  |

| R/W-0                             | R/W-0             | R/W-0  | R/W-0  | R/W-0                              | R/W-0  | R/W-0              | R/W-0 |  |

|         | <ul> <li>1 = Enables interrupt when a general call address (0000h) is received in the SSPxSR</li> <li>0 = General call address disabled</li> </ul>        |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | ACKSTAT: Acknowledge Status bit                                                                                                                           |

|         | Unused in Slave mode.                                                                                                                                     |

| bit 5-2 | ADMSK5:ADMSK2: Slave Address Mask Select bits (5-Bit Address Masking)                                                                                     |

|         | <ul><li>1 = Masking of corresponding bits of SSPxADD enabled</li><li>0 = Masking of corresponding bits of SSPxADD disabled</li></ul>                      |

| bit 1   | ADMSK1: Slave Address Least Significant bit(s) Mask Select bit                                                                                            |

|         | <u>In 7-Bit Addressing mode:</u><br>1 = Masking of SSPxADD<1> only enabled<br>0 = Masking of SSPxADD<1> only disabled                                     |

|         | <u>In 10-Bit Addressing mode:</u><br>1 = Masking of SSPxADD<1:0> enabled<br>0 = Masking of SSPxADD<1:0> disabled                                          |

| bit 0   | SEN: Start Condition Enable/Stretch Enable bit <sup>(1)</sup>                                                                                             |

|         | <ul> <li>1 = Clock stretching is enabled for both slave transmit and slave receive (stretch enabled)</li> <li>0 = Clock stretching is disabled</li> </ul> |

|         |                                                                                                                                                           |

**Note 1:** If the I<sup>2</sup>C module is active, these bits may not be set (no spooling) and the SSPxBUF may not be written (or writes to the SSPxBUF are disabled).

| REGISTER 19-7: | SSPxMSK: $I^2C^{\text{TM}}$ SLAVE ADDRESS MASK REGISTER (7-BIT MASKING MODE) <sup>(1)</sup> |

|----------------|---------------------------------------------------------------------------------------------|

|----------------|---------------------------------------------------------------------------------------------|

| R/W-1               |

|-------|-------|-------|-------|-------|-------|-------|---------------------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0 <sup>(2)</sup> |

| bit 7 | •     |       |       |       |       |       | bit 0               |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 MSK7:MSK0: Slave Address Mask Select bit

- 1 = Masking of corresponding bit of SSPxADD enabled

- 0 = Masking of corresponding bit of SSPxADD disabled

- Note 1: This register shares the same SFR address as SSPxADD, and is only addressable in select MSSP operating modes. See Section 19.4.3.4 "7-Bit Address Masking Mode" for more details.

- 2: MSK0 is not used as a mask bit in 7-bit addressing.

|       |                       | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                       |            |                             |                       |            |                             |                       |            |                             |  |  |  |

|-------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|

| BAUD  | Fosc = 40.000 MHz     |                               |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |  |  |  |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |

| 0.3   | 0.300                 | 0.00                          | 8332                        | 0.300                 | 0.02       | 4165                        | 0.300                 | 0.02       | 2082                        | 0.300                 | -0.04      | 1665                        |  |  |  |

| 1.2   | 1.200                 | 0.02                          | 2082                        | 1.200                 | -0.03      | 1041                        | 1.200                 | -0.03      | 520                         | 1.201                 | -0.16      | 415                         |  |  |  |

| 2.4   | 2.402                 | 0.06                          | 1040                        | 2.399                 | -0.03      | 520                         | 2.404                 | 0.16       | 259                         | 2.403                 | -0.16      | 207                         |  |  |  |

| 9.6   | 9.615                 | 0.16                          | 259                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16       | 64                          | 9.615                 | -0.16      | 51                          |  |  |  |

| 19.2  | 19.231                | 0.16                          | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73       | 31                          | 19.230                | -0.16      | 25                          |  |  |  |

| 57.6  | 58.140                | 0.94                          | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36      | 10                          | 55.555                | 3.55       | 8                           |  |  |  |

| 115.2 | 113.636               | -1.36                         | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51       | 4                           |                       | —          | —                           |  |  |  |

## TABLE 20-3: BAUD RATES FOR ASYNCHRONOUS MODES (CONTINUED)

|              |                       | SYNC = 0, BRGH = 0, BRG16 = 1 |                             |                       |            |                             |                       |            |                             |  |  |  |  |

|--------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|--|

| BAUD<br>RATE | Foso                  | c = 4.000                     | MHz                         | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |  |  |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |

| 0.3          | 0.300                 | 0.04                          | 832                         | 0.300                 | -0.16      | 415                         | 0.300                 | -0.16      | 207                         |  |  |  |  |

| 1.2          | 1.202                 | 0.16                          | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                          |  |  |  |  |

| 2.4          | 2.404                 | 0.16                          | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                          |  |  |  |  |

| 9.6          | 9.615                 | 0.16                          | 25                          | 9.615                 | -0.16      | 12                          | —                     | _          | _                           |  |  |  |  |

| 19.2         | 19.231                | 0.16                          | 12                          | —                     | _          | _                           | —                     | _          | _                           |  |  |  |  |

| 57.6         | 62.500                | 8.51                          | 3                           | —                     | _          | _                           | —                     | _          | _                           |  |  |  |  |

| 115.2        | 125.000               | 8.51                          | 1                           |                       | —          | _                           | _                     | —          | —                           |  |  |  |  |

|              |                       | SYNC = 0, BRGH = 1, BRG16 = 1 or SYNC = 1, BRG16 = 1 |                             |                       |                   |                             |                       |                   |                             |                       |                  |                             |  |  |

|--------------|-----------------------|------------------------------------------------------|-----------------------------|-----------------------|-------------------|-----------------------------|-----------------------|-------------------|-----------------------------|-----------------------|------------------|-----------------------------|--|--|

| BAUD<br>RATE | Fosc = 40.000 MHz     |                                                      |                             | Fosc                  | Fosc = 20.000 MHz |                             |                       | Fosc = 10.000 MHz |                             |                       | Fosc = 8.000 MHz |                             |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error                                           | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |  |

| 0.3          | 0.300                 | 0.00                                                 | 33332                       | 0.300                 | 0.00              | 16665                       | 0.300                 | 0.00              | 8332                        | 0.300                 | -0.01            | 6665                        |  |  |

| 1.2          | 1.200                 | 0.00                                                 | 8332                        | 1.200                 | 0.02              | 4165                        | 1.200                 | 0.02              | 2082                        | 1.200                 | -0.04            | 1665                        |  |  |

| 2.4          | 2.400                 | 0.02                                                 | 4165                        | 2.400                 | 0.02              | 2082                        | 2.402                 | 0.06              | 1040                        | 2.400                 | -0.04            | 832                         |  |  |

| 9.6          | 9.606                 | 0.06                                                 | 1040                        | 9.596                 | -0.03             | 520                         | 9.615                 | 0.16              | 259                         | 9.615                 | -0.16            | 207                         |  |  |

| 19.2         | 19.193                | -0.03                                                | 520                         | 19.231                | 0.16              | 259                         | 19.231                | 0.16              | 129                         | 19.230                | -0.16            | 103                         |  |  |

| 57.6         | 57.803                | 0.35                                                 | 172                         | 57.471                | -0.22             | 86                          | 58.140                | 0.94              | 42                          | 57.142                | 0.79             | 34                          |  |  |

| 115.2        | 114.943               | -0.22                                                | 86                          | 116.279               | 0.94              | 42                          | 113.636               | -1.36             | 21                          | 117.647               | -2.12            | 16                          |  |  |

|              |                       | SYN        | IC = 0, BR0                 | GH = 1, BI            | <b>RG16 =</b> 1 | or SYNC =                   | : 1, BRG1             | 6 = 1      |                             |  |

|--------------|-----------------------|------------|-----------------------------|-----------------------|-----------------|-----------------------------|-----------------------|------------|-----------------------------|--|

| BAUD<br>RATE | Fos                   | c = 4.000  | MHz                         | Fos                   | c = 2.000       | MHz                         | Fosc = 1.000 MHz      |            |                             |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error      | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 0.3          | 0.300                 | 0.01       | 3332                        | 0.300                 | -0.04           | 1665                        | 0.300                 | -0.04      | 832                         |  |

| 1.2          | 1.200                 | 0.04       | 832                         | 1.201                 | -0.16           | 415                         | 1.201                 | -0.16      | 207                         |  |

| 2.4          | 2.404                 | 0.16       | 415                         | 2.403                 | -0.16           | 207                         | 2.403                 | -0.16      | 103                         |  |

| 9.6          | 9.615                 | 0.16       | 103                         | 9.615                 | -0.16           | 51                          | 9.615                 | -0.16      | 25                          |  |

| 19.2         | 19.231                | 0.16       | 51                          | 19.230                | -0.16           | 25                          | 19.230                | -0.16      | 12                          |  |

| 57.6         | 58.824                | 2.12       | 16                          | 55.555                | 3.55            | 8                           | —                     | _          | —                           |  |

| 115.2        | 111.111               | -3.55      | 8                           | —                     | _               | —                           | —                     | _          | —                           |  |

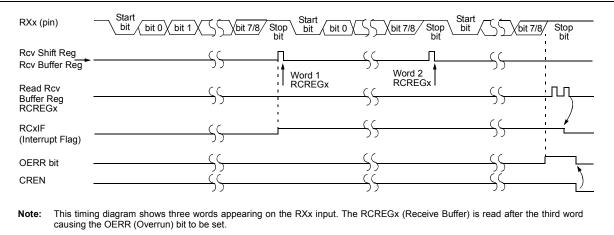

### FIGURE 20-7: ASYNCHRONOUS RECEPTION

| Name     | Bit 7    | Bit 6       | Bit 5       | Bit 4        | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|----------|----------|-------------|-------------|--------------|--------|--------|--------|--------|-----------------------------|

| INTCON   | GIE/GIEH | PEIE/GIEL   | TMR0IE      | INT0IE       | RBIE   | TMR0IF | INT0IF | RBIF   | 61                          |

| PIR1     | PMPIF    | ADIF        | RC1IF       | TX1IF        | SSP1IF | CCP1IF | TMR2IF | TMR1IF | 64                          |

| PIE1     | PMPIE    | ADIE        | RC1IE       | TX1IE        | SSP1IE | CCP1IE | TMR2IE | TMR1IE | 64                          |

| IPR1     | PMPIP    | ADIP        | RC1IP       | TX1IP        | SSP1IP | CCP1IP | TMR2IP | TMR1IP | 64                          |

| PIR3     | SSP2IF   | BCL2IF      | RC2IF       | TX2IF        | TMR4IF | CCP5IF | CCP4IF | CCP3IF | 64                          |

| PIE3     | SSP2IE   | BCL2IE      | RC2IE       | TX2IE        | TMR4IE | CCP5IE | CCP4IE | CCP3IE | 64                          |

| IPR3     | SSP2IP   | BCL2IP      | RC2IP       | TX2IP        | TMR4IP | CCP5IP | CCP4IP | CCP3IP | 64                          |

| RCSTAx   | SPEN     | RX9         | SREN        | CREN         | ADDEN  | FERR   | OERR   | RX9D   | 63                          |

| RCREGx   | EUSARTx  | Receive Reg | ister       |              |        |        |        |        | 63                          |

| TXSTAx   | CSRC     | TX9         | TXEN        | SYNC         | SENDB  | BRGH   | TRMT   | TX9D   | 63                          |

| BAUDCONx | ABDOVF   | RCIDL       | DTRXP       | SCKP         | BRG16  | —      | WUE    | ABDEN  | 65                          |

| SPBRGHx  | EUSARTx  | Baud Rate G | enerator Re | egister High | Byte   |        |        |        | 65                          |

| SPBRGx   | EUSARTx  | Baud Rate G | enerator Re | egister Low  | Byte   |        |        |        | 65                          |

|          |          |             |             |              |        |        |        |        |                             |

### TABLE 20-6: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: — = unimplemented locations read as '0'. Shaded cells are not used for asynchronous reception.

#### 20.2.4 AUTO-WAKE-UP ON SYNC BREAK CHARACTER

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper byte reception cannot be performed. The auto-wake-up feature allows the controller to wake-up due to activity on the RXx/DTx line while the EUSART is operating in Asynchronous mode.

The auto-wake-up feature is enabled by setting the WUE bit (BAUDCONx<1>). Once set, the typical receive sequence on RXx/DTx is disabled and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on

the RXx/DTx line. (This coincides with the start of a Sync Break or a Wake-up Signal character for the LIN protocol.)

Following a wake-up event, the module generates an RCxIF interrupt. The interrupt is generated synchronously to the Q clocks in normal operating modes (Figure 20-8) and asynchronously if the device is in Sleep mode (Figure 20-9). The interrupt condition is cleared by reading the RCREGx register.

The WUE bit is automatically cleared once a low-to-high transition is observed on the RXx line following the wake-up event. At this point, the EUSART module is in Idle mode and returns to normal operation. This signals to the user that the Sync Break event is over.

### 20.3 EUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTAx<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTAx<4>). In addition, enable bit, SPEN (RCSTAx<7>), is set in order to configure the TXx and RXx pins to CKx (clock) and DTx (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CKx line. Clock polarity is selected with the SCKP bit (BAUDCONx<4>). Setting SCKP sets the Idle state on CKx as high, while clearing the bit sets the Idle state as low. This option is provided to support Microwire devices with this module.

### 20.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 20-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREGx. The TXREGx register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREGx (if available).

Once the TXREGx register transfers the data to the TSR register (occurs in one TcY), the TXREGx is empty and the TXxIF flag bit is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXxIE. TXxIF is set regardless of the state of enable bit, TXxIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREGx register.

While flag bit, TXxIF, indicates the status of the TXREGx register, another bit, TRMT (TXSTAx<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user must poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TXxIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| വിമ <mark>ു</mark> മായം വിമുമായം വിമുമായം വിമുമായം വിമുമായം വിമുമായം പ്രദേശം വിമുമായം വിമുമായം പിമുമായം പിരുമായം പിരുമായം പിമുമായം പ | Q4         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| RC7/RX1/DT1                                                                                                                                                                                                                                                                 | $\exists$  |

|                                                                                                                                                                                                                                                                             | _          |

| RC6/TX1/CK1 pin ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' '                                                                                                                                                                                                                       | _          |

| Write to                                                                                                                                                                                                                                                                    | _;         |

| TX1IF bit                                                                                                                                                                                                                                                                   |            |

| TRMT bit                                                                                                                                                                                                                                                                    |            |

| TXEN bit <u>'1'</u>                                                                                                                                                                                                                                                         | <u>'1'</u> |

| Note: Sync Master mode, SPBRGx = 0, continuous transmission of two 8-bit words. This example is equally applicable to EUSAF (RG1/TX2/CK2 and RG2/RX2/DT2).                                                                                                                  | :T2        |

FIGURE 20-11: SYNCHRONOUS TRANSMISSION

### 22.4.1.3 BDnSTAT Register (SIE Mode)

When the BD and its buffer are owned by the SIE, most of the bits in BDnSTAT take on a different meaning. The configuration is shown in Register 22-6. Once UOWN is set, any data or control settings previously written there by the user will be overwritten with data from the SIE.

The BDnSTAT register is updated by the SIE with the token Packet Identifier (PID) which is stored in BDnSTAT<5:3>. The transfer count in the corresponding BDnCNT register is updated. Values that overflow the 8-bit register carry over to the two most significant digits of the count, stored in BDnSTAT<1:0>.

### 22.4.2 BD BYTE COUNT

The byte count represents the total number of bytes that will be transmitted during an IN transfer. After an IN transfer, the SIE will return the number of bytes sent to the host.

For an OUT transfer, the byte count represents the maximum number of bytes that can be received and stored in USB RAM. After an OUT transfer, the SIE will return the actual number of bytes received. If the number of bytes received exceeds the corresponding byte count, the data packet will be rejected and a NAK handshake will be generated. When this happens, the byte count will not be updated.

The 10-bit byte count is distributed over two registers. The lower 8 bits of the count reside in the BDnCNT register. The upper two bits reside in BDnSTAT<1:0>. This represents a valid byte range of 0 to 1023.

### 22.4.3 BD ADDRESS VALIDATION

The BD Address register pair contains the starting RAM address location for the corresponding endpoint buffer. No mechanism is available in hardware to validate the BD address.

If the value of the BD address does not point to an address in the USB RAM, or if it points to an address within another endpoint's buffer, data is likely to be lost or overwritten. Similarly, overlapping a receive buffer (OUT endpoint) with a BD location in use can yield unexpected results. When developing USB applications, the user may want to consider the inclusion of software-based address validation in their code.

## REGISTER 22-6: BDnSTAT: BUFFER DESCRIPTOR n STATUS REGISTER (BD0STAT THROUGH BD63STAT), SIE MODE (DATA RETURNED BY THE SIDE TO THE MCU)

| R/W-x | U-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-------|-------|-------|-------|-------|-------|

| UOWN  | —   | PID3  | PID2  | PID1  | PID0  | BC9   | BC8   |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7   | <b>UOWN:</b> USB Own bit<br>1 = The SIE owns the BD and its corresponding buffer                                                                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | Reserved: Not written by the SIE                                                                                                                                                                                |

| bit 5-2 | <b>PID3:PID0:</b> Packet Identifier bits<br>The received token PID value of the last transfer (IN, OUT or SETUP transactions only).                                                                             |

| bit 1-0 | <b>BC9:BC8:</b> Byte Count 9 and 8 bits<br>These bits are updated by the SIE to reflect the actual number of bytes received on an OUT transfer<br>and the actual number of bytes transmitted on an IN transfer. |

| R/W-0      | R/W-0                                    | R/W-0                                       | R/W-1                         | R/W-1                                                              | R/W-1           | R/W-1              | R/W-1          |  |

|------------|------------------------------------------|---------------------------------------------|-------------------------------|--------------------------------------------------------------------|-----------------|--------------------|----------------|--|

| CON        | COE                                      | CPOL                                        | EVPOL1                        | EVPOL0                                                             | CREF            | CCH1               | CCH0           |  |

| bit 7      |                                          |                                             |                               |                                                                    |                 |                    | bit            |  |

| Legend:    |                                          |                                             |                               |                                                                    |                 |                    |                |  |

| R = Read   | able bit                                 | W = Writable                                | bit                           | U = Unimplen                                                       | nented bit, rea | d as '0'           |                |  |

| -n = Value | e at POR                                 | '1' = Bit is set '0' = Bit is cleared       |                               |                                                                    |                 | x = Bit is unknown |                |  |

| bit 7      | •                                        | rator Enable b                              | t                             |                                                                    |                 |                    |                |  |

|            | 1 = Compara<br>0 = Compara               | tor is enabled<br>tor is disabled           |                               |                                                                    |                 |                    |                |  |

| bit 6      | COE: Compa                               | rator Output E                              | nable bit                     |                                                                    |                 |                    |                |  |

|            |                                          | tor output is pro<br>tor output is int      | esent on the Ca<br>ernal only | xOUT pin                                                           |                 |                    |                |  |

| bit 5      | CPOL: Comp                               | CPOL: Comparator Output Polarity Select bit |                               |                                                                    |                 |                    |                |  |

|            | •                                        | tor output is inv<br>tor output is no       |                               |                                                                    |                 |                    |                |  |

| bit 4-3    |                                          | -                                           | Polarity Selec                |                                                                    |                 |                    |                |  |

|            | 10 = Interrupt<br>01 = Interrupt         | generation on                               | ly on low-to-hig              | f the output <sup>(1)</sup><br>w transition of<br>gh transition of |                 |                    |                |  |

| bit 2      |                                          | •                                           |                               | on-inverting in                                                    | out)            |                    |                |  |

|            | 1 = Non-inver                            | ting input conr                             |                               | I CVREF voltage                                                    | ,               |                    |                |  |

| bit 1-0    | CCH1:CCH0                                | Comparator C                                | hannel Select                 | bits                                                               |                 |                    |                |  |