Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART, USB                             |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 65                                                                          |

| Program Memory Size        | 96KB (48K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f86j55t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.1.5 EXTERNAL MEMORY BUS

In the event that 128 Kbytes of memory are inadequate for an application, the 80-pin members of the PIC18F87J10 family also implement an External Memory Bus (EMB). This allows the controller's internal program counter to address a memory space of up to 2 Mbytes, permitting a level of data access that few 8-bit devices can claim. This allows additional memory options, including:

- Using combinations of on-chip and external memory up to the 2-Mbyte limit

- Using external Flash memory for reprogrammable application code or large data tables

- Using external RAM devices for storing large amounts of variable data

#### 1.1.6 EXTENDED INSTRUCTION SET

The PIC18F87J10 family implements the optional extension to the PIC18 instruction set, adding 8 new instructions and an Indexed Addressing mode. Enabled as a device configuration option, the extension has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as 'C'.

#### 1.1.7 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also aids in migrating to the next larger device. This is true when moving between the 64-pin members, between the 80-pin members, or even jumping from 64-pin to 80-pin devices.

The PIC18F87J10 family is also pin compatible with other PIC18 families, such as the PIC18F87J10, PIC18F87J11, PIC18F8720 and PIC18F8722. This allows a new dimension to the evolution of applications, allowing developers to select different price points within Microchip's PIC18 portfolio, while maintaining the same feature set.

### 1.2 Other Special Features

Communications: The PIC18F87J10 family incorporates a range of serial and parallel communication peripherals, including a fully featured Universal Serial Bus communications module that is compliant with the USB Specification Revision 2.0. This device also includes 2 independent Enhanced USARTs and 2 Master SSP modules, capable of both SPI and I2C<sup>™</sup> (Master and Slave) modes of operation. The device also has a parallel port and can be configured to serve as either a Parallel Master Port or as a Parallel Slave Port.

- CCP Modules: All devices in the family incorporate two Capture/Compare/PWM (CCP) modules and three Enhanced CCP modules to maximize flexibility in control applications. Up to four different time bases may be used to perform several different operations at once. Each of the three ECCPs offers up to four PWM outputs, allowing for a total of 12 PWMs. The ECCPs also offer many beneficial features, including polarity selection, programmable dead time, auto-shutdown and restart and Half-Bridge and Full-Bridge Output modes.

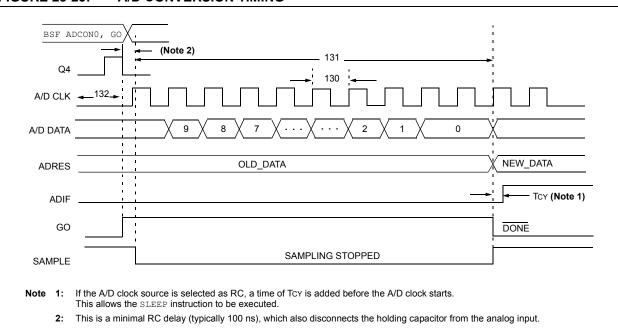

- **10-Bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, and thus, reducing code overhead.

- Extended Watchdog Timer (WDT): This enhanced version incorporates a 16-bit prescaler, allowing an extended time-out range that is stable across operating voltage and temperature. See Section 28.0 "Electrical Characteristics" for time-out periods.

#### 1.3 Details on Individual Family Members

Devices in the PIC18F87J10 family are available in 64-pin and 80-pin packages. Block diagrams for the two groups are shown in Figure 1-1 and Figure 1-2. The devices are differentiated from each other in two ways:

- 1. Flash program memory (six sizes, ranging from 32 Kbytes for PIC18FX5J50 devices to 128 Kbytes for PIC18FX7J50).

- I/O ports (7 bidirectional ports on 64-pin devices, 9 bidirectional ports on 80-pin devices).

All other features for devices in this family are identical. These are summarized in Table 1-1 and Table 1-2.

The pinouts for all devices are listed in Table 1-3 and Table 1-4.

#### 5.1.6.4 Stack Full and Underflow Resets

Device Resets on stack overflow and stack underflow conditions are enabled by setting the STVREN bit in Configuration Register 1L. When STVREN is set, a full or underflow condition will set the appropriate STKFUL or STKUNF bit and then cause a device Reset. When STVREN is cleared, a full or underflow condition will set the appropriate STKFUL or STKUNF bit, but not cause a device Reset. The STKFUL or STKUNF bits are cleared by the user software or a Power-on Reset.

#### 5.1.7 FAST REGISTER STACK

A Fast Register Stack is provided for the STATUS, WREG and BSR registers to provide a "fast return" option for interrupts. This stack is only one level deep and is neither readable nor writable. It is loaded with the current value of the corresponding register when the processor vectors for an interrupt. All interrupt sources will push values into the Stack registers. The values in the registers are then loaded back into the working registers if the RETFIE, FAST instruction is used to return from the interrupt.

If both low and high-priority interrupts are enabled, the Stack registers cannot be used reliably to return from low-priority interrupts. If a high-priority interrupt occurs while servicing a low-priority interrupt, the Stack register values stored by the low-priority interrupt will be overwritten. In these cases, users must save the key registers in software during a low-priority interrupt.

If interrupt priority is not used, all interrupts may use the Fast Register Stack for returns from interrupt. If no interrupts are used, the Fast Register Stack can be used to restore the STATUS, WREG and BSR registers at the end of a subroutine call. To use the Fast Register Stack for a subroutine call, a CALL label, FAST instruction must be executed to save the STATUS, WREG and BSR registers to the Fast Register Stack. A RETURN, FAST instruction is then executed to restore these registers from the Fast Register Stack.

Example 5-1 shows a source code example that uses the Fast Register Stack during a subroutine call and return.

#### EXAMPLE 5-1: FAST REGISTER STACK CODE EXAMPLE

| CALL SUB1, FAST | ;STATUS, WREG, BSR<br>;SAVED IN FAST REGISTER<br>;STACK |

|-----------------|---------------------------------------------------------|

| SUB1 •          |                                                         |

| RETURN FAST     | ;RESTORE VALUES SAVED<br>;IN FAST REGISTER STACK        |

# 5.1.8 LOOK-UP TABLES IN PROGRAM MEMORY

There may be programming situations that require the creation of data structures, or look-up tables, in program memory. For PIC18 devices, look-up tables can be implemented in two ways:

- Computed GOTO

- Table Reads

#### 5.1.8.1 Computed GOTO

A computed GOTO is accomplished by adding an offset to the program counter. An example is shown in Example 5-2.

A look-up table can be formed with an ADDWF PCL instruction and a group of RETLW nn instructions. The W register is loaded with an offset into the table before executing a call to that table. The first instruction of the called routine is the ADDWF PCL instruction. The next instruction executed will be one of the RETLW nn instructions that returns the value 'nn' to the calling function.

The offset value (in WREG) specifies the number of bytes that the program counter should advance and should be multiples of 2 (LSb = 0).

In this method, only one data byte may be stored in each instruction location and room on the return address stack is required.

#### EXAMPLE 5-2: COMPUTED GOTO USING AN OFFSET VALUE

|       |       | /         |

|-------|-------|-----------|

|       | MOVF  | OFFSET, W |

|       | CALL  | TABLE     |

| ORG   | nn00h |           |

| TABLE | ADDWF | PCL       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       | RETLW | nnh       |

|       | •     |           |

|       |       |           |

|       |       |           |

|       |       |           |

#### 5.1.8.2 Table Reads

A better method of storing data in program memory allows two bytes of data to be stored in each instruction location.

Look-up table data may be stored two bytes per program word while programming. The Table Pointer (TBLPTR) specifies the byte address and the Table Latch (TABLAT) contains the data that is read from the program memory. Data is transferred from program memory one byte at a time.

Table read operation is discussed further in **Section 6.1 "Table Reads and Table Writes**".

#### 6.3 Reading the Flash Program Memory

The TBLRD instruction is used to retrieve data from program memory and places it into data RAM. Table reads from program memory are performed one byte at a time.

TBLPTR points to a byte address in program space. Executing TBLRD places the byte pointed to into TABLAT. In addition, TBLPTR can be modified automatically for the next table read operation.

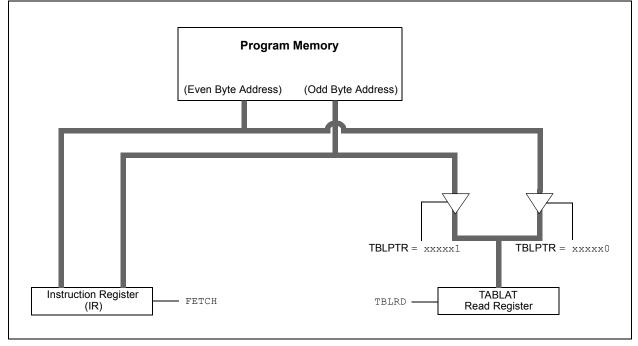

The internal program memory is typically organized by words. The Least Significant bit of the address selects between the high and low bytes of the word. Figure 6-4 shows the interface between the internal program memory and the TABLAT.

#### FIGURE 6-4: READS FROM FLASH PROGRAM MEMORY

#### EXAMPLE 6-1: READING A FLASH PROGRAM MEMORY WORD

|           | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW |   | Load TBLPTR with the base<br>address of the word |

|-----------|-------------------------------------------|--------------------------------------------------------------------------|---|--------------------------------------------------|

|           | MOVWF                                     | TBLPTRL                                                                  |   |                                                  |

| READ_WORD |                                           |                                                                          |   |                                                  |

|           | TBLRD*+                                   |                                                                          | ; | read into TABLAT and increment                   |

|           | MOVF                                      | TABLAT, W                                                                | ; | get data                                         |

|           | MOVWF                                     | WORD EVEN                                                                |   |                                                  |

|           | TBLRD*+                                   | _                                                                        | ; | read into TABLAT and increment                   |

|           | MOVF                                      | TABLAT, W                                                                | ; | get data                                         |

|           | MOVWF                                     | WORD_ODD                                                                 |   |                                                  |

| Pin Name | Function | TRIS<br>Setting | I/O | l/O<br>Type | Description                                                                                     |

|----------|----------|-----------------|-----|-------------|-------------------------------------------------------------------------------------------------|

| RJ0/ALE  | RJ0      | 0               | 0   | DIG         | LATJ<0> data output.                                                                            |

|          |          | 1               | I   | ST          | PORTJ<0> data input.                                                                            |

|          | ALE      | х               | 0   | DIG         | External memory interface address latch enable control output; takes priority over digital I/O. |

| RJ1/OE   | RJ1      | 0               | 0   | DIG         | LATJ<1> data output.                                                                            |

|          |          | 1               | Ι   | ST          | PORTJ<1> data input.                                                                            |

|          | ŌĒ       | х               | 0   | DIG         | External memory interface output enable control output; takes priority over digital I/O.        |

| RJ2/WRL  | RJ2      | 0               | 0   | DIG         | LATJ<2> data output.                                                                            |

|          |          | 1               | I   | ST          | PORTJ<2> data input.                                                                            |

|          | WRL      | х               | 0   | DIG         | External Memory Bus write low byte control; takes priority over digital I/O.                    |

| RJ3/WRH  | RJ3      | 0               | 0   | DIG         | LATJ<3> data output.                                                                            |

|          |          | 1               | I   | ST          | PORTJ<3> data input.                                                                            |

|          | WRH      | х               | 0   | DIG         | External memory interface write high byte control output; takes priority over digital I/O.      |

| RJ4/BA0  | RJ4      | 0               | 0   | DIG         | LATJ<4> data output.                                                                            |

|          |          | 1               | Ι   | ST          | PORTJ<4> data input.                                                                            |

|          | BA0      | х               | 0   | DIG         | External memory interface byte address 0 control output; takes priority over digital I/O.       |

| RJ5/CE   | RJ5      | 0               | 0   | DIG         | LATJ<5> data output.                                                                            |

|          |          | 1               | Ι   | ST          | PORTJ<5> data input.                                                                            |

|          | CE       | х               | 0   | DIG         | External memory interface chip enable control output; takes priority over digital I/O.          |

| RJ6/LB   | RJ6      | 0               | 0   | DIG         | LATJ<6> data output.                                                                            |

|          |          | 1               | I   | ST          | PORTJ<6> data input.                                                                            |

|          | LB       | х               | 0   | DIG         | External memory interface lower byte enable control output; takes priority over digital I/O.    |

| RJ7/UB   | RJ7      | 0               | 0   | DIG         | LATJ<7> data output.                                                                            |

|          |          | 1               | I   | ST          | PORTJ<7> data input.                                                                            |

|          | UB       | Х               | 0   | DIG         | External memory interface upper byte enable control output; takes priority over digital I/O.    |

#### TABLE 10-20: PORTJ FUNCTIONS

Legend: O = Output, I = Input, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input,

x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

| TABLE 10-21: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTJ |

|--------------|--------------------------------------------|

|--------------|--------------------------------------------|

| Name                 | Bit 7  | Bit 6  | Bit 5               | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|----------------------|--------|--------|---------------------|--------|--------|--------|--------|--------|-----------------------------|

| PORTJ <sup>(1)</sup> | RJ7    | RJ6    | RJ5                 | RJ4    | RJ3    | RJ2    | RJ1    | RJ0    | 65                          |

| LATJ <sup>(1)</sup>  | LATJ7  | LATJ6  | LATJ5               | LATJ4  | LATJ3  | LATJ2  | LATJ1  | LATJ0  | 64                          |

| TRISJ <sup>(1)</sup> | TRISJ7 | TRISJ6 | TRISJ5              | TRISJ4 | TRISJ3 | TRISJ2 | TRISJ1 | TRISJ0 | 64                          |

| PORTG                | RDPU   | REPU   | RJPU <sup>(1)</sup> | RG4    | RG3    | RG2    | RG1    | RG0    | 65                          |

**Legend:** Shaded cells are not used by PORTJ.

Note 1: Unimplemented on 64-pin devices, read as '0'.

| TABLE 13-2: | <b>REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER</b> |

|-------------|------------------------------------------------------------|

|-------------|------------------------------------------------------------|

| Name                 | Bit 7                                      | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|----------------------|--------------------------------------------|-----------|---------|---------|---------|--------|--------|--------|-----------------------------|

| INTCON               | GIE/GIEH                                   | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 61                          |

| PIR1                 | PMPIF                                      | ADIF      | RC1IF   | TX1IF   | SSP1IF  | CCP1IF | TMR2IF | TMR1IF | 64                          |

| PIE1                 | PMPIE                                      | ADIE      | RC1IE   | TX1IE   | SSP1IE  | CCP1IE | TMR2IE | TMR1IE | 64                          |

| IPR1                 | PMPIP                                      | ADIP      | RC1IP   | TX1IP   | SSP1IP  | CCP1IP | TMR2IP | TMR1IP | 64                          |

| TMR1L <sup>(1)</sup> | IL <sup>(1)</sup> Timer1 Register Low Byte |           |         |         |         |        |        |        | 62                          |

| TMR1H <sup>(1)</sup> | H <sup>(1)</sup> Timer1 Register High Byte |           |         |         |         |        |        | 62     |                             |

| T1CON <sup>(1)</sup> | RD16                                       | T1RUN     | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 62                          |

Legend: Shaded cells are not used by the Timer1 module.

**Note 1:** Default (legacy) SFR at this address, available when WDTCON<4> = 0.

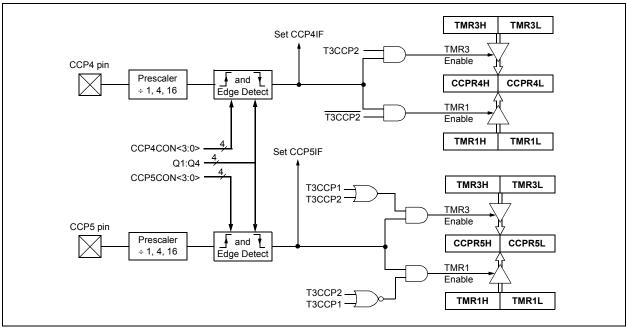

### 17.2 Capture Mode

In Capture mode, the CCPRxH:CCPRxL register pair captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on the corresponding CCPx pin. An event is defined as one of the following:

- · every falling edge

- · every rising edge

- every 4th rising edge

- · every 16th rising edge

The event is selected by the mode select bits, CCPxM3:CCPxM0 (CCPxCON<3:0>). When a capture is made, the interrupt request flag bit, CCPxIF, is set; it must be cleared in software. If another capture occurs before the value in register CCPRx is read, the old captured value is overwritten by the new captured value.

#### 17.2.1 CCPx PIN CONFIGURATION

In Capture mode, the appropriate CCPx pin should be configured as an input by setting the corresponding TRIS direction bit.

| Note: | If RG4/CCP5 is configured as an output, a |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|

|       | write to the port can cause a capture     |  |  |  |  |  |  |  |  |

|       | condition.                                |  |  |  |  |  |  |  |  |

#### 17.2.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation will not work. The timer to be used with each CCP module is selected in the T3CON register (see Section 17.1.1 "CCP Modules and Timer Resources").

#### 17.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit clear to avoid false interrupts. The interrupt flag bit, CCPxIF, should also be cleared following any such change in operating mode.

#### 17.2.4 CCP PRESCALER

There are four prescaler settings in Capture mode. They are specified as part of the operating mode selected by the mode select bits (CCPxM3:CCPxM0). Whenever the CCPx module is turned off or Capture mode is disabled, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 17-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 17-1: CHANGING BETWEEN CAPTURE PRESCALERS (CCP5 SHOWN)

|       |         | ; | Turn CCP module off<br>Load WREG with the<br>new prescaler mode |

|-------|---------|---|-----------------------------------------------------------------|

|       |         |   | -                                                               |

|       |         | ; | value and CCP ON                                                |

| MOVWE | CCP5CON | ; | Load CCP5CON with                                               |

|       |         | ; | this value                                                      |

|       |         |   |                                                                 |

#### FIGURE 17-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

### 18.0 ENHANCED CAPTURE/ COMPARE/PWM (ECCP) MODULE

In the PIC18F87J10 family of devices, three of the CCP modules are implemented as standard CCP modules with Enhanced PWM capabilities. These include the provision for 2 or 4 output channels, user-selectable polarity, dead-band control and automatic shutdown and restart. The Enhanced features are discussed in detail in **Section 18.4 "Enhanced PWM Mode"**. Capture, Compare and single-output PWM functions of the ECCP module are the same as described for the standard CCP module.

The control register for the Enhanced CCP module is shown in Register 18-1. It differs from the CCP4CON/ CCP5CON registers in that the two Most Significant bits are implemented to control PWM functionality.

In addition to the expanded range of modes available through the Enhanced CCPxCON register, the ECCP modules each have two additional registers associated with Enhanced PWM operation and auto-shutdown features. They are:

- ECCPxDEL (ECCPx PWM Delay)

- ECCPxAS (ECCPx Auto-Shutdown Control)

| REGISTER 18-1: | CCPxCON: ECCPx CONTROL REGISTER (ECCP1/ECCP2/ECCP3) |

|----------------|-----------------------------------------------------|

|                |                                                     |

| R/W-0        | R/W-0                                                                                                                                                       | R/W-0                                      | R/W-0                               | R/W-0                                 | R/W-0                  | R/W-0                     | R/W-0           |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------|---------------------------------------|------------------------|---------------------------|-----------------|--|--|--|--|

| PxM1         | PxM0                                                                                                                                                        | DCxB1                                      | DCxB0                               | CCPxM3                                | CCPxM2                 | CCPxM1                    | CCPxM0          |  |  |  |  |

| bit 7        |                                                                                                                                                             |                                            |                                     |                                       |                        |                           | bit C           |  |  |  |  |

|              |                                                                                                                                                             |                                            |                                     |                                       |                        |                           |                 |  |  |  |  |

| Legend:      |                                                                                                                                                             |                                            |                                     |                                       |                        |                           |                 |  |  |  |  |

| R = Readab   | le bit                                                                                                                                                      | W = Writable I                             | oit                                 | U = Unimplem                          | nented bit, read       | d as '0'                  |                 |  |  |  |  |

| -n = Value a | It POR                                                                                                                                                      | '1' = Bit is set                           |                                     | '0' = Bit is clea                     | ared                   | x = Bit is unkr           | nown            |  |  |  |  |

|              |                                                                                                                                                             |                                            |                                     |                                       |                        |                           |                 |  |  |  |  |

| bit 7-6      | PxM1:PxM0:                                                                                                                                                  | Enhanced PWM                               | Output Config                       | uration bits                          |                        |                           |                 |  |  |  |  |

|              |                                                                                                                                                             | <u>CPxM2 = 00, 01,</u><br>signed as Captur |                                     | ut/output: DvD F                      |                        | and an port pipe          |                 |  |  |  |  |

|              | If CCPxM3:C                                                                                                                                                 | •                                          | e/Compare inp                       | иі/оцриі, Рхв, г                      | -xc, FxD assig         | led as port pins          |                 |  |  |  |  |

|              |                                                                                                                                                             | output: PxA mod                            | lulated; PxB,                       | PxC, PxD assig                        | ned as port pir        | IS                        |                 |  |  |  |  |

|              |                                                                                                                                                             | dge output forwa                           |                                     |                                       |                        |                           |                 |  |  |  |  |

|              |                                                                                                                                                             | dge output: P1A                            |                                     |                                       |                        |                           | ed as port pins |  |  |  |  |

|              |                                                                                                                                                             | dge output rever                           |                                     |                                       | ve; P1A, P1D           | nactive                   |                 |  |  |  |  |

| bit 5-4      |                                                                                                                                                             | 30: PWM Duty C                             | ycle bit 1 and t                    | oit O                                 |                        |                           |                 |  |  |  |  |

|              | Capture mode<br>Unused.                                                                                                                                     | <u>e:</u>                                  |                                     |                                       |                        |                           |                 |  |  |  |  |

|              | Compare mod                                                                                                                                                 | de:                                        |                                     |                                       |                        |                           |                 |  |  |  |  |

|              | Unused.                                                                                                                                                     |                                            |                                     |                                       |                        |                           |                 |  |  |  |  |

|              | <u>PWM mode:</u><br>These bits are                                                                                                                          | the two I She of th                        | na 10_hit P\\/M                     | duty cycle. The ei                    | aht MShe of the        | duty cycle are fo         |                 |  |  |  |  |

| bit 3-0      | These bits are the two LSbs of the 10-bit PWM duty cycle. The eight MSbs of the duty cycle are found in CCPRxL CCPxM3:CCPxM0: ECCPx Module Mode Select bits |                                            |                                     |                                       |                        |                           |                 |  |  |  |  |

|              |                                                                                                                                                             | ure/Compare/PW                             |                                     |                                       |                        |                           |                 |  |  |  |  |

|              | 0001 = Rese                                                                                                                                                 | erved                                      |                                     | ,                                     |                        |                           |                 |  |  |  |  |

|              | 0010 = Com<br>0011 = Capt                                                                                                                                   | pare mode: toggl                           | e output on ma                      | atch                                  |                        |                           |                 |  |  |  |  |

|              |                                                                                                                                                             | ure mode: every                            | falling edge                        |                                       |                        |                           |                 |  |  |  |  |

|              | 0101 = Capt                                                                                                                                                 | ure mode: every                            | rising edge                         |                                       |                        |                           |                 |  |  |  |  |

|              | 0110 = Capt                                                                                                                                                 | ure mode: every ure mode, every            | 4th rising edge<br>16th rising edge | e<br>Ie                               |                        |                           |                 |  |  |  |  |

|              | 1000 = Com                                                                                                                                                  | pare mode: initia                          | lize ECCPx pir                      | n low; set output                     | on compare ma          | atch (set CCPxII          | =)              |  |  |  |  |

|              | 1001 = Com                                                                                                                                                  | pare mode: initia                          | lize ECCPx pir                      | high; clear outp                      | out on compare         | match (set CCF            | PxIF)           |  |  |  |  |

|              | 1010 = Com<br>1011 = Com                                                                                                                                    | pare mode: gene<br>pare mode: trigge       | erate software i<br>er special ever | nterrupt only; EC<br>at (ECCPx resets | SCPx pin reverts       | s to I/O state            | bit. FCCP2      |  |  |  |  |

|              | trigge                                                                                                                                                      | er also starts A/D                         | conversion if                       | A/D module is en                      | nabled) <sup>(1)</sup> | -, - <b>0 0 0 0 1</b> All | ,               |  |  |  |  |

|              |                                                                                                                                                             | 1 mode: PxA, Px0<br>1 mode: PxA, Px0       |                                     |                                       |                        |                           |                 |  |  |  |  |

|              |                                                                                                                                                             | 1 mode: PxA, Px0                           |                                     |                                       |                        |                           |                 |  |  |  |  |

|              |                                                                                                                                                             | 1 mode: PxA, Px                            |                                     |                                       |                        |                           |                 |  |  |  |  |

Note 1: Implemented only for ECCP1 and ECCP2; same as '1010' for ECCP3.

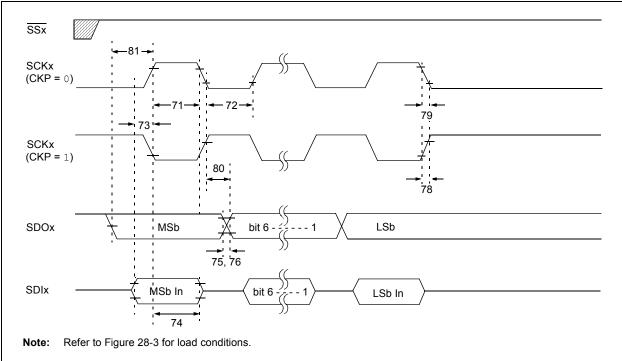

#### 19.3.4 ENABLING SPI I/O

To enable the serial port, MSSP Enable bit, SSPEN (SSPxCON1<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, reinitialize the SSPxCON registers and then set the SSPEN bit. This configures the SDIx, SDOx, SCKx and SSx pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- SDIx is automatically controlled by the SPI module

- SDOx must have the TRISC<5> or TRISD<4> bit cleared

- SCKx (Master mode) must have the TRISC<3> or TRISD<6>bit cleared

- SCKx (Slave mode) must have the TRISC<3> or TRISD<6> bit set

- SSx must have the TRISF<7> or TRISD<7> bit set

Any serial port function that is not desired may be overridden by programming the corresponding Data Direction (TRIS) register to the opposite value.

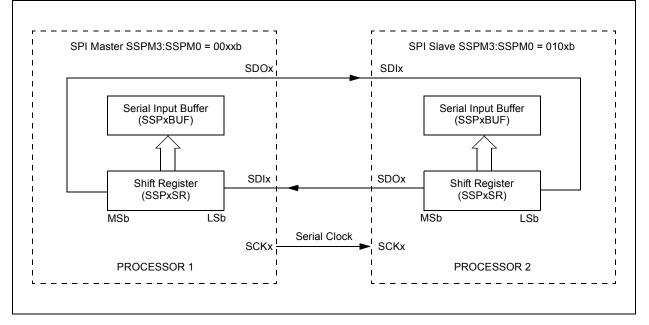

#### 19.3.5 TYPICAL CONNECTION

Figure 19-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCKx signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- · Master sends data Slave sends dummy data

- · Master sends data Slave sends data

- Master sends dummy data Slave sends data

#### FIGURE 19-2: SPI MASTER/SLAVE CONNECTION

#### 19.4.3.5 Reception

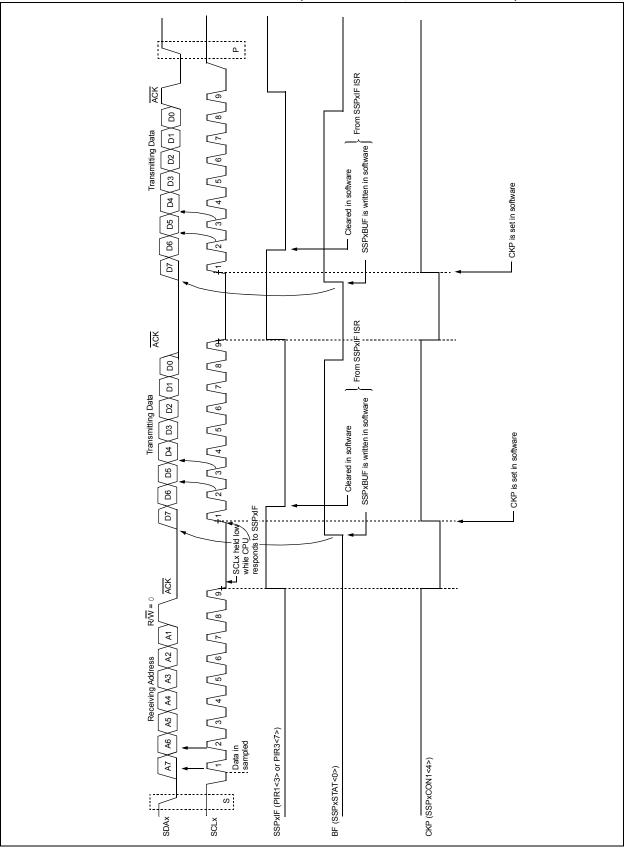

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPxSTAT register is cleared. The received address is loaded into the SSPxBUF register and the SDAx line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit, BF (SSPxSTAT<0>), is set or bit, SSPOV (SSPxCON1<6>), is set.

An MSSP interrupt is generated for each data transfer byte. The interrupt flag bit, SSPxIF, must be cleared in software. The SSPxSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPxCON2<0> = 1), SCLx will be held low (clock stretch) following each data transfer. The clock must be released by setting bit, CKP (SSPxCON1<4>). See **Section 19.4.4** "Clock **Stretching**" for more details.

### 19.4.3.6 Transmission

When the  $R/\overline{W}$  bit of the incoming address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the SSPxSTAT register is set. The received address is loaded into the SSPxBUF register. The ACK pulse will be sent on the ninth bit and pin SCLx is held low regardless of SEN (see **Section 19.4.4 "Clock Stretching"** for more details). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPxBUF register which also loads the SSPxSR register. Then, pin SCLx should be enabled by setting bit, CKP (SSPxCON1<4>). The eight data bits are shifted out on the falling edge of the SCLx input. This ensures that the SDAx signal is valid during the SCLx high time (Figure 19-10).

The ACK pulse from the master-receiver is latched on the rising edge of the ninth SCLx input pulse. If the SDAx line is high (not ACK), then the data transfer is complete. In this case, when the ACK is latched by the slave, the slave logic is reset (resets the SSPxSTAT register) and the slave monitors for another occurrence of the Start bit. If the SDAx line was low (ACK), the next transmit data must be loaded into the SSPxBUF register. Again, pin SCLx must be enabled by setting bit, CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPxIF bit must be cleared in software and the SSPxSTAT register is used to determine the status of the byte. The SSPxIF bit is set on the falling edge of the ninth clock pulse.

# PIC18F87J50 FAMILY

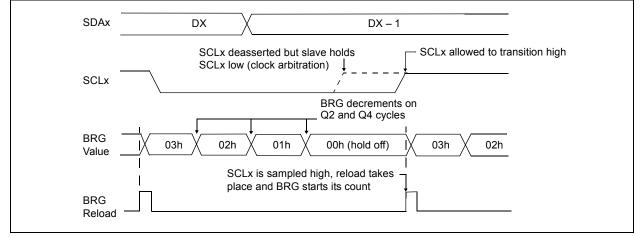

#### 19.4.7.2 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCLx pin (SCLx allowed to float high). When the SCLx pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCLx pin is actually sampled high. When the

SCLx pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPxADD<6:0> and begins counting. This ensures that the SCLx high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 19-20).

#### EXAMPLE 20-1: CALCULATING BAUD RATE ERROR

| For a device with Fosc of | 16 N | MHz, desired baud rate of 9600, Asynchronous mode, and 8-bit BRG: |

|---------------------------|------|-------------------------------------------------------------------|

| Desired Baud Rate         | =    | FOSC/(64 ([SPBRGHx:SPBRGx] + 1))                                  |

| Solving for SPBRGHx:SI    | PBR  | Gx:                                                               |

| Х                         | =    | ((FOSC/Desired Baud Rate)/64) – 1                                 |

|                           | =    | ((1600000/9600)/64) – 1                                           |

|                           | =    | [25.042] = 25                                                     |

| Calculated Baud Rate      | =    | 1600000/(64 (25 + 1))                                             |

|                           | =    | 9615                                                              |

| Error                     | =    | (Calculated Baud Rate - Desired Baud Rate)/Desired Baud Rate      |

|                           | =    | (9615 - 9600)/9600 = 0.16%                                        |

|                           |      |                                                                   |

#### TABLE 20-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Bit 7                                   | Bit 6                                          | Bit 5                                | Bit 4                                                               | Bit 3                                                                                      | Bit 2                                    | Bit 1                                                                                                                   | Bit 0                                                                                                                               | Reset Values<br>on Page:                                                                                                                       |

|-----------------------------------------|------------------------------------------------|--------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| CSRC                                    | TX9                                            | TXEN                                 | SYNC                                                                | SENDB                                                                                      | BRGH                                     | TRMT                                                                                                                    | TX9D                                                                                                                                | 63                                                                                                                                             |

| SPEN RX9 SREN CREN ADDEN FERR OERR RX9D |                                                |                                      |                                                                     |                                                                                            |                                          |                                                                                                                         | 63                                                                                                                                  |                                                                                                                                                |

| ABDOVF                                  | RCIDL                                          | DTRXP                                | SCKP                                                                | BRG16                                                                                      | _                                        | WUE                                                                                                                     | ABDEN                                                                                                                               | 65                                                                                                                                             |

| EUSARTx                                 | EUSARTx Baud Rate Generator Register High Byte |                                      |                                                                     |                                                                                            |                                          |                                                                                                                         |                                                                                                                                     |                                                                                                                                                |

| EUSARTx                                 | USARTx Baud Rate Generator Register Low Byte   |                                      |                                                                     |                                                                                            |                                          |                                                                                                                         |                                                                                                                                     |                                                                                                                                                |

|                                         | CSRC<br>SPEN<br>ABDOVF<br>EUSARTx              | CSRCTX9SPENRX9ABDOVFRCIDLEUSARTxBaud | CSRCTX9TXENSPENRX9SRENABDOVFRCIDLDTRXPEUSARTx Baud Rate Generator F | CSRCTX9TXENSYNCSPENRX9SRENCRENABDOVFRCIDLDTRXPSCKPEUSARTx Baud RateGenerator Register High | CSRCTX9TXENSYNCSENDBSPENRX9SRENCRENADDEN | CSRCTX9TXENSYNCSENDBBRGHSPENRX9SRENCRENADDENFERRABDOVFRCIDLDTRXPSCKPBRG16—EUSARTx Baud Rate Generator Register HighByte | CSRCTX9TXENSYNCSENDBBRGHTRMTSPENRX9SRENCRENADDENFERROERRABDOVFRCIDLDTRXPSCKPBRG16—WUEEUSARTx Baud Rate Generator Register High Byte | CSRCTX9TXENSYNCSENDBBRGHTRMTTX9DSPENRX9SRENCRENADDENFERROERRRX9DABDOVFRCIDLDTRXPSCKPBRG16—WUEABDENEUSARTx Baud Rate Generator Register Highter |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the BRG.

### 22.2 USB Status and Control

The operation of the USB module is configured and managed through three control registers. In addition, a total of 22 registers are used to manage the actual USB transactions. The registers are:

- USB Control register (UCON)

- USB Configuration register (UCFG)

- USB Transfer Status register (USTAT)

- USB Device Address register (UADDR)

- Frame Number registers (UFRMH:UFRML)

- Endpoint Enable registers 0 through 15 (UEPn)

#### 22.2.1 USB CONTROL REGISTER (UCON)

The USB Control register (Register 22-1) contains bits needed to control the module behavior during transfers. The register contains bits that control the following:

- Main USB Peripheral Enable

- Ping-Pong Buffer Pointer Reset

- Control of the Suspend mode

- Packet Transfer Disable

### REGISTER 22-1: UCON: USB CONTROL REGISTER

In addition, the USB Control register contains a status bit, SE0 (UCON<5>), which is used to indicate the occurrence of a single-ended zero on the bus. When the USB module is enabled, this bit should be monitored to determine whether the differential data lines have come out of a single-ended zero condition. This helps to differentiate the initial power-up state from the USB Reset signal.

The overall operation of the USB module is controlled by the USBEN bit (UCON<3>). Setting this bit activates the module and resets all of the PPBI bits in the Buffer Descriptor Table to '0'. This bit also activates the internal pull-up resistors, if they are enabled. Thus, this bit can be used as a soft attach/detach to the USB. Although all status and control bits are ignored when this bit is clear, the module needs to be fully preconfigured prior to setting this bit. This bit cannot be set until the USB module is supplied with an active clock source. If the PLL is being used, it should be enabled at least two milliseconds (enough time for the PLL to lock) before attempting to set the USBEN bit.

| U-0   | R/W-0  | R-x | R/C-0  | R/W-0                | R/W-0  | R/W-0  | U-0   |

|-------|--------|-----|--------|----------------------|--------|--------|-------|

| —     | PPBRST | SE0 | PKTDIS | USBEN <sup>(1)</sup> | RESUME | SUSPND | —     |

| bit 7 |        |     |        |                      |        |        | bit 0 |

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7 | Unimplemented: Read as '0'                                                                                                                                                                                            |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | PPBRST: Ping-Pong Buffers Reset bit                                                                                                                                                                                   |

|       | <ul> <li>1 = Reset all Ping-Pong Buffer Pointers to the Even Buffer Descriptor (BD) banks</li> <li>0 = Ping-Pong Buffer Pointers not being reset</li> </ul>                                                           |

| bit 5 | SE0: Live Single-Ended Zero Flag bit                                                                                                                                                                                  |

|       | <ul><li>1 = Single-ended zero active on the USB bus</li><li>0 = No single-ended zero detected</li></ul>                                                                                                               |

| bit 4 | PKTDIS: Packet Transfer Disable bit                                                                                                                                                                                   |

|       | <ul> <li>1 = SIE token and packet processing disabled, automatically set when a SETUP token is received</li> <li>0 = SIE token and packet processing enabled</li> </ul>                                               |

| bit 3 | USBEN: USB Module Enable bit <sup>(1)</sup>                                                                                                                                                                           |

|       | <ul> <li>1 = USB module and supporting circuitry enabled (device attached)</li> <li>0 = USB module and supporting circuitry disabled (device detached)</li> </ul>                                                     |

| bit 2 | RESUME: Resume Signaling Enable bit                                                                                                                                                                                   |

|       | <ul><li>1 = Resume signaling activated</li><li>0 = Resume signaling disabled</li></ul>                                                                                                                                |

| bit 1 | SUSPND: Suspend USB bit                                                                                                                                                                                               |

|       | <ul> <li>1 = USB module and supporting circuitry in Power Conserve mode, SIE clock inactive</li> <li>0 = USB module and supporting circuitry in normal operation, SIE clock clocked at the configured rate</li> </ul> |

| bit 0 | Unimplemented: Read as '0'                                                                                                                                                                                            |

|       |                                                                                                                                                                                                                       |

Note 1: This bit cannot be set if the USB module does not have an appropriate clock source.

#### . OW (DVTE ADDDECC 200000L) NEIGAI .

| R/WO-1       | R/WO-1                                     | R/WO-1                                                                                                                            | U-0           | R/WO-1           | R/WO-1           | R/WO-1          | R/WO-1 |  |  |  |  |

|--------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|------------------|-----------------|--------|--|--|--|--|

| DEBUG        | XINST                                      | STVREN                                                                                                                            | _             | PLLDIV2          | PLLDIV1          | PLLDIV0         | WDTEN  |  |  |  |  |

| bit 7        |                                            |                                                                                                                                   |               | ·                |                  |                 | bit C  |  |  |  |  |

| Legend:      |                                            |                                                                                                                                   |               |                  |                  |                 |        |  |  |  |  |

| R = Readab   | le bit                                     | WO = Write-C                                                                                                                      | nce bit       | U = Unimpler     | nented bit, read | d as '0'        |        |  |  |  |  |

| -n = Value a | t POR                                      | '1' = Bit is set                                                                                                                  |               | '0' = Bit is cle | ared             | x = Bit is unkr | iown   |  |  |  |  |

| bit 7        | DEBUG: Ba                                  | ckground Debug                                                                                                                    | iger Enable b | it               |                  |                 |        |  |  |  |  |

|              | 1 = Backgro                                | ound debugger d                                                                                                                   | isabled; RB6  | and RB7 confi    |                  |                 | pins   |  |  |  |  |

| bit 6        | XINST: Exte                                | nded Instruction                                                                                                                  | Set Enable b  | bit              |                  |                 |        |  |  |  |  |

|              |                                            | ion set extensior<br>ion set extensior                                                                                            |               | •                |                  | _egacy mode)    |        |  |  |  |  |

| bit 5        | STVREN: St                                 | ack Overflow/Ur                                                                                                                   | nderflow Rese | et Enable bit    |                  |                 |        |  |  |  |  |

|              |                                            | n stack overflow                                                                                                                  |               |                  |                  |                 |        |  |  |  |  |

|              |                                            | on stack overflov                                                                                                                 |               | isabled          |                  |                 |        |  |  |  |  |

| bit 4        | •                                          | nted: Read as '                                                                                                                   |               |                  |                  |                 |        |  |  |  |  |

| bit 3-1      | PLLDIV2:PLLDIV0: Oscillator Selection bits |                                                                                                                                   |               |                  |                  |                 |        |  |  |  |  |

|              |                                            | Divider must be selected to provide a 4 MHz input into the 96 MHz PLL<br>111 = No divide - oscillator used directly (4 MHz input) |               |                  |                  |                 |        |  |  |  |  |

|              |                                            |                                                                                                                                   | •             | • • • •          |                  |                 |        |  |  |  |  |

|              |                                            | <ul> <li>110 = Oscillator divided by 2 (8 MHz input)</li> <li>101 = Oscillator divided by 3 (12 MHz input)</li> </ul>             |               |                  |                  |                 |        |  |  |  |  |

|              |                                            | 100 = Oscillator divided by 4 (16 MHz input)                                                                                      |               |                  |                  |                 |        |  |  |  |  |

|              |                                            | lator divided by                                                                                                                  |               |                  |                  |                 |        |  |  |  |  |

|              |                                            | lator divided by lator divided by                                                                                                 |               |                  |                  |                 |        |  |  |  |  |

|              |                                            | lator divided by                                                                                                                  |               |                  |                  |                 |        |  |  |  |  |

| bit 0        |                                            | atchdog Timer E                                                                                                                   |               | . 7              |                  |                 |        |  |  |  |  |

|              | 1 = WDT er                                 | -                                                                                                                                 |               |                  |                  |                 |        |  |  |  |  |

|              | 0 = WDT di                                 |                                                                                                                                   |               |                  |                  |                 |        |  |  |  |  |

| Mnemo    | onic,                           | Description                              | Cycles     | 16-E | Bit Insti | ruction V | Vord | Status          | Notes      |

|----------|---------------------------------|------------------------------------------|------------|------|-----------|-----------|------|-----------------|------------|

| Operands |                                 | Description                              | Cycles     | MSb  |           |           | LSb  | Affected        | Notes      |

| BYTE-ORI | ENTED O                         | OPERATIONS                               |            |      |           |           |      |                 |            |

| ADDWF    | f, d, a                         | Add WREG and f                           | 1          | 0010 | 01da      | ffff      | ffff | C, DC, Z, OV, N | 1, 2       |

| ADDWFC   | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010 | 00da      | ffff      | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF    | f, d, a                         | AND WREG with f                          | 1          | 0001 | 01da      | ffff      | ffff | Z, N            | 1,2        |

| CLRF     | f, a                            | Clear f                                  | 1          | 0110 | 101a      | ffff      | ffff | Z               | 2          |

| COMF     | f, d, a                         | Complement f                             | 1          | 0001 | 11da      | ffff      | ffff | Z, N            | 1, 2       |

| CPFSEQ   | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110 | 001a      | ffff      | ffff | None            | 4          |

| CPFSGT   | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110 | 010a      | ffff      | ffff | None            | 4          |

| CPFSLT   | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110 | 000a      | ffff      | ffff | None            | 1, 2       |

| DECF     | f, d, a                         | Decrement f                              | 1          | 0000 | 01da      | ffff      | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ   | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010 | 11da      | ffff      | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ   | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100 | 11da      | ffff      | ffff | None            | 1, 2       |

| INCF     | f, d, a                         | Increment f                              | 1          | 0010 | 10da      | ffff      | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ   | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011 | 11da      | ffff      | ffff | None            | 4          |

| INFSNZ   | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100 | 10da      | ffff      | ffff | None            | 1, 2       |

| IORWF    | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001 | 00da      | ffff      | ffff | Z, N            | 1, 2       |

| MOVF     | f, d, a                         | Move f                                   | 1          | 0101 | 00da      | ffff      | ffff | Z, N            | 1          |

| MOVFF    | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100 | ffff      | ffff      | ffff | None            |            |

|          | 0 u                             | f <sub>d</sub> (destination) 2nd word    |            | 1111 | ffff      | ffff      | ffff |                 |            |

| MOVWF    | f, a                            | Move WREG to f                           | 1          | 0110 | 111a      | ffff      | ffff | None            |            |

| MULWF    | f, a                            | Multiply WREG with f                     | 1          | 0000 | 001a      | ffff      | ffff | None            | 1, 2       |

| NEGF     | f, a                            | Negate f                                 | 1          | 0110 | 110a      | ffff      | ffff | C, DC, Z, OV, N |            |

| RLCF     | f, d, a                         | Rotate Left f through Carry              | 1          | 0011 | 01da      | ffff      |      | C, Z, N         | 1, 2       |

| RLNCF    | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100 | 01da      | ffff      | ffff | Z, N            |            |

| RRCF     | f, d, a                         | Rotate Right f through Carry             | 1          | 0011 | 00da      | ffff      | ffff | C, Z, N         |            |

| RRNCF    | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100 | 00da      | ffff      | ffff | Z, N            |            |

| SETF     | f, a                            | Set f                                    | 1          | 0110 | 100a      | ffff      | ffff | None            | 1, 2       |

| SUBFWB   | f, d, a                         | Subtract f from WREG with                | 1          | 0101 | 01da      | ffff      | ffff | C, DC, Z, OV, N |            |

|          | , , -                           | Borrow                                   |            |      |           |           |      | . , , ,         |            |

| SUBWF    | f, d, a                         | Subtract WREG from f                     | 1          | 0101 | 11da      | ffff      | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWFB   | f, d, a                         | Subtract WREG from f with                | 1          | 0101 | 10da      | ffff      |      | C, DC, Z, OV, N |            |

|          | , , -                           | Borrow                                   |            |      |           |           |      | . , , ,         |            |

| SWAPF    | f, d, a                         | Swap Nibbles in f                        | 1          | 0011 | 10da      | ffff      | ffff | None            | 4          |

| TSTFSZ   | f, a                            | Test f, Skip if 0                        | 1 (2 or 3) |      |           | ffff      | ffff | None            | 1, 2       |

| XORWF    | f, d, a                         | Exclusive OR WREG with f                 | 1          |      | 10da      | ffff      | ffff |                 |            |

|          |                                 |                                          | -          |      |           |           |      |                 | l          |

#### TABLE 26-2: PIC18F87J50 FAMILY INSTRUCTION SET

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

#### 28.2 DC Characteristics: Power-Down and Supply Current PIC18F87J50 Family (Industrial) (Continued)

|              | 7J50 Family<br>strial)                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |       |       |                                       |                                          |  |  |

|--------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|---------------------------------------|------------------------------------------|--|--|

| Param<br>No. | Device                                    | Тур                                                                                                                                | Max  | Units |       | Conditions                            |                                          |  |  |

|              | Supply Current (IDD) Cont. <sup>(2)</sup> |                                                                                                                                    |      |       |       |                                       |                                          |  |  |

|              | All devices                               | 0.17                                                                                                                               | 0.35 | mA    | -40°C |                                       | Fosc = 1 MHz                             |  |  |

|              |                                           | 0.18                                                                                                                               | 0.35 | mA    | +25°C | VDD = 2.0V, $VDDCORE = 2.0V(4)$       |                                          |  |  |

|              |                                           | 0.20                                                                                                                               | 0.42 | mA    | +85°C | VBBOOKE 2.0V                          |                                          |  |  |

|              | All devices                               | 0.29                                                                                                                               | 0.52 | mA    | -40°C |                                       |                                          |  |  |

|              |                                           | 0.31                                                                                                                               | 0.52 | mA    | +25°C | VDD = 2.5V,<br>$VDDCORE = 2.5V^{(4)}$ | ( <b>PRI_RUN</b> mode,<br>EC oscillator) |  |  |

|              |                                           | 0.34                                                                                                                               | 0.61 | mA    | +85°C | VBBOOKE 2.0V                          |                                          |  |  |

|              | All devices                               | 0.59                                                                                                                               | 1.1  | mA    | -40°C |                                       |                                          |  |  |

|              |                                           | 0.44                                                                                                                               | 0.85 | mA    | +25°C | VDD = 3.3V <sup>(5)</sup>             |                                          |  |  |

|              |                                           | 0.42                                                                                                                               | 0.85 | mA    | +85°C |                                       |                                          |  |  |

|              | All devices                               | 0.70                                                                                                                               | 1.25 | mA    | -40°C |                                       |                                          |  |  |