Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| D.L.U.                     |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Details                    |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | EBI/EMI, I²C, SPI, UART/USART, USB                                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 65                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f87j50-i-pt |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 6.5.2 FLASH PROGRAM MEMORY WRITE SEQUENCE (WORD PRORAMMING).

The PIC18F87J10 family of devices have a feature that allows programming a single word (two bytes). This feature is enabled when the WPROG bit is set. If the memory location is already erased, the following sequence is required to enable this feature:

- Load the Table Pointer register with the address of the data to be written. (It must be an even address.)

- 2. Write the 2 bytes into the holding registers by performing table writes. (Do not post-increment on the second table write.)

- Set the WREN bit (EECON1<2>) to enable writes and the WPROG bit (EECON1<5>) to select Word Write mode.

- 4. Disable interrupts.

- 5. Write 55h to EECON2.

- 6. Write AAh to EECON2.

- 7. Set the WR bit. This will begin the write cycle.

- 8. The CPU will stall for duration of the write for T<sub>IW</sub> (see parameter D133A).

- 9. Re-enable interrupts.

#### EXAMPLE 6-4: SINGLE WORD WRITE TO FLASH PROGRAM MEMORY

|                |         |                 |   | ,                                                 |

|----------------|---------|-----------------|---|---------------------------------------------------|

|                | MOVLW   | CODE_ADDR_UPPER | ; | Load TBLPTR with the base address                 |

|                | MOVWF   | TBLPTRU         |   |                                                   |

|                | MOVLW   | CODE_ADDR_HIGH  |   |                                                   |

|                | MOVWF   | TBLPTRH         |   |                                                   |

|                | MOVLW   | CODE_ADDR_LOW   | ; | The table pointer must be loaded with an even     |

|                |         |                 |   | address                                           |

|                | MOVWF   | TBLPTRL         |   |                                                   |

|                | MOVLW   | DATA0           | ; | LSB of word to be written                         |

|                | MOVWF   | TABLAT          |   |                                                   |

|                | TBLWT*+ |                 |   |                                                   |

|                | MOVLW   | DATA1           | ; | MSB of word to be written                         |

|                | MOVWF   | TABLAT          |   |                                                   |

|                | TBLWT*  |                 | ; | The last table write must not increment the table |

|                |         |                 |   | pointer! The table pointer needs to point to the  |

|                |         |                 |   | MSB before starting the write operation.          |

|                |         |                 |   |                                                   |

|                |         |                 |   |                                                   |

| PROGRAM_MEMORY |         |                 |   |                                                   |

|                | BSF     | EECON1, WPROG   | - | enable single word write                          |

|                | BSF     | EECON1, WREN    |   | enable write to memory                            |

|                | BCF     | INTCON, GIE     | ; | disable interrupts                                |

|                | MOVLW   | 55h             |   |                                                   |

| Required       | MOVWF   | EECON2          | ; | write 55h                                         |

| Sequence       | MOVLW   | 0AAh            |   |                                                   |

|                | MOVWF   | EECON2          | • | write OAAh                                        |

|                | BSF     | EECON1, WR      |   | start program (CPU stall)                         |

|                | BSF     | INTCON, GIE     |   | re-enable interrupts                              |

|                | BCF     | EECON1, WPROG   |   | disable single word write                         |

|                | BCF     | EECON1, WREN    | ; | disable write to memory                           |

|                |         |                 |   |                                                   |

# 7.8 Operation in Power-Managed Modes

In alternate, power-managed Run modes, the external bus continues to operate normally. If a clock source with a lower speed is selected, bus operations will run at that speed. In these cases, excessive access times for the external memory may result if wait states have been enabled and added to external memory operations. If operations in a lower power Run mode are anticipated, users should provide in their applications for adjusting memory access times at the lower clock speeds.

In Sleep and Idle modes, the microcontroller core does not need to access data; bus operations are suspended. The state of the external bus is frozen, with the address/data pins and most of the control pins holding at the same state they were in when the mode was invoked. The only potential changes are the  $\overline{\text{CE}}$ ,  $\overline{\text{LB}}$  and  $\overline{\text{UB}}$  pins, which are held at logic high.

#### REGISTER 9-9: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

| R/W-0       | R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |  |

|-------------|--------|-------|-------|--------|--------|--------|--------|--|

| SSP2IE      | BCL2IE | RC2IE | TX2IE | TMR4IE | CCP5IE | CCP4IE | CCP3IE |  |

| bit 7 bit 0 |        |       |       |        |        |        |        |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 SSP2IE: Master Synchronous Serial Port 2 Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 6 BCL2IE: Bus Collision Interrupt Enable bit (MSSP2 module)

1 = Enabled

0 = Disabled

bit 5 RC2IE: EUSART2 Receive Interrupt Enable bit

1 = Enabled0 = Disabled

bit 4 TX2IE: EUSART2 Transmit Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 3 TMR4IE: TMR4 to PR4 Match Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 2 CCP5IE: CCP5 Interrupt Enable bit

1 = Enabled0 = Disabled

bit 1 CCP4IE: CCP4 Interrupt Enable bit

1 = Enabled

0 = Disabled

bit 0 CCP3IE: ECCP3 Interrupt Enable bit

1 = Enabled0 = Disabled

TABLE 10-7: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Name    | Bit 7    | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page: |

|---------|----------|-----------|---------|---------|---------|--------|--------|--------|-----------------------------|

| PORTB   | RB7      | RB6       | RB5     | RB4     | RB3     | RB2    | RB1    | RB0    | 65                          |

| LATB    | LATB7    | LATB6     | LATB5   | LATB4   | LATB3   | LATB2  | LATB1  | LATB0  | 64                          |

| TRISB   | TRISB7   | TRISB6    | TRISB5  | TRISB4  | TRISB3  | TRISB2 | TRISB1 | TRISB0 | 64                          |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 61                          |

| INTCON2 | RBPU     | INTEDG0   | INTEDG1 | INTEDG2 | INTEDG3 | TMR0IP | INT3IP | RBIP   | 61                          |

| INTCON3 | INT2IP   | INT1IP    | INT3IE  | INT2IE  | INT1IE  | INT3IF | INT2IF | INT1IF | 61                          |

Legend: Shaded cells are not used by PORTB.

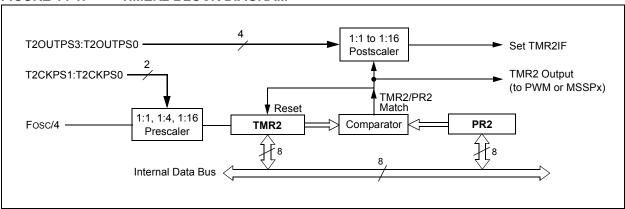

#### 14.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2 to PR2 match) provides the input for the 4-bit output counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF (PIR1<1>). The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE (PIE1<1>).

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS3:T2OUTPS0 (T2CON<6:3>).

#### 14.3 Timer2 Output

The unscaled output of TMR2 is available primarily to the ECCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP modules operating in SPI mode. Additional information is provided in Section 19.0 "Master Synchronous Serial Port (MSSP) Module".

FIGURE 14-1: TIMER2 BLOCK DIAGRAM

TABLE 14-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Name                | Bit 7                  | Bit 6     | Bit 5    | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on Page: |

|---------------------|------------------------|-----------|----------|----------|----------|--------|---------|---------|-----------------------------|

| INTCON              | GIE/GIEH               | PEIE/GIEL | TMR0IE   | INT0IE   | RBIE     | TMR0IF | INT0IF  | RBIF    | 61                          |

| PIR1                | PMPIF                  | ADIF      | RC1IF    | TX1IF    | SSP1IF   | CCP1IF | TMR2IF  | TMR1IF  | 64                          |

| PIE1                | PMPIE                  | ADIE      | RC1IE    | TX1IE    | SSP1IE   | CCP1IE | TMR2IE  | TMR1IE  | 64                          |

| IPR1                | PMPIP                  | ADIP      | RC1IP    | TX1IP    | SSP1IP   | CCP1IP | TMR2IP  | TMR1IP  | 64                          |

| TMR2 <sup>(1)</sup> | Timer2 Register        |           |          |          |          |        |         |         | 62                          |

| T2CON               | _                      | T2OUTPS3  | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 62                          |

| PR2 <sup>(1)</sup>  | Timer2 Period Register |           |          |          |          |        |         |         | 62                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: Default (legacy) SFR at this address, available when WDTCON<4> = 0.

TABLE 17-2: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1 AND TIMER3

| Name                  | Bit 7                                    | Bit 6         | Bit 5        | Bit 4       | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Reset<br>Values<br>on Page: |

|-----------------------|------------------------------------------|---------------|--------------|-------------|---------|---------|---------|---------|-----------------------------|

| INTCON                | GIE/GIEH                                 | PEIE/GIEL     | TMR0IE       | INT0IE      | RBIE    | TMR0IF  | INT0IF  | RBIF    | 61                          |

| RCON                  | IPEN                                     | _             | CM           | RI          | TO      | PD      | POR     | BOR     | 62                          |

| PIR1                  | PMPIF                                    | ADIF          | RC1IF        | TX1IF       | SSP1IF  | CCP1IF  | TMR2IF  | TMR1IF  | 64                          |

| PIE1                  | PMPIE                                    | ADIE          | RC1IE        | TX1IE       | SSP1IE  | CCP1IE  | TMR2IE  | TMR1IE  | 64                          |

| IPR1                  | PMPIP                                    | ADIP          | RC1IP        | TX1IP       | SSP1IP  | CCP1IP  | TMR2IP  | TMR1IP  | 64                          |

| PIR2                  | OSCFIF                                   | CM2IF         | CM1IF        | USBIF       | BCL1IF  | LVDIF   | TMR3IF  | CCP2IF  | 64                          |

| PIE2                  | OSCFIE                                   | CM2IE         | CM1IE        | USBIE       | BCL1IE  | LVDIE   | TMR3IE  | CCP2IE  | 64                          |

| IPR2                  | OSCFIP                                   | CM2IP         | CM1IP        | USBIP       | BCL1IP  | LVDIP   | TMR3IP  | CCP2IP  | 64                          |

| PIR3                  | SSP2IF                                   | BCL2IF        | RC2IF        | TX2IF       | TMR4IF  | CCP5IF  | CCP4IF  | CCP3IF  | 64                          |

| PIE3                  | SSP2IE                                   | BCL2IE        | RC2IE        | TX2IE       | TMR4IE  | CCP5IE  | CCP4IE  | CCP3IE  | 64                          |

| IPR3                  | SSP2IP                                   | BCL2IP        | RC2IP        | TX2IP       | TMR4IP  | CCP5IP  | CCP4IP  | CCP3IP  | 64                          |

| TRISG                 | _                                        | _             | _            | TRISG4      | TRISG3  | TRISG2  | TRISG1  | TRISG0  | 64                          |

| TMR1L <sup>(1)</sup>  | Timer1 Reg                               | gister Low B  | syte         |             |         |         |         |         | 62                          |

| TMR1H <sup>(1)</sup>  | Timer1 Req                               | gister High E | 3yte         |             |         |         |         |         | 62                          |

| ODCON1 <sup>(2)</sup> | _                                        | _             | _            | CCP5OD      | CCP4OD  | ECCP3OD | ECCP2OD | ECCP10D | 62                          |

| T1CON <sup>(1)</sup>  | RD16                                     | T1RUN         | T1CKPS1      | T1CKPS0     | T10SCEN | T1SYNC  | TMR1CS  | TMR10N  | 62                          |

| TMR3H                 | Timer3 Req                               | gister High E | Byte         |             |         |         |         |         | 65                          |

| TMR3L                 | Timer3 Req                               | gister Low B  | syte         |             |         |         |         |         | 65                          |

| T3CON                 | RD16                                     | T3CCP2        | T3CKPS1      | T3CKPS0     | T3CCP1  | T3SYNC  | TMR3CS  | TMR3ON  | 65                          |

| CCPR4L                | Capture/Co                               | mpare/PWI     | M Register 4 | 4 Low Byte  |         |         |         |         | 65                          |

| CCPR4H                | Capture/Co                               | mpare/PWI     | M Register 4 | 4 High Byte |         |         |         |         | 65                          |

| CCPR5L                | Capture/Co                               | mpare/PWI     | M Register ( | 5 Low Byte  |         |         |         |         | 65                          |

| CCPR5H                | Capture/Compare/PWM Register 5 High Byte |               |              |             |         |         |         | 65      |                             |

| CCP4CON               |                                          | _             | DC4B1        | DC4B0       | CCP4M3  | CCP4M2  | CCP4M1  | CCP4M0  | 65                          |

| CCP5CON               | _                                        | _             | DC5B1        | DC5B0       | CCP5M3  | CCP5M2  | CCP5M1  | CCP5M0  | 65                          |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by Capture/Compare, Timer1 or Timer3.

**Note 1:** Default (legacy) SFR at this address, available when WDTCON<4> = 0.

<sup>2:</sup> Configuration SFR, overlaps with default SFR at this address; available only when WDTCON<4> = 1.

#### 18.1 ECCP Outputs and Configuration

Each of the Enhanced CCP modules may have up to four PWM outputs, depending on the selected operating mode. These outputs, designated PxA through PxD, are multiplexed with various I/O pins. Some ECCP pin assignments are constant, while others change based on device configuration. For those pins that do change, the controlling bits are:

- · CCP2MX Configuration bit

- ECCPMX Configuration bit (80-pin devices only)

- Program Memory Operating mode, set by the EMB Configuration bits (80-pin devices only)

The pin assignments for the Enhanced CCP modules are summarized in Table 18-1, Table 18-2 and Table 18-3. To configure the I/O pins as PWM outputs, the proper PWM mode must be selected by setting the PxMx and CCPxMx bits (CCPxCON<7:6> and <3:0>, respectively). The appropriate TRIS direction bits for the corresponding port pins must also be set as outputs.

## 18.1.1 ECCP1/ECCP3 OUTPUTS AND PROGRAM MEMORY MODE

In 80-pin devices, the use of Extended Microcontroller mode has an indirect effect on the use of ECCP1 and ECCP3 in Enhanced PWM modes. By default, PWM outputs, P1B/P1C and P3B/P3C, are multiplexed to PORTE pins along with the high-order byte of the External Memory Bus. When the bus is active in Extended Microcontroller mode, it overrides the Enhanced CCP outputs and makes them unavailable. Because of this, ECCP1 and ECCP3 can only be used in compatible (single output) PWM modes when the device is in Extended Microcontroller mode and default pin configuration.

An exception to this configuration is when a 12-bit address width is selected for the external bus (EMB1:EMB0 Configuration bits = 01). In this case, the upper pins of PORTE continue to operate as digital I/O, even when the external bus is active. P1B/P1C and P3B/P3C remain available for use as Enhanced PWM outputs.

If an application requires the use of additional PWM outputs during enhanced microcontroller operation, the P1B/P1C and P3B/P3C outputs can be reassigned to the upper bits of PORTH. This is done by clearing the ECCPMX Configuration bit.

## 18.1.2 ECCP2 OUTPUTS AND PROGRAM MEMORY MODES

For 80-pin devices, the program memory mode of the device (Section 5.1.3 "PIC18F87J50 Family Program Memory Modes") also impacts pin multiplexing for the module. The ECCP2 input/output (ECCP2/P2A) can be multiplexed to one of three pins. The default assignment (CCP2MX Configuration bit is set) for all devices is RC1. Clearing CCP2MX reassigns ECCP2/P2A to RE7.

An additional option exists for 80-pin devices. When these devices are operating in Microcontroller mode, the multiplexing options described above still apply. In Extended Microcontroller mode, clearing CCP2MX reassigns ECCP2/P2A to RB3.

Changing the pin assignment of ECCP2 does not automatically change any requirements for configuring the port pin. Users must always verify that the appropriate TRIS register is configured correctly for ECCP2 operation regardless of where it is located.

## 18.1.3 USE OF CCP4 AND CCP5 WITH ECCP1 AND ECCP3

Only the ECCP2 module has four dedicated output pins that are available for use. Assuming that the I/O ports or other multiplexed functions on those pins are not needed, they may be used whenever needed without interfering with any other CCP module.

ECCP1 and ECCP3, on the other hand, only have three dedicated output pins: ECCPx/PxA, PxB and PxC. Whenever these modules are configured for Quad PWM mode, the pin normally used for CCP4 or CCP5 becomes the PxD output pins for ECCP3 and ECCP1, respectively. The CCP4 and CCP5 modules remain functional but their outputs are overridden.

## 18.1.4 ECCP MODULES AND TIMER RESOURCES

Like the standard CCP modules, the ECCP modules can utilize Timers 1, 2, 3 or 4, depending on the mode selected. Timer1 and Timer3 are available for modules in Capture or Compare modes, while Timer2 and Timer4 are available for modules in PWM mode. Additional details on timer resources are provided in Section 17.1.1 "CCP Modules and Timer Resources".

#### 18.1.5 OPEN-DRAIN OUTPUT OPTION

When operating in compare or standard PWM modes, the drivers for the ECCPx pins can be optionally configured as open-drain outputs. This feature allows the voltage level on the pin to be pulled to a higher level through an external pull-up resistor, and allows the output to communicate with external circuits without the need for additional level shifters. For more information, see **Section 10.1.4** "Open-Drain Outputs".

The open-drain output option is controlled by the bits in the ODCON1 register. Setting the appropriate bit configures the pin for the corresponding module for open-drain operation. The ODCON1 memory shares the same address space as of TMR1H. The ODCON1 register can be accessed by setting the ADSHR bit in the WDTCON register (WDTCON<4>).

#### 18.4.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The PWM duty cycle is calculated by the following equation:

#### **EQUATION 18-2:**

CCPR1L and CCP1CON<5:4> can be written to at any time but the duty cycle value is not copied into CCPR1H until a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation. When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or two bits of the TMR2 prescaler, the ECCP1 pin is cleared. The maximum PWM resolution (bits) for a given PWM frequency is given by the equation:

#### **EQUATION 18-3:**

PWM Resolution (max) =

$$\frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)}$$

bits

Note: If the PWM duty cycle value is longer than the PWM period, the ECCP1 pin will not be cleared.

#### 18.4.3 PWM OUTPUT CONFIGURATIONS

The P1M1:P1M0 bits in the CCP1CON register allow one of four configurations:

- · Single Output

- · Half-Bridge Output

- · Full-Bridge Output, Forward mode

- · Full-Bridge Output, Reverse mode

The Single Output mode is the standard PWM mode discussed in **Section 18.4** "Enhanced PWM Mode". The Half-Bridge and Full-Bridge Output modes are covered in detail in the sections that follow.

The general relationship of the outputs in all configurations is summarized in Figure 18-2.

TABLE 18-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh      | FFh      | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8          | 7          | 6.58       |

#### REGISTER 19-2: SSPxCON1: MSSPx CONTROL REGISTER 1 (SPI MODE)

| R/W-0 | R/W-0                | R/W-0                | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|-------|----------------------|----------------------|-------|----------------------|----------------------|----------------------|----------------------|

| WCOL  | SSPOV <sup>(1)</sup> | SSPEN <sup>(2)</sup> | CKP   | SSPM3 <sup>(3)</sup> | SSPM2 <sup>(3)</sup> | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| bit 7 |                      |                      |       |                      |                      |                      | bit 0                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 WCOL: Write Collision Detect bit

1 = The SSPxBUF register is written while it is still transmitting the previous word (must be cleared in software)

0 = No collision

bit 6 SSPOV: Receive Overflow Indicator bit<sup>(1)</sup>

SPI Slave mode:

1 = A new byte is received while the SSPxBUF register is still holding the previous data. In case of overflow, the data in SSPxSR is lost. Overflow can only occur in Slave mode. The user must read the SSPxBUF, even if only transmitting data, to avoid setting overflow (must be cleared in software).

0 = No overflow

bit 5 SSPEN: Master Synchronous Serial Port Enable bit (2)

1 = Enables serial port and configures SCKx, SDOx, SDIx and  $\overline{SSx}$  as serial port pins

0 = Disables serial port and configures these pins as I/O port pins

bit 4 **CKP:** Clock Polarity Select bit

1 = Idle state for clock is a high level

0 = Idle state for clock is a low level

bit 3-0 **SSPM3:SSPM0:** Master Synchronous Serial Port Mode Select bits<sup>(3)</sup>

0101 = SPI Slave mode, clock = SCKx pin,  $\overline{SSx}$  pin control disabled,  $\overline{SSx}$  can be used as I/O pin

0100 = SPI Slave mode, clock = SCKx pin, SSx pin control enabled

0011 = SPI Master mode, clock = TMR2 output/2

0010 = SPI Master mode, clock = Fosc/64

0001 = SPI Master mode, clock = Fosc/16

0000 = SPI Master mode, clock = Fosc/4

**Note 1:** In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPxBUF register.

2: When enabled, this pin must be properly configured as input or output.

3: Bit combinations not specifically listed here are either reserved or implemented in I<sup>2</sup>C™ mode only.

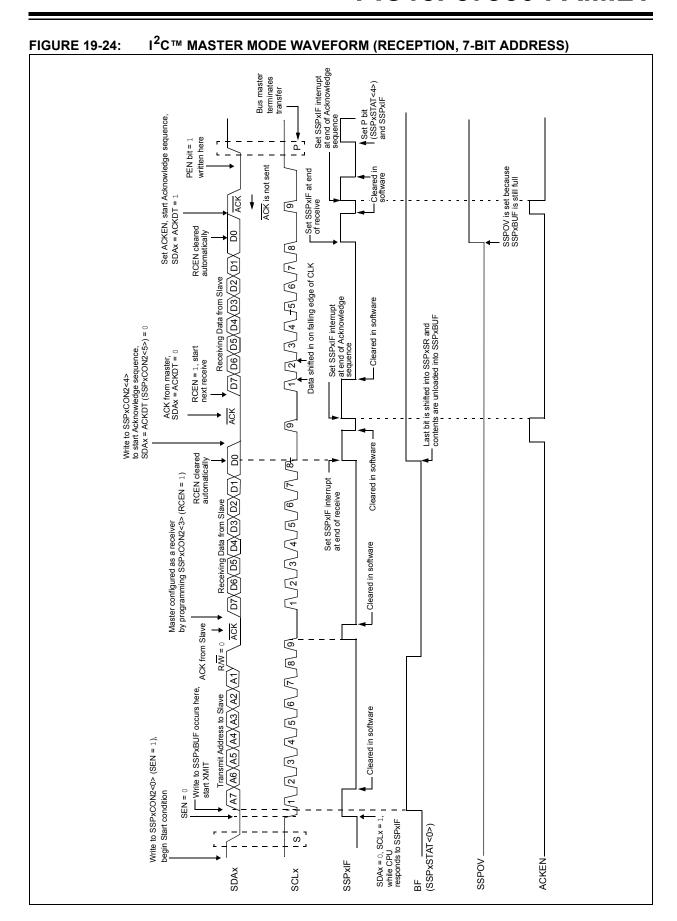

#### REGISTER 19-5: SSPxCON2: MSSPx CONTROL REGISTER 2 (I<sup>2</sup>C™ MASTER MODE)

| R/W-0 | R/W-0   | R/W-0                | R/W-0                | R/W-0               | R/W-0              | R/W-0               | R/W-0              |

|-------|---------|----------------------|----------------------|---------------------|--------------------|---------------------|--------------------|

| GCEN  | ACKSTAT | ACKDT <sup>(1)</sup> | ACKEN <sup>(2)</sup> | RCEN <sup>(2)</sup> | PEN <sup>(2)</sup> | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup> |

| bit 7 |         |                      |                      |                     |                    |                     | bit 0              |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 **GCEN:** General Call Enable bit (Slave mode only)

1 = Enable interrupt when a general call address (0000h) is received in the SSPxSR

0 = General call address disabled

bit 6 ACKSTAT: Acknowledge Status bit (Master Transmit mode only)

1 = Acknowledge was not received from slave

0 = Acknowledge was received from slave

bit 5 ACKDT: Acknowledge Data bit (Master Receive mode only)<sup>(1)</sup>

1 = Not Acknowledge

0 = Acknowledge

bit 4 ACKEN: Acknowledge Sequence Enable bit<sup>(2)</sup>

1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit. Automatically cleared by hardware.

0 = Acknowledge sequence Idle

bit 3 RCEN: Receive Enable bit (Master Receive mode only)(2)

1 = Enables Receive mode for I<sup>2</sup>C

0 = Receive Idle

bit 2 **PEN:** Stop Condition Enable bit<sup>(2)</sup>

1 = Initiates Stop condition on SDAx and SCLx pins. Automatically cleared by hardware.

0 = Stop condition Idle

bit 1 RSEN: Repeated Start Condition Enable bit<sup>(2)</sup>

1 = Initiates Repeated Start condition on SDAx and SCLx pins. Automatically cleared by hardware.

0 = Repeated Start condition Idle

bit 0 **SEN:** Start Condition Enable bit<sup>(2)</sup>

1 = Initiates Start condition on SDAx and SCLx pins. Automatically cleared by hardware.

0 = Start condition Idle

Note 1: Value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.

2: If the I<sup>2</sup>C module is active, these bits may not be set (no spooling) and the SSPxBUF may not be written (or writes to the SSPxBUF are disabled).

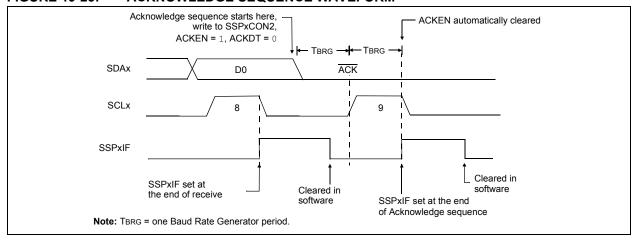

## 19.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit. **ACKEN** (SSPxCON2<4>). When this bit is set, the SCLx pin is pulled low and the contents of the Acknowledge data bit are presented on the SDAx pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCLx pin is deasserted (pulled high). When the SCLx pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG; the SCLx pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into an inactive state (Figure 19-25).

#### 19.4.12.1 WCOL Status Flag

If the user writes the SSPxBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

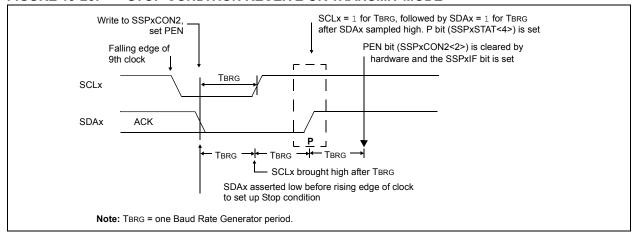

#### 19.4.13 STOP CONDITION TIMING

A Stop bit is asserted on the SDAx pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPxCON2<2>). At the end of a receive/transmit, the SCLx line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDAx line low. When the SDAx line is sampled low, the Baud Rate Generator is reloaded and counts down to 0. When the Baud Rate Generator times out, the SCLx pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDAx pin will be deasserted. When the SDAx pin is sampled high while SCLx is high, the P bit (SSPxSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPxIF bit is set (Figure 19-26).

#### 19.4.13.1 WCOL Status Flag

If the user writes the SSPxBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 19-25: ACKNOWLEDGE SEQUENCE WAVEFORM

#### FIGURE 19-26: STOP CONDITION RECEIVE OR TRANSMIT MODE

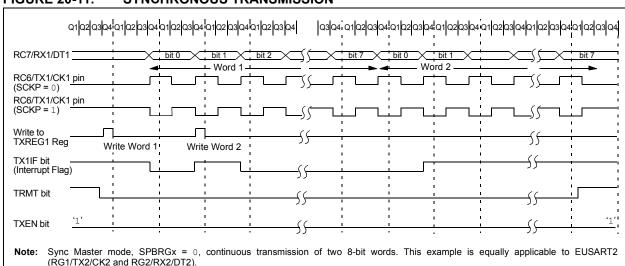

#### 20.3 EUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTAx<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTAx<4>). In addition, enable bit, SPEN (RCSTAx<7>), is set in order to configure the TXx and RXx pins to CKx (clock) and DTx (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CKx line. Clock polarity is selected with the SCKP bit (BAUDCONx<4>). Setting SCKP sets the Idle state on CKx as high, while clearing the bit sets the Idle state as low. This option is provided to support Microwire devices with this module.

## 20.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 20-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREGx. The TXREGx register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREGx (if available).

Once the TXREGx register transfers the data to the TSR register (occurs in one Tcy), the TXREGx is empty and the TXxIF flag bit is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TXxIE. TXxIF is set regardless of the state of enable bit, TXxIE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREGx register.

While flag bit, TXxIF, indicates the status of the TXREGx register, another bit, TRMT (TXSTAx<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user must poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- If interrupts are desired, set enable bit, TXxIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are

#### 21.1 A/D Acquisition Requirements

For the A/D Converter to meet its specified accuracy, the charge holding capacitor (Chold) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 21-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor Chold. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . After the analog input channel is selected (changed), the channel must be sampled for at least the minimum acquisition time before starting a conversion.

**Note:** When the conversion is started, the holding capacitor is disconnected from the input pin.

To calculate the minimum acquisition time, Equation 21-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

Equation 21-3 shows the calculation of the minimum required acquisition time, TACQ. This calculation is based on the following application system assumptions:

CHOLD = 25 pF Rs =  $2.5 \text{ k}\Omega$ Conversion Error  $\leq$  1/2 LSb

VDD =  $3V \rightarrow Rss = 2 \text{ k}\Omega$ Temperature =  $85^{\circ}\text{C}$  (system max.)

#### **EQUATION 21-1: ACQUISITION TIME**

```

TACQ = Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient

= TAMP + TC + TCOFF

```

#### **EQUATION 21-2: A/D MINIMUM CHARGING TIME**

```

\begin{array}{lll} V_{HOLD} & = & (V_{REF} - (V_{REF}/2048)) \bullet (1 - e^{(-T_{C}/C_{HOLD}(R_{IC} + R_{SS} + R_{S}))}) \\ \text{or} \\ T_{C} & = & -(C_{HOLD})(R_{IC} + R_{SS} + R_{S}) \ln(1/2048) \end{array}

```

#### **EQUATION 21-3: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME**

```

TACO

TAMP + TC + TCOFF

TAMP

0.2 \mu s

TCOFF

(Temp - 25^{\circ}C)(0.02 \mu s/^{\circ}C)

(85^{\circ}C - 25^{\circ}C)(0.02 \,\mu\text{s}/^{\circ}C)

1.2 \mu s

Temperature coefficient is only required for temperatures > 25°C. Below 25°C, TCOFF = 0 ms.

TC

-(CHOLD)(RIC + RSS + RS) \ln(1/2048) µs

-(25 \text{ pF}) (1 \text{ k}\Omega + 2 \text{ k}\Omega + 2.5 \text{ k}\Omega) \ln(0.0004883) \text{ }\mu\text{s}

1.05 \mu s

0.2 \mu s + 1.05 \mu s + 1.2 \mu s

TACQ

2.45 \mu s

```

# 22.0 UNIVERSAL SERIAL BUS (USB)

This section describes the details of the USB peripheral. Because of the very specific nature of the module, knowledge of USB is expected. Some high-level USB information is provided in **Section 22.9** "Overview of USB" only for application design reference. Designers are encouraged to refer to the official specification published by the USB Implementers Forum (USB-IF) for the latest information. USB Specification Revision 2.0 is the most current specification at the time of publication of this document.

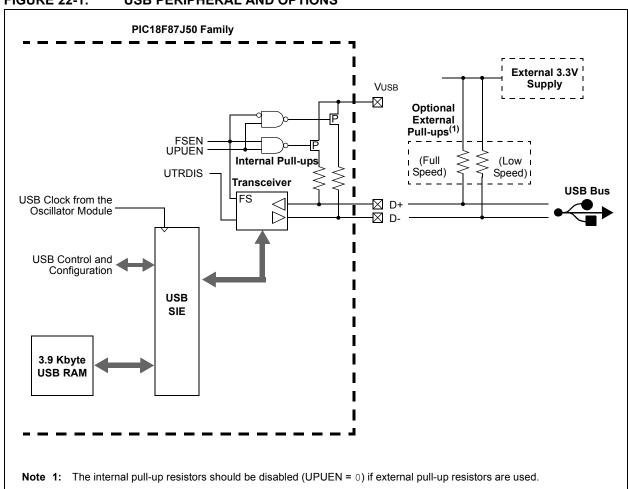

#### 22.1 Overview of the USB Peripheral

PIC18F87J10 family devices contain a full-speed and low-speed, compatible USB Serial Interface Engine (SIE) that allows fast communication between any USB host and the PIC® microcontroller. The SIE can be interfaced directly to the USB, utilizing the internal transceiver.

Some special hardware features have been included to improve performance. Dual access port memory in the device's data memory space (USB RAM) has been supplied to share direct memory access between the microcontroller core and the SIE. Buffer descriptors are also provided, allowing users to freely program endpoint memory usage within the USB RAM space. Figure 22-1 presents a general overview of the USB peripheral and its features.

FIGURE 22-1: USB PERIPHERAL AND OPTIONS

© 2009 Microchip Technology Inc.

#### 23.6 Comparator Interrupts

The comparator interrupt flag is set whenever any of the following occurs:

- Low-to-high transition of the comparator output

- High-to-low transition of the comparator output

- Any change in the comparator output.

The comparator interrupt selection is done by the EVPOL1:EVPOL0 bits in the CMxCON register (CMxCON<4:3>).

In order to provide maximum flexibility, the output of the comparator may be inverted using the CPOL bit in the CMxCON register (CMxCON<5>). This is functionally identical to reversing the inverting and non-inverting inputs of the comparator for a particular mode.

An interrupt is generated on the low-to-high or high-to-low transition of the comparator output. This mode of interrupt generation is dependent on EVPOL<1:0> in the CMxCON register. When EVPOL<1:0> = 01 or 10, the interrupt is generated on a low-to-high or high-to-

low transition of the comparator output. Once the interrupt is generated, it is required to clear the interrupt flag by software.

When EVPOL<1:0> = 11, the comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMSTAT<1:0>, to determine the actual change that occurred. The CMxIF bits (PIR2<6:5>) are the Comparator Interrupt Flags. The CMxIF bits must be reset by clearing them. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated. Table 23-2 shows the interrupt generation with respect to comparator input voltages and EVPOL bit settings.

Both the CMxIE bits (PIE2<6:5>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit (INTCON<7>) must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMxIF bits will still be set if an interrupt condition occurs. A simplified diagram of the interrupt section is shown in Figure 23-3.

**TABLE 23-2: COMPARATOR INTERRUPT GENERATION**

| CPOL | EVPOL<1:0> | Comparator<br>Input Change | COUTx Transition | Interrupt<br>Generated |

|------|------------|----------------------------|------------------|------------------------|

|      | 00         | VIN+ > VIN-                | Low-to-High      | No                     |

|      | 00         | VIN+ < VIN-                | High-to-Low      | No                     |

|      | 0.1        | VIN+ > VIN-                | Low-to-High      | Yes                    |

| 0    | 01         | VIN+ < VIN-                | High-to-Low      | No                     |

| U    | 1.0        | VIN+ > VIN-                | Low-to-High      | No                     |

|      | 10         | VIN+ < VIN-                | High-to-Low      | Yes                    |

|      | 11         | VIN+ > VIN-                | Low-to-High      | Yes                    |

|      |            | VIN+ < VIN-                | High-to-Low      | Yes                    |

|      | 0.0        | VIN+ > VIN-                | High-to-Low      | No                     |

|      | 00         | VIN+ < VIN-                | Low-to-High      | No                     |

|      | 0.1        | VIN+ > VIN-                | High-to-Low      | No                     |

| 1    | 01         | VIN+ < VIN-                | Low-to-High      | Yes                    |

| 1    | 1.0        | VIN+ > VIN-                | High-to-Low      | Yes                    |

|      | 10         | VIN+ < VIN-                | Low-to-High      | No                     |

|      | 1.1        | VIN+ > VIN-                | High-to-Low      | Yes                    |

|      | 11         | VIN+ < VIN-                | Low-to-High      | Yes                    |

#### ADDWFC ADD W and Carry bit to f

$\label{eq:Syntax: ADDWFC f {d {a}}} Syntax: \qquad ADDWFC \qquad f {d {a}}$  Operands:  $0 \leq f \leq 255 \\ d \in [0,1] \\ a \in [0,1]$

Operation:  $(W) + (f) + (C) \rightarrow dest$ Status Affected: N,OV, C, DC, Z

Encoding: 0010 00da ffff ffff

Description: Add W, the Carry flag and data memory location 'f'. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed in data memory location 'f'.

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the

GPR bank (default).

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See Section 26.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.

Words: 1 Cycles: 1

Q Cycle Activity:

| Q1           | Q1 Q2 |         | Q4          |  |

|--------------|-------|---------|-------------|--|

| Decode Read  |       | Process | Write to    |  |

| register 'f' |       | Data    | destination |  |

Example: ADDWFC REG, 0, 1

50h

Before Instruction

Carry bit = 1

REG = 02h

W = 4Dh

After Instruction

Carry bit = 0

REG = 02h

ANDLW AND Literal with W

Status Affected: N, Z

Encoding: 0000 1011 kkkk kkkk

Description: The contents of W are ANDed with the 8-bit literal 'k'. The result is placed in W.

Words: 1

Cycles: 1

Q Cycle Activity:

| Q1     | Q2                  | Q3   | Q4       |

|--------|---------------------|------|----------|

| Decode | Decode Read literal |      | Write to |

|        | 'k'                 | Data | W        |

Example: ANDLW 05Fh

Before Instruction W = A3h

After Instruction

W = 03h

**FIGURE 28-6:** PROGRAM MEMORY READ TIMING DIAGRAM Q1 Q2 Q3 Q4 Q1 Q2 OSC1 A<19:16> Address Address BA0 AD<15:0> Address Data from External Address 162 166 **←**168 → ALE 169 CE OE Operating Conditions: 2.0V < VDD < 3.6V, -40°C < TA < +85°C unless otherwise stated.

TABLE 28-11: PROGRAM MEMORY READ TIMING REQUIREMENTS

| Param.<br>No | Symbol   | Characteristics                                                           | Min            | Тур       | Max            | Units |

|--------------|----------|---------------------------------------------------------------------------|----------------|-----------|----------------|-------|

| 150          | TadV2alL | Address Out Valid to ALE ↓ (address setup time)                           | 0.25 Tcy - 10  | _         | _              | ns    |

| 151          | TalL2adl | ALE ↓ to Address Out Invalid (address hold time)                          | 5              |           | _              | ns    |

| 155          | TalL2oeL | ALE ↓ to <del>OE</del> ↓                                                  | 10             | 0.125 TcY | _              | ns    |

| 160          | TadZ2oeL | AD high-Z to $\overline{OE} \downarrow$ (bus release to $\overline{OE}$ ) | 0              | _         | _              | ns    |

| 161          | ToeH2adD | OE ↑ to AD Driven                                                         | 0.125 Tcy - 5  | _         | _              | ns    |

| 162          | TadV2oeH | Least Significant Data Valid before OE ↑ (data setup time)                | 20             | _         | _              | ns    |

| 163          | ToeH2adl | OE ↑ to Data In Invalid (data hold time)                                  | 0              | _         | _              | ns    |

| 164          | TalH2alL | ALE Pulse Width                                                           | _              | 0.25 TcY  | _              | ns    |

| 165          | ToeL2oeH | OE Pulse Width                                                            | 0.5 Tcy - 5    | 0.5 Tcy   | _              | ns    |

| 166          | TalH2alH | ALE ↑ to ALE ↑ (cycle time)                                               | _              | Tcy       | _              | ns    |

| 167          | Tacc     | Address Valid to Data Valid                                               | 0.75 Tcy - 25  | _         | _              | ns    |

| 168          | Toe      | OE ↓ to Data Valid                                                        |                |           | 0.5 Tcy - 25   | ns    |

| 169          | TalL2oeH | ALE ↓ to <del>OE</del> ↑                                                  | 0.625 Tcy - 10 | -         | 0.625 Tcy + 10 | ns    |

| 171          | TalH2csL | Chip Enable Active to ALE ↓                                               | 0.25 Tcy - 20  | _         | _              | ns    |

| 171A         | TubL2oeH | AD Valid to Chip Enable Active                                            | _              | _         | 10             | ns    |