#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | H8/300                                                                          |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 16MHz                                                                           |

| Connectivity               | Host Interface, I <sup>2</sup> C, SCI                                           |

| Peripherals                | POR, PWM, WDT                                                                   |

| Number of I/O              | 74                                                                              |

| Program Memory Size        | 60KB (60K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                             |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 80-BQFP                                                                         |

| Supplier Device Package    | 80-QFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd64f3337sf16v |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.5.3 Logic Operations

Table 2.6 describes the four instructions that perform logic operations. See figure 2.6 in section 2.5.4, Shift Operations, for their object codes.

| Instruction     | Size*        | Function                                                                                                        |

|-----------------|--------------|-----------------------------------------------------------------------------------------------------------------|

| AND             | В            | $Rd \land Rs \to Rd,  Rd \land \#imm \to Rd$                                                                    |

|                 |              | Performs a logical AND operation on a general register and another general register or immediate data.          |

| OR              | В            | $Rd \lor Rs \to Rd,  Rd \lor \#imm \to Rd$                                                                      |

|                 |              | Performs a logical OR operation on a general register and another general register or immediate data.           |

| XOR             | В            | $Rd \oplus Rs \to Rd, Rd \oplus \#imm \to Rd$                                                                   |

|                 |              | Performs a logical exclusive OR operation on a general register and another general register or immediate data. |

| NOT             | В            | $\neg (Rd) \to (Rd)$                                                                                            |

|                 |              | Obtains the one's complement (logical complement) of general register contents.                                 |

| Note: * Size: C | Dperand size |                                                                                                                 |

Note: \* Size: Operand size B: Byte

### 2.5.4 Shift Operations

Table 2.7 describes the eight shift instructions. Figure 2.6 shows the object code formats of the arithmetic, logic, and shift instructions.

### Table 2.7Shift Instructions

| Instruction   | Size* | Function                                                             |

|---------------|-------|----------------------------------------------------------------------|

| SHAL          | В     | $Rd shift \to Rd$                                                    |

| SHAR          |       | Performs an arithmetic shift operation on general register contents. |

| SHLL          | В     | $Rd shift \to Rd$                                                    |

| SHLR          |       | Performs a logical shift operation on general register contents.     |

| ROTL          | В     | Rd rotate $\rightarrow$ Rd                                           |

| ROTR          |       | Rotates general register contents.                                   |

| ROTXL         | В     | Rd rotate through carry $\rightarrow$ Rd                             |

| ROTXR         |       | Rotates general register contents through the C (carry) bit.         |

| Nata & Olar C |       |                                                                      |

Note: \* Size: Operand size

B: Byte

**Bit 0—RAM Enable (RAME):** Enables or disables the on-chip RAM. The RAME bit is initialized by a reset, but is not initialized in the software standby mode.

| Bit 0: RAME | Description                  |                 |

|-------------|------------------------------|-----------------|

| 0           | The on-chip RAM is disabled. |                 |

| 1           | The on-chip RAM is enabled.  | (Initial value) |

# **3.3** Mode Control Register (MDCR)

| Bit           | 7                  | 6 | 5 | 4 | 3 | 2 | 1    | 0    |

|---------------|--------------------|---|---|---|---|---|------|------|

|               | EXPE <sup>*1</sup> | _ | — |   | — | — | MDS1 | MDS0 |

| Initial value | *2                 | 1 | 1 | 0 | 0 | 1 | *2   | *2   |

| Read/Write    | R/W*2              | _ | _ | _ | _ | _ | R    | R    |

Notes: \*1 H8/3337SF (S-mask model, single-power-supply on-chip flash memory version) only. Otherwise, this is a reserved bit that is always read as 1.

\*2 Determined by the mode pins ( $MD_1$  and  $MD_0$ ).

The mode control register (MDCR) is an 8-bit register that indicates the operating mode of the chip.

**Bit 7—Expanded Mode Enable (EXPE):** Functions only in the H8/3337SF (S-mask model, single-power-supply on-chip flash memory version). For details, see section 21.1.6, Mode Control Register (MDCR).

In models other than the H8/3337SF, this is a reserved bit that cannot be modified and is always read as 1.

Bits 6 and 5—Reserved: These bits cannot be modified and are always read as 1.

Bits 4 and 3—Reserved: These bits cannot be modified and are always read as 0.

Bit 2—Reserved: This bit cannot be modified and is always read as 1.

**Bits 1 and 0—Mode Select 1 and 0 (MDS1 and MDS0):** These bits indicate the values of the mode pins ( $MD_1$  and  $MD_0$ ), thereby indicating the current operating mode of the chip. MDS1 corresponds to  $MD_1$  and MDS0 to  $MD_0$ . These bits can be read but not written. When the mode control register is read, the levels at the mode pins ( $MD_1$  and  $MD_0$ ) are latched in these bits.

# 3.4 Address Space Map in Each Operating Mode

Figures 3.1 to 3.3 show memory maps of the H8/3337Y, H8/3336Y, H8/3334Y, H8/3397, H8/3396, and H8/3394 in modes 1, 2, and 3.

# RENESAS

66

**Bit 5—Input Capture Flag C (ICFC):** This status bit is set to 1 to flag input of a rising or falling edge of FTIC as selected by the IEDGC bit. When BUFEA = 0, this indicates capture of the FRC count in ICRC. When BUFEA = 1, however, the FRC count is not captured, so ICFC becomes simply an external interrupt flag. In other words, the buffer mode frees FTIC for use as a general-purpose interrupt signal (which can be enabled or disabled by the ICICE bit).

ICFC must be cleared by software. It is set by hardware, however, and cannot be set by software.

| Bit 5: ICFC | Description                                                                                                   |

|-------------|---------------------------------------------------------------------------------------------------------------|

| 0           | To clear ICFC, the CPU must read ICFC after it has been set to 1, then write a 0 in this bit. (Initial value) |

| 1           | This bit is set to 1 when an FTIC input signal is received.                                                   |

**Bit 4—Input Capture Flag D (ICFD):** This status bit is set to 1 to flag input of a rising or falling edge of FTID as selected by the IEDGD bit. When BUFEB = 0, this indicates capture of the FRC count in ICRD. When BUFEB = 1, however, the FRC count is not captured, so ICFD becomes simply an external interrupt flag. In other words, the buffer mode frees FTID for use as a general-purpose interrupt signal (which can be enabled or disabled by the ICIDE bit).

ICFD must be cleared by software. It is set by hardware, however, and cannot be set by software.

| Bit 4: ICFD | Description                                                                                                   |

|-------------|---------------------------------------------------------------------------------------------------------------|

| 0           | To clear ICFD, the CPU must read ICFD after it has been set to 1, then write a 0 in this bit. (Initial value) |

| 1           | This bit is set to 1 when an FTID input signal is received.                                                   |

**Bit 3—Output Compare Flag A (OCFA):** This status flag is set to 1 when the FRC value matches the OCRA value. This flag must be cleared by software. It is set by hardware, however, and cannot be set by software.

| Bit 3: OCFA | Description                                                                                                   |

|-------------|---------------------------------------------------------------------------------------------------------------|

| 0           | To clear OCFA, the CPU must read OCFA after it has been set to 1, then write a 0 in this bit. (Initial value) |

| 1           | This bit is set to 1 when FRC = OCRA.                                                                         |

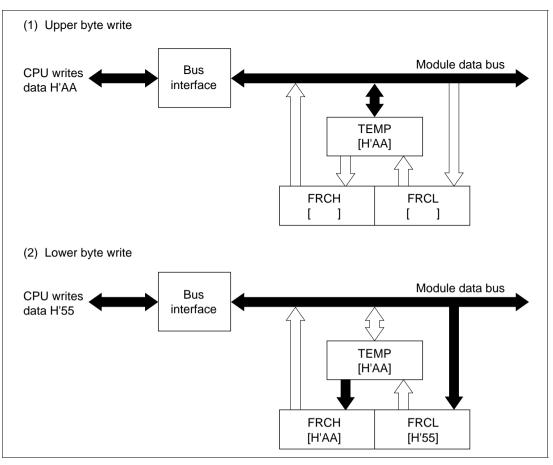

Figure 8.3 (a) Write Access to FRC (when CPU Writes H'AA55)

# 9.2 **Register Descriptions**

#### 9.2.1 **Timer Counter (TCNT)** Bit 7 4 2 1 0 6 5 3 0 0 0 0 0 0 0 Initial value 0 R/W R/W R/W R/W R/W R/W R/W R/W Read/Write

Each timer counter (TCNT) is an 8-bit up-counter that increments on a pulse generated from an internal or external clock source selected by clock select bits 2 to 0 (CKS2 to CKS0) of the timer control register (TCR). The CPU can always read or write the timer counter.

The timer counter can be cleared by an external reset input or by an internal compare-match signal generated at a compare-match event. Clock clear bits 1 and 0 (CCLR1 and CCLR0) of the timer control register select the method of clearing.

When a timer counter overflows from H'FF to H'00, the overflow flag (OVF) in the timer control/status register (TCSR) is set to 1.

The timer counters are initialized to H'00 by a reset and in the standby modes.

### 9.2.2 Time Constant Registers A and B (TCORA and TCORB)

TCORA and TCORB are 8-bit readable/writable registers. The timer count is continually compared with the constants written in these registers (except during the  $T_3$  state of a write cycle to TCORA or TCORB). When a match is detected, the corresponding compare-match flag (CMFA or CMFB) is set in the timer control/status register (TCSR).

The timer output signal is controlled by these compare-match signals as specified by output select bits 3 to 0 (OS3 to OS0) in the timer control/status register (TCSR).

TCORA and TCORB are initialized to H'FF by a reset and in the standby modes.

# Section 10 PWM Timers

# 10.1 Overview

The H8/3337 Series and H8/3397 Series have an on-chip pulse-width modulation (PWM) timer module with two independent channels (PWM0 and PWM1). Both channels are functionally identical. Each PWM channel generates a rectangular output pulse with a duty cycle of 0 to 100%. The duty cycle is specified in an 8-bit duty register (DTR).

### 10.1.1 Features

The PWM timer module has the following features:

- Selection of eight clock sources

- Duty cycles from 0 to 100% with 1/250 resolution

- Direct or inverted PWM output, and software enable/disable control

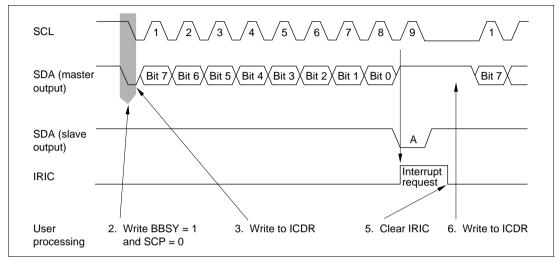

6. To continue transmitting, write the next transmit data in ICDR. Transmission of the next byte will begin in synchronization with the internal clock.

Steps 4 to 6 can be repeated to transmit data continuously. To end the transmission, write 0 in BBSY and 0 in SCP in ICSR. This generates a stop condition by causing a low-to-high transition of SDA while SCL is high.

Figure 13.6 Operation Timing in Master Transmit Mode (MLS = WAIT = ACK = 0)

### 14.2.7 Output Data Register 2 (ODR2)

| Bit              | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------------------|------|------|------|------|------|------|------|------|

|                  | ODR7 | ODR6 | ODR5 | ODR4 | ODR3 | ODR2 | ODR1 | ODR0 |

| Initial value    | —    | —    | —    | —    | —    | —    | —    | —    |

| Slave Read/Write | R/W  |

| Host Read/Write  | R    | R    | R    | R    | R    | R    | R    | R    |

ODR2 is an 8-bit read/write register to the slave processor, and an 8-bit read-only register to the host processor. The ODR2 contents are output on the host data bus when  $HA_0$  is low,  $\overline{CS}_2$  is low, and  $\overline{IOR}$  is low.

The initial values of ODR2 after a reset or standby are undetermined.

### 14.2.8 Status Register 2 (STR2)

| Bit              | 7   | 6   | 5   | 4   | 3                | 2   | 1   | 0   |

|------------------|-----|-----|-----|-----|------------------|-----|-----|-----|

|                  | DBU | DBU | DBU | DBU | $C/\overline{D}$ | DBU | IBF | OBF |

| Initial value    | 0   | 0   | 0   | 0   | 0                | 0   | 0   | 0   |

| Slave Read/Write | R/W | R/W | R/W | R/W | R                | R/W | R   | R   |

| Host Read/Write  | R   | R   | R   | R   | R                | R   | R   | R   |

STR2 is an 8-bit register that indicates status information during host interface processing. Bits 3, 1, and 0 are read-only bits to both the host and slave processors.

STR2 is initialized to H'00 by a reset and in hardware standby mode.

Bits 7 to 4 and Bit 2—Defined by User (DBU): The user can use these bits as necessary.

Bit 3—Command/Data (C/ $\overline{D}$ ): Receives the HA<sub>0</sub> input when the host processor writes to IDR2, and indicates whether IDR2 contains data or a command.

| Bit 3: C/D | Description                    |                 |

|------------|--------------------------------|-----------------|

| 0          | Contents of IDR2 are data      | (Initial value) |

| 1          | Contents of IDR2 are a command |                 |

# Renesas

|        | CMP.B<br>BEQ<br>BRA    | #H'32,<br>NGEND<br>PRGMS |                           | ; If p | 0            | ify executed 50 times?<br>erify executed 50 times, branch to NGEND<br>ain |

|--------|------------------------|--------------------------|---------------------------|--------|--------------|---------------------------------------------------------------------------|

| PVOK:  | BCLR<br>MOV.B<br>MOV.B | #2,<br>#H'00,<br>R6L,    | @FLMCR:<br>R6L<br>@EBR*:8 | ;      | ;<br>Clear E | Clear PV bit<br>BR*                                                       |

|        | One byte pro           | grammed                  |                           |        |              |                                                                           |

| NGEND: | Programming            | g error                  |                           |        |              |                                                                           |

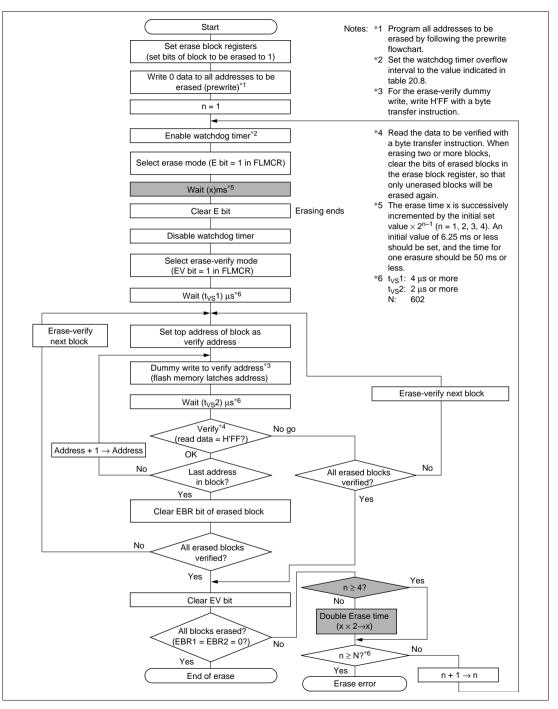

#### 19.4.4 Erase Mode

To erase the flash memory, follow the erasing algorithm shown in figure 19.11. This erasing algorithm can erase data without subjecting the device to voltage stress or impairing the reliability of programmed data.

To erase flash memory, before starting to erase, first place all memory data in all blocks to be erased in the programmed state (program all memory data to H'00). If all memory data is not in the programmed state, follow the sequence described later (figure 18-17) to program the memory data to zero. Select the flash memory areas to be erased with erase block registers 1 and 2 (EBR1 and EBR2). Next set the E bit in FLMCR, selecting erase mode. The erase time is the time during which the E bit is set. To prevent overerasing, use a software timer to divide the erase time into repeated 10 ms intervals, and perform erase operations a maximum of 3000 times so that the total erase time does not exceed 30 seconds. Overerasing, due to program runaway for example, can give memory cells a negative threshold voltage and cause them to operate incorrectly. Before selecting erase mode, set up the watchdog timer so as to prevent overerasing.

### 19.4.5 Erase-Verify Mode

In erase-verify mode, after data has been erased, it is read to check that it has been erased correctly. After the erase time has elapsed, exit erase mode (clear the E bit to 0) and select erase-verify mode (set the EV bit to 1). Before reading data in erase-verify mode, write H'FF dummy data to the address to be read. This dummy write applies an erase-verify voltage to the memory cells at the latched address. If the flash memory is read in this state, the data at the latched address will be read. After the dummy write, wait 2  $\mu$ s or more before reading. When performing the initial dummy write, wait 4  $\mu$ s or more after selecting erase-verify mode. If the read data has been successfully erased, perform an erase-verify (dummy write, wait 2  $\mu$ s or more, then read) for the next address. If the read data has not been erased, select erase mode again and repeat the same erase and erase-verify sequence through the last address. Do not repeat the erase and erase-verify sequence more than 3000 times, however.

# **19.5** Flash Memory Emulation by RAM

Erasing and programming flash memory takes time, which can make it difficult to tune parameters and other data in real time. If necessary, real-time updates of flash memory can be emulated by overlapping the small-block flash-memory area with part of the RAM (HFC00 to H'FD7F). This RAM reassignment is performed using bits 7 and 6 of the wait-state control register (WSCR).

After a flash memory area has been overlapped by RAM, the RAM area can be accessed from two address areas: the overlapped flash memory area, and the original RAM area (H'FC00 to H'FD7F). Table 19.11 indicates how to reassign RAM.

| Bit                         | 7    | 6    | 5     | 4   | 3    | 2    | 1   | 0   |

|-----------------------------|------|------|-------|-----|------|------|-----|-----|

|                             | RAMS | RAM0 | CKDBL |     | WMS1 | WMS0 | WC1 | WC0 |

| Initial value <sup>*1</sup> | 0    | 0    | 0     | 0   | 1    | 0    | 0   | 0   |

| Read/Write                  | R/W  | R/W  | R/W   | R/W | R/W  | R/W  | R/W | R/W |

### Wait-State Control Register (WSCR)<sup>\*2</sup>

Notes: \*1 WSCR is initialized by a reset and in hardware standby mode. It is not initialized in software standby mode.

\*2 For details of WSCR settings, see section 19.2.4, Wait-State Control Register (WSCR).

| Table 19.11 | RAM Area Selection |

|-------------|--------------------|

|-------------|--------------------|

| Bit 7: RAMS | Bit 6: RAMO | RAM Area         | ROM Area         |

|-------------|-------------|------------------|------------------|

| 0           | 0           | None             | _                |

|             | 1           | H'FC80 to H'FCFF | H'0080 to H'00FF |

| 1           | 0           | H'FC80 to H'FD7F | H'0080 to H'017F |

|             | 1           | H'FC00 to H'FC7F | H'0000 to H'007F |

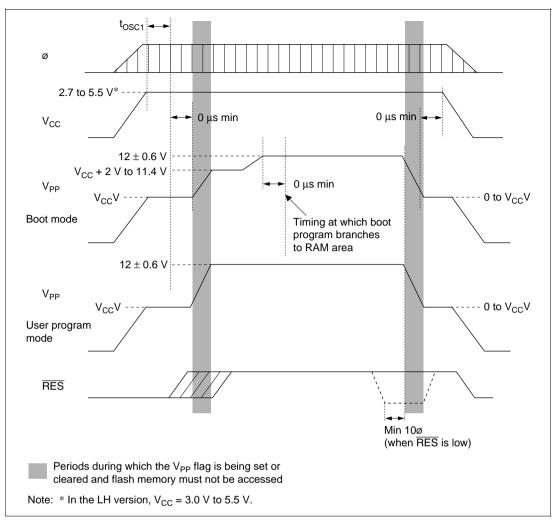

### Figure 19.20 V<sub>PP</sub> Power-On and Power-Off Timing

### (6) Do not apply 12 V to the $FV_{PP}$ pin during normal operation.

To prevent accidental programming or erasing due to microcontroller program runaway etc., apply 12 V to the  $V_{PP}$  pin only when the flash memory is programmed or erased, or when flash memory is emulated by RAM. Overprogramming or overerasing due to program runaway can cause memory cells to malfunction. Avoid system configurations in which 12 V is always applied to the FV<sub>PP</sub> pin.

While 12 V is applied, the watchdog timer should be running and enabled to halt runaway program execution, so that program runaway will not lead to overprogramming or overerasing.

#### 20.2.4 Wait-State Control Register (WSCR)

WSCR is an 8-bit readable/writable register that enables flash-memory updates to be emulated in RAM. It also controls frequency division of clock signals supplied to the on-chip supporting modules and insertion of wait states by the wait-state controller.

WSCR is initialized to H'08 by a reset and in hardware standby mode. It is not initialized in software standby mode.

| Bit           | 7    | 6    | 5     | 4   | 3    | 2    | 1   | 0   |

|---------------|------|------|-------|-----|------|------|-----|-----|

|               | RAMS | RAM0 | CKDBL | —   | WMS1 | WMS0 | WC1 | WC0 |

| Initial value | 0    | 0    | 0     | 0   | 1    | 0    | 0   | 0   |

| Read/Write    | R/W  | R/W  | R/W   | R/W | R/W  | R/W  | R/W | R/W |

**Bits 7 and 6—RAM Select and RAM0 (RAMS and RAM0):** These bits are used to reassign an area to RAM (see table 20.5). These bits are write-enabled and their initial value is 0. They are initialized by a reset and in hardware standby mode. They are not initialized in software standby mode.

If only one of bits 7 and 6 is set, part of the RAM area can be overlapped onto the small-block flash memory area. In that case, access is to RAM, not flash memory, and all flash memory blocks are write/erase-protected (emulation protect<sup>\*1</sup>). In this state, the mode cannot be changed to program or erase mode, even if the P bit or E bit in the flash memory control register (FLMCR) is set (although verify mode can be selected). Therefore, clear both of bits 7 and 6 before programming or erasing the flash memory area.

If both of bits 7 and 6 are set, part of the RAM area can be overlapped onto the small-block flash memory area, but this overlapping begins only when an interrupt signal is input while 12 V is being applied to the  $FV_{PP}$  pin. Up until that point, flash memory is accessed. Use this setting for interrupt handling while flash memory is being programmed or erased.<sup>\*2</sup>

| Bit 7: RAMS | Bit 6: RAM0 | RAM Area         | ROM Area         |

|-------------|-------------|------------------|------------------|

| 0           | 0           | None             | _                |

|             | 1           | H'F880 to H'F8FF | H'0080 to H'00FF |

| 1           | 0           | H'F880 to H'F97F | H'0080 to H'017F |

|             | 1           | H'F800 to H'F87F | H'0000 to H'007F |

### Table 20.5 RAM Area Reassignment\*3

#### **Flowchart for Erasing Multiple Blocks**

Figure 20.11 Multiple-Block Erase Flowchart

|           | Mode 1                 | Mode 2                   | Mode 3                         |  |  |  |  |

|-----------|------------------------|--------------------------|--------------------------------|--|--|--|--|

| FLSHE = 1 | Reserved area          | Flash memory control reg | ister initial values           |  |  |  |  |

|           | (always H'FF)          | FLLMCR1 = H'80           |                                |  |  |  |  |

|           |                        | FLMCR2 = H'00            |                                |  |  |  |  |

|           |                        | EBR2 = H'00              |                                |  |  |  |  |

| FLSHE = 0 | External address space | External address space   | Reserved area<br>(always H'FF) |  |  |  |  |

Table 21.22

Area Accessed in Each Mode with FLSHE = 0 and FLSHE = 1

2. When a flash memory control register is accessed in mode 2 (expanded mode with on-chip ROM enabled)

When a flash memory control register is accessed in mode 2, it can be read or written to if FLSHE = 1, but if FLSHE = 0, external address space will be accessed. It is therefore essential to confirm that FLSHE is set to 1 before accessing these registers.

3. To check whether FLSHE = 0 or 1 in mode 3 (single-chip mode) When address H'FF80 is accessed in mode 3, if FLSHE = 1, FLMCR1 is read/written to, and its initial value after a reset is H'80. When FLSHE = 0, however, this address is a reserved area that cannot be modified and always reads H'FF.

### 22.3.3 Clock Settling Time for Exit from Software Standby Mode

Set bits STS2 to STS0 in SYSCR as follows:

Crystal oscillator

Set STS2 to STS0 for a settling time of at least 8 ms. Table 22.3 lists the settling times selected by these bits at several clock frequencies.

External clock

The STS bits can be set to any value. The shortest time setting (STS2=STS1=STS0=0) is recommended in most cases. When 1,024 states (STS2 to STS0 = 101) is selected, the following points should be noted.

If a period exceeding  $\phi/1,024$  (e.g.  $\phi/2,048$ ) is specified when selecting the 8-bit timer, PWM timer, or watchdog timer clock, the counter in the timer will not count up normally when 1,024 states is specified for the setting time. To avoid this problem, set the STS value just before the transition to software standby mode (before executing the SLEEP instruction), and re-set the value of STS2 to STS0 to a value from 000 to 100 directly after software standby mode is cleared by an interrupt.

|      |      |      | Settling<br>Time | System Clock Frequency (MHz) |      |      |      |      |      |      |       |       |

|------|------|------|------------------|------------------------------|------|------|------|------|------|------|-------|-------|

| STS2 | STS1 | STS0 | (States)         | 16                           | 12   | 10   | 8    | 6    | 4    | 2    | 1     | 0.5   |

| 0    | 0    | 0    | 8,192            | 0.51                         | 0.65 | 0.8  | 1.0  | 1.3  | 2.0  | 4.1  | 8.2   | 16.4  |

| 0    | 0    | 1    | 16,384           | 1.0                          | 1.3  | 1.6  | 2.0  | 2.7  | 4.1  | 8.2  | 16.4  | 32.8  |

| 0    | 1    | 0    | 32,768           | 2.0                          | 2.7  | 3.3  | 4.1  | 5.5  | 8.2  | 16.4 | 32.8  | 65.5  |

| 0    | 1    | 1    | 65,536           | 4.1                          | 5.5  | 6.6  | 8.2  | 10.9 | 16.4 | 32.8 | 65.5  | 131.1 |

| 1    | 0    | 0/—* | 131,072          | 8.2                          | 10.9 | 13.1 | 16.4 | 21.8 | 32.8 | 65.5 | 131.1 | 262.1 |

#### Table 22.3 Times Set by Standby Timer Select Bits (Unit: ms)

Note: Recommended values are printed in boldface.

\* F-ZTAT version/ZTAT and mask-ROM versions.

#### Table 23.3 DC Characteristics (4-V Version)

Conditions:  $V_{CC} = 4.0 \text{ V}$  to 5.5 V,  $AV_{CC} = 4.0 \text{ V}$  to 5.5  $V^{*1}$ ,  $V_{SS} = AV_{SS} = 0 \text{ V}$ ,  $Ta = -20^{\circ}\text{C}$  to  $+75^{\circ}\text{C}$  (regular specifications),  $Ta = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  (wide-range specifications)

| Item                  |                                                                                             |     | Symbol                          | Min                 | Тур | Мах                   | Unit | Test<br>Conditions                                                   |

|-----------------------|---------------------------------------------------------------------------------------------|-----|---------------------------------|---------------------|-----|-----------------------|------|----------------------------------------------------------------------|

| Schmitt               |                                                                                             | (1) | $V_{T}^{-}$                     | 1.0                 | _   | _                     | V    | $V_{cc}$ = 4.5 V to                                                  |

| trigger input         | $\overline{IRQ}_2$ to $\overline{IRQ}_0^{*5}$ ,<br>$\overline{IRQ}_7$ to $\overline{IRQ}_3$ |     | $V_{T}^{+}$                     | _                   | —   | $V_{cc} 	imes 0.7$    |      | 5.5 V                                                                |

| voltage               |                                                                                             |     | $V_{T}^{+}-V_{T}^{-}$           | 0.4                 | —   | _                     | _    |                                                                      |

|                       |                                                                                             |     | V <sub>T</sub> <sup>-</sup>     | 0.8                 | _   | _                     | _    | $V_{\rm CC}$ = 4.0 V to                                              |

|                       |                                                                                             |     | V <sub>T</sub> <sup>+</sup>     | _                   | _   | $V_{cc} 	imes 0.7$    | _    | 4.5 V                                                                |

|                       |                                                                                             |     | $V_{\rm T}^{^+}-V_{\rm T}^{^-}$ | 0.3                 | —   | _                     |      |                                                                      |

| Input high<br>voltage | RES, STBY,<br>MD <sub>1</sub> , MD <sub>0</sub> ,<br>EXTAL, NMI                             | (2) | V <sub>IH</sub>                 | $V_{cc} - 0.7$      | _   | V <sub>cc</sub> + 0.3 | V    |                                                                      |

|                       | SCL, SDA                                                                                    |     |                                 | $V_{cc} \times 0.7$ | —   | V <sub>cc</sub> + 0.3 | _    |                                                                      |

|                       | $P7_7$ to $P7_0$                                                                            |     |                                 | 2.0                 |     | $AV_{cc}$ + 0.3       | _    |                                                                      |

|                       | All input pins oth<br>than (1) and (2)<br>above                                             | er  |                                 | 2.0                 | _   | V <sub>cc</sub> + 0.3 |      |                                                                      |

| Input low<br>voltage  | $\overline{\text{RES}}, \overline{\text{STBY}}, \\ \text{MD}_1, \text{MD}_0$                | (3) | V <sub>IL</sub>                 | -0.3                |     | 0.5                   | V    |                                                                      |

|                       | SCL, SDA                                                                                    |     |                                 | -0.3                | —   | 1.0                   |      | V <sub>cc</sub> = 4.5 V to<br>5.5 V                                  |

|                       |                                                                                             |     |                                 | -0.3                | —   | 0.8                   |      | V <sub>cc</sub> = 4.0 V to<br>4.5 V                                  |

|                       | All input pins oth than (1) and (3)                                                         | er  | _                               | -0.3                | —   | 0.8                   |      | V <sub>cc</sub> = 4.5 V to<br>5.5 V                                  |

|                       | above                                                                                       |     |                                 | -0.3                | —   | 0.6                   |      | V <sub>cc</sub> = 4.0 V to<br>4.5 V                                  |

|                       | All output pins*6                                                                           |     | V <sub>OH</sub>                 | $V_{cc} - 0.5$      | _   | _                     | V    | $I_{_{OH}}$ = -200 $\mu$ A                                           |

| voltage               |                                                                                             |     |                                 | 3.5                 | _   | _                     |      | $I_{OH} = -1.0 \text{ mA},$<br>$V_{CC} = 4.5 \text{ V to}$<br>5.5 V  |

|                       |                                                                                             |     |                                 | 2.8                 |     | _                     | _    | $I_{OH} = -1.0 \text{ mA},$<br>$V_{CC} = 4.0 \text{ V to}$<br>4.5  V |

#### Table 23.18 Allowable Output Current Values (3-V Version)

Conditions:  $V_{CC} = 3.0$  to 5.5 V,  $AV_{CC} = 3.0$  V to 5.5 V,  $V_{SS} = AV_{SS} = 0$  V,  $Ta = -20^{\circ}C$  to  $+75^{\circ}C$  (regular specifications),  $Ta = -40^{\circ}C$  to  $+85^{\circ}C$  (wide-range specifications)

| Item                                    |                                   | Symbol            | Min | Тур | Max | Unit |

|-----------------------------------------|-----------------------------------|-------------------|-----|-----|-----|------|

| Allowable output low current (per pin)  | SCL, SDA<br>(bus drive selection) | I <sub>ol</sub>   | _   | —   | 10  | mA   |

|                                         | Ports 1 and 2                     |                   | _   | _   | 2   |      |

|                                         | Other output pins                 |                   | _   | _   | 1   |      |

| Allowable output low                    | Ports 1 and 2, total              | $\Sigma I_{OL}$   | —   | _   | 40  | mA   |

| current (total)                         | Total of all output               |                   | _   | —   | 60  |      |

| Allowable output high current (per pin) | All output pins                   | —І <sub>он</sub>  | —   | —   | 2   | mA   |

| Allowable output high current (total)   | Total of all output               | $\Sigma - I_{OH}$ | —   | —   | 30  | mA   |

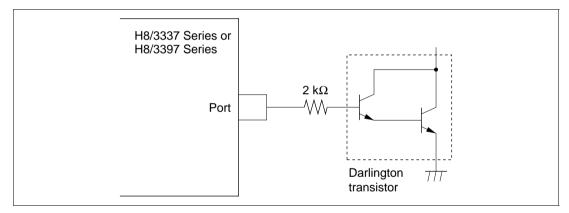

Figure 23.4 Example of Circuit for Driving a Darlington Transistor (5-V Version)

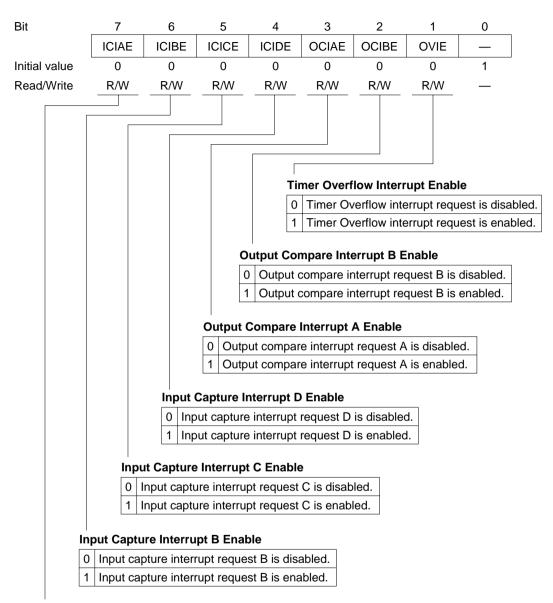

#### **TIER—Timer Interrupt Enable Register**

H'90

#### Input Capture Interrupt A Enable

| 0 Input capture interrupt request A is disabled |

|-------------------------------------------------|

|-------------------------------------------------|

1 Input capture interrupt request A is enabled.

H'97

#### **Output Compare Register Select**

| 0 | OCRA is selected. |

|---|-------------------|

| 1 | OCRB is selected. |

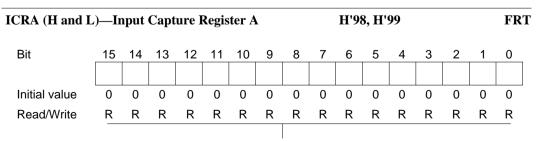

Contains FRC count captured on FTIA input.

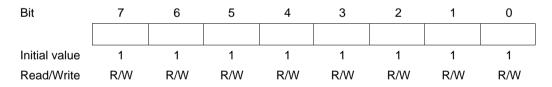

### P9DR—Port 9 Data Register

H'C1

Port 9

| Bit           | 7               | 6               | 5               | 4               | 3               | 2               | 1               | 0               |

|---------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

|               | P9 <sub>7</sub> | P9 <sub>6</sub> | P9 <sub>5</sub> | P9 <sub>4</sub> | P9 <sub>3</sub> | P9 <sub>2</sub> | P9 <sub>1</sub> | P9 <sub>0</sub> |

| Initial value | 0               | *               | 0               | 0               | 0               | 0               | 0               | 0               |

| Read/Write    | R/W             | R               | R/W             | R/W             | R/W             | R/W             | R/W             | R/W             |

Note: \* Depends on the level of pin  $P9_6$ .