### E. Aralog Devices Inc./Maxim Integrated - MAXQ7667AACM/V+T Datasheet

Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                  |

| Core Processor             | -                                                                    |

| Core Size                  | 16-Bit                                                               |

| Speed                      | 16MHz                                                                |

| Connectivity               | LINbus, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                     |

| Number of I/O              | 16                                                                   |

| Program Memory Size        | 32KB (16K x 16)                                                      |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 2K x 16                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.25V ~ 2.75V                                                        |

| Data Converters            | A/D 5x12b                                                            |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 48-LQFP                                                              |

| Supplier Device Package    | 48-LQFP (7x7)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/maxq7667aacm-v-t |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **ABSOLUTE MAXIMUM RATINGS**

DVDDIO, GATE5, REG3P3, REG2P5 to

| DGND                           | 0.3V to +6.0V                        |

|--------------------------------|--------------------------------------|

| AVDD to AGND                   | 0.3V to +4.0V                        |

| DVDD to DGND                   | 0.3V to +3.0V                        |

| DVDDIO to DVDD                 | 0.3V to +6.0V                        |

| AVDD to DVDD                   | 0.3V to +4.0V                        |

| AGND to DGND                   | 0.3V to +0.3V                        |

| Digital Inputs/Outputs to DGND | 0.3V to (V <sub>DVDDIO</sub> + 0.3V) |

| nalog Inputs/Outputs to AGND0.3V to (V <sub>AVDD</sub> + 0.3V) | )  |

|----------------------------------------------------------------|----|

| (IN, XOUT to DGND                                              | )  |

| Iaximum Current into Any Pin50mA                               | L. |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )          |    |

| 48-Pin LQFP (derate 21.7mW/°C above +70°C)1739.1mW             | 1  |

| Dperating Temperature Range40°C to +125°C                      | ;  |

| Storage Temperature Range60°C to +150°C                        |    |

| ead Temperature (soldering, 10s)+300°C                         | ;  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{DVDDIO} = +5V, V_{AVDD} = +3.3V; V_{DVDD} = +2.5V$ , system clock  $(f_{SYSCLK}) = 16MHz$ , burst frequency  $(f_{BURST}) =$  bandpass frequency  $(f_{BPF}) = 50$ kHz, CREFBG = CREF = 1µF in parallel with 0.01µF, f\_{ADCCLK} = 2MHz (SAR data rate = 125ksps), T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise specified. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                              | SYMBOL          | CONDI                                 | TIONS                                           | MIN | ТҮР                   | MAX | UNITS                    |

|----------------------------------------|-----------------|---------------------------------------|-------------------------------------------------|-----|-----------------------|-----|--------------------------|

| ECHO INPUT (Low-Noise Am               | plifier and s   | Sigma-Delta ADC)                      | ·                                               |     |                       |     |                          |

| Input-Referred Noise                   |                 | VGA gain adjust =                     | 1.55µV <sub>P-P</sub> /LSB                      |     | 5.6                   |     |                          |

| (Note 1)                               |                 | VGA gain adjust = (                   | ).1µV <sub>P-P</sub> /LSB                       |     | 0.7                   |     | - μV <sub>RMS</sub>      |

| Minimum Detectoble Cignel              |                 | VGA gain adjust = <sup>-</sup>        | 1.55µV <sub>P-P</sub> /LSB                      |     | 80                    |     |                          |

| Minimum Detectable Signal              |                 | VGA gain adjust = 0                   | ).1µV <sub>P-P</sub> /LSB                       |     | 10                    |     | - μV <sub>P-P</sub>      |

| Operating Input Range                  |                 | VGA gain adjust =<br>unclipped        | 1.55µV <sub>P-P</sub> /LSB,                     |     | 100                   |     | – mV <sub>P-P</sub>      |

| Operating input hange                  |                 | VGA gain adjust = (<br>unclipped      | D.1µV <sub>P-P</sub> /LSB,                      |     | 6.7                   |     | 11146-b                  |

| Programmable Gain                      |                 | From echo input to bandpass filter in | VGA gain adjust<br>= 1.55µV <sub>P-P</sub> /LSB |     | 1.55                  |     | – μV <sub>P-P</sub> /LSB |

| Frogrammable Gain                      |                 | reply to input                        | VGA gain adjust<br>= 0.1µV <sub>P-P</sub> /LSB  |     | 0.1                   |     | μνρ-ρ/μορ                |

| Programmable-Gain Adjust<br>Resolution |                 | (Note 2)                              |                                                 |     | 10                    |     | %                        |

| LNA Bandwidth                          |                 |                                       |                                                 |     | 150                   |     | kHz                      |

| ADC Sampling Rate                      |                 |                                       |                                                 |     | 80 x f <sub>BPF</sub> |     | kHz                      |

| ADC Output Data Rate                   |                 |                                       |                                                 |     | 10 x f <sub>BPF</sub> |     | kHz                      |

| ADC Output Data Resolution             |                 |                                       |                                                 |     | 16                    |     | Bits                     |

| Echo-Input Resistance                  | R <sub>IN</sub> | For each echo inpu                    | t                                               |     | 14                    |     | kΩ                       |

| Echo-Input Capacitance                 |                 |                                       |                                                 |     | 14                    |     | рF                       |

| Echo-Input DC Bias Voltage             |                 |                                       |                                                 |     | V <sub>AVDD</sub> /2  |     | V                        |

| Maximum Overvoltage<br>Recovery Time   |                 | Recover from 2V <sub>P-P</sub>        | input                                           |     | 10                    |     | μs                       |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DVDDIO} = +5V, V_{AVDD} = +3.3V; V_{DVDD} = +2.5V$ , system clock  $(f_{SYSCLK}) = 16MHz$ , burst frequency  $(f_{BURST}) =$  bandpass frequency  $(f_{BPF}) = 50kHz$ ,  $C_{REFBG} = C_{REF} = 1\mu$ F in parallel with  $0.01\mu$ F,  $f_{ADCCLK} = 2MHz$  (SAR data rate = 125ksps),  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise specified. Typical values are at  $T_A = +25^{\circ}$ C.)

| PARAMETER                             | SYMBOL  | CONDITIONS                                  | MIN                  | ТҮР                     | МАХ                  | UNITS     |

|---------------------------------------|---------|---------------------------------------------|----------------------|-------------------------|----------------------|-----------|

| BANDPASS FILTER                       |         |                                             | -                    |                         |                      |           |

| Center Frequency                      | fBPF    |                                             | 25                   |                         | 100                  | kHz       |

| Passband Width                        |         | -3dB                                        |                      | 0.14 x f <sub>BPF</sub> |                      | kHz       |

| Minimum Stopband<br>Rejection         |         | One decade away from center<br>frequency    |                      | -60                     |                      | dB        |

| Output Data Rate                      |         |                                             |                      | 10 x f <sub>BPF</sub>   |                      | ksps      |

| Output Data Resolution                |         |                                             |                      | 16                      |                      | Bits      |

| LOWPASS FILTER                        |         |                                             |                      |                         |                      |           |

| Corner Frequency                      | fLPF    | -3dB                                        |                      | 0.1 x f <sub>BPF</sub>  |                      | kHz       |

| Rolloff                               |         |                                             |                      | 40                      |                      | dB/Decade |

| Output Data Rate                      |         |                                             |                      | 5 x f <sub>BPF</sub>    |                      | ksps      |

| Output Data Resolution                |         |                                             |                      | 16                      |                      | Bits      |

| SAR ADC                               |         | ·                                           | ·                    |                         |                      |           |

| Resolution                            |         | Measurement                                 | 12                   |                         |                      | Bits      |

| Resolution                            |         | No missing codes                            | 11                   |                         |                      | DIIS      |

| Integral Nonlinearity                 |         | Tested at 125ksps                           |                      | ±1                      | ±2                   | LSB       |

| Differential Nonlinearity             |         | Tested at 125ksps                           | -2                   |                         | +2                   | LSB       |

| Offset Error                          |         |                                             |                      | ±1                      | ±3                   | mV        |

| Offset-Error Drift                    |         |                                             |                      | ±5                      |                      | µV/°C     |

| Gain Error                            |         |                                             |                      |                         | ±1                   | %         |

| Gain-Error Temperature<br>Coefficient |         |                                             |                      | ±0.4                    |                      | ppmFS/°C  |

| Input-Referred Noise                  |         | At ADC inputs                               |                      | 400                     |                      | μVrms     |

| Differential Innut Dance              |         | Unipolar                                    | 0                    |                         | V <sub>REF</sub>     | v         |

| Differential Input Range              |         | Bipolar                                     | -V <sub>REF</sub> /2 |                         | +V <sub>REF</sub> /2 |           |

| Absolute Input Range                  |         |                                             | 0                    |                         | VAVDD                | V         |

| Input Leakage Current                 |         |                                             |                      | ±0.1                    |                      | μA        |

| Conversion Time                       |         | 13 ADCCLK cycles at 2MHz                    |                      |                         | 6.5                  | μs        |

| Input Capacitance                     |         |                                             |                      | 14                      |                      | pF        |

| Track-and-Hold Acquisition<br>Time    |         | Three ADCCLK cycles at 2MHz                 |                      |                         | 1.5                  | μs        |

| Turn-On Time                          |         | Eight ADCCLK cycles at 2MHz                 |                      |                         | 4                    | μs        |

| Conversion Clock                      | fadcclk |                                             | 0.5                  |                         | 4                    | MHz       |

| Conversion Rate                       |         | $f_{ADCCLK} = 4MHz$ (not production tested) |                      |                         | 250                  | ksps      |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DVDDIO} = +5V, V_{AVDD} = +3.3V; V_{DVDD} = +2.5V$ , system clock  $(f_{SYSCLK}) = 16MHz$ , burst frequency  $(f_{BURST}) = bandpass$  frequency  $(f_{BPF}) = 50$ kHz,  $C_{REFBG} = C_{REF} = 1\mu$ F in parallel with 0.01 $\mu$ F,  $f_{ADCCLK} = 2$ MHz (SAR data rate = 125ksps),  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise specified. Typical values are at  $T_A = +25^{\circ}$ C.)

| PARAMETER                    | SYMBOL       | со                                    | NDITIONS                                        | MIN                        | ТҮР   | МАХ  | UNITS |

|------------------------------|--------------|---------------------------------------|-------------------------------------------------|----------------------------|-------|------|-------|

| +2.5V LINEAR REGULATOR       | (REG2P5)     |                                       |                                                 | 1                          |       |      | •     |

| REG2P5 Output Voltage        |              |                                       |                                                 | 2.38                       |       | 2.62 | V     |

| Load Current                 |              |                                       |                                                 |                            |       | 50   | mA    |

| Output Short-Circuit Current |              | REG2P5 shorted                        | d to DGND                                       |                            | 100   |      | mA    |

| POWER REQUIREMENTS           |              |                                       |                                                 |                            |       |      |       |

|                              |              | DVDD                                  |                                                 | 2.25                       | 2.5   | 2.75 |       |

| Supply Voltage Range         |              | AVDD                                  |                                                 | 3.00                       | 3.3   | 3.6  | V     |

|                              |              | DVDDIO                                |                                                 | 4.5                        | 5.0   | 5.5  |       |

|                              |              | All analog funct                      | tions enabled                                   |                            | 12    | 18   | mA    |

|                              |              | All analog funct                      | tions disabled                                  |                            | 3     | 10   | μA    |

|                              |              |                                       | LNA                                             |                            | 2.4   |      |       |

|                              |              |                                       | Sigma-delta ADC                                 |                            | 12    |      | mA    |

|                              |              |                                       | SAR ADC, 250ksps,<br>f <sub>ADCCLK</sub> = 4MHz |                            | 600   |      |       |

|                              |              |                                       | PLL                                             |                            | 300   |      |       |

| AVDD Supply Current          |              | Incremental<br>AVDD supply<br>current | Supply voltage<br>supervisors                   |                            | 3     |      | μA    |

|                              |              | current                               | Internal voltage<br>reference                   |                            | 220   |      |       |

|                              |              |                                       | Reference buffer                                |                            | 300   |      |       |

|                              |              |                                       | Bias (any AVDD<br>module enabled)               |                            | 1.5   |      | mA    |

| DVDD Supply Current          |              |                                       | 1                                               |                            | 11    |      | mA    |

| DVDDIO Supply Current        |              |                                       |                                                 |                            | 2.5   |      | mA    |

| DIGITAL INPUTS (GPIO, UAR    | RT, JTAG, SI | PI™)                                  |                                                 |                            |       |      |       |

| Input High Voltage           |              |                                       |                                                 | V <sub>DVDDIO</sub><br>- 1 |       |      | V     |

| Input Low Voltage            |              |                                       |                                                 |                            |       | 0.8  | V     |

| Input Hysteresis             |              | V <sub>DVDDIO</sub> = 5.0V            | ,                                               |                            | 500   |      | mV    |

| Input Leakage Current        |              | Digital input vo<br>DVDDIO, pullup    | ltage = DGND or<br>disabled                     |                            | ±0.01 | ±1   | μA    |

| Pullup/Pulldown Resistance   |              | Pulled up to DV<br>down to DGND       | DDIO internally, pulled internally              |                            | 150   |      | kΩ    |

| Input Capacitance            |              |                                       |                                                 |                            | 15    |      | рF    |

### **Pin Description**

| PIN       | NAME               | FUNCTION                                                                                                                                                                                                                                                                                                                                                    |

|-----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | P1.3/TCK           | Port 1 Data 3/JTAG Serial Clock Input. P1.3 is a general-purpose digital I/O. TCK is the JTAG serial test clock input. Refer to the <i>MAXQ7667 User's Guide</i> Sections 5 and 11.                                                                                                                                                                         |

| 2         | P1.4/MOSI          | Port 1 Data 4/SPI Serial Data Output. P1.4 is a general-purpose digital I/O. MOSI is the master output, slave input for the SPI interface. Refer to the <i>MAXQ7667 User's Guide</i> Sections 5 and 9.                                                                                                                                                      |

| 3         | P1.5/MISO          | Port 1 Data 5/SPI Serial Data Input. P1.5 is a general-purpose digital I/O. MISO is the master input, slave output for the SPI interface. Refer to the <i>MAXQ7667 User's Guide</i> Sections 5 and 9.                                                                                                                                                       |

| 4         | P1.6/SCLK          | Port 1 Data 6/SPI Serial Clock Output. P1.6 is a general-purpose digital I/O. SCLK is the serial clock for the SPI interface. SCLK is an input when operating as a slave and an output when operating as a master. Refer to the <i>MAXQ7667 User's Guide</i> Sections 5 and 9.                                                                              |

| 5         | P1.7/SYNC/SS       | Port 1 Data 7/Schedule Timer Sync Input/SPI Slave Select. P1.7 is a general-purpose digital I/O. A rising edge on the SYNC input resets the schedule timer. In SPI slave mode, SS is the SPI slave-select input. In SPI master mode, use SS or a GPIO to manually select an external slave. Refer to the <i>MAXQ7667 User's Guide</i> Sections 5, 7, and 9. |

| 6, 19, 42 | DVDD               | Digital Supply Voltage. Connect DVDD directly to a +2.5V external source or to REG2P5 output for single supply operation. Bypass DVDD to DGND with a $0.1\mu$ F capacitor as close as possible to the device. Connect all DVDD nodes together.                                                                                                              |

| 7, 18, 43 | DGND               | Digital Ground. Connect all DGND nodes together. Connect to AGND at a single point.                                                                                                                                                                                                                                                                         |

| 8, 17, 44 | DVDDIO             | Digital I/O Supply Voltage. DVDDIO powers all digital I/Os except for XIN and XOUT. Bypass DVDDIO to DGND with a $0.1\mu$ F capacitor as close as possible to the device. Connect all DVDDIO nodes together.                                                                                                                                                |

| 9         | P0.0/URX           | Port 0 Data 0/UART Receive Data Input. P0.0 is a general-purpose digital I/O. URX is a UART or LIN data receive input. Refer to the <i>MAXQ7667 User's Guide</i> Sections 5 and 8.                                                                                                                                                                          |

| 10        | P0.1/UTX           | Port 0 Data 1/UART Transmit Data Output. P0.1 is a general-purpose digital I/O. UTX is a UART or LIN data transmit output. Refer to the <i>MAXQ7667 User's Guide</i> Sections 5 and 8.                                                                                                                                                                      |

| 11        | P0.2/TXEN          | Port 0 Data 2/UART Transmit Output. P0.2 is a general-purpose digital I/O. TXEN asserts low when the UART is transmitting. Use TXEN to enable an external LIN/UART transceiver. Refer to the <i>MAXQ7667 User's Guide</i> Sections 5 and 8.                                                                                                                 |

| 12        | P0.3/T0/<br>ADCCTL | Port 0 Data 3/Timer 0 I/O/ADC Control Input. P0.3 is a general-purpose digital I/O. T0 is the primary Type 2 timer/counter 0 output or input. ADCCTL is a sampling/conversion trigger input for the SAR ADC. Refer to the <i>MAXQ7667 User's Guide</i> Sections 5, 6, and 14.                                                                               |

| 13        | P0.4/T0B           | Port 0 Data 4/Timer 0B I/O/Comparator Output. P0.4 is a general-purpose digital I/O. T0B is the secondary Type 2 timer/counter 0 output or input. Refer to the <i>MAXQ7667 User's Guide</i> Sections 5 and 6.                                                                                                                                               |

| 14        | P0.5/T1            | Port 0 Data 5/Timer 1 I/O. P0.5 is a general-purpose digital I/O. T1 is the primary Type 2 timer/counter 1 output or input. Refer to the <i>MAXQ7667 User's Guide</i> Sections 5 and 6.                                                                                                                                                                     |

| 15        | P0.6/T2            | Port 0 Data 6/Timer 2 I/O. P0.6 is a general-purpose digital I/O. T2 is the primary Type 2 timer/counter 2 output or input. Refer to the <i>MAXQ7667 User's Guide</i> Sections 5 and 6.                                                                                                                                                                     |

| 16        | P0.7/T2B           | Port 0 Data 7/Timer 2B I/O. P0.7 is a general-purpose digital I/O. T2B is the secondary Type 2 timer/counter 2 output or input. Refer to the <i>MAXQ7667 User's Guide</i> Sections 5 and 6.                                                                                                                                                                 |

| 20        | XIN                | Crystal Oscillator Input. Connect an external crystal or resonator between XIN and XOUT. When using an external clock source drive XIN with 2.5V level clock while leaving XOUT unconnected. Connect XIN to DGND when an external clock source is not used.                                                                                                 |

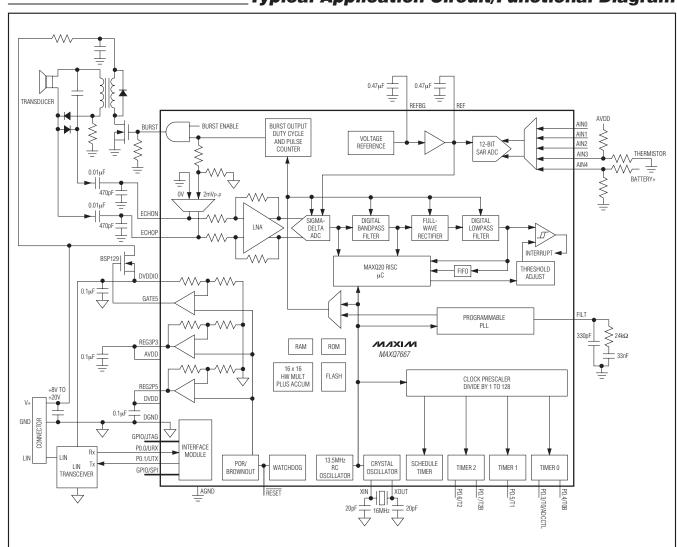

**MAXQ7667**

Typical Application Circuit/Functional Diagram

### **Detailed Features**

Smart Analog Peripherals

Dedicated Ultrasonic Burst Generator

Echo Receiving Path

Low-Noise Amplifier

**Time Variable Gain Amplifier**

16-Bit Sigma-Delta ADC

**Digital Bandpass Filter**

Full-Wave Rectifier and Digital Lowpass Filter 8-Deep, 16-Bit Wide FIFO Simplifies Real-Time Processing

**Magnitude Comparator**

5-Channel, 12-Bit SAR ADC with 250ksps Sampling Rate

Internal Bandgap Voltage Reference for the ADCs (Also Accepts External Voltage Reference)

### • Timer/Digital I/O Peripherals

SPI Interface

Three 16-Bit (or Six 8-Bit) Programmable Type 2 Timers/Counters

**16-Bit Schedule Timer**

Programmable Watchdog Timer

16 General-Purpose Digital I/Os with Multipurpose Capability

High-Performance, Low-Power, 16-Bit RISC Core 1MHz–16MHz Operation, Approaching 1MIPS per 1MHz

Low Power (< 2.5mA/MIPS, DVDD = +2.5V)

16-Bit Instruction Word, 16-Bit Data Bus

33 Instructions (Most Require Only One Clock Cycle)

**16-Level Hardware Stack**

Three Independent Data Pointers with Automatic Increment/Decrement

- Program and Data Memory Internal 32KB Program Flash Internal 4KB Data RAM Internal 8KB Utility ROM

- Crystal/Clock Module

1MHz–16MHz External Crystal Oscillator

13.5MHz Internal RC Oscillator

External Clock Source Operation

- 16 x 16 Hardware Multiplier with 48-Bit Accumulator, Single Clock Cycle Operation

- Power-Management Module Power-On Reset (POR)

Power-Supply Supervisor/Brownout Detection for All Supplies

On-Chip +5V, +3.3V, and +2.5V Regulators for Single Supply Operation

- JTAG Interface

Extensive Debug and Emulation Support In-System Test Capability

Flash-Memory-Program Download

- ♦ UART

Synchronous and Asynchronous Transfers Independent Baud-Rate Generator 2-Wire Interface Transmit and Receive FIFOs

+ LIN

Supports LIN 1.3, LIN 2.0, and SAE J2602 Automatic Baud-Rate Detection and LIN Frame Synchronization

Up to 64 Bytes Frame Length Automatic Calculation of Standard (LIN 1.3) and Enhanced (LIN 2.0) Checksums

- 7mm x 7mm, 48-Pin LQFP Package

- ♦ -40°C to +125°C Operating Temperature Range

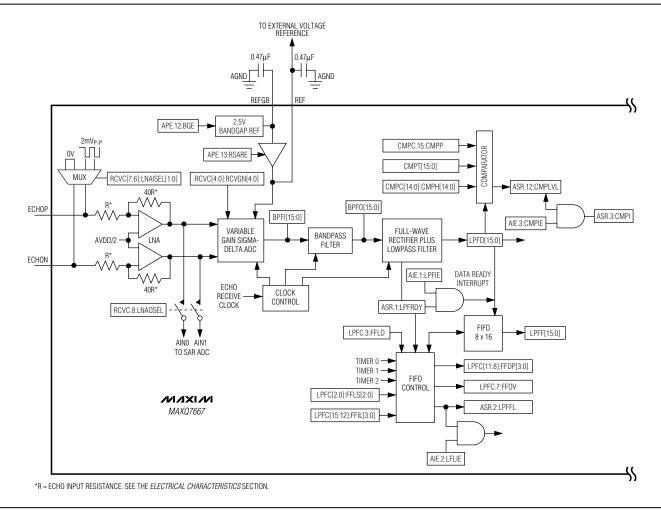

### Echo Receive Path

### Low-Noise Amplifier (LNA)

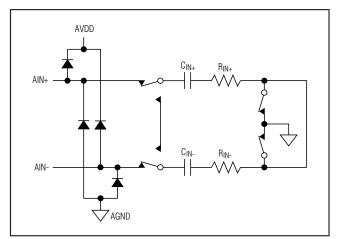

The LNA provides a 40V/V fixed gain to the input signal. The differential inputs of the LNA are ECHOP and ECHON. For proper biasing of the LNA, AC-couple the transducer or any external circuitry to ECHOP and ECHON. For a single-ended input signal, AC-couple the signal to ECHOP with a  $0.01\mu$ F capacitor and connect ECHON to AGND through a  $0.01\mu$ F capacitor placed as close as possible to the signal source. The outputs of the LNA connect to the inputs of a 16-bit sigma-delta ADC and can connect internally to the AINO and AIN1 inputs of the SAR ADC for external monitoring (Figure 2).

An analog multiplexer located at the input of the LNA selects one of three possible signals for processing by the echo receive path; the normal echo signal AC-coupled to the ECHOP and ECHON inputs, 0V signal, or a 2mVP-P internally generated signal (Figure 2). The 2mVP-P square-wave signal, with frequency and duty cycle matching the burst signal, allows the echo receive chain to process a simulated echo.

Figure 2. Echo Receive Path

**Diagnostic Signals**

### Sigma-Delta ADC

The MAXQ7667 features a 16-bit sigma-delta ADC with an analog gain adjustable from 38dB to 60dB (including the fixed LNA gain) with a maximum gain step of 12.5% (typical). Gain changes settle within one ADC conversion. Use software to create a virtual time variable gain amplifier. A digital bandpass and lowpass filters remove switching glitches and DC offset at the output of the ADC.

In a typical application, the software sets the gain to a low value when the burst is first sent and increases the gain as the time from when the burst was sent increases. As a result, strong echoes from nearby objects are processed without clipping while small signals from distant objects are processed with the maximum gain. The ADC samples the amplified echo signal from the LNA at 80 times the burst output frequency. The ADC provides conversion results at a data rate equal to 10 times the burst output frequency. The ADC conversion results also load to an 8-deep first-in-first-out (FIFO) at the native data rate or a separate time base without loading the CPU.

### Digital Bandpass Filter

The digital bandpass filter has a center frequency that tracks the burst output frequency. The bandpass width is 14% of the center frequency. The bandpass filter provides the 16-bit output data at a data rate equal to 10 times the burst output frequency.

### Full-Wave Rectifier

The full-wave rectifier detects the envelope of the digital bandwidth filter output to generate a DC output proportional to the peak-to-peak amplitude of the input signal. Full-wave rectification allows the digital lowpass filter to respond faster without excessive ripple.

### **Digital Lowpass Filter**

The lowpass filter removes the ripple from the full-wave detector output. The output of the lowpass filter is available at a data rate equal to five times the burst output frequency. The corner frequency is 1/5 the burst frequency with approximately 40dB per decade rolloff. The 16-bit output data of the lowpass filter is stored in a FIFO register with a depth of eight samples. The MAXQ7667 allows data transfer from the lowpass filter

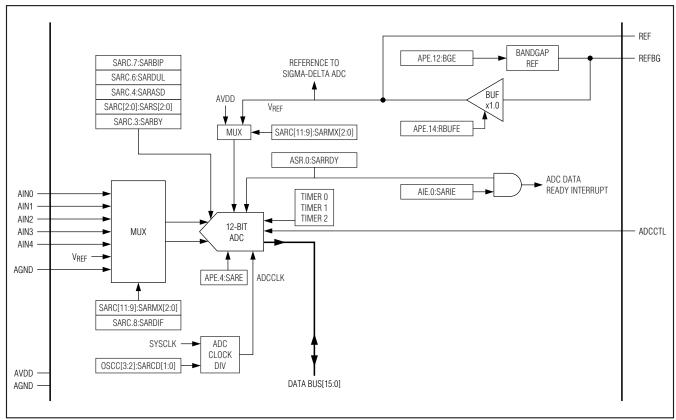

Figure 3. SAR ADC Block Diagram

**MAXQ7667**

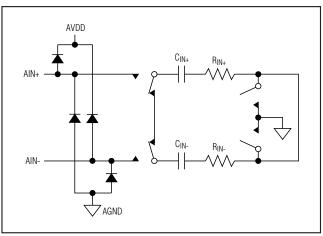

### SAR ADC Analog Input Track-and-Hold (T/H)

Figures 6 and 7 show the equivalent input circuit of the MAXQ7667 analog input architecture. During acquisition (track), a sampling capacitor charges to the positive input voltage at AINO–AIN4 in single-ended mode or AIN0 and AIN2 in differential mode while a second sampling capacitor connects to AGND in single-ended mode or AIN1 and AIN3 in differential mode. The ADC conversion start source and the ADC dual mode selection bits control the T/H timing.

### **Voltage Reference**

The MAXQ7667 supports three possible voltage reference sources for ADC conversion; 2.5V internal buffered bandgap reference, external source, and AVDD. The internal 2.5V bandgap reference has high initial accuracy and temperature coefficient of typically less than 100ppm/°C. When operating in internal reference mode, either the buffered output of the internal reference or AVDD connects to the SAR ADC while the buffered output of the internal reference connects to the sigma-delta ADC. When operating in external reference mode, an external source ranging between 1V and VAVDD applied at either the REF or REFBG inputs pro-

Figure 6. Equivalent Input Circuit (Track/Acquisition Mode)

vides the reference to the SAR ADC and sigma-delta ADC. Bypass REFBG and REF to AGND with a  $0.47\mu$ F capacitor for optimum performance. See Section 14 of the *MAXQ7667 User's Guide*.

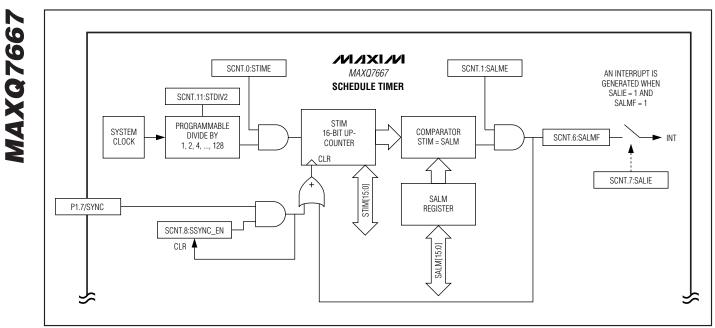

### **Schedule Timer**

The MAXQ7667's schedule timer provides general timekeeping and software synchronization to an external I/O. The schedule timer features include the following:

- 16-bit autoreload up-counter for the timer

- Programmable 16-bit alarm register

- Alarm interrupts

- Schedule timer incremented by a programmable system clock prescaler (1, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, 1/128)

- Schedule timer up-counter resettable through an external I/O pin, which allows synchronization of a schedule timer to an external event

- Wake-up alarm to pull the system clock from stopmode to normal operation

Figure 8 shows a simplified block diagram of the schedule timer.

Figure 7. Equivalent Input Circuit (Hold/Conversion Mode)

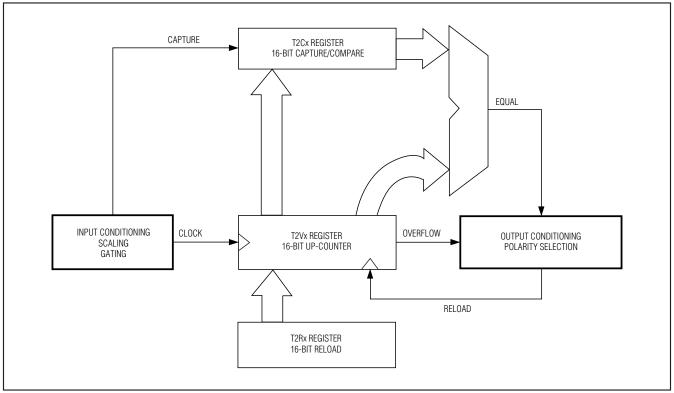

### **Type 2 Timers/Counters**

The MAXQ7667 includes three 16-bit timers/counters with programmable I/O (Figure 9). Each timer is a Type 2 timer implemented in the MAXQ<sup>®</sup> family. The Type 2 timer is an autoreload 16-bit timer/counter offering the following functions:

- 8-bit/16-bit timer/counter

- Up/down autoreload

- Counter function of external pulse

- Capture

- Compare

### **Clock Sources**

The MAXQ7667 oscillator module supplies the system clock for the  $\mu$ C core and all of the peripheral modules. The high-frequency oscillator operates with a 1MHz to 16MHz crystal. Use the internal RC oscillator as the system clock for applications that do not require precise timing. See Section 15 of the *MAXQ7667 User's Guide*.

The MAXQ7667 supports the following master clock sources:

• Internal high-frequency oscillator drives an external 1MHz–16MHz crystal or ceramic resonator

- Internal, fast-starting, 13.5MHz RC oscillator (default oscillator at startup and in the event the external crystal fails)

- External 4MHz-16MHz clock input

### Crystal Selection

The MAXQ7667 requires a crystal with the following specifications:

Frequency: 1MHz-16MHz

CLOAD: 6pF (min)

Drive level: 5µW

Series resonance resistance:  $30\Omega$  (max)

**Note:** Quartz crystal vendors often specify series resonance resistance (R1). Series resonance resistance is the resistance observed when the resonator is in the series resonant condition. When a resonator is used in the parallel resonant mode with an external load capacitance, as is the case with the MAXQ7667 oscillator circuit, the effective resistance at the loaded frequency of oscillation is:

### R1 x (1 + (CO/CLOAD))<sup>2</sup>

For typical shunt capacitance (CO) and load capacitance ( $C_{LOAD}$ ) values, the effective resistance potentially exceeds R1 by a factor of 2.

MAXQ is a registered trademark of Maxim Integrated Products, Inc.

Figure 8. Schedule-Timer Module Block Diagram

Figure 9. Type 2 Timer/Counter in 16-Bit Mode

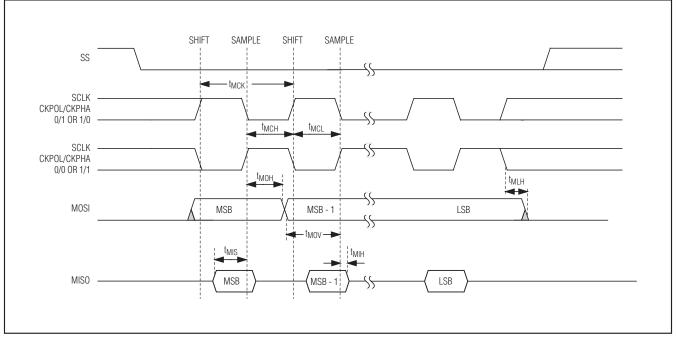

Figure 11. SPI Timing Diagram in Master Mode

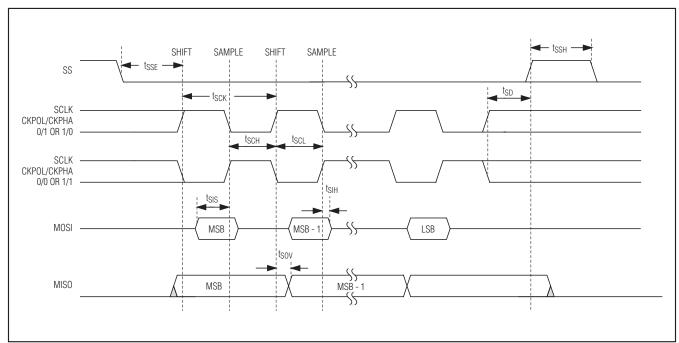

Figure 12. SPI Timing Diagram in Slave Mode

**MAXQ7667**

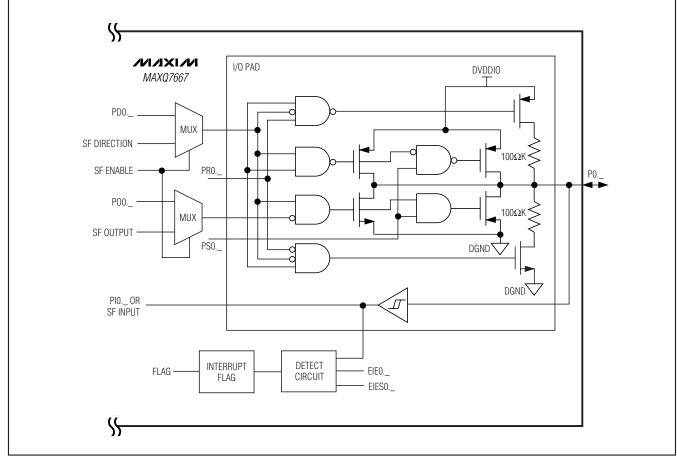

Figure 13. Port 0 Digital I/O Basic Circuitry. Port 1 Circuitry is the Same as Port 2.

Connect bypass capacitors at each power-supply input as close as possible to the device. Use a bypass capacitor less than  $0.47\mu$ F on DVDDIO. For most applications,  $0.1\mu$ F bypass capacitors are adequate.

### **Supply Brownout Monitor**

Power supplies DVDD, AVDD, and DVDDIO each include a brownout monitor/supervisor that alerts the  $\mu$ C when their corresponding supply voltages drop below the interrupt threshold. Activate each brownout monitor independently using the corresponding brownout enable bits: VDBE, VIBE, and VABE.

### Reset

In reset mode, no instruction execution occurs and all inputs/outputs return to their default states. Code execution resumes at address 8000h (in the utility ROM) once the reset condition is removed. Four different sources reset the MAXQ7667: POR, watchdog timer reset, external reset, and internal system reset.

During normal operation, force RESET low for at least four system clock cycles for an external reset. Set the ROD bit in the SC register, while the SPE bit in the ICDF register is set, for an internal system reset. See Section 16 of the *MAXQ7667 User's Guide*.

### Power-On Reset (POR)

The MAXQ7667 includes a DVDD voltage supervisor to control the  $\mu$ C POR. On power-up, internal circuitry pulls RESET low and resets all the internal registers. RESET is held low for the duration of the power-on delay after VDVDD rises above the DVDD reset threshold. The internal RC oscillator starts up and software execution begins at the reset vector location 8000h immediately after the device exits POR while RESET is

### Data Memory

memory. Access physical memory segments (other than the stack and register memories) as either program memory or data memory, but not both at once.

By default, the memory is arranged in a Harvard architecture, with separate address spaces for program and data memory. The configuration of program and data space depends on the current execution location.

- When executing code from flash memory, access the SRAM and utility ROM in data space.

- When executing code from SRAM, access the flash memory and utility ROM in data space.

- When executing code from the utility ROM, access the flash memory and SRAM in data space.

### Utility ROM (see Section 18 of the MAXQ7667 User's Guide)

The utility ROM is a  $4K \times 16$  block of internal ROM memory that defaults to a starting address of 8000h. The utility ROM consists of subroutines called from application software. The subroutines include:

- In-system programming (bootloader) over the JTAG or UART interface

- In-circuit debug routines

- Test routines (internal memory tests, memory loader, etc.)

- User-callable routines for in-application flash programming and code space table lookup

Following any reset, execution begins in the utility ROM. The ROM software determines whether the program execution immediately jumps to the start of the userapplication code (located at address 0000h) or to one of the special routines mentioned above. Call the routines within the utility ROM using the application software. Refer to the *MAXQ7667 User's Guide* for more information on the utility ROM contents.

Password protect in-system programming, in-application programming, and in-circuit debugging functions using a password-lock (PWL) bit. The PWL bit is implemented in the SC register. When the PWL bit is set to one (POR default), the password is required to access the utility ROM, including in-circuit debug and in-system programming routines that allow reading or writing of internal memory. When the PWL bit is cleared to zero, these utilities are fully accessible without the password. The password is automatically set to all ones following a mass erase. The 2K x 16 internal data SRAM maps into either program or data space. The contents of the SRAM are maintained during stop mode and across non-POR resets, as long as DVDD remains within the operating voltage range.

A data memory cycle requires only one system clock period to support fast internal execution. This allows a complete read or write operation on SRAM in one clock cycle. The MMU handles data memory mapping and access control. Read or write to the data memory with word or byte-wide commands.

### Stack Memory

The MAXQ7667 provides a 16 x 16 hardware stack to support subroutine calls and system interrupts. A 16-bit wide internal hardware stack provides storage for program return addresses and general-purpose use. The stack is used automatically by the processor when the CALL, RET, and RETI instructions are executed and interrupts serviced.

### **Register Set**

Sets of registers control most functions. These registers provide a working space for memory operations as well as configuring and addressing peripheral registers on the device. Registers are divided into two major types; system registers and peripheral registers. The register set common to most MAXQ-based devices, also known as the system registers, includes the ALU, accumulator registers, data pointers, interrupt vectors and control, and stack pointer. The peripheral registers define additional functionality. Tables 1 and 3 show the MAXQ7667 register set.

### Programming

Two different methods program the flash memory: insystem programming and in-application programming. Both methods afford great flexibility in system design as well as reduce the life-cycle cost of the embedded system. The MAXQ7667 password protects these features to prevent unauthorized access to code memory.

### In-System Programming

An internal bootstrap loader reloads the device over a simple JTAG or UART interface allowing cost savings in system software upgrade. During power-up, the MAXQ7667 first checks for activity on the JTAG port. If no activity is present, the device checks if a password-protected program is present. If the password is set,

the application code executes. The application codes initiate reprogramming. If the password is not set, the MAXQ7667 monitors the UART for an autobaud character (0x0D). If this character is received, the device sets its serial baud rate and initiates a boot loader procedure. If 0x0D is not received after five seconds, the device begins execution of the application code.

The following bootloader functions are supported:

- Load

- Dump

- CRC

- Verify

- Erase

### In-Application Programming

The in-application programming feature allows the  $\mu$ C to modify its own flash program memory while simultaneously executing its application software. This allows on the fly software updates in mission-critical applications that cannot afford downtime. Erase and program the flash memory using the flash programming functions in the utility ROM. Refer to Section 18 of the *MAXQ7667 User's Guide* for a detailed description of the utility ROM functions.

### **Stop Mode**

Power consumption reaches its minimum in stop mode (STOP = 1). In this mode, the external oscillator, internal RC oscillator, system clock, and all processing halts. Trigger an enabled external interrupt input or directly apply an external reset on RESET to exit stop mode. Upon exiting stop mode, the  $\mu$ C either waits for the external high-frequency crystal to complete its warmup period or starts execution immediately from its internal RC oscillator while the crystal warms up.

### Interrupts

Multiple interrupt sources quickly respond to internal and external events. The MAXQ architecture uses a single interrupt vector (IV) and single interrupt-service routine (ISR) design. Enable interrupts globally, individually, or by module. When an interrupt condition occurs, its individual flag is set even if the interrupt source is disabled at the local, module, or global level. Clear interrupt flags within the interrupt routine to avoid repeated false interrupts from the same source. Provide an adequate delay between the write to the flag and the RETI instruction using application software to allow time for the interrupt hardware to remove the internal interrupt condition. Asynchronous interrupt flags require a one-instruction delay and synchronous interrupt flags require a two-instruction delay.

When an enabled interrupt is detected, software jumps to a user-programmable interrupt vector location. The IV register defaults to 0000h on reset or power-up. Once software control transfers to the ISR, use the interrupt identification register (IIR) to determine if the source of the interrupt is a system register or peripheral register. The specified module identifies the specific interrupt source. The following interrupt sources are available:

- Watchdog interrupt

- External interrupts 0-7 on port 0 and port 1

- Timer 0 low compare, low overflow, capture/compare, and overflow interrupts

- Timer 1 low compare, low overflow, capture/compare, and overflow interrupts

- Timer 2 low compare, low overflow, and overflow interrupts

- Schedule timer alarm interrupt

- SPI data transfer complete, mode fault, write collision and receive overrun interrupts

- UART transmit, receive interrupts

- LIN mode master or slave interrupt

- SAR ADC data ready interrupt

- Echo envelope LPF output, FIFO full, and comparator interrupts

- Digital and I/O voltage brownout interrupts

- High-frequency oscillator failure interrupt

### Table 1. System Register Map

MODULE NAME (BASE SPECIFIER) REGISTER INDEX AP (8h) A (9h) PFX (Bh) IP (Ch) SP (Dh) DPC (Eh) DP (Fh) AP IP 0h A[0] PFX[0] \_\_\_\_ \_\_\_\_ SP 1h APC PFX[1] A[1] \_\_\_\_ 2h \_\_\_\_ A[2] PFX[2] \_\_\_\_ IV \_\_\_\_ \_\_\_\_ 3h \_\_\_\_ \_\_\_\_ A[3] PFX[3] \_\_\_\_ OFFS DP[0] 4h PSF PFX[4] DPC **A**[4] \_\_\_\_ \_\_\_\_ \_\_\_\_ 5h IC PFX[5] GR A[5] \_\_\_\_ \_\_\_\_ IMR GRL 6h A[6] **PFX[6]** \_\_\_\_ LC[0] \_\_\_\_ 7h \_\_\_\_ **A**[7] PFX[7] LC[1] BΡ DP[1] \_ 8h SC **A[8]** GRS \_\_\_\_ \_\_\_\_ \_\_\_\_ 9h \_\_\_\_ A[9] \_\_\_\_ \_\_\_\_ \_\_\_\_ GRH \_\_\_\_ Ah A[10] GRXL \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ Bh IIR A[11] FP \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ Ch \_\_\_\_ A[12] \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ Dh A[13] \_\_\_\_ \_\_\_\_ \_\_\_\_ \_ \_\_\_\_ \_\_\_\_ Eh CKCN A[14] \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_ Fh WDCN A[15] \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_

Note: Registers in italics are read-only. Registers in bold are 16-bit wide.

**MAXQ7667**

| BEGICTER    |    |    |    |    |   |    |   |        |                  |      |      |      |      |             |       |      |

|-------------|----|----|----|----|---|----|---|--------|------------------|------|------|------|------|-------------|-------|------|

|             | 15 | 14 | 13 | 12 | Ħ | 10 | 6 | 8      | 7                | 9    | 5    | 4    | 3    | 2           | -     | •    |

|             |    |    |    |    |   |    |   |        |                  |      | Ι    | I    |      | AP (4 Bits) | Bits) |      |

|             |    |    |    |    |   |    |   |        | 0                | 0    | 0    | 0    | 0    | 0           | 0     | 0    |

|             |    |    |    |    |   |    |   |        | CLR              | SQI  |      |      |      | MOD2        | MOD1  | MODO |

|             |    |    |    |    |   |    |   |        | 0                | 0    | 0    | 0    | 0    | 0           | 0     | 0    |

| Ц<br>О<br>С |    |    |    |    |   |    |   |        | Z                | S    |      | GPF1 | GPFO | N           | U     | ш    |

|             |    |    |    |    |   |    |   |        | -                | 0    | 0    | 0    | 0    | 0           | 0     | 0    |

| Ċ           |    |    |    |    |   |    |   |        |                  |      | CGDS |      | I    | Ι           | SNI   | IGE  |

| <br>ک       |    |    |    |    |   |    |   |        | 0                | 0    | 0    | 0    | 0    | 0           | 0     | 0    |

|             |    |    |    |    |   |    |   |        | IMS              |      | IM5  | IM4  | IM3  | IM2         | 1M1   | OMI  |

|             |    |    |    |    |   |    |   |        | 0                | 0    | 0    | 0    | 0    | 0           | 0     | 0    |

| C<br>U      |    |    |    |    |   |    |   |        | TAP              |      | CDA1 | CDA0 |      | ROD         | PWL   |      |

| )<br>)<br>) |    |    |    |    |   |    |   |        | -                | 0    | 0    | 0    | 0    | 0           | °*    | 0    |

| ₽           |    |    |    |    |   |    |   |        | SII              |      | 115  | 114  | 113  | 112         | Ħ     | 9    |

|             |    |    |    |    |   |    |   |        | 0                | 0    | 0    | 0    | 0    | 0           | 0     | 0    |

|             |    |    |    |    |   |    |   |        | XTRC             |      | RGMD | STOP | SWB  | PMME        | CD1   | CDO  |

|             |    |    |    |    |   |    |   |        | °*               | 0    | 0    | 0    | 0    | 0           | 0     | 0    |

|             |    |    |    |    |   |    |   |        | POR              | EWDI | WD1  | WD0  | WDIF | WTRF        | EWT   | RWT  |

|             |    |    |    |    |   |    |   |        | °*               | °*   | 0    | 0    | 0    | °*          | °*    | 0    |

|             |    |    |    |    |   |    |   | A[n]   | A[n] (16 Bits)   |      |      |      |      |             |       |      |

|             | 0  | 0  | 0  | 0  | 0 | 0  | 0 | 0      | 0                | 0    | 0    | 0    | 0    | 0           | 0     | 0    |

|             |    |    |    |    |   |    |   | PFX[r  | PFX[n] (16 Bits) |      |      |      |      |             |       |      |

|             | 0  | 0  | 0  | 0  | 0 | 0  | 0 | 0      | 0                | 0    | 0    | 0    | 0    | 0           | 0     | 0    |

| ₽           |    |    |    |    |   |    |   | )<br>H | IP (16 Bits)     |      |      |      |      |             |       |      |

| =           | 1  | 0  | 0  | 0  | 0 | 0  | 0 | 0      | 0                | 0    | 0    | 0    | 0    | 0           | 0     | 0    |

| D           |    |    |    |    |   |    |   |        |                  |      |      |      |      | SP (4 I     | Bits) |      |

| 5           | 0  | 0  | 0  | 0  | 0 | 0  | 0 | 0      | 0                | 0    | 0    | 0    | -    | -           | -     | -    |

| IV.         |    |    |    |    |   |    |   | ) ∧(   | IV (16 Bits)     |      |      |      |      |             |       |      |

|             | 0  | 0  | 0  | 0  | 0 | 0  | 0 | 0      | 0                | 0    | 0    | 0    | 0    | 0           | 0     | 0    |

| 10101       |    |    |    |    |   |    |   | rc[0]  | LC[0] (16 Bits)  |      |      |      |      |             |       |      |

|             | 0  | 0  | 0  | 0  | 0 | 0  | 0 | 0      | 0                | 0    | 0    | 0    | 0    | 0           | 0     | 0    |

| 10[1]       |    |    |    |    |   |    |   | LC[1]  | LC[1] (16 Bits)  |      |      |      |      |             |       |      |

|             | 0  | 0  | 0  | 0  | 0 | 0  | 0 | 0      | 0                | 0    | 0    | 0    | 0    | 0           | 0     | 0    |

Table 2. System Register Bit and Reset Values

### 16-Bit, RISC, Microcontroller-Based, Ultrasonic Distance-Measuring System

### **MAXQ7667**

## Table 4. Peripheral Register Bit Functions and Reset Values

|          |             |        |             |        |        |        |       | REGL  | REGISTER BIT |          |         |        |        |            |            |        |

|----------|-------------|--------|-------------|--------|--------|--------|-------|-------|--------------|----------|---------|--------|--------|------------|------------|--------|

|          | 15          | 14     | 13          | 12     | 1      | 10     | 6     | 8     | 7            | 9        | ß       | 4      | e      | 2          | -          | 0      |

| POO      | c           | 0      | c           | c      | c      | c      | c     | c     | P007         | P006     | - P005  | P004   | - P003 | - P002     | P001       | P000   |

| PO1      |             | I      |             |        |        |        |       |       | P017         | P016     | P015    | PO14   | PO13   | P012       | P011       | PO10   |

| )        | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | [            |          | - Ļ     | - i    |        | - <u>i</u> | - j        | - 1    |

| EIFO     | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | 0            | 0 Eo     |         | 1E4    | 0 [2]  | 0 EZ       | 0          | D EO   |

| ĩ        |             |        |             |        |        | •      |       | -     | IE7          | IE6      | E5      | IE4    | E3     | E2         | Ē          | EO     |

|          | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | 0            | 0        | 0       | 0      | 0      | 0          | 0          | 0      |

| OId      |             | I      |             | I      | I      |        |       | Ι     | P107         | P106     | P105    | Pl04   | P103   | P102       | P101       | P100   |

| 2        | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | ST           | ST       | ST      | ST     | ST     | ST         | ST         | ST     |

| EI<br>FI | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | 117          | 9114     |         | P114   | 5113   | 2117       | LT14       | 0117   |

|          | -           | -      | 5           | 5      | -      | 5      | 5     | 5     | 0            | - O      |         |        |        |            |            |        |

| EIEO     | -           | -      | <           | <      | 0      | <      | c     | c     |              | C        | CY3     | 5 C    |        |            |            |        |

|          | >           | >      |             |        |        | >      |       |       | EX7          | EXe      | EX5     | EX4    | EX3    | EX3        | EX1        | EXD    |

| EIE1     | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     |              |          | 0       | 0      | 0      | 0          | 0          | 0      |

|          | 1           | I      | I           |        | 1      | 1      | 1     |       | PD07         | PD06     | PD05    | PD04   | PD03   | PD02       | PD01       | PD00   |

| 004      | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | 0            | 0        | 0       | 0      | 0      | 0          | 0          | 0      |

| 104      | Ι           | I      | Ι           | I      | Ι      | I      | I     |       | PD17         | PD16     | PD15    | PD14   | PD13   | PD12       | PD11       | PD10   |

| -        | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | 0            | 0        | 0       | 0      | 0      | 0          | 0          | 0      |

| EIESO    | 1           | I      | 1           | 1      | 1      | 1      | 1     | ŀ     | 117          | IT6      | IT5     | IT4    | 1T3    | 112        | IT1        | ITO    |

|          | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | 0            | 0        | 0       | 0      | 0      | 0          | 0          | 0      |

| EIES1    | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     |              | 9        | ۹<br>۱۵ | 4      | 5      |            |            | 010    |

|          | >           | -      | >           | -      | >      | >      | -     | >     | DS07         | PSOF     | PSOF    | DS04   | DS03   | 0<br>BS00  | D<br>DS01  | DSOD   |

| PSO      | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | 0            | 0        | 0       | 0      | 0      | 0          | 0          | 0      |

| Č        |             | 1      |             |        |        |        |       |       | PS17         | PS16     | PS15    | PS14   | PS13   | PS12       | PS11       | PS10   |

| 0        | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | 0            | 0        | 0       | 0      | 0      | 0          | 0          | 0      |

| PRO      | I           | I      | I           | Ţ      | 1      | 1      | 1     | I     | PR07         | PR06     | PR05    | PR04   | PR03   | PR02       | PR01       | PR00   |

| 2        | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     |              | -        | -       | -      | -      | -          | -          | -      |

| PR1      | 4           | 0      | 0           | 0      | 4      | (      | (     | 0     | PR17         | PR16     | PR15    | PR14   | PR13   | PR12       | PR11       | PR10   |

|          | 0           | 5      | 5           | 5      | 0      | -      | 0     | 0     | - 2          | NOW      |         |        |        |            |            |        |

| MCNT     | 0           |        | c           | <      | 0      | <      | 0     |       | 5 -          |          |         |        | 3      |            |            | 200    |

|          | MA15        | MA14   | MA13        | MA12   | MA11   | MA10   | MAG   | MAR   | MA7          | MAG      | MA5     | MA4    | MA3    | MA2        | MA1        | MAD    |

| AM       | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | 0            | 0        | 0       | 0      | 0      | 0          | 0          | 0      |

|          | MB15        | MB14   | MB13        | MB12   | MB11   | MB10   | MB9   | MB8   | MB7          | MB6      | MB5     | MB4    | MB3    | MB2        | MB1        | MBO    |

| NIN      | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | 0            | 0        | 0       | 0      | 0      | 0          | 0          | 0      |

| MC2      | MC215       | MC214  | MC213       | MC212  | MC211  | MC210  | MC29  | MC28  | MC27         | MC26     | MC25    | MC24   | MC23   | MC22       | MC21       | MC20   |

|          | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | 0            | 0        | 0       | 0      | 0      | 0          | 0          | 0      |

| MC1      | MC115       | MC114  | MC113       | MC112  | MC111  | MC110  | MC19  | MC18  | MC17         | MC16     | MC15    | MC14   | MC13   | MC12       | MC11       | MC10   |

|          | MC015       | MC014  | MC013       | MC012  | MC011  | MC010  | MC09  | MCDB  | MC07         | MCOB     | MCO5    | MC04   | MCO3   | MC02       | MCD1       | MCDD   |

| MCO      | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | 0            | 0        | 0       | 0      | 0      | 0          | 0          | 0      |

| alao     | SPIB15      | SPIB14 | SPIB13      | SPIB12 | SPIB11 | SPIB10 | SPIB9 | SPIB8 | SPIB7        | SPIB6    | SPIB5   | SPIB4  | SPIB3  | SPIB2      | SPIB1      | SPIBO  |

| 5        | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | 0            | 0        | 0       | 0      | 0      | 0          | 0          | 0      |

| SPICN    | •           | •      | •           |        | •      | (      | •     | (     | STBY         | SPIC     | ROVR    | wcol   | MODF   | MODFE      | MSTM       | SPIEN  |

|          | 0           | 0      | o           | 0      | 0      | 0      | 0     | 0     |              | 0        | 0       | 0      | 0      | 0          |            | 0      |

| SPICF    | 0           | -      | 0           | <      | 0      | 0      | c     | c     |              | CHC<br>0 |         | 0      | c      |            |            |        |

|          | »           | »      | »           | »      | »      | »      | »     | »     | SPICK7       | SPICK6   | SPICK5  | SPICK4 | SPICK3 | SPICK2     | SPICK1     | SPICKO |

| SPICK    | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | 0            | 0        | 0       | 0      | 0      | 0          | 0          | 0      |

| EONTI    | I           | I      | Ι           | Ι      | I      | 1      | 1     | I     | FBUSY        | I        | I       |        |        | FC2        | FC1        | FOO    |

|          | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | ÷            | 0        | 0       | 0      | 0      | 0          | 0          | 0      |

| MC1R     | MC1R15      | MC1R14 | MC1R13      | MC1R12 | MC1R11 | MC1R10 | MC1R9 | MC1R8 | MC1R7        | MC1R6    | MC1R5   | MC1R4  | MC1R3  | MC1R2      | MC1R1      | MC1R0  |

|          | U<br>MC0R15 | MC0R14 | U<br>MC0R13 | MC0R12 | MC0R11 | MCOR10 | MC0R9 | MCDB8 | MC0B7        | MCOR6    | MCOR5   | MC0R4  | MCOR3  | MCDR2      | U<br>MCDR1 | MCORD  |

| MCOH     | 0           | 0      | 0           | 0      | 0      | 0      | 0     | 0     | 0            | 0        | 0       | 0      | 0      | 0          | 0          | 0      |

**16-Bit, RISC, Microcontroller-Based, Ultrasonic Distance-Measuring System**

34

|          |              |             |             |              |         |         |        | REGIS      | REGISTER RIT |            |               |             |               |            |             |            |

|----------|--------------|-------------|-------------|--------------|---------|---------|--------|------------|--------------|------------|---------------|-------------|---------------|------------|-------------|------------|

| REGISTER | 15           | 14          | 13          | 12           | =       | 10      | 6      | 8          | 7            | 9          | 5             | 4           | e             | 2          | -           | 0          |

| SCNT     |              |             | 1           |              | STDIV2  | STDIV1  | STDIV0 | SSYNC_EN   | SALIE        | SALMF      |               |             |               | 1          | SALME       | STIME      |

|          | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | 0          | 0           | 0          |

| STIM     | STIM15       | STIM14      | STIM13      | STIM12       | STIM11  | STIM10  | STIM9  | STIM8      | STIM7        | STIM6      | STIM5         | STIM4       | STIM3         | STIM2      | STIM1       | STIMO      |

|          | SALM15       | SALM14      | SALM13      | SALM12       | SALM11  | SALM10  | SALM9  | SALMB      | SALM7        | SALM6      | SALM5         | SALM4       | SALM3         | SALM2      | SALM1       | SALMO      |

| SALM     | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | 0          | 0           | 0          |

|          | 1            |             |             |              |         | 1       |        |            |              | 1          |               |             |               | 1          | 1           | DPMG       |

|          | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | 0          | 0           | 0          |

| RCTRM    | Ι            | I           | Ι           | I            |         | I       | 1      | RCTRM8     | RCTRM7       | RCTRM6     | <b>RCTRM5</b> | RCTRM4      | <b>RCTRM3</b> | RCTRM2     | RCTRM1      | RCTRM0     |

|          | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | 0          | 0           | 0          |

| DO       | ID015        | ID014       | ID013       | ID012        | ID011   | ID010   | 60QI   | ID08       | ID07         | ID06       | ID05          | ID04        | ID03          | ID02       | ID01        | D00        |

|          | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | 0          | 0           | 0          |

| D1       | D115         | D114        | D113        | D112         | D111    | D110    | D19    | D18        | 1D17         | D16        | 1D15          | D14         | D13           | D12        | D11         | D10        |

|          | 5            | -           | -           | 5            | 5       | 5       | 5      | 5          | ET 0         | TOCED      |               |             | 0<br>Cat      |            | 0           | C OEN      |

| T2CNA0   | 0            | c           | 0           |              | c       | 0       | c      | 0          | 0            | 0          | 0             | 0           | 2             | 0          | 200         | O CELA     |

| o or     |              | ,           |             |              |         |         | ,      |            | T2H07        | T2H06      | T2H05         | T2H04       | T2H03         | T2H02      | T2H01       | T2H00      |

| 0HZI     | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | 0          | 0           | 0          |

|          |              |             |             |              |         |         |        |            | T2RH07       | T2RH06     | T2RH05        | T2RH04      | T2RH03        | T2RH02     | T2RH01      | T2RH00     |

| חבושאו   | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | 0          | 0           | 0          |

| T2CH0    | Ι            |             |             |              |         |         |        |            | T2CH07       | T2CH06     | T2CH05        | T2CH04      | T2CH03        | T2CH02     | T2CH01      | T2CH00     |

|          | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | 0          | 0           | 0          |

| T2CNA1   |              | 1           | 1           | 1            | 1       |         | 1      |            | ET2          | T20E0      | T2POL0        | TR2L        | TR2           | CPRL2      | SS2         | G2EN       |

|          | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | 0          | 0           | 0          |

| T2H1     | <            | <           | <           | <            | <       | <       | <      | c          | 12H1/        | 12H16      | 0112H         | 12H14       | 12H13         | 12H12      | 12H.1       | 12H10      |

|          |              |             |             |              |         |         | >      | >          | T2RH17       | T2RH16     | T2RH15        | T2RH14      | T2RH13        | T2RH12     | T2RH11      | T2RH10     |

| T2RH1    | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | 0          | 0           | 0          |

| FI LOCH  | 1            | 1           | 1           | 1            |         |         |        |            | T2CH17       | T2CH16     | T2CH15        | T2CH14      | T2CH13        | T2CH12     | T2CH11      | T2CH10     |

|          | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | 0          | 0           | 0          |

| T2CNB0   | I            |             |             |              |         |         |        |            | ET2L         | T20E1      | T2POL1        |             | TF2           | TF2L       | TCC2        | TC2L       |

|          | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | 0          | 0           | 0          |

| T2V0     | T2V015       | T2V014      | T2V013      | T2V012       | T2V011  | T2V010  | T2V09  | T2V08      | T2V07        | T2V06      | T2V05         | T2V04       | T2V03         | T2V02      | T2V01       | T2V00      |

|          | TORNIE       | T2R014      | T 2R013     | T2B012       | T2R011  | TORNIO  | TOBNG  | U          | T2B07        | U<br>TORNE | TOROF         | TORA        | TORN3         | TOBOD      | U<br>T2R01  | TORON      |

| T2R0     | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | 0          | 0           | 0          |

| U U U U  | T2C015       | T2C014      | T2C013      | T2C012       | T2C011  | T2C010  | T2C09  | T2C08      | T2C07        | T2C06      | T2C05         | T2C04       | T2C03         | T2C02      | T2C01       | T2C00      |

| 007      | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | 0          | 0           | 0          |

| T2CNB1   | <            | <           | <           | <            | 0       | 0       | 0      | 0          | ET2L         | 120E1      | 12POL1        | <           | 1F2           | TF2L       | TCC2        | TC2L       |

|          | U<br>T9//115 | U<br>T2V114 | U<br>T9V113 | U<br>T9//112 | T2V111  | T2V/110 | T2V19  | U<br>T2V18 | T2V17        | U<br>T2V16 | U<br>T2V15    | U<br>T2V/14 | T2V13         | U<br>T9V12 | U<br>T2V/11 | U<br>T2V10 |

| T2V1     | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | 0          | 0           | 0          |

| 13B1     | T2R115       | T2R114      | T2R113      | T2R112       | T2R111  | T2R110  | T2R19  | T2R18      | T2R17        | T2R16      | T2R15         | T2R14       | T2R13         | T2R12      | T2R11       | T2R10      |

|          | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | 0          | 0           | 0          |

| T2C1     | T2C115       | 12C114      | 12C113      | 12C112       | 12C111  | 12C110  | 12C19  | 12C18      | 12C17        | 12C16      | 12C15         | T2C14       | T2C13         | 12C12      | 12C11       | 12C10      |

|          | >            |             | >           | -            | >       | >       | -      | >          | T2C1         | TPDIV2     | T2DIV1        | TPDIVO      | TOMD          | 005        | OCEO        | сл.        |

| T2CFG0   | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | . 0        | 0           | 0          |

| T2CEG 1  |              |             |             |              |         |         |        |            | T2C1         | T2DIV2     | T2DIV1        | T2DIV0      | T2MD          | CCF1       | CCF0        | C/T2       |

| 5        | 0            | _           | 0           | 0            | 0       | 0       | 0      | 0          | 0            | 0          | 0             | 0           | 0             | 0          | 0           | 0          |

| ICDT0    | ICD1015      | ICD1014     | ICD1013     | ICDI012      | ICD1011 | ICD1010 |        | ICD108     | ICD107       | ICD106     | ICD105        | ICD104      | 1CD103        | ICD102     | ICDI01      |            |

| F CC     | ICDT115      | 2           | ICDT113     | ICDT112      | ICDT111 | ICDT110 | ICDT19 | ICDT18     | ICDT17       | ICDT16     | ICDT15        | ICDT14      | ICDT13        | ICDT12     | ICDT11      | ICDT10     |

| 1001     | DB           |             | DB          | DB           | DB      | DB      | DB     | DB         | DB           | DB         | DB            | DB          | DB            | DB         | DB          | DB         |

| ICDC     | I            |             | I           | I            | I       | I       | 1      |            | DME          | I          | REGE          | Ι           | CMD3          | CMD2       | CMD1        | CMD0       |

|          | 0            | 0           | 0           | 0            | 0       | 0       | 0      | 0          | DW           | 0          | DW            | 0           | DW            | MD         | DW          | DW         |

# Table 4. Peripheral Register Bit Functions and Reset Values (continued)

###

**MAXQ7667**

### **16-Bit, RISC, Microcontroller-Based, Ultrasonic Distance-Measuring System**

| CITOL       |        |        |        |        |        |        |        | REGI            | REGISTER BIT      |          |         |        |        |        |        |        |

|-------------|--------|--------|--------|--------|--------|--------|--------|-----------------|-------------------|----------|---------|--------|--------|--------|--------|--------|

|             | 15     | 14     | 13     | 12     | 7      | 10     | 6      | 8               | 7                 | 9        | ß       | 4      | m      | 7      | ÷      | •      |

| La          | BT15   | BT14   | BT 13  | BT12   | BT11   | BT10   | BT9    | BT8             | BT7               | BT6      | BT5     | BT4    | BT3    | BT2    | BT1    | BTO    |

| 5           | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0               | 0                 | 0        | 0       | 0      | 0      | 0      | 0      | 0      |

| aMT         | TMR15  | TMR14  | TMR13  | TMR12  | TMR11  | TMR10  | TMR9   | TMR8            | TMR7              | TMR6     | TMR5    | TMR4   | TMR3   | TMR2   | TMR1   | TMR0   |

|             | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0               | 0                 | 0        | 0       | 0      | 0      | 0      | 0      | 0      |

|             | BSTT   | BDS    |        |        |        |        | ВРН9   | BPH8            | BPH7              | BPH6     | BPH5    | BPH4   | BPH3   | BPH2   | BPH1   | BPHO   |