Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Active                                                                    |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | 276480                                                                    |

| Number of I/O                  | 119                                                                       |

| Number of Gates                | 1500000                                                                   |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                        |

| Package / Case                 | 256-LBGA                                                                  |

| Supplier Device Package        | 256-FPBGA (17x17)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/afs1500-fgg256i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Timing Characteristics**

Table 2-1 • Combinatorial Cell Propagation Delays

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Combinatorial Cell | Equation                  | Parameter       | -2   | -1   | Std. | Units |

|--------------------|---------------------------|-----------------|------|------|------|-------|

| INV                | Y = !A                    | t <sub>PD</sub> | 0.40 | 0.46 | 0.54 | ns    |

| AND2               | Y = A · B                 | t <sub>PD</sub> | 0.47 | 0.54 | 0.63 | ns    |

| NAND2              | Y = !(A · B)              | t <sub>PD</sub> | 0.47 | 0.54 | 0.63 | ns    |

| OR2                | Y = A + B                 | t <sub>PD</sub> | 0.49 | 0.55 | 0.65 | ns    |

| NOR2               | Y = !(A + B)              | t <sub>PD</sub> | 0.49 | 0.55 | 0.65 | ns    |

| XOR2               | Y = A ⊕ B                 | t <sub>PD</sub> | 0.74 | 0.84 | 0.99 | ns    |

| MAJ3               | Y = MAJ(A, B, C)          | t <sub>PD</sub> | 0.70 | 0.79 | 0.93 | ns    |

| XOR3               | $Y = A \oplus B \oplus C$ | t <sub>PD</sub> | 0.87 | 1.00 | 1.17 | ns    |

| MUX2               | Y = A !S + B S            | t <sub>PD</sub> | 0.51 | 0.58 | 0.68 | ns    |

| AND3               | $Y = A \cdot B \cdot C$   | t <sub>PD</sub> | 0.56 | 0.64 | 0.75 | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

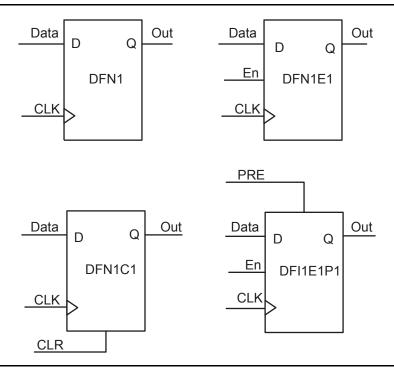

### Sample VersaTile Specifications—Sequential Module

The Fusion library offers a wide variety of sequential cells, including flip-flops and latches. Each has a data input and optional enable, clear, or preset. In this section, timing characteristics are presented for a representative sample from the library (Figure 2-5). For more details, refer to the *IGLOO*, *ProASIC3*, *SmartFusion and Fusion Macro Library Guide*.

Figure 2-5 • Sample of Sequential Cells

2-5 Revision 6

Table 2-7 • AFS250 Global Resource Timing

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Deceription                               |                   | -2                |                   | -1                |                   | Std.              |       |  |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|--|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |  |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.89              | 1.12              | 1.02              | 1.27              | 1.20              | 1.50              | ns    |  |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.88              | 1.14              | 1.00              | 1.30              | 1.17              | 1.53              | ns    |  |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock |                   |                   |                   |                   |                   |                   | ns    |  |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |                   |                   |                   |                   |                   |                   | ns    |  |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.26              |                   | 0.30              |                   | 0.35              | ns    |  |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

Table 2-8 • AFS090 Global Resource Timing

Commercial Temperature Range Conditions: T<sub>.I</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Decemention                               | -2                |                   | <b>–1</b>         |                   | S                 | Units             |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|

|                      | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 0.84              | 1.07              | 0.96              | 1.21              | 1.13              | 1.43              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 0.83              | 1.10              | 0.95              | 1.25              | 1.12              | 1.47              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock |                   |                   |                   |                   |                   |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |                   |                   |                   |                   |                   |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.27              |                   | 0.30              |                   | 0.36              | ns    |

#### Notes:

- 1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

2-17 Revision 6

## **CCC and PLL Characteristics**

## **Timing Characteristics**

## Table 2-12 • Fusion CCC/PLL Specification

| Parameter                                                          | Min.                        | Тур.             | Max.                         | Unit |

|--------------------------------------------------------------------|-----------------------------|------------------|------------------------------|------|

| Clock Conditioning Circuitry Input Frequency f <sub>IN_CCC</sub>   | 1.5                         |                  | 350                          | MHz  |

| Clock Conditioning Circuitry Output Frequency f <sub>OUT_CCC</sub> | 0.75                        |                  | 350                          | MHz  |

| Delay Increments in Programmable Delay Blocks <sup>1, 2</sup>      |                             | 160 <sup>3</sup> |                              | ps   |

| Number of Programmable Values in Each Programmable Delay Block     |                             |                  | 32                           |      |

| Input Period Jitter                                                |                             |                  | 1.5                          | ns   |

| CCC Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub>         | Max Pea                     | k-to-Peak Po     | eriod Jitter                 |      |

|                                                                    | 1 Global<br>Network<br>Used |                  | 3 Global<br>Networks<br>Used |      |

| 0.75 MHz to 24 MHz                                                 | 1.00%                       |                  | 1.00%                        |      |

| 24 MHz to 100 MHz                                                  | 1.50%                       |                  | 1.50%                        |      |

| 100 MHz to 250 MHz                                                 | 2.25%                       |                  | 2.25%                        |      |

| 250 MHz to 350 MHz                                                 | 3.50%                       |                  | 3.50%                        |      |

| Acquisition Time LockControl = 0                                   |                             |                  | 300                          | μs   |

| LockControl = 1                                                    |                             |                  | 6.0                          | ms   |

| Tracking Jitter <sup>4</sup> LockControl = 0                       |                             |                  | 1.6                          | ns   |

| LockControl = 1                                                    |                             |                  | 0.8                          | ns   |

| Output Duty Cycle                                                  | 48.5                        |                  | 51.5                         | %    |

| Delay Range in Block: Programmable Delay 1 <sup>1, 2</sup>         | 0.6                         |                  | 5.56                         | ns   |

| Delay Range in Block: Programmable Delay 2 1, 2                    | 0.025                       |                  | 5.56                         | ns   |

| Delay Range in Block: Fixed Delay <sup>1, 2</sup>                  |                             | 2.2              |                              | ns   |

#### Notes:

- 1. This delay is a function of voltage and temperature. See Table 3-7 on page 3-9 for deratings.

- 2.  $T_J = 25^{\circ}C$ , VCC = 1.5 V

- 3. When the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available. Refer to the Libero SoC Online Help associated with the core for more information.

- 4. Tracking jitter is defined as the variation in clock edge position of PLL outputs with reference to PLL input clock edge. Tracking jitter does not measure the variation in PLL output period, which is covered by period jitter parameter.

The following signals are used to configure the FIFO4K18 memory element.

#### WW and RW

These signals enable the FIFO to be configured in one of the five allowable aspect ratios (Table 2-33).

Table 2-33 • Aspect Ratio Settings for WW[2:0]

| WW2, WW1, WW0 | RW2, RW1, RW0 | D×W      |

|---------------|---------------|----------|

| 000           | 000           | 4k×1     |

| 001           | 001           | 2k×2     |

| 010           | 010           | 1k×4     |

| 011           | 011           | 512×9    |

| 100           | 100           | 256×18   |

| 101, 110, 111 | 101, 110, 111 | Reserved |

#### WBLK and RBLK

These signals are active low and will enable the respective ports when Low. When the RBLK signal is High, the corresponding port's outputs hold the previous value.

#### **WEN** and **REN**

Read and write enables. WEN is active low and REN is active high by default. These signals can be configured as active high or low.

#### WCLK and RCLK

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

#### **RPIPE**

This signal is used to specify pipelined read on the output. A Low on RPIPE indicates a nonpipelined read, and the data appears on the output in the same clock cycle. A High indicates a pipelined read, and data appears on the output in the next clock cycle.

#### RESET

This active low signal resets the output to zero when asserted. It resets the FIFO counters. It also sets all the RD pins Low, the FULL and AFULL pins Low, and the EMPTY and AEMPTY pins High (Table 2-34).

Table 2-34 • Input Data Signal Usage for Different Aspect Ratios

| D×W    | WD/RD Unused       |

|--------|--------------------|

| 4k×1   | WD[17:1], RD[17:1] |

| 2k×2   | WD[17:2], RD[17:2] |

| 1k×4   | WD[17:4], RD[17:4] |

| 512×9  | WD[17:9], RD[17:9] |

| 256×18 | -                  |

### WD

This is the input data bus and is 18 bits wide. Not all 18 bits are valid in all configurations. When a data width less than 18 is specified, unused higher-order signals must be grounded (Table 2-34).

#### RD

This is the output data bus and is 18 bits wide. Not all 18 bits are valid in all configurations. Like the WD bus, high-order bits become unusable if the data width is less than 18. The output data on unused pins is undefined (Table 2-34).

2-69 Revision 6

The AEMPTY flag is asserted when the difference between the write address and the read address is less than a predefined value. In the example above, a value of 200 for AEVAL means that the AEMPTY flag will be asserted when a read causes the difference between the write address and the read address to drop to 200. It will stay asserted until that difference rises above 200. Note that the FIFO can be configured with different read and write widths; in this case, the AFVAL setting is based on the number of write data entries and the AEVAL setting is based on the number of read data entries. For aspect ratios of 512×9 and 256×18, only 4,096 bits can be addressed by the 12 bits of AFVAL and AEVAL. The number of words must be multiplied by 8 and 16, instead of 9 and 18. The SmartGen tool automatically uses the proper values. To avoid halfwords being written or read, which could happen if different read and write aspect ratios are specified, the FIFO will assert FULL or EMPTY as soon as at least a minimum of one word cannot be written or read. For example, if a two-bit word is written and a four-bit word is being read, the FIFO will remain in the empty state when the first word is written. This occurs even if the FIFO is not completely empty, because in this case, a complete word cannot be read. The same is applicable in the full state. If a four-bit word is written and a two-bit word is read, the FIFO is full and one word is read. The FULL flag will remain asserted because a complete word cannot be written at this point.

2-71 Revision 6

## **ADC Interface Timing**

Table 2-48 • ADC Interface Timing

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter                | Description                                    | -2     | -1     | Std.   | Units |

|--------------------------|------------------------------------------------|--------|--------|--------|-------|

| t <sub>SUMODE</sub>      | Mode Pin Setup Time                            | 0.56   | 0.64   | 0.75   | ns    |

| t <sub>HDMODE</sub>      | Mode Pin Hold Time                             | 0.26   | 0.29   | 0.34   | ns    |

| t <sub>sutvc</sub>       | Clock Divide Control (TVC) Setup Time          | 0.68   | 0.77   | 0.90   | ns    |

| t <sub>HDTVC</sub>       | Clock Divide Control (TVC) Hold Time           | 0.32   | 0.36   | 0.43   | ns    |

| t <sub>sustc</sub>       | Sample Time Control (STC) Setup Time           | 1.58   | 1.79   | 2.11   | ns    |

| t <sub>HDSTC</sub>       | Sample Time Control (STC) Hold Time            | 1.27   | 1.45   | 1.71   | ns    |

| t <sub>SUVAREFSEL</sub>  | Voltage Reference Select (VAREFSEL) Setup Time | 0.00   | 0.00   | 0.00   | ns    |

| t <sub>HDVAREFSEL</sub>  | Voltage Reference Select (VAREFSEL) Hold Time  | 0.67   | 0.76   | 0.89   | ns    |

| tsuchnum                 | Channel Select (CHNUMBER) Setup Time           | 0.90   | 1.03   | 1.21   | ns    |

| t <sub>HDCHNUM</sub>     | Channel Select (CHNUMBER) Hold Time            | 0.00   | 0.00   | 0.00   | ns    |

| t <sub>SUADCSTART</sub>  | Start of Conversion (ADCSTART) Setup Time      | 0.75   | 0.85   | 1.00   | ns    |

| t <sub>HDADCSTART</sub>  | Start of Conversion (ADCSTART) Hold Time       | 0.43   | 0.49   | 0.57   | ns    |

| t <sub>CK2QBUSY</sub>    | Busy Clock-to-Q                                | 1.33   | 1.51   | 1.78   | ns    |

| t <sub>CK2QCAL</sub>     | Power-Up Calibration Clock-to-Q                | 0.63   | 0.71   | 0.84   | ns    |

| t <sub>CK2QVAL</sub>     | Valid Conversion Result Clock-to-Q             | 3.12   | 3.55   | 4.17   | ns    |

| t <sub>CK2QSAMPLE</sub>  | Sample Clock-to-Q                              | 0.22   | 0.25   | 0.30   | ns    |

| t <sub>CK2QRESULT</sub>  | Conversion Result Clock-to-Q                   | 2.53   | 2.89   | 3.39   | ns    |

| t <sub>CLR2QBUSY</sub>   | Busy Clear-to-Q                                | 2.06   | 2.35   | 2.76   | ns    |

| t <sub>CLR2QCAL</sub>    | Power-Up Calibration Clear-to-Q                | 2.15   | 2.45   | 2.88   | ns    |

| t <sub>CLR2QVAL</sub>    | Valid Conversion Result Clear-to-Q             | 2.41   | 2.74   | 3.22   | ns    |

| t <sub>CLR2QSAMPLE</sub> | Sample Clear-to-Q                              | 2.17   | 2.48   | 2.91   | ns    |

| t <sub>CLR2QRESULT</sub> | Conversion result Clear-to-Q                   | 2.25   | 2.56   | 3.01   | ns    |

| t <sub>RECCLR</sub>      | Recovery Time of Clear                         | 0.00   | 0.00   | 0.00   | ns    |

| t <sub>REMCLR</sub>      | Removal Time of Clear                          | 0.63   | 0.72   | 0.84   | ns    |

| t <sub>MPWSYSCLK</sub>   | Clock Minimum Pulse Width for the ADC          | 4.00   | 4.00   | 4.00   | ns    |

| t <sub>FMAXSYSCLK</sub>  | Clock Maximum Frequency for the ADC            | 100.00 | 100.00 | 100.00 | MHz   |

## **Analog Configuration MUX**

The ACM is the interface between the FPGA, the Analog Block configurations, and the real-time counter. Microsemi Libero SoC will generate IP that will load and configure the Analog Block via the ACM. However, users are not limited to using the Libero SoC IP. This section provides a detailed description of the ACM's register map, truth tables for proper configuration of the Analog Block and RTC, as well as timing waveforms so users can access and control the ACM directly from their designs.

The Analog Block contains four 8-bit latches per Analog Quad that are initialized through the ACM. These latches act as configuration bits for Analog Quads. The ACM block runs from the core voltage supply (1.5 V).

Access to the ACM is achieved via 8-bit address and data busses with enables. The pin list is provided in Table 2-36 on page 2-78. The ACM clock speed is limited to a maximum of 10 MHz, more than sufficient to handle the low-bandwidth requirements of configuring the Analog Block and the RTC (sub-block of the Analog Block).

Table 2-54 decodes the ACM address space and maps it to the corresponding Analog Quad and configuration byte for that quad.

Table 2-54 • ACM Address Decode Table for Analog Quad

| ACMADDR [7:0] in<br>Decimal | Name      | Description             | Associated Peripheral |

|-----------------------------|-----------|-------------------------|-----------------------|

| 0                           | -         | _                       | Analog Quad           |

| 1                           | AQ0       | Byte 0                  | Analog Quad           |

| 2                           | AQ0       | Byte 1                  | Analog Quad           |

| 3                           | AQ0       | Byte 2                  | Analog Quad           |

| 4                           | AQ0       | Byte 3                  | Analog Quad           |

| 5                           | AQ1       | Byte 0                  | Analog Quad           |

|                             |           |                         | Analog Quad           |

|                             |           |                         |                       |

| 36                          | AQ8       | Byte 3                  | Analog Quad           |

| 37                          | AQ9       | Byte 0                  | Analog Quad           |

| 38                          | AQ9       | Byte 1                  | Analog Quad           |

| 39                          | AQ9       | Byte 2                  | Analog Quad           |

| 40                          | AQ9       | Byte 3                  | Analog Quad           |

| 41                          |           | Undefined               | Analog Quad           |

|                             |           | Undefined               | Analog Quad           |

|                             |           |                         |                       |

| 63                          |           | Undefined               | RTC                   |

| 64                          | COUNTER0  | Counter bits 7:0        | RTC                   |

| 65                          | COUNTER1  | Counter bits 15:8       | RTC                   |

| 66                          | COUNTER2  | Counter bits 23:16      | RTC                   |

| 67                          | COUNTER3  | Counter bits 31:24      | RTC                   |

| 68                          | COUNTER4  | Counter bits 39:32      | RTC                   |

| 72                          | MATCHREG0 | Match register bits 7:0 | RTC                   |

## **I/O Registers**

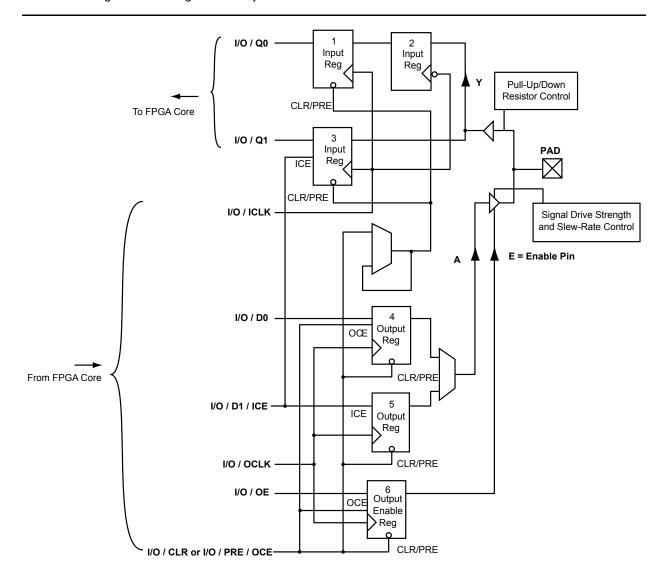

Each I/O module contains several input, output, and enable registers. Refer to Figure 2-100 for a simplified representation of the I/O block.

The number of input registers is selected by a set of switches (not shown in Figure 2-100) between registers to implement single or differential data transmission to and from the FPGA core. The Designer software sets these switches for the user.

A common CLR/PRE signal is employed by all I/O registers when I/O register combining is used. Input register 2 does not have a CLR/PRE pin, as this register is used for DDR implementation. The I/O register combining must satisfy some rules.

Note: Fusion I/Os have registers to support DDR functionality (see the "Double Data Rate (DDR) Support" section on page 2-139 for more information).

Figure 2-100 • I/O Block Logical Representation

Table 2-83 • Fusion Pro I/O Supported Standards and Corresponding VREF and VTT Voltages

| I/O Standard               | Input/Output Supply<br>Voltage (VCCI_TYP) | Input Reference Voltage<br>(VREF_TYP) | Board Termination Voltage (VTT_TYP) |

|----------------------------|-------------------------------------------|---------------------------------------|-------------------------------------|

| LVTTL/LVCMOS 3.3 V         | 3.30 V                                    | -                                     | -                                   |

| LVCMOS 2.5 V               | 2.50 V                                    | -                                     | -                                   |

| LVCMOS 2.5 V / 5.0 V Input | 2.50 V                                    | -                                     | -                                   |

| LVCMOS 1.8 V               | 1.80 V                                    | -                                     | -                                   |

| LVCMOS 1.5 V               | 1.50 V                                    | -                                     | _                                   |

| PCI 3.3 V                  | 3.30 V                                    | -                                     | -                                   |

| PCI-X 3.3 V                | 3.30 V                                    | -                                     | _                                   |

| GTL+ 3.3 V                 | 3.30 V                                    | 1.00 V                                | 1.50 V                              |

| GTL+ 2.5 V                 | 2.50 V                                    | 1.00 V                                | 1.50 V                              |

| GTL 3.3 V                  | 3.30 V                                    | 0.80 V                                | 1.20 V                              |

| GTL 2.5 V                  | 2.50 V                                    | 0.80 V                                | 1.20 V                              |

| HSTL Class I               | 1.50 V                                    | 0.75 V                                | 0.75 V                              |

| HSTL Class II              | 1.50 V                                    | 0.75 V                                | 0.75 V                              |

| SSTL3 Class I              | 3.30 V                                    | 1.50 V                                | 1.50 V                              |

| SSTL3 Class II             | 3.30 V                                    | 1.50 V                                | 1.50 V                              |

| SSTL2 Class I              | 2.50 V                                    | 1.25 V                                | 1.25 V                              |

| SSTL2 Class II             | 2.50 V                                    | 1.25 V                                | 1.25 V                              |

| LVDS, BLVDS, M-LVDS        | 2.50 V                                    | _                                     | -                                   |

| LVPECL                     | 3.30 V                                    | -                                     | -                                   |

2-155 Revision 6

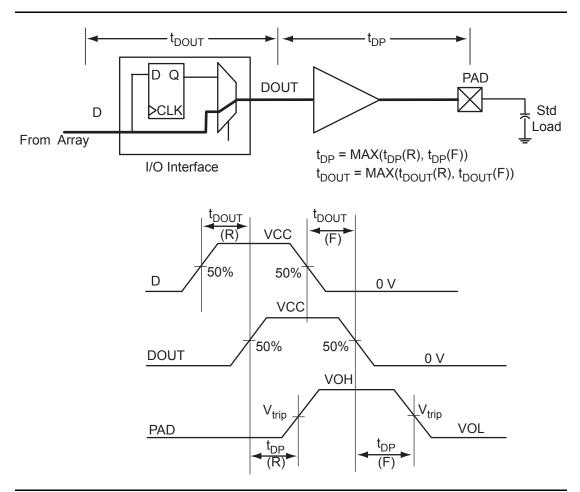

Figure 2-117 • Output Buffer Model and Delays (example)

Table 2-96 • I/O Output Buffer Maximum Resistances <sup>1</sup> (continued)

| Standard                      | Drive Strength              | R <sub>PULL-DOWN</sub> (ohms) <sup>2</sup> | R <sub>PULL-UP</sub><br>(ohms) <sup>3</sup> |

|-------------------------------|-----------------------------|--------------------------------------------|---------------------------------------------|

| HSTL (I)                      | 8 mA                        | 50                                         | 50                                          |

| HSTL (II)                     | 15 mA                       | 25                                         | 25                                          |

| SSTL2 (I)                     | 17 mA                       | 27                                         | 31                                          |

| SSTL2 (II)                    | 21 mA                       | 13                                         | 15                                          |

| SSTL3 (I)                     | 16 mA                       | 44                                         | 69                                          |

| SSTL3 (II)                    | 24 mA                       | 18                                         | 32                                          |

| Applicable to Advanced I/O Ba | nks                         | 1                                          |                                             |

| 3.3 V LVTTL / 3.3 V LVCMOS    | 2 mA                        | 100                                        | 300                                         |

|                               | 4 mA                        | 100                                        | 300                                         |

|                               | 6 mA                        | 50                                         | 150                                         |

|                               | 8 mA                        | 50                                         | 150                                         |

|                               | 12 mA                       | 25                                         | 75                                          |

|                               | 16 mA                       | 17                                         | 50                                          |

|                               | 24 mA                       | 11                                         | 33                                          |

| 2.5 V LVCMOS                  | 2 mA                        | 100                                        | 200                                         |

|                               | 4 mA                        | 100                                        | 200                                         |

|                               | 6 mA                        | 50                                         | 100                                         |

|                               | 8 mA                        | 50                                         | 100                                         |

|                               | 12 mA                       | 25                                         | 50                                          |

|                               | 16 mA                       | 20                                         | 40                                          |

|                               | 24 mA                       | 11                                         | 22                                          |

| 1.8 V LVCMOS                  | 2 mA                        | 200                                        | 225                                         |

|                               | 4 mA                        | 100                                        | 112                                         |

|                               | 6 mA                        | 50                                         | 56                                          |

|                               | 8 mA                        | 50                                         | 56                                          |

|                               | 12 mA                       | 20                                         | 22                                          |

|                               | 16 mA                       | 20                                         | 22                                          |

| 1.5 V LVCMOS                  | 2 mA                        | 200                                        | 224                                         |

|                               | 4 mA                        | 100                                        | 112                                         |

|                               | 6 mA                        | 67                                         | 75                                          |

|                               | 8 mA                        | 33                                         | 37                                          |

|                               | 12 mA                       | 33                                         | 37                                          |

| 3.3 V PCI/PCI-X               | Per PCI/PCI-X specification | 25                                         | 75                                          |

#### Notes:

These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCC, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website: http://www.microsemi.com/soc/techdocs/models/ibis.html.

<sup>2.</sup>  $R_{(PULL-DOWN-MAX)} = VOLspec / I_{OLspec}$

<sup>3.</sup> R<sub>(PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / IOHspec

Table 2-121 • 1.8 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V Applicable to Pro I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zh</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 12.10           | 0.04             | 1.45            | 1.91             | 0.43              | 9.59            | 12.10           | 2.78            | 1.64            | 11.83            | 14.34            | ns    |

|                   | -1             | 0.56              | 10.30           | 0.04             | 1.23            | 1.62             | 0.36              | 8.16            | 10.30           | 2.37            | 1.39            | 10.06            | 12.20            | ns    |

|                   | -2             | 0.49              | 9.04            | 0.03             | 1.08            | 1.42             | 0.32              | 7.16            | 9.04            | 2.08            | 1.22            | 8.83             | 10.71            | ns    |

| 4 mA              | Std.           | 0.66              | 7.05            | 0.04             | 1.45            | 1.91             | 0.43              | 6.20            | 7.05            | 3.25            | 2.86            | 8.44             | 9.29             | ns    |

|                   | -1             | 0.56              | 6.00            | 0.04             | 1.23            | 1.62             | 0.36              | 5.28            | 6.00            | 2.76            | 2.44            | 7.18             | 7.90             | ns    |

|                   | -2             | 0.49              | 5.27            | 0.03             | 1.08            | 1.42             | 0.32              | 4.63            | 5.27            | 2.43            | 2.14            | 6.30             | 6.94             | ns    |

| 8 mA              | Std.           | 0.66              | 4.52            | 0.04             | 1.45            | 1.91             | 0.43              | 4.47            | 4.52            | 3.57            | 3.47            | 6.70             | 6.76             | ns    |

|                   | <b>–</b> 1     | 0.56              | 3.85            | 0.04             | 1.23            | 1.62             | 0.36              | 3.80            | 3.85            | 3.04            | 2.95            | 5.70             | 5.75             | ns    |

|                   | -2             | 0.49              | 3.38            | 0.03             | 1.08            | 1.42             | 0.32              | 3.33            | 3.38            | 2.66            | 2.59            | 5.00             | 5.05             | ns    |

| 12 mA             | Std.           | 0.66              | 4.12            | 0.04             | 1.45            | 1.91             | 0.43              | 4.20            | 3.99            | 3.63            | 3.62            | 6.43             | 6.23             | ns    |

|                   | -1             | 0.56              | 3.51            | 0.04             | 1.23            | 1.62             | 0.36              | 3.57            | 3.40            | 3.09            | 3.08            | 5.47             | 5.30             | ns    |

|                   | -2             | 0.49              | 3.08            | 0.03             | 1.08            | 1.42             | 0.32              | 3.14            | 2.98            | 2.71            | 2.71            | 4.81             | 4.65             | ns    |

| 16 mA             | Std.           | 0.66              | 3.80            | 0.04             | 1.45            | 1.91             | 0.43              | 3.87            | 3.09            | 3.73            | 4.24            | 6.10             | 5.32             | ns    |

|                   | <b>–1</b>      | 0.56              | 3.23            | 0.04             | 1.23            | 1.62             | 0.36              | 3.29            | 2.63            | 3.18            | 3.60            | 5.19             | 4.53             | ns    |

|                   | -2             | 0.49              | 2.83            | 0.03             | 1.08            | 1.42             | 0.32              | 2.89            | 2.31            | 2.79            | 3.16            | 4.56             | 3.98             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

2-189 Revision 6

### **Timing Characteristics**

Table 2-128 • 1.5 V LVCMOS Low Slew

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Pro I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 14.11           | 0.04             | 1.70            | 2.14             | 0.43              | 14.37           | 13.14           | 3.40            | 2.68            | 16.61            | 15.37            | ns    |

|                   | -1             | 0.56              | 12.00           | 0.04             | 1.44            | 1.82             | 0.36              | 12.22           | 11.17           | 2.90            | 2.28            | 14.13            | 13.08            | ns    |

|                   | -2             | 0.49              | 10.54           | 0.03             | 1.27            | 1.60             | 0.32              | 10.73           | 9.81            | 2.54            | 2.00            | 12.40            | 11.48            | ns    |

| 4 mA              | Std.           | 0.66              | 11.23           | 0.04             | 1.70            | 2.14             | 0.43              | 11.44           | 9.87            | 3.77            | 3.36            | 13.68            | 12.10            | ns    |

|                   | -1             | 0.56              | 9.55            | 0.04             | 1.44            | 1.82             | 0.36              | 9.73            | 8.39            | 3.21            | 2.86            | 11.63            | 10.29            | ns    |

|                   | -2             | 0.49              | 8.39            | 0.03             | 1.27            | 1.60             | 0.32              | 8.54            | 7.37            | 2.81            | 2.51            | 10.21            | 9.04             | ns    |

| 8 mA              | Std.           | 0.66              | 10.45           | 0.04             | 1.70            | 2.14             | 0.43              | 10.65           | 9.24            | 3.84            | 3.55            | 12.88            | 11.48            | ns    |

|                   | -1             | 0.56              | 8.89            | 0.04             | 1.44            | 1.82             | 0.36              | 9.06            | 7.86            | 3.27            | 3.02            | 10.96            | 9.76             | ns    |

|                   | -2             | 0.49              | 7.81            | 0.03             | 1.27            | 1.60             | 0.32              | 7.95            | 6.90            | 2.87            | 2.65            | 9.62             | 8.57             | ns    |

| 12 mA             | Std.           | 0.66              | 10.02           | 0.04             | 1.70            | 2.14             | 0.43              | 10.20           | 9.23            | 3.97            | 4.22            | 12.44            | 11.47            | ns    |

|                   | -1             | 0.56              | 8.52            | 0.04             | 1.44            | 1.82             | 0.36              | 8.68            | 7.85            | 3.38            | 3.59            | 10.58            | 9.75             | ns    |

|                   | -2             | 0.49              | 7.48            | 0.03             | 1.27            | 1.60             | 0.32              | 7.62            | 6.89            | 2.97            | 3.15            | 9.29             | 8.56             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

Table 2-129 • 1.5 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Pro I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOU</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 8.53            | 0.04             | 1.70            | 2.14             | 0.43             | 7.26            | 8.53            | 3.39            | 2.79            | 9.50             | 10.77            | ns    |

|                   | <b>–</b> 1     | 0.56              | 7.26            | 0.04             | 1.44            | 1.82             | 0.36             | 6.18            | 7.26            | 2.89            | 2.37            | 8.08             | 9.16             | ns    |

|                   | -2             | 0.49              | 6.37            | 0.03             | 1.27            | 1.60             | 0.32             | 5.42            | 6.37            | 2.53            | 2.08            | 7.09             | 8.04             | ns    |

| 4 mA              | Std.           | 0.66              | 5.41            | 0.04             | 1.70            | 2.14             | 0.43             | 5.22            | 5.41            | 3.75            | 3.48            | 7.45             | 7.65             | ns    |

|                   | <b>–</b> 1     | 0.56              | 4.60            | 0.04             | 1.44            | 1.82             | 0.36             | 4.44            | 4.60            | 3.19            | 2.96            | 6.34             | 6.50             | ns    |

|                   | -2             | 0.49              | 4.04            | 0.03             | 1.27            | 1.60             | 0.32             | 3.89            | 4.04            | 2.80            | 2.60            | 5.56             | 5.71             | ns    |

| 8 mA              | Std.           | 0.66              | 4.80            | 0.04             | 1.70            | 2.14             | 0.43             | 4.89            | 4.75            | 3.83            | 3.67            | 7.13             | 6.98             | ns    |

|                   | <b>–</b> 1     | 0.56              | 4.09            | 0.04             | 1.44            | 1.82             | 0.36             | 4.16            | 4.04            | 3.26            | 3.12            | 6.06             | 5.94             | ns    |

|                   | -2             | 0.49              | 3.59            | 0.03             | 1.27            | 1.60             | 0.32             | 3.65            | 3.54            | 2.86            | 2.74            | 5.32             | 5.21             | ns    |

| 12 mA             | Std.           | 0.66              | 4.42            | 0.04             | 1.70            | 2.14             | 0.43             | 4.50            | 3.62            | 3.96            | 4.37            | 6.74             | 5.86             | ns    |

|                   | <b>–</b> 1     | 0.56              | 3.76            | 0.04             | 1.44            | 1.82             | 0.36             | 3.83            | 3.08            | 3.37            | 3.72            | 5.73             | 4.98             | ns    |

|                   | -2             | 0.49              | 3.30            | 0.03             | 1.27            | 1.60             | 0.32             | 3.36            | 2.70            | 2.96            | 3.27            | 5.03             | 4.37             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

## Voltage Referenced I/O Characteristics

3.3 V GTL

Gunning Transceiver Logic is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 3.3 V.

Table 2-138 • Minimum and Maximum DC Input and Output Levels

| 3.3 V GTL          |           | VIL         | VIH         |           | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|--------------------|-----------|-------------|-------------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength  | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 20 mA <sup>3</sup> | -0.3      | VREF - 0.05 | VREF + 0.05 | 3.6       | 0.4       | -         | 20  | 20 | 181                     | 268                     | 10                      | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

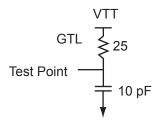

Figure 2-124 • AC Loading

Table 2-139 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF - 0.05   | VREF + 0.05    | 0.8                  | 0.8             | 1.2            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

## Timing Characteristics

Table 2-140 • 3.3 V GTL

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V, VREF = 0.8 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zh</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.08            | 0.04             | 2.93            | 0.43              | 2.04            | 2.08            |                 |                 | 4.27             | 4.31             | ns    |

| <b>-1</b>      | 0.56              | 1.77            | 0.04             | 2.50            | 0.36              | 1.73            | 1.77            |                 |                 | 3.63             | 3.67             | ns    |

| -2             | 0.49              | 1.55            | 0.03             | 2.19            | 0.32              | 1.52            | 1.55            |                 |                 | 3.19             | 3.22             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

2-199 Revision 6

## **User-Defined Supply Pins**

#### VREF I/O Voltage Reference

Reference voltage for I/O minibanks. Both AFS600 and AFS1500 (north bank only) support Microsemi Pro I/O. These I/O banks support voltage reference standard I/O. The VREF pins are configured by the user from regular I/Os, and any I/O in a bank, except JTAG I/Os, can be designated as the voltage reference I/O. Only certain I/O standards require a voltage reference—HSTL (I) and (II), SSTL2 (I) and (II), SSTL3 (I) and GTL/GTL+. One VREF pin can support the number of I/Os available in its minibank.

#### VAREF Analog Reference Voltage

The Fusion device can be configured to generate a 2.56 V internal reference voltage that can be used by the ADC. While using the internal reference, the reference voltage is output on the VAREF pin for use as a system reference. If a different reference voltage is required, it can be supplied by an external source and applied to this pin. The valid range of values that can be supplied to the ADC is 1.0 V to 3.3 V. When VAREF is internally generated by the Fusion device, a bypass capacitor must be connected from this pin to ground. The value of the bypass capacitor should be between 3.3 µF and 22 µF, which is based on the needs of the individual designs. The choice of the capacitor value has an impact on the settling time it takes the VAREF signal to reach the required specification of 2.56 V to initiate valid conversions by the ADC. If the lower capacitor value is chosen, the settling time required for VAREF to achieve 2.56 V will be shorter than when selecting the larger capacitor value. The above range of capacitor values supports the accuracy specification of the ADC, which is detailed in the datasheet. Designers choosing the smaller capacitor value will not obtain as much margin in the accuracy as that achieved with a larger capacitor value. Depending on the capacitor value selected in the Analog System Builder, a tool in Libero SoC, an automatic delay circuit will be generated using logic tiles available within the FPGA to ensure that VAREF has achieved the 2.56 V value. Microsemi recommends customers use 10 uF as the value of the bypass capacitor. Designers choosing to use an external VAREF need to ensure that a stable and clean VAREF source is supplied to the VAREF pin before initiating conversions by the ADC. Designers should also make sure that the ADCRESET signal is deasserted before initiating valid conversions.<sup>2</sup>

If the user connects VAREF to external 3.3 V on their board, the internal VAREF driving OpAmp tries to bring the pin down to the nominal 2.56 V until the device is programmed and up/functional. Under this scenario, it is recommended to connect an external 3.3 V supply through a ~1 KOhm resistor to limit current, along with placing a 10-100nF capacitor between VAREF and GNDA.

## **User Pins**

#### I/O User Input/Output

The I/O pin functions as an input, output, tristate, or bidirectional buffer. Input and output signal levels are compatible with the I/O standard selected. Unused I/O pins are configured as inputs with pull-up resistors.

During programming, I/Os become tristated and weakly pulled up to VCCI. With the VCCI and VCC supplies continuously powered up, when the device transitions from programming to operating mode, the I/Os get instantly configured to the desired user configuration.

Unused I/Os are configured as follows:

- · Output buffer is disabled (with tristate value of high impedance)

- Input buffer is disabled (with tristate value of high impedance)

- · Weak pull-up is programmed

### Axy Analog Input/Output

Analog I/O pin, where x is the analog pad type (C = current pad, G = Gate driver pad, T = Temperature pad, V = Voltage pad) and y is the Analog Quad number (0 to 9). There is a minimum 1 M $\Omega$  to ground on AV, AC, and AT. This pin can be left floating when it is unused.

2-225 Revision 6

<sup>2.</sup> The ADC is functional with an external reference down to 1V, however to meet the performance parameters highlighted in the datasheet refer to the VAREF specification in Table 3-2 on page 3-3.

#### TMS Test Mode Select

The TMS pin controls the use of the IEEE1532 boundary scan pins (TCK, TDI, TDO, TRST). There is an internal weak pull-up resistor on the TMS pin.

#### TRST Boundary Scan Reset Pin

The TRST pin functions as an active low input to asynchronously initialize (or reset) the boundary scan circuitry. There is an internal weak pull-up resistor on the TRST pin. If JTAG is not used, an external pull-down resistor could be included to ensure the TAP is held in reset mode. The resistor values must be chosen from Table 2-183 and must satisfy the parallel resistance value requirement. The values in Table 2-183 correspond to the resistor recommended when a single device is used and to the equivalent parallel resistor when multiple devices are connected via a JTAG chain.

In critical applications, an upset in the JTAG circuit could allow entering an undesired JTAG state. In such cases, Microsemi recommends tying off TRST to GND through a resistor placed close to the FPGA pin.

Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements.

## **Special Function Pins**

#### NC No Connect

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

#### DC Don't Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

#### NCAP Negative Capacitor

Negative Capacitor is where the negative terminal of the charge pump capacitor is connected. A capacitor, with a  $2.2 \, \mu F$  recommended value, is required to connect between PCAP and NCAP.

#### PCAP Positive Capacitor

Positive Capacitor is where the positive terminal of the charge pump capacitor is connected. A capacitor, with a 2.2 µF recommended value, is required to connect between PCAP and NCAP.

### PUB Push Button

*Push button* is the connection for the external momentary switch used to turn on the 1.5 V voltage regulator and can be floating if not used.

#### PTBASE Pass Transistor Base

Pass Transistor Base is the control signal of the voltage regulator. This pin should be connected to the base of the external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.

### PTEM Pass Transistor Emitter

Pass Transistor Emitter is the feedback input of the voltage regulator.

This pin should be connected to the emitter of the external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.

## XTAL1 Crystal Oscillator Circuit Input

Input to crystal oscillator circuit. Pin for connecting external crystal, ceramic resonator, RC network, or external clock input. When using an external crystal or ceramic oscillator, external capacitors are also recommended (Please refer to the crystal oscillator manufacturer for proper capacitor value).

If using external RC network or clock input, XTAL1 should be used and XTAL2 left unconnected. In the case where the Crystal Oscillator block is not used, the XTAL1 pin should be connected to GND and the XTAL2 pin should be left floating.

2-227 Revision 6

Table 3-9 • AFS600 Quiescent Supply Current Characteristics

| Parameter          | Description                | Conditions                                                            | Temp.                  | Min | Тур  | Max | Unit |

|--------------------|----------------------------|-----------------------------------------------------------------------|------------------------|-----|------|-----|------|

| ICC <sup>1</sup>   | 1.5 V quiescent current    | Operational standby <sup>4</sup> ,                                    | T <sub>J</sub> = 25°C  |     | 13   | 25  | mA   |

|                    |                            | VCC = 1.575 V                                                         | T <sub>J</sub> = 85°C  |     | 20   | 45  | mA   |

|                    |                            |                                                                       | T <sub>J</sub> =100°C  |     | 25   | 75  | mA   |

|                    |                            | Standby mode <sup>5</sup> or Sleep mode <sup>6</sup> , VCC = 0 V      |                        |     | 0    | 0   | μA   |

| ICC33 <sup>2</sup> | 3.3 V analog supplies      | Operational standby <sup>4</sup> ,                                    | $T_J = 25^{\circ}C$    |     | 9.8  | 13  | mA   |

|                    | current                    | VCC33 = 3.63 V                                                        | T <sub>J</sub> = 85°C  |     | 10.7 | 14  | mA   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 10.8 | 15  | mA   |

|                    |                            | Operational standby,                                                  | $T_J = 25^{\circ}C$    |     | 0.31 | 2   | mA   |

|                    |                            | only Analog Quad and -3.3 V output ON, VCC33 = 3.63 V                 | $T_J = 85^{\circ}C$    |     | 0.35 | 2   | mA   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 0.45 | 2   | mA   |

|                    |                            | Standby mode <sup>5</sup> ,                                           | $T_J = 25^{\circ}C$    |     | 2.8  | 3.6 | mA   |

|                    |                            | VCC33 = 3.63 V                                                        | T <sub>J</sub> = 85°C  |     | 2.9  | 4   | mA   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 3.5  | 6   | mA   |

|                    |                            | Sleep mode <sup>6</sup> , V <sub>CC33</sub> = 3.63 V                  | $T_J = 25^{\circ}C$    |     | 17   | 19  | μΑ   |

|                    |                            |                                                                       | T <sub>J</sub> = 85°C  |     | 18   | 20  | μΑ   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 24   | 25  | μA   |

| ICCI <sup>3</sup>  | I/O quiescent current      | Operational standby <sup>4</sup> ,                                    | $T_J = 25^{\circ}C$    |     | 417  | 648 | μΑ   |

|                    |                            | VCCIx = 3.63 V                                                        | T <sub>J</sub> = 85°C  |     | 417  | 648 | μΑ   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 417  | 649 | μΑ   |

| IJTAG              | JTAG I/O quiescent current | Operational standby <sup>4</sup> ,                                    | T <sub>J</sub> = 25°C  |     | 80   | 100 | μΑ   |

|                    |                            | VJTAG = 3.63 V                                                        | T <sub>J</sub> = 85°C  |     | 80   | 100 | μΑ   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 80   | 100 | μΑ   |

|                    |                            | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , VJTAG = 0 V |                        |     | 0    | 0   | μA   |

## Notes:

- 1. ICC is the 1.5 V power supplies, ICC and ICC15A.

- 2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

- 3. ICCI includes all ICCI0, ICCI1, ICCI2, and ICCI4.

- 4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

- 5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

- 6. Sleep Mode, VCC = VJTAG = VPUMP = 0 V.

Fusion Family of Mixed Signal FPGAs

|            | QN180           |                 |

|------------|-----------------|-----------------|

| Pin Number | AFS090 Function | AFS250 Function |

| В9         | XTAL2           | XTAL2           |

| B10        | GEA0/IO44NDB3V0 | GFA0/IO66NDB3V0 |

| B11        | GEB2/IO42PDB3V0 | IO60NDB3V0      |

| B12        | VCC             | VCC             |

| B13        | VCCNVM          | VCCNVM          |

| B14        | VCC15A          | VCC15A          |

| B15        | NCAP            | NCAP            |

| B16        | VCC33N          | VCC33N          |

| B17        | GNDAQ           | GNDAQ           |

| B18        | AC0             | AC0             |

| B19        | AT0             | AT0             |

| B20        | AT1             | AT1             |

| B21        | AV1             | AV1             |

| B22        | AC2             | AC2             |

| B23        | ATRTN1          | ATRTN1          |

| B24        | AG3             | AG3             |

| B25        | AV3             | AV3             |

| B26        | AG4             | AG4             |

| B27        | ATRTN2          | ATRTN2          |

| B28        | NC              | AC5             |

| B29        | VCC33A          | VCC33A          |

| B30        | VAREF           | VAREF           |

| B31        | PUB             | PUB             |

| B32        | PTEM            | PTEM            |

| B33        | GNDNVM          | GNDNVM          |

| B34        | VCC             | VCC             |

| B35        | TCK             | TCK             |

| B36        | TMS             | TMS             |

| B37        | TRST            | TRST            |

| B38        | GDB2/IO41PSB1V0 | GDA2/IO55PSB1V0 |

| B39        | GDC0/IO38NDB1V0 | GDB0/IO53NDB1V0 |

| B40        | VCCIB1          | VCCIB1          |

| B41        | GCA1/IO36PDB1V0 | GCA1/IO49PDB1V0 |

| B42        | GCC0/IO34NDB1V0 | GCC0/IO47NDB1V0 |

| B43        | GCB2/IO33PSB1V0 | GBC2/IO42PSB1V0 |

| B44        | VCC             | VCC             |

|            | QN180           |                 |

|------------|-----------------|-----------------|

| Pin Number | AFS090 Function | AFS250 Function |

| B45        | GBA2/IO31PDB1V0 | GBA2/IO40PDB1V0 |

| B46        | GNDQ            | GNDQ            |

| B47        | GBA1/IO30RSB0V0 | GBA0/IO38RSB0V0 |

| B48        | GBB1/IO28RSB0V0 | GBC1/IO35RSB0V0 |

| B49        | VCC             | VCC             |

| B50        | GBC0/IO25RSB0V0 | IO31RSB0V0      |

| B51        | IO23RSB0V0      | IO28RSB0V0      |

| B52        | IO20RSB0V0      | IO25RSB0V0      |

| B53        | VCC             | VCC             |

| B54        | IO11RSB0V0      | IO14RSB0V0      |

| B55        | IO08RSB0V0      | IO11RSB0V0      |

| B56        | GAC1/IO05RSB0V0 | IO08RSB0V0      |

| B57        | VCCIB0          | VCCIB0          |

| B58        | GAB0/IO02RSB0V0 | GAC0/IO04RSB0V0 |

| B59        | GAA0/IO00RSB0V0 | GAA1/IO01RSB0V0 |

| B60        | VCCPLA          | VCCPLA          |

| C1         | NC              | NC              |

| C2         | NC              | VCCIB3          |

| C3         | GND             | GND             |

| C4         | NC              | GFC2/IO69PPB3V0 |

| C5         | GFC1/IO49PDB3V0 | GFC1/IO68PDB3V0 |

| C6         | GFA0/IO47NPB3V0 | GFB0/IO67NPB3V0 |

| C7         | VCCIB3          | NC              |

| C8         | GND             | GND             |

| C9         | GEA1/IO44PDB3V0 | GFA1/IO66PDB3V0 |

| C10        | GEA2/IO42NDB3V0 | GEC2/IO60PDB3V0 |

| C11        | NC              | GEA2/IO58PSB3V0 |

| C12        | NC              | NC              |

| C13        | GND             | GND             |

| C14        | NC              | NC              |

| C15        | NC              | NC              |

| C16        | GNDA            | GNDA            |

| C17        | NC              | NC              |

| C18        | NC              | NC              |

| C19        | NC              | NC              |

| C20        | NC              | NC              |

| FG484         |                 |                  |  |  |  |  |

|---------------|-----------------|------------------|--|--|--|--|

| Pin<br>Number | AFS600 Function | AFS1500 Function |  |  |  |  |

| V3            | VCCIB4          | VCCIB4           |  |  |  |  |

| V4            | GEA1/IO61PDB4V0 | GEA1/IO88PDB4V0  |  |  |  |  |

| V5            | GEA0/IO61NDB4V0 | GEA0/IO88NDB4V0  |  |  |  |  |

| V6            | GND             | GND              |  |  |  |  |

| V7            | VCC33PMP        | VCC33PMP         |  |  |  |  |

| V8            | NC              | NC               |  |  |  |  |

| V9            | VCC33A          | VCC33A           |  |  |  |  |

| V10           | AG4             | AG4              |  |  |  |  |

| V11           | AT4             | AT4              |  |  |  |  |

| V12           | ATRTN2          | ATRTN2           |  |  |  |  |

| V13           | AT5             | AT5              |  |  |  |  |

| V14           | VCC33A          | VCC33A           |  |  |  |  |

| V15           | NC              | NC               |  |  |  |  |

| V16           | VCC33A          | VCC33A           |  |  |  |  |

| V17           | GND             | GND              |  |  |  |  |

| V18           | TMS             | TMS              |  |  |  |  |

| V19           | VJTAG           | VJTAG            |  |  |  |  |

| V20           | VCCIB2          | VCCIB2           |  |  |  |  |

| V21           | TRST            | TRST             |  |  |  |  |

| V22           | TDO             | TDO              |  |  |  |  |

| W1            | NC              | IO93PDB4V0       |  |  |  |  |

| W2            | GND             | GND              |  |  |  |  |

| W3            | NC              | IO93NDB4V0       |  |  |  |  |

| W4            | GEB2/IO59PDB4V0 | GEB2/IO86PDB4V0  |  |  |  |  |

| W5            | IO59NDB4V0      | IO86NDB4V0       |  |  |  |  |

| W6            | AV0             | AV0              |  |  |  |  |

| W7            | GNDA            | GNDA             |  |  |  |  |

| W8            | AV1             | AV1              |  |  |  |  |

| W9            | AV2             | AV2              |  |  |  |  |

| W10           | GNDA            | GNDA             |  |  |  |  |

| W11           | AV3             | AV3              |  |  |  |  |

| W12           | AV6             | AV6              |  |  |  |  |

| W13           | GNDA            | GNDA             |  |  |  |  |

| W14           | AV7             | AV7              |  |  |  |  |

| W15           | AV8             | AV8              |  |  |  |  |

| FG484         |                 |                  |  |  |  |  |

|---------------|-----------------|------------------|--|--|--|--|

| Pin<br>Number | AFS600 Function | AFS1500 Function |  |  |  |  |

| W16           | GNDA            | GNDA             |  |  |  |  |

| W17           | AV9             | AV9              |  |  |  |  |

| W18           | VCCIB2          | VCCIB2           |  |  |  |  |

| W19           | NC              | IO68PPB2V0       |  |  |  |  |

| W20           | TCK             | TCK              |  |  |  |  |

| W21           | GND             | GND              |  |  |  |  |

| W22           | NC              | IO76PPB2V0       |  |  |  |  |

| Y1            | GEC2/IO60PDB4V0 | GEC2/IO87PDB4V0  |  |  |  |  |

| Y2            | IO60NDB4V0      | IO87NDB4V0       |  |  |  |  |

| Y3            | GEA2/IO58PDB4V0 | GEA2/IO85PDB4V0  |  |  |  |  |

| Y4            | IO58NDB4V0      | IO85NDB4V0       |  |  |  |  |

| Y5            | NCAP            | NCAP             |  |  |  |  |

| Y6            | AC0             | AC0              |  |  |  |  |

| Y7            | VCC33A          | VCC33A           |  |  |  |  |

| Y8            | AC1             | AC1              |  |  |  |  |

| Y9            | AC2             | AC2              |  |  |  |  |

| Y10           | VCC33A          | VCC33A           |  |  |  |  |

| Y11           | AC3             | AC3              |  |  |  |  |

| Y12           | AC6             | AC6              |  |  |  |  |

| Y13           | VCC33A          | VCC33A           |  |  |  |  |

| Y14           | AC7             | AC7              |  |  |  |  |

| Y15           | AC8             | AC8              |  |  |  |  |

| Y16           | VCC33A          | VCC33A           |  |  |  |  |

| Y17           | AC9             | AC9              |  |  |  |  |

| Y18           | ADCGNDREF       | ADCGNDREF        |  |  |  |  |

| Y19           | PTBASE          | PTBASE           |  |  |  |  |

| Y20           | GNDNVM          | GNDNVM           |  |  |  |  |

| Y21           | VCCNVM          | VCCNVM           |  |  |  |  |

| Y22           | VPUMP           | VPUMP            |  |  |  |  |

4-26 Revision 6

Fusion Family of Mixed Signal FPGAs

| FG676      |                  |  |  |  |  |

|------------|------------------|--|--|--|--|

| Pin Number | AFS1500 Function |  |  |  |  |

| R21        | IO72NDB2V0       |  |  |  |  |

| R22        | IO72PDB2V0       |  |  |  |  |

| R23        | GND              |  |  |  |  |

| R24        | IO71PDB2V0       |  |  |  |  |

| R25        | VCCIB2           |  |  |  |  |

| R26        | IO67NDB2V0       |  |  |  |  |

| T1         | GND              |  |  |  |  |

| T2         | NC               |  |  |  |  |

| Т3         | GFA1/IO105PDB4V0 |  |  |  |  |

| T4         | GFA0/IO105NDB4V0 |  |  |  |  |

| T5         | IO101NDB4V0      |  |  |  |  |

| T6         | IO96PDB4V0       |  |  |  |  |

| T7         | IO96NDB4V0       |  |  |  |  |

| Т8         | IO99NDB4V0       |  |  |  |  |

| Т9         | IO97NDB4V0       |  |  |  |  |

| T10        | VCCIB4           |  |  |  |  |

| T11        | VCC              |  |  |  |  |

| T12        | GND              |  |  |  |  |

| T13        | VCC              |  |  |  |  |

| T14        | GND              |  |  |  |  |

| T15        | VCC              |  |  |  |  |

| T16        | GND              |  |  |  |  |

| T17        | VCCIB2           |  |  |  |  |

| T18        | IO83NDB2V0       |  |  |  |  |

| T19        | IO78NDB2V0       |  |  |  |  |

| T20        | GDA1/IO81PDB2V0  |  |  |  |  |

| T21        | GDB1/IO80PDB2V0  |  |  |  |  |

| T22        | IO73NDB2V0       |  |  |  |  |

| T23        | IO73PDB2V0       |  |  |  |  |

| T24        | IO71NDB2V0       |  |  |  |  |

| T25        | NC               |  |  |  |  |

| T26        | GND              |  |  |  |  |

| U1         | NC               |  |  |  |  |

| U2         | NC               |  |  |  |  |

| U3         | IO102PDB4V0      |  |  |  |  |

| U4         | IO102NDB4V0      |  |  |  |  |

|            | FG676            |

|------------|------------------|

| Pin Number | AFS1500 Function |

| U5         | VCCIB4           |

| U6         | IO91PDB4V0       |

| U7         | IO91NDB4V0       |

| U8         | IO92PDB4V0       |

| U9         | GND              |

| U10        | GND              |

| U11        | VCC33A           |

| U12        | GNDA             |

| U13        | VCC33A           |

| U14        | GNDA             |

| U15        | VCC33A           |

| U16        | GNDA             |

| U17        | VCC              |

| U18        | GND              |

| U19        | IO74NDB2V0       |

| U20        | GDA0/IO81NDB2V0  |

| U21        | GDB0/IO80NDB2V0  |

| U22        | VCCIB2           |

| U23        | IO75NDB2V0       |

| U24        | IO75PDB2V0       |

| U25        | NC               |

| U26        | NC               |

| V1         | NC               |

| V2         | VCCIB4           |

| V3         | IO100PPB4V0      |

| V4         | GND              |

| V5         | IO95PDB4V0       |

| V6         | IO95NDB4V0       |

| V7         | VCCIB4           |

| V8         | IO92NDB4V0       |

| V9         | GNDNVM           |

| V10        | GNDA             |

| V11        | NC               |

| V12        | AV4              |

| V13        | NC               |

| V14        | AV5              |

| FG676      |                  |

|------------|------------------|

| Pin Number | AFS1500 Function |

| V15        | AC5              |

| V16        | NC               |

| V17        | GNDA             |

| V18        | IO77PPB2V0       |

| V19        | IO74PDB2V0       |

| V20        | VCCIB2           |

| V21        | IO82NDB2V0       |

| V22        | GDA2/IO82PDB2V0  |

| V23        | GND              |

| V24        | GDC1/IO79PDB2V0  |

| V25        | VCCIB2           |

| V26        | NC               |

| W1         | GND              |

| W2         | IO94PPB4V0       |

| W3         | IO98PDB4V0       |

| W4         | IO98NDB4V0       |

| W5         | GEC1/IO90PDB4V0  |

| W6         | GEC0/IO90NDB4V0  |

| W7         | GND              |

| W8         | VCCNVM           |

| W9         | VCCIB4           |

| W10        | VCC15A           |

| W11        | GNDA             |

| W12        | AC4              |

| W13        | VCC33A           |

| W14        | GNDA             |

| W15        | AG5              |

| W16        | GNDA             |

| W17        | PUB              |

| W18        | VCCIB2           |

| W19        | TDI              |