Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                   |

|--------------------------------|--------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | ·                                                                        |

| Total RAM Bits                 | 276480                                                                   |

| Number of I/O                  | 223                                                                      |

| Number of Gates                | 1500000                                                                  |

| Voltage - Supply               | 1.425V ~ 1.575V                                                          |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                          |

| Package / Case                 | 484-BGA                                                                  |

| Supplier Device Package        | 484-FPBGA (23x23)                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/afs1500-fgg484 |

|                                |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Modes of Operation**

# Standby Mode

Standby mode allows periodic power-up and power-down of the FPGA fabric. In standby mode, the real-time counter and crystal block are ON. The FPGA is not powered by disabling the 1.5 V voltage regulator. The 1.5 V voltage regulator can be enabled when the preset count is matched. Refer to the "Real-Time Counter (part of AB macro)" section for details. To enter standby mode, the RTC must be first configured and enabled. Then VRPSM is shut off by deasserting the VRPU signal. The 1.5 V voltage regulator is then disabled, and shuts off the 1.5 V output.

# Sleep Mode

In sleep mode, the real-time counter and crystal blocks are OFF. The 1.5 V voltage regulator inside the VRPSM can only be enabled by the PUB or TRST pin. Refer to the "Voltage Regulator and Power System Monitor (VRPSM)" section on page 2-36 for details on power-up and power-down of the 1.5 V voltage regulator.

# Standby and Sleep Mode Circuit Implementation

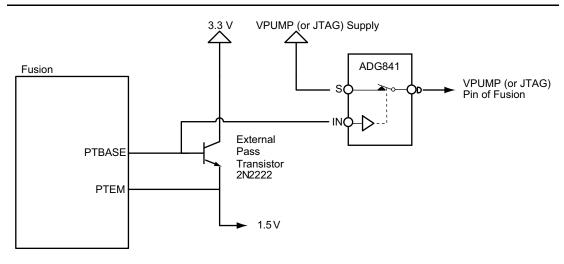

For extra power savings, VJTAG and VPUMP should be at the same voltage as VCC, floated or ground, during standby and sleep modes. Note that when VJTAG is not powered, the 1.5 V voltage regulator cannot be enabled through TRST.

VPUMP and VJTAG can be controlled through an external switch. Microsemi recommends ADG839, ADG849, or ADG841 as possible switches. Figure 2-28 shows the implementation for controlling VPUMP. The IN signal of the switch can be connected to PTBASE of the Fusion device. VJTAG can be controlled in same manner.

Figure 2-28 • Implementation to Control VPUMP

## **Unprotect Page Operation**

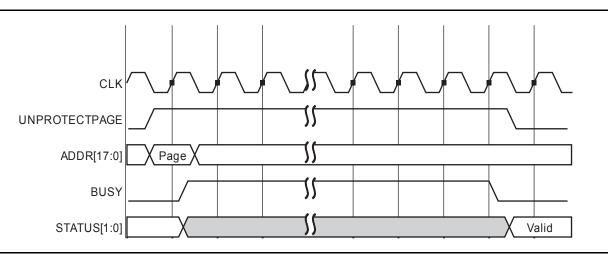

An Unprotect Page operation will clear the protection for a page addressed on the ADDR input. It is initiated by setting the UNPROTECTPAGE signal on the interface along with the page address on ADDR.

If the page is not in the Page Buffer, the Unprotect Page operation will copy the page into the Page Buffer. The Copy Page operation occurs only if the current page in the Page Buffer is not Page Loss Protected.

The waveform for an Unprotect Page operation is shown in Figure 2-42.

# Figure 2-42 • FB Unprotected Page Waveform

The Unprotect Page operation can incur the following error conditions:

- 1. If the copy of the page to the Page Buffer determines that the page has a single-bit correctable error in the data, it will report a STATUS = '01'.

- 2. If the address on ADDR does not match the address of the Page Buffer, PAGELOSSPROTECT is asserted, and the Page Buffer has been modified, then STATUS = '11' and the addressed page is not loaded into the Page Buffer.

- 3. If the copy of the page to the Page Buffer determines that at least one block in the page has a double-bit uncorrectable error, STATUS = '10' and the Page Buffer will contain the corrupted data.

#### **Discard Page Operation**

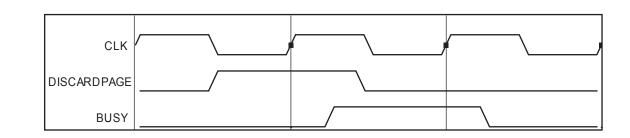

If the contents of the modified Page Buffer have to be discarded, the DISCARDPAGE signal should be asserted. This command results in the Page Buffer being marked as unmodified.

The timing for the operation is shown in Figure 2-43. The BUSY signal will remain asserted until the operation has completed.

Figure 2-43 • FB Discard Page Waveform

# **Current Monitor**

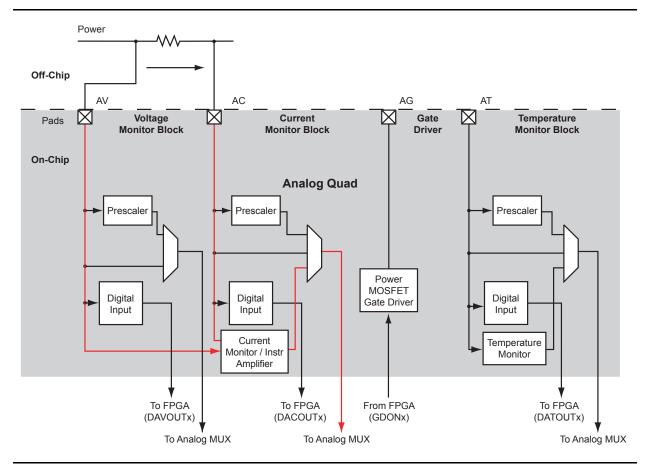

The Fusion Analog Quad is an excellent element for voltage- and current-monitoring applications. In addition to supporting the same functionality offered by the AV pad, the AC pad can be configured to monitor current across an external sense resistor (Figure 2-70). To support this current monitor function, a differential amplifier with 10x gain passes the amplified voltage drop between the AV and AC pads to the ADC. The amplifier enables the user to use very small resistor values, thereby limiting any impact on the circuit. This function of the AC pad does not limit AV pad operation. The AV pad can still be configured for use as a direct voltage input or scaled through the AV prescaler independently of it's use as an input to the AC pad's differential amplifier.

Figure 2-70 • Analog Quad Current Monitor Configuration

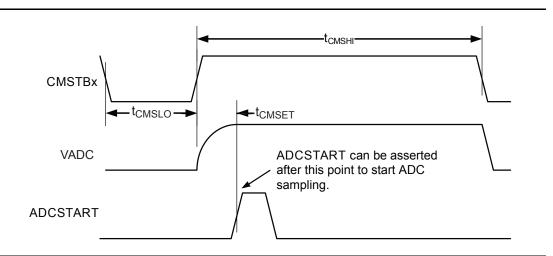

To initiate a current measurement, the appropriate Current Monitor Strobe (CMSTB) signal on the AB macro must be asserted low for at least  $t_{CMSLO}$  in order to discharge the previous measurement. Then CMSTB must be asserted high for at least  $t_{CMSET}$  prior to asserting the ADCSTART signal. The CMSTB must remain high until after the SAMPLE signal is de-asserted by the AB macro. Note that the minimum sample time cannot be less than  $t_{CMSHI}$ . Figure 2-71 shows the timing diagram of CMSTB in relationship with the ADC control signals.

Figure 2-71 • Timing Diagram for Current Monitor Strobe

Figure 2-72 illustrates positive current monitor operation. The differential voltage between AV and AC goes into the 10× amplifier and is then converted by the ADC. For example, a current of 1.5 A is drawn from a 10 V supply and is measured by the voltage drop across a 0.050  $\Omega$  sense resistor, The voltage drop is amplified by ten times by the amplifier and then measured by the ADC. The 1.5 A current creates a differential voltage across the sense resistor of 75 mV. This becomes 750 mV after amplification. Thus, the ADC measures a current of 1.5 A as 750 mV. Using an ADC with 8-bit resolution and VAREF of 2.56 V, the ADC result is decimal 75. EQ 3 shows how to compute the current from the ADC result.

$$||| = (ADC \times V_{AREF}) / (10 \times 2^{N} \times R_{sense})$$

EQ 3

where

I is the current flowing through the sense resistor

ADC is the result from the ADC

VAREF is the Reference voltage

N is the number of bits

Rsense is the resistance of the sense resistor

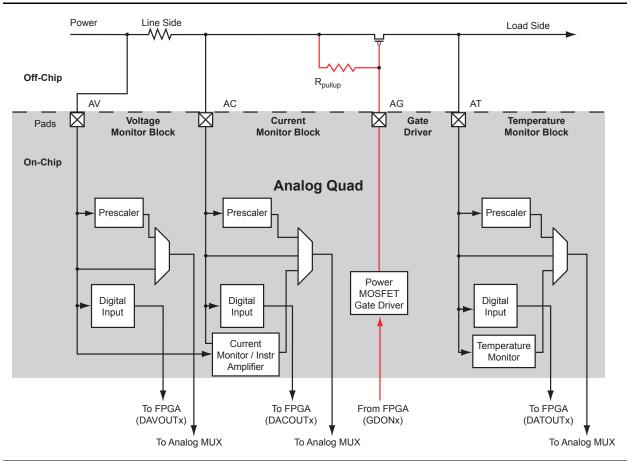

# Gate Driver

The Fusion Analog Quad includes a Gate Driver connected to the Quad's AG pin (Figure 2-74). Designed to work with external p- or n-channel MOSFETs, the Gate driver is a configurable current sink or source and requires an external pull-up or pull-down resistor. The AG supports 4 selectable gate drive levels: 1  $\mu$ A, 3  $\mu$ A, 10  $\mu$ A, and 30  $\mu$ A (Figure 2-75 on page 2-91). The AG also supports a High Current Drive mode in which it can sink 20 mA; in this mode the switching rate is approximately 1.3 MHz with 100 ns turn-on time and 600 ns turn-off time. Modeled on an open-drain-style output, it does not output a voltage level without an appropriate pull-up or pull-down resistor. If 1 V is forced on the drain, the current sinking/sourcing will exceed the ability of the transistor, and the device could be damaged.

The AG pad is turned on via the corresponding GDONx pin in the Analog Block macro, where x is the number of the corresponding Analog Quad for the AG pad to be enabled (GDON0 to GDON9).

The gate-to-source voltage ( $V_{gs}$ ) of the external MOSFET is limited to the programmable drive current times the external pull-up or pull-down resistor value (EQ 5).

$$V_{gs} \le I_g \times (R_{pullup} \text{ or } R_{pulldown})$$

EQ 5

Device Architecture

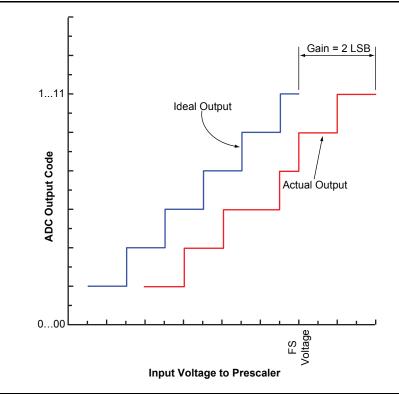

# Gain Error

The gain error of an ADC indicates how well the slope of an actual transfer function matches the slope of the ideal transfer function. Gain error is usually expressed in LSB or as a percent of full-scale (%FSR). Gain error is the full-scale error minus the offset error (Figure 2-84).

Figure 2-84 • Gain Error

# Gain Error Drift

Gain-error drift is the variation in gain error due to a change in ambient temperature, typically expressed in ppm/°C.

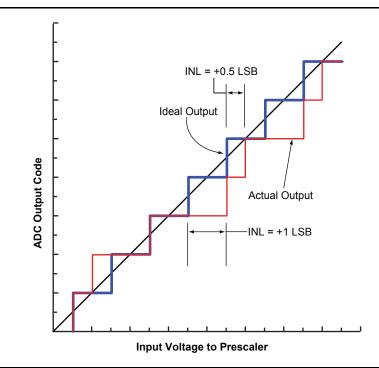

# INL – Integral Non-Linearity

INL is the deviation of an actual transfer function from a straight line. After nullifying offset and gain errors, the straight line is either a best-fit straight line or a line drawn between the end points of the transfer function (Figure 2-85).

Figure 2-85 • Integral Non-Linearity (INL)

# LSB – Least Significant Bit

In a binary number, the LSB is the least weighted bit in the group. Typically, the LSB is the furthest right bit. For an ADC, the weight of an LSB equals the full-scale voltage range of the converter divided by  $2^N$ , where N is the converter's resolution.

EQ 13 shows the calculation for a 10-bit ADC with a unipolar full-scale voltage of 2.56 V:

EQ 13

#### **No Missing Codes**

An ADC has no missing codes if it produces all possible digital codes in response to a ramp signal applied to the analog input.

| Analog MUX Channel | Signal                       | Analog Quad Number |

|--------------------|------------------------------|--------------------|

| 16                 | AV5                          |                    |

| 17                 | AC5                          | Analog Quad 5      |

| 18                 | AT5                          |                    |

| 19                 | AV6                          |                    |

| 20                 | AC6                          | Analog Quad 6      |

| 21                 | AT6                          |                    |

| 22                 | AV7                          |                    |

| 23                 | AC7                          | Analog Quad 7      |

| 24                 | AT7                          |                    |

| 25                 | AV8                          |                    |

| 26                 | AC8                          | Analog Quad 8      |

| 27                 | AT8                          |                    |

| 28                 | AV9                          |                    |

| 29                 | AC9                          | Analog Quad 9      |

| 30                 | AT9                          |                    |

| 31                 | Internal temperature monitor |                    |

#### Table 2-40 • Analog MUX Channels (continued)

The ADC can be powered down independently of the FPGA core, as an additional control or for powersaving considerations, via the PWRDWN pin of the Analog Block. The PWRDWN pin controls only the comparators in the ADC.

#### **ADC Modes**

The Fusion ADC can be configured to operate in 8-, 10-, or 12-bit modes, power-down after conversion, and dynamic calibration. This is controlled by MODE[3:0], as defined in Table 2-41 on page 2-106.

The output of the ADC is the RESULT[11:0] signal. In 8-bit mode, the Most Significant 8 Bits RESULT[11:4] are used as the ADC value and the Least Significant 4 Bits RESULT[3:0] are logical '0's. In 10-bit mode, RESULT[11:2] are used the ADC value and RESULT[1:0] are logical 0s.

| Name | Bits | Function                                                                                          |

|------|------|---------------------------------------------------------------------------------------------------|

| MODE | 3    | 0 – Internal calibration after every conversion; two ADCCLK cycles are used after the conversion. |

|      |      | 1 – No calibration after every conversion                                                         |

| MODE | 2    | 0 – Power-down after conversion                                                                   |

|      |      | 1 – No Power-down after conversion                                                                |

| MODE | 1:0  | 00 – 10-bit                                                                                       |

|      |      | 01 – 12-bit                                                                                       |

|      |      | 10 – 8-bit                                                                                        |

|      |      | 11 – Unused                                                                                       |

# **Timing Characteristics**

# Table 2-55 • Analog Configuration Multiplexer (ACM) TimingCommercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter               | Description                                        | -2    | -1    | Std.  | Units |

|-------------------------|----------------------------------------------------|-------|-------|-------|-------|

| t <sub>CLKQACM</sub>    | Clock-to-Q of the ACM                              | 19.73 | 22.48 | 26.42 | ns    |

| t <sub>SUDACM</sub>     | Data Setup time for the ACM                        | 4.39  | 5.00  | 5.88  | ns    |

| t <sub>HDACM</sub>      | Data Hold time for the ACM                         | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUAACM</sub>     | Address Setup time for the ACM                     | 4.73  | 5.38  | 6.33  | ns    |

| t <sub>HAACM</sub>      | Address Hold time for the ACM                      | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUEACM</sub>     | Enable Setup time for the ACM                      | 3.93  | 4.48  | 5.27  | ns    |

| t <sub>HEACM</sub>      | Enable Hold time for the ACM                       | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>MPWARACM</sub>   | Asynchronous Reset Minimum Pulse Width for the ACM | 10.00 | 10.00 | 10.00 | ns    |

| t <sub>REMARACM</sub>   | Asynchronous Reset Removal time for the ACM        | 12.98 | 14.79 | 17.38 | ns    |

| t <sub>RECARACM</sub>   | Asynchronous Reset Recovery time for the ACM       | 12.98 | 14.79 | 17.38 | ns    |

| t <sub>MPWCLKACM</sub>  | Clock Minimum Pulse Width for the ACM              | 45.00 | 45.00 | 45.00 | ns    |

| t <sub>FMAXCLKACM</sub> | lock Maximum Frequency for the ACM                 | 10.00 | 10.00 | 10.00 | MHz   |

Device Architecture

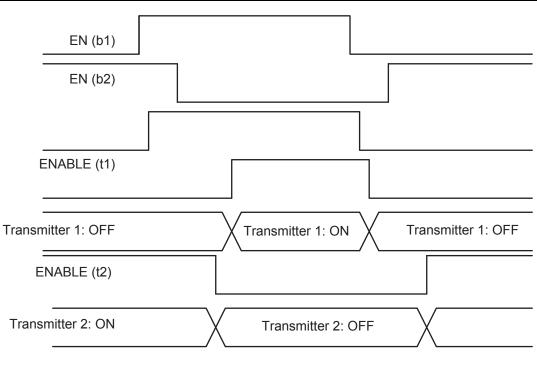

**Result: No Bus Contention**

*Figure 2-112* • Timing Diagram (with skew circuit selected)

# Weak Pull-Up and Weak Pull-Down Resistors

Fusion devices support optional weak pull-up and pull-down resistors for each I/O pin. When the I/O is pulled up, it is connected to the VCCI of its corresponding I/O bank. When it is pulled down, it is connected to GND. Refer to Table 2-97 on page 2-171 for more information.

# Slew Rate Control and Drive Strength

Fusion devices support output slew rate control: high and low. The high slew rate option is recommended to minimize the propagation delay. This high-speed option may introduce noise into the system if appropriate signal integrity measures are not adopted. Selecting a low slew rate reduces this kind of noise but adds some delays in the system. Low slew rate is recommended when bus transients are expected. Drive strength should also be selected according to the design requirements and noise immunity of the system.

The output slew rate and multiple drive strength controls are available in LVTTL/LVCMOS 3.3 V, LVCMOS 2.5 V, LVCMOS 2.5 V, 5.0 V input, LVCMOS 1.8 V, and LVCMOS 1.5 V. All other I/O standards have a high output slew rate by default.

For Fusion slew rate and drive strength specifications, refer to the appropriate I/O bank table:

- Fusion Standard I/O (Table 2-78 on page 2-152)

- Fusion Advanced I/O (Table 2-79 on page 2-152)

- Fusion Pro I/O (Table 2-80 on page 2-152)

Table 2-83 on page 2-155 lists the default values for the above selectable I/O attributes as well as those that are preset for each I/O standard.

Refer to Table 2-78, Table 2-79, and Table 2-80 on page 2-152 for SLEW and OUT\_DRIVE settings. Table 2-81 on page 2-153 and Table 2-82 on page 2-154 list the I/O default attributes. Table 2-83 on page 2-155 lists the voltages for the supported I/O standards.

# Table 2-93 • Summary of I/O Timing Characteristics – Software Default SettingsCommercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,Worst-Case VCCI = I/O Standard DependentApplicable to Advanced I/Os

|                              |                     |           |                      |                         |        | r    |      |      | 1     |      |      |      |      | r    |      |       |

|------------------------------|---------------------|-----------|----------------------|-------------------------|--------|------|------|------|-------|------|------|------|------|------|------|-------|

| I/O Standard                 | Drive Strength (mA) | Slew Rate | Capacitive Load (pF) | External Resistor (Ohm) | t роит | top  | toin | tev  | teour | tzı  | tzH  | tız  | ZHţ  | tzLS | tzHS | Units |

| 3.3 V LVTTL/<br>3.3 V LVCMOS | 12 mA               | High      | 35 pF                | -                       | 0.49   | 2.64 | 0.03 | 0.90 | 0.32  | 2.69 | 2.11 | 2.40 | 2.68 | 4.36 | 3.78 | ns    |

| 2.5 V LVCMOS                 | 12 mA               | High      | 35 pF                | _                       | 0.49   | 2.66 | 0.03 | 0.98 | 0.32  | 2.71 | 2.56 | 2.47 | 2.57 | 4.38 | 4.23 | ns    |

| 1.8 V LVCMOS                 | 12 mA               | High      | 35 pF                | -                       | 0.49   | 2.64 | 0.03 | 0.91 | 0.32  | 2.69 | 2.27 | 2.76 | 3.05 | 4.36 | 3.94 | ns    |

| 1.5 V LVCMOS                 | 12 mA               | High      | 35 pF                | -                       | 0.49   | 3.05 | 0.03 | 1.07 | 0.32  | 3.10 | 2.67 | 2.95 | 3.14 | 4.77 | 4.34 | ns    |

| 3.3 V PCI                    | Per PCI<br>spec     | High      | 10 pF                | 25 <sup>2</sup>         | 0.49   | 2.00 | 0.03 | 0.65 | 0.32  | 2.04 | 1.46 | 2.40 | 2.68 | 3.71 | 3.13 | ns    |

| 3.3 V PCI-X                  | Per PCI-X<br>spec   | High      | 10 pF                | 25 <sup>2</sup>         | 0.49   | 2.00 | 0.03 | 0.62 | 0.32  | 2.04 | 1.46 | 2.40 | 2.68 | 3.71 | 3.13 | ns    |

| LVDS                         | 24 mA               | High      | -                    | -                       | 0.49   | 1.37 | 0.03 | 1.20 | N/A   | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | ns    |

| LVPECL                       | 24 mA               | High      | -                    | -                       | 0.49   | 1.34 | 0.03 | 1.05 | N/A   | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | ns    |

Notes:

1. For specific junction temperature and voltage-supply levels, refer to Table 3-6 on page 3-7 for derating values.

2. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-123 on page 2-197 for connectivity. This resistor is not required during normal operation.

# Table 2-94 • Summary of I/O Timing Characteristics – Software Default SettingsCommercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V,Worst-Case VCCI = I/O Standard DependentApplicable to Standard I/Os

| I/O Standard                 | Drive Strength (mA) | Slew Rate | Capacitive Load (pF) | External Resistor (Ohm) | t pour | top  | t <sub>DIN</sub> | t <sub>Þ</sub> v | teour | t <sub>zı</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|------------------------------|---------------------|-----------|----------------------|-------------------------|--------|------|------------------|------------------|-------|-----------------|-----------------|-----------------|-----------------|-------|

| 3.3 V LVTTL/<br>3.3 V LVCMOS | 8 mA                | High      | 35 pF                | -                       | 0.49   | 3.29 | 0.03             | 0.75             | 0.32  | 3.36            | 2.80            | 1.79            | 2.01            | ns    |

| 2.5 V LVCMOS                 | 8 mA                | High      | 35pF                 | -                       | 0.49   | 3.56 | 0.03             | 0.96             | 0.32  | 3.40            | 3.56            | 1.78            | 1.91            | ns    |

| 1.8 V LVCMOS                 | 4 mA                | High      | 35pF                 | Ι                       | 0.49   | 4.74 | 0.03             | 0.90             | 0.32  | 4.02            | 4.74            | 1.80            | 1.85            | ns    |

| 1.5 V LVCMOS                 | 2 mA                | High      | 35pF                 | Ι                       | 0.49   | 5.71 | 0.03             | 1.06             | 0.32  | 4.71            | 5.71            | 1.83            | 1.83            | ns    |

Note: For specific junction temperature and voltage-supply levels, refer to Table 3-6 on page 3-7 for derating values.

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|------------------------|

| 0             | 3.3            | 1.4                  | -               | 35                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

# Table 2-104 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Pro I/Os

|                   | 1              |                   | 1               |                  | 1               |                  | r                 |                 | r               |                 |                 |                  |                  | 1     |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

| 4 mA              | Std.           | 0.66              | 11.01           | 0.04             | 1.20            | 1.57             | 0.43              | 11.21           | 9.05            | 2.69            | 2.44            | 13.45            | 11.29            | ns    |

|                   | -1             | 0.56              | 9.36            | 0.04             | 1.02            | 1.33             | 0.36              | 9.54            | 7.70            | 2.29            | 2.08            | 11.44            | 9.60             | ns    |

|                   | -2             | 0.49              | 8.22            | 0.03             | 0.90            | 1.17             | 0.32              | 8.37            | 6.76            | 2.01            | 1.82            | 10.04            | 8.43             | ns    |

| 8 mA              | Std.           | 0.66              | 7.86            | 0.04             | 1.20            | 1.57             | 0.43              | 8.01            | 6.44            | 3.04            | 3.06            | 10.24            | 8.68             | ns    |

|                   | -1             | 0.56              | 6.69            | 0.04             | 1.02            | 1.33             | 0.36              | 6.81            | 5.48            | 2.58            | 2.61            | 8.71             | 7.38             | ns    |

|                   | -2             | 0.49              | 5.87            | 0.03             | 0.90            | 1.17             | 0.32              | 5.98            | 4.81            | 2.27            | 2.29            | 7.65             | 6.48             | ns    |

| 12 mA             | Std.           | 0.66              | 6.03            | 0.04             | 1.20            | 1.57             | 0.43              | 6.14            | 5.02            | 3.28            | 3.47            | 8.37             | 7.26             | ns    |

|                   | -1             | 0.56              | 5.13            | 0.04             | 1.02            | 1.33             | 0.36              | 5.22            | 4.27            | 2.79            | 2.95            | 7.12             | 6.17             | ns    |

|                   | -2             | 0.49              | 4.50            | 0.03             | 0.90            | 1.17             | 0.32              | 4.58            | 3.75            | 2.45            | 2.59            | 6.25             | 5.42             | ns    |

| 16 mA             | Std.           | 0.66              | 5.62            | 0.04             | 1.20            | 1.57             | 0.43              | 5.72            | 4.72            | 3.32            | 3.58            | 7.96             | 6.96             | ns    |

|                   | -1             | 0.56              | 4.78            | 0.04             | 1.02            | 1.33             | 0.36              | 4.87            | 4.02            | 2.83            | 3.04            | 6.77             | 5.92             | ns    |

|                   | -2             | 0.49              | 4.20            | 0.03             | 0.90            | 1.17             | 0.32              | 4.27            | 3.53            | 2.48            | 2.67            | 5.94             | 5.20             | ns    |

| 24 mA             | Std.           | 0.66              | 5.24            | 0.04             | 1.20            | 1.57             | 0.43              | 5.34            | 4.69            | 3.39            | 3.96            | 7.58             | 6.93             | ns    |

|                   | -1             | 0.56              | 4.46            | 0.04             | 1.02            | 1.33             | 0.36              | 4.54            | 3.99            | 2.88            | 3.37            | 6.44             | 5.89             | ns    |

|                   | -2             | 0.49              | 3.92            | 0.03             | 0.90            | 1.17             | 0.32              | 3.99            | 3.50            | 2.53            | 2.96            | 5.66             | 5.17             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

Device Architecture

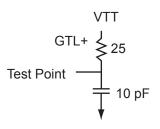

# 3.3 V GTL+

Gunning Transceiver Logic Plus is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 3.3 V.

Table 2-144 • Minimum and Maximum DC Input and Output Levels

| 3.3 V GTL+        |           | VIL        | VIH        |           | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL¹            | IIH <sup>2</sup> |

|-------------------|-----------|------------|------------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-----------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 35 mA             | -0.3      | VREF – 0.1 | VREF + 0.1 | 3.6       | 0.6       | _         | 35  | 35 | 181                     | 268                     | 10              | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

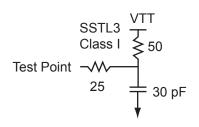

#### Figure 2-126 • AC Loading

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.1    | VREF + 0.1     | 1.0                  | 1.0             | 1.5            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

Table 2-146 • 3.3 V GTL+

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V, VREF = 1.0 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.06            | 0.04             | 1.59            | 0.43              | 2.09            | 2.06            |                 |                 | 4.33             | 4.29             | ns    |

| -1             | 0.56              | 1.75            | 0.04             | 1.35            | 0.36              | 1.78            | 1.75            |                 |                 | 3.68             | 3.65             | ns    |

| -2             | 0.49              | 1.53            | 0.03             | 1.19            | 0.32              | 1.56            | 1.53            |                 |                 | 3.23             | 3.20             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

Device Architecture

# SSTL3 Class I

Stub-Speed Terminated Logic for 3.3 V memory bus standard (JESD8-8). Fusion devices support Class I. This provides a differential amplifier input buffer and a push-pull output buffer.

Table 2-162 • Minimum and Maximum DC Input and Output Levels

| SSTL3 Class I     | STL3 Class I VIL |            | VIH        | VIH       |           | VOH        | IOL | IOH | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|------------------|------------|------------|-----------|-----------|------------|-----|-----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength | Min.<br>V        | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V  | mA  | mA  | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 14 mA             | -0.3             | VREF – 0.2 | VREF + 0.2 | 3.6       | 0.7       | VCCI – 1.1 | 14  | 14  | 54                      | 51                      | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

#### Figure 2-132 • AC Loading

#### Table 2-163 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.2    | VREF + 0.2     | 1.5                  | 1.5             | 1.485          | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

Table 2-164 • SSTL3 Class I

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V, VREF = 1.5 V

| Speed<br>Grade | t <sub>dout</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.31            | 0.04             | 1.25            | 0.43              | 2.35            | 1.84            |                 |                 | 4.59             | 4.07             | ns    |

| -1             | 0.56              | 1.96            | 0.04             | 1.06            | 0.36              | 2.00            | 1.56            |                 |                 | 3.90             | 3.46             | ns    |

| -2             | 0.49              | 1.72            | 0.03             | 0.93            | 0.32              | 1.75            | 1.37            |                 |                 | 3.42             | 3.04             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

| Symbol              | Parameter <sup>2</sup>              | Commercial                    | Industrial                | Units          |    |

|---------------------|-------------------------------------|-------------------------------|---------------------------|----------------|----|

| TJ                  | Junction temperature                |                               | 0 to +85                  | -40 to +100    | °C |

| VCC                 | 1.5 V DC core supply voltage        |                               | 1.425 to 1.575            | 1.425 to 1.575 | V  |

| VJTAG               | JTAG DC voltage                     | G DC voltage                  |                           |                | V  |

| VPUMP               | Programming voltage                 | Programming mode <sup>3</sup> | 3.15 to 3.45              | 3.15 to 3.45   | V  |

|                     |                                     | Operation <sup>4</sup>        | 0 to 3.6                  | 0 to 3.6       | V  |

| VCCPLL              | Analog power supply (PLL)           |                               | 1.425 to 1.575            | 1.425 to 1.575 | V  |

| VCCI                | 1.5 V DC supply voltage             |                               | 1.425 to 1.575            | 1.425 to 1.575 | V  |

|                     | 1.8 V DC supply voltage             |                               | 1.7 to 1.9                | 1.7 to 1.9     | V  |

|                     | 2.5 V DC supply voltage             |                               | 2.3 to 2.7                | 2.3 to 2.7     | V  |

|                     | 3.3 V DC supply voltage             |                               | 3.0 to 3.6                | 3.0 to 3.6     | V  |

|                     | LVDS differential I/O               |                               | 2.375 to 2.625            | 2.375 to 2.625 | V  |

|                     | LVPECL differential I/O             |                               | 3.0 to 3.6                | 3.0 to 3.6     | V  |

| VCC33A              | +3.3 V power supply                 |                               | 2.97 to 3.63              | 2.97 to 3.63   | V  |

| VCC33PMP            | +3.3 V power supply                 | 2.97 to 3.63                  | 2.97 to 3.63              | V              |    |

| VAREF               | Voltage reference for ADC           | 2.527 to 2.593                | 2.527 to 2.593            | V              |    |

| VCC15A <sup>5</sup> | Digital power supply for the analog | 1.425 to 1.575                | 1.425 to 1.575            | V              |    |

| VCCNVM              | Embedded flash power supply         |                               | 1.425 to 1.575            | 1.425 to 1.575 | V  |

| VCCOSC              | Oscillator power supply             |                               | 2.97 to 3.63              | 2.97 to 3.63   | V  |

| AV, AC <sup>6</sup> | Unpowered, ADC reset asserted o     | r unconfigured                | -10.5 to 12.0             | -10.5 to 11.6  | V  |

|                     | Analog input (+16 V to +2 V presca  | aler range)                   | –0.3 to 12.0              | –0.3 to 11.6   | V  |

|                     | Analog input (+1 V to + 0.125 V pre | -0.3 to 3.6                   | -0.3 to 3.6               | V              |    |

|                     | Analog input (-16 V to -2 V presca  | -10.5 to 0.3                  | -10.5 to 0.3              | V              |    |

|                     | Analog input (-1 V to -0.125 V pre  | scaler range)                 | -3.6 to 0.3               | -3.6 to 0.3    | V  |

|                     | Analog input (direct input to ADC)  |                               | -0.3 to 3.6               | -0.3 to 3.6    | V  |

|                     | Digital input                       |                               | –0.3 to 12.0              | –0.3 to 11.6   | V  |

| AG <sup>6</sup>     | Unpowered, ADC reset asserted o     | r unconfigured                | -10.5 to 12.0             | -10.5 to 11.6  | V  |

|                     | Low Current Mode (1 µA, 3 µA, 10    | μΑ, 30 μΑ)                    | –0.3 to 12.0              | –0.3 to 11.6   | V  |

|                     | Low Current Mode (-1 µA, -3 µA,     | –10 μA, –30 μA)               | -10.5 to 0.3              | -10.5 to 0.3   | V  |

|                     | High Current Mode <sup>7</sup>      |                               | -10.5 to 12.0             | -10.5 to 11.6  | V  |

| AT <sup>6</sup>     | Unpowered, ADC reset asserted o     | r unconfigured                | -0.3 to 15.5 -0.3 to 14.5 |                | V  |

|                     | Analog input (+16 V, +4 V prescale  | er range)                     | –0.3 to 15.5 –0.3 to 14.5 |                | V  |

|                     | Analog input (direct input to ADC)  |                               | -0.3 to 3.6               | -0.3 to 3.6    | V  |

|                     | Digital input                       |                               | -0.3 to 15.5              | -0.3 to 14.5   | V  |

# Table 3-2 • Recommended Operating Conditions<sup>1</sup>

Notes:

1. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given in Table 2-85 on page 2-157.

- 2. All parameters representing voltages are measured with respect to GND unless otherwise specified.

- 3. The programming temperature range supported is  $T_{ambient} = 0^{\circ}C$  to 85°C.

- 4. VPUMP can be left floating during normal operation (not programming mode).

- 5. Violating the V<sub>CC15A</sub> recommended voltage supply during an embedded flash program cycle can corrupt the page being programmed.

- 6. The input voltage may overshoot by up to 500 mV above the Recommended Maximum (150 mV in Direct mode), provided the duration of the overshoot is less than 50% of the operating lifetime of the device.

- 7. The AG pad should also conform to the limits as specified in Table 2-48 on page 2-114.

DC and Power Characteristics

| Parameter | Description         | Conditions                                                            | Temp.                  | Min. | Тур. | Max. | Unit |

|-----------|---------------------|-----------------------------------------------------------------------|------------------------|------|------|------|------|

| IJTAG     | JTAG I/O quiescent  | Operational standby <sup>4</sup> ,                                    | T <sub>J</sub> = 25°C  |      | 80   | 100  | μA   |

|           | current             | VJTAG = 3.63 V                                                        | T <sub>J</sub> = 85°C  |      | 80   | 100  | μA   |

|           |                     |                                                                       | T <sub>J</sub> = 100°C |      | 80   | 100  | μA   |

|           |                     | Standby mode <sup>5</sup> or Sleep mode <sup>6</sup> ,<br>VJTAG = 0 V |                        |      | 0    | 0    | μA   |

| IPP       | Programming supply  | Non-programming mode,                                                 | T <sub>J</sub> = 25°C  |      | 39   | 80   | μA   |

|           | current             | VPUMP = 3.63 V                                                        | T <sub>J</sub> = 85°C  |      | 40   | 80   | μA   |

|           |                     |                                                                       | T <sub>J</sub> = 100°C |      | 40   | 80   | μA   |

|           |                     | Standby mode <sup>5</sup> or Sleep mode <sup>6</sup> ,<br>VPUMP = 0 V |                        |      | 0    | 0    | μA   |

| ICCNVM    | Embedded NVM        | Reset asserted, V <sub>CCNVM</sub> = 1.575 V                          | T <sub>J</sub> = 25°C  |      | 50   | 150  | μA   |

|           | current             |                                                                       | T <sub>J</sub> =85°C   |      | 50   | 150  | μA   |

|           |                     |                                                                       | T <sub>J</sub> = 100°C |      | 50   | 150  | μA   |

| ICCPLL    | 1.5 V PLL quiescent | Operational standby                                                   | T <sub>J</sub> = 25°C  |      | 130  | 200  | μA   |

|           | current             | , VCCPLL = 1.575 V                                                    | T <sub>J</sub> = 85°C  |      | 130  | 200  | μA   |

|           |                     |                                                                       | T <sub>J</sub> = 100°C |      | 130  | 200  | μA   |

| Table 3-8 | • AFS1500 Quiescent Supply Current Characteristics (continued) |

|-----------|----------------------------------------------------------------|

|-----------|----------------------------------------------------------------|

Notes:

1. ICC is the 1.5 V power supplies, ICC and ICC15A.

2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

3. ICCI includes all ICCI0, ICCI1, ICCI2, and ICCI4.

4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

6. Sleep Mode, VCC = VJTAG = VPUMP = 0 V.

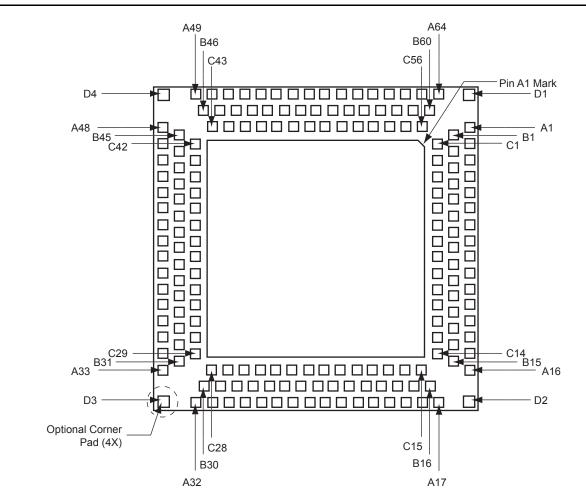

# **QN180**

Note: The die attach paddle center of the package is tied to ground (GND).

# Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/default.aspx.

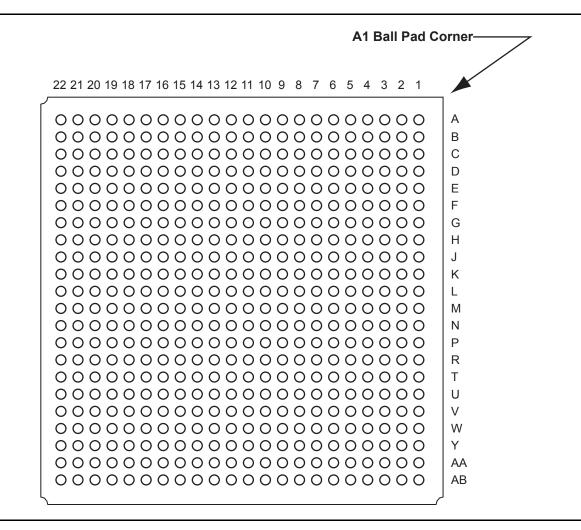

# FG484

# Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/default.aspx.

Package Pin Assignments

|               | FG484           |                  | FG484         |                 |                  |  |  |  |

|---------------|-----------------|------------------|---------------|-----------------|------------------|--|--|--|

| Pin<br>Number | AFS600 Function | AFS1500 Function | Pin<br>Number | AFS600 Function | AFS1500 Function |  |  |  |

| V3            | VCCIB4          | VCCIB4           | W16           | GNDA            | GNDA             |  |  |  |

| V4            | GEA1/IO61PDB4V0 | GEA1/IO88PDB4V0  | W17           | AV9             | AV9              |  |  |  |

| V5            | GEA0/IO61NDB4V0 | GEA0/IO88NDB4V0  | W18           | VCCIB2          | VCCIB2           |  |  |  |

| V6            | GND             | GND              | W19           | NC              | IO68PPB2V0       |  |  |  |

| V7            | VCC33PMP        | VCC33PMP         | W20           | тск             | TCK              |  |  |  |

| V8            | NC              | NC               | W21           | GND             | GND              |  |  |  |

| V9            | VCC33A          | VCC33A           | W22           | NC              | IO76PPB2V0       |  |  |  |

| V10           | AG4             | AG4              | Y1            | GEC2/IO60PDB4V0 | GEC2/IO87PDB4V0  |  |  |  |

| V11           | AT4             | AT4              | Y2            | IO60NDB4V0      | IO87NDB4V0       |  |  |  |

| V12           | ATRTN2          | ATRTN2           | Y3            | GEA2/IO58PDB4V0 | GEA2/IO85PDB4V0  |  |  |  |

| V13           | AT5             | AT5              | Y4            | IO58NDB4V0      | IO85NDB4V0       |  |  |  |

| V14           | VCC33A          | VCC33A           | Y5            | NCAP            | NCAP             |  |  |  |

| V15           | NC              | NC               | Y6            | AC0             | AC0              |  |  |  |

| V16           | VCC33A          | VCC33A           | Y7            | VCC33A          | VCC33A           |  |  |  |

| V17           | GND             | GND              | Y8            | AC1             | AC1              |  |  |  |

| V18           | TMS             | TMS              | Y9            | AC2             | AC2              |  |  |  |

| V19           | VJTAG           | VJTAG            | Y10           | VCC33A          | VCC33A           |  |  |  |

| V20           | VCCIB2          | VCCIB2           | Y11           | AC3             | AC3              |  |  |  |

| V21           | TRST            | TRST             | Y12           | AC6             | AC6              |  |  |  |

| V22           | TDO             | TDO              | Y13           | VCC33A          | VCC33A           |  |  |  |

| W1            | NC              | IO93PDB4V0       | Y14           | AC7             | AC7              |  |  |  |

| W2            | GND             | GND              | Y15           | AC8             | AC8              |  |  |  |

| W3            | NC              | IO93NDB4V0       | Y16           | VCC33A          | VCC33A           |  |  |  |

| W4            | GEB2/IO59PDB4V0 | GEB2/IO86PDB4V0  | Y17           | AC9             | AC9              |  |  |  |

| W5            | IO59NDB4V0      | IO86NDB4V0       | Y18           | ADCGNDREF       | ADCGNDREF        |  |  |  |

| W6            | AV0             | AV0              | Y19           | PTBASE          | PTBASE           |  |  |  |

| W7            | GNDA            | GNDA             | Y20           | GNDNVM          | GNDNVM           |  |  |  |

| W8            | AV1             | AV1              | Y21           | VCCNVM          | VCCNVM           |  |  |  |

| W9            | AV2             | AV2              | Y22           | VPUMP           | VPUMP            |  |  |  |

| W10           | GNDA            | GNDA             |               | •               | 1                |  |  |  |

| W11           | AV3             | AV3              |               |                 |                  |  |  |  |

| W12           | AV6             | AV6              |               |                 |                  |  |  |  |

| W13           | GNDA            | GNDA             |               |                 |                  |  |  |  |

| W14           | AV7             | AV7              |               |                 |                  |  |  |  |

| W15           | AV8             | AV8              |               |                 |                  |  |  |  |

|               |                 |                  |               |                 |                  |  |  |  |

Fusion Family of Mixed Signal FPGAs

| Revision                    | Changes                                                                                                                                                                                                                                    | Page            |  |  |  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|

| Advance v0.8<br>(continued) | This sentence was updated in the "No-Glitch MUX (NGMUX)" section to delete GLA:<br>The GLMUXCFG[1:0] configuration bits determine the source of the CLK inputs (i.e., internal signal or GLC).                                             |                 |  |  |  |

|                             | In Table 2-13 • NGMUX Configuration and Selection Table, 10 and 11 were deleted.                                                                                                                                                           | 2-32            |  |  |  |

|                             | The method to enable sleep mode was updated for bit 0 in Table 2-16 • RTC Control/Status Register.                                                                                                                                         | 2-38            |  |  |  |

|                             | S2 was changed to D2 in Figure 2-39 • Read Waveform (Pipe Mode, 32-bit access) for RD[31:0] was updated.                                                                                                                                   | 2-51            |  |  |  |

|                             | The definitions for bits 2 and 3 were updated in Table 2-24 • Page Status Bit Definition.                                                                                                                                                  | 2-52            |  |  |  |

|                             | Figure 2-46 • FlashROM Timing Diagram was updated.                                                                                                                                                                                         | 2-58            |  |  |  |

|                             | Table 2-26 • FlashROM Access Time is new.                                                                                                                                                                                                  | 2-58            |  |  |  |

|                             | Figure 2-55 • Write Access After Write onto Same Address, Figure 2-56 • Read Access After Write onto Same Address, and Figure 2-57 • Write Access After Read onto Same Address are new.                                                    |                 |  |  |  |

|                             | Table 2-31 • RAM4K9 and Table 2-32 • RAM512X18 were updated.                                                                                                                                                                               | 2-71, 2-72      |  |  |  |

|                             | The VAREF and SAMPLE functions were updated in Table 2-36 • Analog Block Pin Description.                                                                                                                                                  | 2-82            |  |  |  |

|                             | The title of Figure 2-72 • Timing Diagram for Current Monitor Strobe was updated to add the word "positive."                                                                                                                               |                 |  |  |  |

|                             | The "Gate Driver" section was updated to give information about the switching rate in High Current Drive mode.                                                                                                                             | 2-94            |  |  |  |

|                             | The "ADC Description" section was updated to include information about the SAMPLE and BUSY signals and the maximum frequencies for SYSCLK and ADCCLK. EQ 2 was updated to add parentheses around the entire expression in the denominator. |                 |  |  |  |

|                             | Table 2-46 $\cdot$ Analog Channel Specifications and Table 2-47 $\cdot$ ADC Characteristics in Direct Input Mode were updated.                                                                                                             | 2-118,<br>2-121 |  |  |  |

|                             | The note was removed from Table 2-55 • Analog Multiplexer Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3).                                                                                                                              | 2-131           |  |  |  |

|                             | Table 2-63 • Internal Temperature Monitor Control Truth Table is new.                                                                                                                                                                      | 2-132           |  |  |  |

|                             | The "Cold-Sparing Support" section was updated to add information about cases where current draw can occur.                                                                                                                                | 2-143           |  |  |  |

|                             | Figure 2-104 • Solution 4 was updated.                                                                                                                                                                                                     | 2-147           |  |  |  |

|                             | Table 2-75 • Fusion Standard I/O Standards—OUT_DRIVE Settings was updated.                                                                                                                                                                 | 2-153           |  |  |  |

|                             | The "GNDA Ground (analog)" section and "GNDAQ Ground (analog quiet)" section were updated to add information about maximum differential voltage.                                                                                           | 2-224           |  |  |  |

|                             | The "V <sub>AREF</sub> Analog Reference Voltage" section and "VPUMP Programming Supply Voltage" section were updated.                                                                                                                      |                 |  |  |  |

|                             | The "V_{CCPLA/B} PLL Supply Voltage" section was updated to include information about the east and west PLLs.                                                                                                                              | 2-225           |  |  |  |

|                             | The V <sub>COMPLF</sub> pin description was deleted.                                                                                                                                                                                       | N/A             |  |  |  |

|                             | The "Axy Analog Input/Output" section was updated with information about grounding and floating the pin.                                                                                                                                   | 2-226           |  |  |  |