Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Detailo                        |                                                                          |

|--------------------------------|--------------------------------------------------------------------------|

| Product Status                 | Active                                                                   |

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | -                                                                        |

| Total RAM Bits                 | 276480                                                                   |

| Number of I/O                  | 252                                                                      |

| Number of Gates                | 1500000                                                                  |

| Voltage - Supply               | 1.425V ~ 1.575V                                                          |

| Mounting Type                  | Surface Mount                                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                          |

| Package / Case                 | 676-BGA                                                                  |

| Supplier Device Package        | 676-FBGA (27x27)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/afs1500-fgg676 |

|                                |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Fusion Device Family Overview

The FlashPoint tool in the Fusion development software solutions, Libero SoC and Designer, has extensive support for flash memory blocks and FlashROM. One such feature is auto-generation of sequential programming files for applications requiring a unique serial number in each part. Another feature allows the inclusion of static data for system version control. Data for the FlashROM can be generated quickly and easily using the Libero SoC and Designer software tools. Comprehensive programming file support is also included to allow for easy programming of large numbers of parts with differing FlashROM contents.

### SRAM and FIFO

Fusion devices have embedded SRAM blocks along the north and south sides of the device. Each variable-aspect-ratio SRAM block is 4,608 bits in size. Available memory configurations are 256×18, 512×9, 1k×4, 2k×2, and 4k×1 bits. The individual blocks have independent read and write ports that can be configured with different bit widths on each port. For example, data can be written through a 4-bit port and read as a single bitstream. The SRAM blocks can be initialized from the flash memory blocks or via the device JTAG port (ROM emulation mode), using the UJTAG macro.

In addition, every SRAM block has an embedded FIFO control unit. The control unit allows the SRAM block to be configured as a synchronous FIFO without using additional core VersaTiles. The FIFO width and depth are programmable. The FIFO also features programmable Almost Empty (AEMPTY) and Almost Full (AFULL) flags in addition to the normal EMPTY and FULL flags. The embedded FIFO control unit contains the counters necessary for the generation of the read and write address pointers. The SRAM/FIFO blocks can be cascaded to create larger configurations.

## **Clock Resources**

## PLLs and Clock Conditioning Circuits (CCCs)

Fusion devices provide designers with very flexible clock conditioning capabilities. Each member of the Fusion family contains six CCCs. In the two larger family members, two of these CCCs also include a PLL; the smaller devices support one PLL.

The inputs of the CCC blocks are accessible from the FPGA core or from one of several inputs with dedicated CCC block connections.

The CCC block has the following key features:

- Wide input frequency range (f<sub>IN CCC</sub>) = 1.5 MHz to 350 MHz

- Output frequency range (f<sub>OUT CCC</sub>) = 0.75 MHz to 350 MHz

- Clock phase adjustment via programmable and fixed delays from -6.275 ns to +8.75 ns

- Clock skew minimization (PLL)

- Clock frequency synthesis (PLL)

- · On-chip analog clocking resources usable as inputs:

- 100 MHz on-chip RC oscillator

- Crystal oscillator

Additional CCC specifications:

- Internal phase shift = 0°, 90°, 180°, and 270°

- Output duty cycle =  $50\% \pm 1.5\%$

- Low output jitter. Samples of peak-to-peak period jitter when a single global network is used:

- 70 ps at 350 MHz

- 90 ps at 100 MHz

- 180 ps at 24 MHz

- Worst case < 2.5% × clock period

- Maximum acquisition time = 150 µs

- Low power consumption of 5 mW

The system application, Level 3, is the larger user application that utilizes one or more applets. Designing at the highest level of abstraction supported by the Fusion technology stack, the application can be easily created in FPGA gates by importing and configuring multiple applets.

In fact, in some cases an entire FPGA system design can be created without any HDL coding.

An optional MCU enables a combination of software and HDL-based design methodologies. The MCU can be on-chip or off-chip as system requirements dictate. System portioning is very flexible, allowing the MCU to reside above the applets or to absorb applets, or applets and backbone, if desired.

The Fusion technology stack enables a very flexible design environment. Users can engage in design across a continuum of abstraction from very low to very high.

# **Core Architecture**

## VersaTile

Based upon successful ProASIC3/E logic architecture, Fusion devices provide granularity comparable to gate arrays. The Fusion device core consists of a sea-of-VersaTiles architecture.

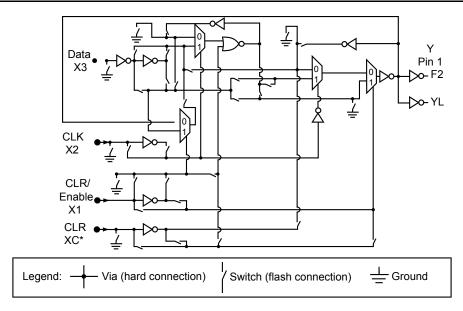

As illustrated in Figure 2-2, there are four inputs in a logic VersaTile cell, and each VersaTile can be configured using the appropriate flash switch connections:

- Any 3-input logic function

- Latch with clear or set

- D-flip-flop with clear or set

- Enable D-flip-flop with clear or set (on a 4th input)

VersaTiles can flexibly map the logic and sequential gates of a design. The inputs of the VersaTile can be inverted (allowing bubble pushing), and the output of the tile can connect to high-speed, very-long-line routing resources. VersaTiles and larger functions are connected with any of the four levels of routing hierarchy.

When the VersaTile is used as an enable D-flip-flop, the SET/CLR signal is supported by a fourth input, which can only be routed to the core cell over the VersaNet (global) network.

The output of the VersaTile is F2 when the connection is to the ultra-fast local lines, or YL when the connection is to the efficient long-line or very-long-line resources (Figure 2-2).

*Note:* \*This input can only be connected to the global clock distribution network.

Figure 2-2 • Fusion Core VersaTile

Table 2-57 details the settings available to control the prescaler values of the AV, AC, and AT pins. Note that the AT pin has a reduced number of available prescaler values.

| Control Lines<br>Bx[2:0] | Scaling<br>Factor, Pad to<br>ADC Input | LSB for an<br>8-Bit<br>Conversion <sup>1</sup><br>(mV) | LSB for a<br>10-Bit<br>Conversion <sup>1</sup><br>(mV) | LSB for a<br>12-Bit<br>Conversion <sup>1</sup><br>(mV) | Full-Scale<br>Voltage in<br>10-Bit<br>Mode <sup>2</sup> | Range Name |

|--------------------------|----------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|------------|

| 000 <sup>3</sup>         | 0.15625                                | 64                                                     | 16                                                     | 4                                                      | 16.368 V                                                | 16 V       |

| 001                      | 0.3125                                 | 32                                                     | 8                                                      | 2                                                      | 8.184 V                                                 | 8 V        |

| 010 <sup>3</sup>         | 0.625                                  | 16                                                     | 4                                                      | 1                                                      | 4.092 V                                                 | 4 V        |

| 011                      | 1.25                                   | 8                                                      | 2                                                      | 0.5                                                    | 2.046 V                                                 | 2 V        |

| 100                      | 2.5                                    | 4                                                      | 1                                                      | 0.25                                                   | 1.023 V                                                 | 1 V        |

| 101                      | 5.0                                    | 2                                                      | 0.5                                                    | 0.125                                                  | 0.5115 V                                                | 0.5 V      |

| 110                      | 10.0                                   | 1                                                      | 0.25                                                   | 0.0625                                                 | 0.25575 V                                               | 0.25 V     |

| 111                      | 20.0                                   | 0.5                                                    | 0.125                                                  | 0.03125                                                | 0.127875 V                                              | 0.125 V    |

Table 2-57 Prescaler Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)

Notes:

1. LSB voltage equivalences assume VAREF = 2.56 V.

2. Full Scale voltage for n-bit mode: ((2^n) - 1) x (LSB for a n-bit Conversion)

3. These are the only valid ranges for the Temperature Monitor Block Prescaler.

Table 2-58 details the settings available to control the MUX within each of the AV, AC, and AT circuits. This MUX determines whether the signal routed to the ADC is the direct analog input, prescaled signal, or output of either the Current Monitor Block or the Temperature Monitor Block.

Table 2-58 Analog Multiplexer Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)

| Control Lines Bx[4] | Control Lines Bx[3] | ADC Connected To                      |

|---------------------|---------------------|---------------------------------------|

| 0                   | 0                   | Prescaler                             |

| 0                   | 1                   | Direct input                          |

| 1                   | 0                   | Current amplifier temperature monitor |

| 1                   | 1                   | Not valid                             |

Table 2-59 details the settings available to control the Direct Analog Input switch for the AV, AC, and AT pins.

Table 2-59 Direct Analog Input Switch Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)

| Control Lines Bx[5] | Direct Input Switch |

|---------------------|---------------------|

| 0                   | Off                 |

| 1                   | On                  |

Table 2-60 details the settings available to control the polarity of the signals coming to the AV, AC, and AT pins. Note that the only valid setting for the AT pin is logic 0 to support positive voltages.

Table 2-60 Voltage Polarity Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)\*

| Control Lines Bx[6] | Input Signal Polarity |

|---------------------|-----------------------|

| 0                   | Positive              |

| 1                   | Negative              |

Note: \*The B3[6] signal for the AT pad should be kept at logic 0 to accept only positive voltages.

### Integrated Voltage Reference

The Fusion device has an integrated on-chip 2.56 V reference voltage for the ADC. The value of this reference voltage was chosen to make the prescaling and postscaling factors for the prescaler blocks change in a binary fashion. However, if desired, an external reference voltage of up to 3.3 V can be connected between the VAREF and ADCGNDREF pins. The VAREFSEL control pin is used to select the reference voltage.

### Table 2-42 • VAREF Bit Function

| Name  | Bit | Function                                                           |

|-------|-----|--------------------------------------------------------------------|

| VAREF | 0   | Reference voltage selection                                        |

|       |     | 0 – Internal voltage reference selected. VAREF pin outputs 2.56 V. |

|       |     | 1 – Input external voltage reference from VAREF and ADCGNDREF      |

### **ADC Clock**

The speed of the ADC depends on its internal clock, ADCCLK, which is not accessible to users. The ADCCLK is derived from SYSCLK. Input signal TVC[7:0], Time Divider Control, determines the speed of the ADCCLK in relationship to SYSCLK, based on EQ 15.

$$t_{ADCCLK} = 4 \times (1 + TVC) \times t_{SYSCLK}$$

EQ 15

TVC: Time Divider Control (0-255)

$t_{\text{ADCCLK}}$  is the period of ADCCLK, and must be between 0.5 MHz and 10 MHz  $t_{\text{SYSCLK}}$  is the period of SYSCLK

#### Table 2-43 • TVC Bits Function

| Name | Bits  | Function               |

|------|-------|------------------------|

| TVC  | [7:0] | SYSCLK divider control |

The frequency of ADCCLK, f<sub>ADCCLK</sub>, must be within 0.5 Hz to 10 MHz.

The inputs to the ADC are synchronized to SYSCLK. A conversion is initiated by asserting the ADCSTART signal on a rising edge of SYSCLK. Figure 2-90 on page 2-112 and Figure 2-91 on page 2-112 show the timing diagram for the ADC.

### Acquisition Time or Sample Time Control

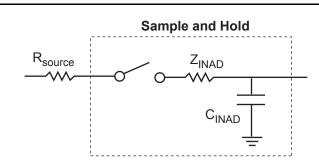

Acquisition time (t<sub>SAMPLE</sub>) specifies how long an analog input signal has to charge the internal capacitor array. Figure 2-88 shows a simplified internal input sampling mechanism of a SAR ADC.

### Figure 2-88 • Simplified Sample and Hold Circuitry

The internal impedance ( $Z_{INAD}$ ), external source resistance ( $R_{SOURCE}$ ), and sample capacitor ( $C_{INAD}$ ) form a simple RC network. As a result, the accuracy of the ADC can be affected if the ADC is given insufficient time to charge the capacitor. To resolve this problem, you can either reduce the source resistance or increase the sampling time by changing the acquisition time using the STC signal.

## Single-Ended I/O Characteristics

### 3.3 V LVTTL / 3.3 V LVCMOS

Low-Voltage Transistor–Transistor Logic is a general-purpose standard (EIA/JESD) for 3.3 V applications. It uses an LVTTL input buffer and push-pull output buffer. The 3.3 V LVCMOS standard is supported as part of the 3.3 V LVTTL support.

| Table 2-102 • Minimum | and Maximum DC | Input and Output Levels |

|-----------------------|----------------|-------------------------|

|                       |                | mput and Output Levels  |

| 3.3 V LVTTL /<br>3.3 V LVCMOS | v         | IL        | v         | н         | VOL       | VOH       | IOL | юн | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive Strength                | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| Applicable to P               | ro I/O Ba | nks       |           | •         |           |           |     |    |                         | •                       |                  |                  |

| 4 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 4   | 4  | 27                      | 25                      | 10               | 10               |

| 8 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 8   | 8  | 54                      | 51                      | 10               | 10               |

| 12 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 12  | 12 | 109                     | 103                     | 10               | 10               |

| 16 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 16  | 16 | 127                     | 132                     | 10               | 10               |

| 24 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 24  | 24 | 181                     | 268                     | 10               | 10               |

| Applicable to A               | dvanced   | I/O Bank  | s         | •         |           |           |     |    |                         | •                       |                  |                  |

| 2 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 2   | 2  | 27                      | 25                      | 10               | 10               |

| 4 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 4   | 4  | 27                      | 25                      | 10               | 10               |

| 6 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 6   | 6  | 54                      | 51                      | 10               | 10               |

| 8 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 8   | 8  | 54                      | 51                      | 10               | 10               |

| 12 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 12  | 12 | 109                     | 103                     | 10               | 10               |

| 16 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 16  | 16 | 127                     | 132                     | 10               | 10               |

| 24 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 24  | 24 | 181                     | 268                     | 10               | 10               |

| Applicable to S               | tandard I | /O Banks  |           | •         |           |           |     |    |                         |                         |                  |                  |

| 2 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 2   | 2  | 27                      | 25                      | 10               | 10               |

| 4 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 4   | 4  | 27                      | 25                      | 10               | 10               |

| 6 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 6   | 6  | 54                      | 51                      | 10               | 10               |

| 8 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 8   | 8  | 54                      | 51                      | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

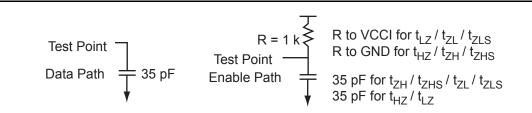

Figure 2-119 • AC Loading

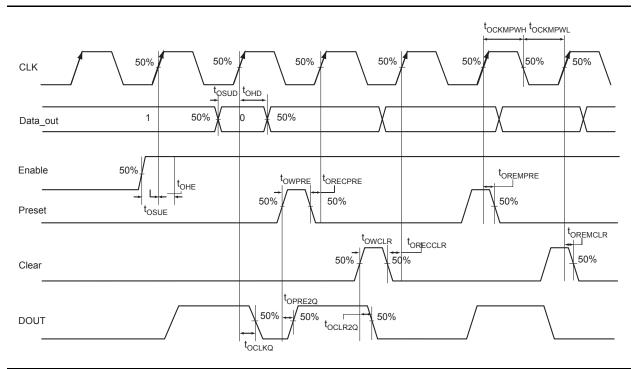

### **Output Register**

### **Timing Characteristics**

Table 2-177 • Output Data Register Propagation DelaysCommercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                          | -2   | -1   | Std. | Units |

|----------------------|----------------------------------------------------------------------|------|------|------|-------|

| t <sub>oclkq</sub>   | Clock-to-Q of the Output Data Register                               | 0.59 | 0.67 | 0.79 | ns    |

| t <sub>OSUD</sub>    | Data Setup Time for the Output Data Register                         | 0.31 | 0.36 | 0.42 | ns    |

| t <sub>OHD</sub>     | Data Hold Time for the Output Data Register                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>OSUE</sub>    | Enable Setup Time for the Output Data Register                       | 0.44 | 0.50 | 0.59 | ns    |

| t <sub>OHE</sub>     | Enable Hold Time for the Output Data Register                        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>OCLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Data Register                  | 0.80 | 0.91 | 1.07 | ns    |

| t <sub>OPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Data Register                 | 0.80 | 0.91 | 1.07 | ns    |

| t <sub>OREMCLR</sub> | Asynchronous Clear Removal Time for the Output Data Register         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ORECCLR</sub> | Asynchronous Clear Recovery Time for the Output Data Register        |      | 0.25 | 0.30 | ns    |

| t <sub>OREMPRE</sub> | Asynchronous Preset Removal Time for the Output Data Register        |      | 0.00 | 0.00 | ns    |

| t <sub>ORECPRE</sub> | Asynchronous Preset Recovery Time for the Output Data Register       |      | 0.25 | 0.30 | ns    |

| t <sub>OWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Data Register  | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Data Register | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OCKMPWH</sub> | Clock Minimum Pulse Width High for the Output Data Register          | 0.36 | 0.41 | 0.48 | ns    |

| t <sub>OCKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Data Register           | 0.32 | 0.37 | 0.43 | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

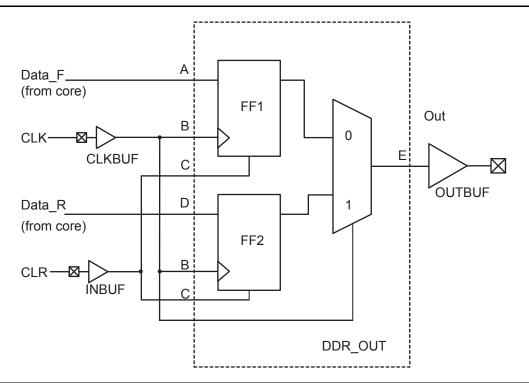

## **Output DDR**

## Figure 2-144 • Output DDR Timing Model

### Table 2-181 • Parameter Definitions

| Parameter Name          | Parameter Definition      | Measuring Nodes (From, To) |

|-------------------------|---------------------------|----------------------------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out              | B, E                       |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out | C, E                       |

| t <sub>DDROREMCLR</sub> | Clear Removal             | С, В                       |

| t <sub>DDRORECCLR</sub> | Clear Recovery            | С, В                       |

| t <sub>DDROSUD1</sub>   | Data Setup Data_F         | A, B                       |

| t <sub>DDROSUD2</sub>   | Data Setup Data_R         | D, B                       |

| t <sub>DDROHD1</sub>    | Data Hold Data_F          | А, В                       |

| t <sub>DDROHD2</sub>    | Data Hold Data_R          | D, B                       |

### ISP

Fusion devices support IEEE 1532 ISP via JTAG and require a single VPUMP voltage of 3.3 V during programming. In addition, programming via a microcontroller in a target system can be achieved. Refer to the standard or the "In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X" chapter of the *Fusion FPGA Fabric User's Guide* for more details.

## JTAG IEEE 1532

### Programming with IEEE 1532

Fusion devices support the JTAG-based IEEE1532 standard for ISP. As part of this support, when a Fusion device is in an unprogrammed state, all user I/O pins are disabled. This is achieved by keeping the global IO\_EN signal deactivated, which also has the effect of disabling the input buffers. Consequently, the SAMPLE instruction will have no effect while the Fusion device is in this unprogrammed state—different behavior from that of the ProASICPLUS® device family. This is done because SAMPLE is defined in the IEEE1532 specification as a noninvasive instruction. If the input buffers were to be enabled by SAMPLE temporarily turning on the I/Os, then it would not truly be a noninvasive instruction. Refer to the standard or the "In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X" chapter of the *Fusion FPGA Fabric User's Guide* for more details.

### **Boundary Scan**

Fusion devices are compatible with IEEE Standard 1149.1, which defines a hardware architecture and the set of mechanisms for boundary scan testing. The basic Fusion boundary scan logic circuit is composed of the test access port (TAP) controller, test data registers, and instruction register (Figure 2-146 on page 2-230). This circuit supports all mandatory IEEE 1149.1 instructions (EXTEST, SAMPLE/PRELOAD, and BYPASS) and the optional IDCODE instruction (Table 2-185 on page 2-230).

Each test section is accessed through the TAP, which has five associated pins: TCK (test clock input), TDI, TDO (test data input and output), TMS (test mode selector), and TRST (test reset input). TMS, TDI, and TRST are equipped with pull-up resistors to ensure proper operation when no input data is supplied to them. These pins are dedicated for boundary scan test usage. Refer to the "JTAG Pins" section on page 2-226 for pull-up/-down recommendations for TDO and TCK pins. The TAP controller is a 4-bit state machine (16 states) that operates as shown in Figure 2-146 on page 2-230. The 1s and 0s represent the values that must be present on TMS at a rising edge of TCK for the given state transition to occur. IR and DR indicate that the instruction register or the data register is operating in that state.

| VJTAG          | Tie-Off Resistance* |

|----------------|---------------------|

| VJTAG at 3.3 V | 200 Ω to 1 kΩ       |

| VJTAG at 2.5 V | 200 Ω to 1 kΩ       |

| VJTAG at 1.8 V | 500 Ω to 1 kΩ       |

| VJTAG at 1.5 V | 500 Ω to 1 kΩ       |

#### Table 2-184 • TRST and TCK Pull-Down Recommendations

*Note:* \**Equivalent parallel resistance if more than one device is on JTAG chain.*

The TAP controller receives two control inputs (TMS and TCK) and generates control and clock signals for the rest of the test logic architecture. On power-up, the TAP controller enters the Test-Logic-Reset state. To guarantee a reset of the controller from any of the possible states, TMS must remain High for five TCK cycles. The TRST pin can also be used to asynchronously place the TAP controller in the Test-Logic-Reset state.

Fusion devices support three types of test data registers: bypass, device identification, and boundary scan. The bypass register is selected when no other register needs to be accessed in a device. This speeds up test data transfer to other devices in a test data path. The 32-bit device identification register is a shift register with four fields (LSB, ID number, part number, and version). The boundary scan register observes and controls the state of each I/O pin. Each I/O cell has three boundary scan register cells, each with a serial-in, serial-out, parallel-in, and parallel-out pin.

The serial pins are used to serially connect all the boundary scan register cells in a device into a boundary scan register chain, which starts at the TDI pin and ends at the TDO pin. The parallel ports are

Fusion Family of Mixed Signal FPGAs

| PQ208         |                 |                 | PQ208         |                 |                 |  |

|---------------|-----------------|-----------------|---------------|-----------------|-----------------|--|

| Pin<br>Number | AFS250 Function | AFS600 Function | Pin<br>Number | AFS250 Function | AFS600 Function |  |

| 74            | AV2             | AV4             | 111           | VCCNVM          | VCCNVM          |  |

| 75            | AC2             | AC4             | 112           | VCC             | VCC             |  |

| 76            | AG2             | AG4             | 112           | VCC             | VCC             |  |

| 77            | AT2             | AT4             | 113           | VPUMP           | VPUMP           |  |

| 78            | ATRTN1          | ATRTN2          | 114           | GNDQ            | NC              |  |

| 79            | AT3             | AT5             | 115           | VCCIB1          | ТСК             |  |

| 80            | AG3             | AG5             | 116           | ТСК             | TDI             |  |

| 81            | AC3             | AC5             | 117           | TDI             | TMS             |  |

| 82            | AV3             | AV5             | 118           | TMS             | TDO             |  |

| 83            | AV4             | AV6             | 119           | TDO             | TRST            |  |

| 84            | AC4             | AC6             | 120           | TRST            | VJTAG           |  |

| 85            | AG4             | AG6             | 121           | VJTAG           | IO57NDB2V0      |  |

| 86            | AT4             | AT6             | 122           | IO57NDB1V0      | GDC2/IO57PDB2V  |  |

| 87            | ATRTN2          | ATRTN3          | 123           | GDC2/IO57PDB1V0 | IO56NDB2V0      |  |

| 88            | AT5             | AT7             | 124           | IO56NDB1V0      | GDB2/IO56PDB2V  |  |

| 89            | AG5             | AG7             | 125           | GDB2/IO56PDB1V0 | IO55NDB2V0      |  |

| 90            | AC5             | AC7             | 126           | VCCIB1          | GDA2/IO55PDB2V  |  |

| 91            | AV5             | AV7             | 127           | GND             | GDA0/IO54NDB2V  |  |

| 92            | NC              | AV8             | 128           | IO55NDB1V0      | GDA1/IO54PDB2V  |  |

| 93            | NC              | AC8             | 129           | GDA2/IO55PDB1V0 | VCCIB2          |  |

| 94            | NC              | AG8             | 130           | GDA0/IO54NDB1V0 | GND             |  |

| 95            | NC              | AT8             | 131           | GDA1/IO54PDB1V0 | VCC             |  |

| 96            | NC              | ATRTN4          | 132           | GDB0/IO53NDB1V0 | GCA0/IO45NDB2   |  |

| 97            | NC              | AT9             | 133           | GDB1/IO53PDB1V0 | GCA1/IO45PDB2V  |  |

| 98            | NC              | AG9             | 134           | GDC0/IO52NDB1V0 | GCB0/IO44NDB2V  |  |

| 99            | NC              | AC9             | 135           | GDC1/IO52PDB1V0 | GCB1/IO44PDB2V  |  |

| 100           | NC              | AV9             | 136           | IO51NSB1V0      | GCC0/IO43NDB2   |  |

| 101           | GNDAQ           | GNDAQ           |               |                 | 0               |  |

| 102           | VCC33A          | VCC33A          | 137           | VCCIB1          | GCC1/IO43PDB2V  |  |

| 103           | ADCGNDREF       | ADCGNDREF       | 138           | GND             | IO42NDB2V0      |  |

| 104           | VAREF           | VAREF           | 139           | VCC             | IO42PDB2V0      |  |

| 105           | PUB             | PUB             | 140           | IO50NDB1V0      | IO41NDB2V0      |  |

| 106           | VCC33A          | VCC33A          | 141           | IO50PDB1V0      | GCC2/IO41PDB2V  |  |

| 107           | GNDA            | GNDA            | 142           | GCA0/IO49NDB1V0 | VCCIB2          |  |

| 108           | PTEM            | PTEM            | 143           | GCA1/IO49PDB1V0 | GND             |  |

| 109           | PTBASE          | PTBASE          | 144           | GCB0/IO48NDB1V0 | VCC             |  |

| 110           | GNDNVM          | GNDNVM          | 145           | GCB1/IO48PDB1V0 | IO40NDB2V0      |  |

| -             | <u> </u>        | <u> </u>        | 146           | GCC0/IO47NDB1V0 | GCB2/IO40PDB2V  |  |

| FG256      |                 |                 |                 |                  |  |  |  |

|------------|-----------------|-----------------|-----------------|------------------|--|--|--|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |  |  |  |

| H3         | XTAL2           | XTAL2           | XTAL2           | XTAL2            |  |  |  |

| H4         | XTAL1           | XTAL1           | XTAL1           | XTAL1            |  |  |  |

| H5         | GNDOSC          | GNDOSC          | GNDOSC          | GNDOSC           |  |  |  |

| H6         | VCCOSC          | VCCOSC          | VCCOSC          | VCCOSC           |  |  |  |

| H7         | VCC             | VCC             | VCC             | VCC              |  |  |  |

| H8         | GND             | GND             | GND             | GND              |  |  |  |

| H9         | VCC             | VCC             | VCC             | VCC              |  |  |  |

| H10        | GND             | GND             | GND             | GND              |  |  |  |

| H11        | GDC0/IO38NDB1V0 | IO51NDB1V0      | IO47NDB2V0      | IO69NDB2V0       |  |  |  |

| H12        | GDC1/IO38PDB1V0 | IO51PDB1V0      | IO47PDB2V0      | IO69PDB2V0       |  |  |  |

| H13        | GDB1/IO39PDB1V0 | GCA1/IO49PDB1V0 | GCA1/IO45PDB2V0 | GCA1/IO64PDB2V0  |  |  |  |

| H14        | GDB0/IO39NDB1V0 | GCA0/IO49NDB1V0 | GCA0/IO45NDB2V0 | GCA0/IO64NDB2V0  |  |  |  |

| H15        | GCA0/IO36NDB1V0 | GCB0/IO48NDB1V0 | GCB0/IO44NDB2V0 | GCB0/IO63NDB2V0  |  |  |  |

| H16        | GCA1/IO36PDB1V0 | GCB1/IO48PDB1V0 | GCB1/IO44PDB2V0 | GCB1/IO63PDB2V0  |  |  |  |

| J1         | GEA0/IO44NDB3V0 | GFA0/IO66NDB3V0 | GFA0/IO70NDB4V0 | GFA0/IO105NDB4V0 |  |  |  |

| J2         | GEA1/IO44PDB3V0 | GFA1/IO66PDB3V0 | GFA1/IO70PDB4V0 | GFA1/IO105PDB4V0 |  |  |  |

| J3         | IO43NDB3V0      | GFB0/IO67NDB3V0 | GFB0/IO71NDB4V0 | GFB0/IO106NDB4V0 |  |  |  |

| J4         | GEC2/IO43PDB3V0 | GFB1/IO67PDB3V0 | GFB1/IO71PDB4V0 | GFB1/IO106PDB4V0 |  |  |  |

| J5         | NC              | GFC0/IO68NDB3V0 | GFC0/IO72NDB4V0 | GFC0/IO107NDB4V0 |  |  |  |

| J6         | NC              | GFC1/IO68PDB3V0 | GFC1/IO72PDB4V0 | GFC1/IO107PDB4V0 |  |  |  |

| J7         | GND             | GND             | GND             | GND              |  |  |  |

| J8         | VCC             | VCC             | VCC             | VCC              |  |  |  |

| J9         | GND             | GND             | GND             | GND              |  |  |  |

| J10        | VCC             | VCC             | VCC             | VCC              |  |  |  |

| J11        | GDC2/IO41NPB1V0 | IO56NPB1V0      | IO56NPB2V0      | IO83NPB2V0       |  |  |  |

| J12        | NC              | GDB0/IO53NPB1V0 | GDB0/IO53NPB2V0 | GDB0/IO80NPB2V0  |  |  |  |

| J13        | NC              | GDA1/IO54PDB1V0 | GDA1/IO54PDB2V0 | GDA1/IO81PDB2V0  |  |  |  |

| J14        | GDA0/IO40PDB1V0 | GDC1/IO52PPB1V0 | GDC1/IO52PPB2V0 | GDC1/IO79PPB2V0  |  |  |  |

| J15        | NC              | IO50NPB1V0      | IO51NSB2V0      | IO77NSB2V0       |  |  |  |

| J16        | GDA2/IO40NDB1V0 | GDC0/IO52NPB1V0 | GDC0/IO52NPB2V0 | GDC0/IO79NPB2V0  |  |  |  |

| K1         | NC              | IO65NPB3V0      | IO67NPB4V0      | IO92NPB4V0       |  |  |  |

| K2         | VCCIB3          | VCCIB3          | VCCIB4          | VCCIB4           |  |  |  |

| K3         | NC              | IO65PPB3V0      | IO67PPB4V0      | IO92PPB4V0       |  |  |  |

| K4         | NC              | IO64PDB3V0      | IO65PDB4V0      | IO96PDB4V0       |  |  |  |

| K5         | GND             | GND             | GND             | GND              |  |  |  |

| K6         | NC              | IO64NDB3V0      | IO65NDB4V0      | IO96NDB4V0       |  |  |  |

| K7         | VCC             | VCC             | VCC             | VCC              |  |  |  |

| K8         | GND             | GND             | GND             | GND              |  |  |  |

Datasheet Information

| Revision                       | Changes                                                                                                                                                                                                                                           | Page  |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Advance v1.0<br>(January 2008) | All Timing Characteristics tables were updated. For the Differential I/O Standards, the Standard I/O support tables are new.                                                                                                                      | N/A   |

|                                | Table 2-3 • Array Coordinates was updated to change the max x and y values                                                                                                                                                                        | 2-9   |

|                                | Table 2-12 • Fusion CCC/PLL Specification was updated.                                                                                                                                                                                            | 2-31  |

|                                | A note was added to Table 2-16 · RTC ACM Memory Map.                                                                                                                                                                                              | 2-37  |

|                                | A reference to the Peripheral's User's Guide was added to the "Voltage Regulator<br>Power Supply Monitor (VRPSM)" section.                                                                                                                        | 2-42  |

|                                | In Table 2-25 • Flash Memory Block Timing, the commercial conditions were updated.                                                                                                                                                                | 2-55  |

|                                | In Table 2-26 • FlashROM Access Time, the commercial conditions were missing and have been added below the title of the table.                                                                                                                    | 2-58  |

|                                | In Table 2-36 • Analog Block Pin Description, the function description was updated for the ADCRESET.                                                                                                                                              | 2-82  |

|                                | In the "Voltage Monitor" section, the following sentence originally had $\pm$ 10% and it was changed to +10%.                                                                                                                                     | 2-86  |

|                                | The Analog Quad inputs are tolerant up to 12 V + 10%.                                                                                                                                                                                             |       |

|                                | In addition, this statement was deleted from the datasheet:                                                                                                                                                                                       |       |

|                                | Each I/O will draw power when connected to power (3 mA at 3 V).                                                                                                                                                                                   |       |

|                                | The "Terminology" section is new.                                                                                                                                                                                                                 | 2-88  |

|                                | The "Current Monitor" section was significantly updated. Figure 2-72 • Timing Diagram for Current Monitor Strobe to Figure 2-74 • Negative Current Monitor and Table 2-37 • Recommended Resistor for Different Current Range Measurement are new. | 2-90  |

|                                | The "ADC Description" section was updated to add the "Terminology" section.                                                                                                                                                                       | 2-93  |

|                                | In the "Gate Driver" section, 25 mA was changed to 20 mA and 1.5 MHz was changed to 1.3 MHz. In addition, the following sentence was deleted: The maximum AG pad switching frequency is 1.25 MHz.                                                 | 2-94  |

|                                | The "Temperature Monitor" section was updated to rewrite most of the text and add Figure 2-78, Figure 2-79, and Table 2-38 • Temperature Data Format.                                                                                             | 2-96  |

|                                | In Table 2-38 • Temperature Data Format, the temperature K column was changed for 85°C from 538 to 358.                                                                                                                                           | 2-98  |

|                                | In Table 2-45 • ADC Interface Timing, "Typical-Case" was changed to "Worst-Case."                                                                                                                                                                 | 2-110 |

|                                | The "ADC Interface Timing" section is new.                                                                                                                                                                                                        | 2-110 |

|                                | Table 2-46 • Analog Channel Specifications was updated.                                                                                                                                                                                           | 2-118 |

|                                | The "V <sub>CC15A</sub> Analog Power Supply (1.5 V)" section was updated.                                                                                                                                                                         | 2-224 |

|                                | The "V <sub>CCPLA/B</sub> PLL Supply Voltage" section is new.                                                                                                                                                                                     | 2-225 |

|                                | In "V <sub>CCNVM</sub> Flash Memory Block Power Supply (1.5 V)" section, supply was changed to supply input.                                                                                                                                      | 2-224 |

|                                | The "V <sub>CCPLA/B</sub> PLL Supply Voltage" pin description was updated to include the following statement:                                                                                                                                     | 2-225 |

|                                | Actel recommends tying VCCPLX to VCC and using proper filtering circuits to decouple $V_{CC}$ noise from PLL.                                                                                                                                     |       |

|                                | The "V <sub>COMPLA/B</sub> Ground for West and East PLL" section was updated.                                                                                                                                                                     | 2-225 |

Fusion Family of Mixed Signal FPGAs

| Revision                    | Changes                                                                                                                                                                                  | Page  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Advance v0.6<br>(continued) | The "Analog-to-Digital Converter Block" section was updated with the following statement:<br>"All results are MSB justified in the ADC."                                                 | 2-99  |

|                             | The information about the ADCSTART signal was updated in the "ADC Description" section.                                                                                                  | 2-102 |

|                             | Table 2-46 · Analog Channel Specifications was updated.                                                                                                                                  | 2-118 |

|                             | Table 2-47 · ADC Characteristics in Direct Input Mode was updated.                                                                                                                       | 2-121 |

|                             | Table 2-51 • ACM Address Decode Table for Analog Quad was updated.                                                                                                                       | 2-127 |

|                             | In Table 2-53 • Analog Quad ACM Byte Assignment, the Function and Default Setting for Bit 6 in Byte 3 was updated.                                                                       | 2-130 |

|                             | The "Introduction" section was updated to include information about digital inputs, outputs, and bibufs.                                                                                 | 2-133 |

|                             | In Table 2-69 • Fusion Pro I/O Features, the programmable delay descriptions were updated for the following features:<br>Single-ended receiver                                           | 2-137 |

|                             | Voltage-referenced differential receiver                                                                                                                                                 |       |

|                             | LVDS/LVPECL differential receiver features                                                                                                                                               |       |

|                             | The "User I/O Naming Convention" section was updated to include "V" and "z" descriptions                                                                                                 | 2-159 |

|                             | The "VCC33PMP Analog Power Supply (3.3 V)" section was updated to include information about avoiding high current draw.                                                                  | 2-224 |

|                             | The "VCCNVM Flash Memory Block Power Supply (1.5 V)" section was updated to include information about avoiding high current draw.                                                        | 2-224 |

|                             | The "VMVx I/O Supply Voltage (quiet)" section was updated to include this statement: VMV and VCCI must be connected to the same power supply and $V_{CCI}$ pins within a given I/O bank. | 2-185 |

|                             | The "PUB Push Button" section was updated to include information about leaving the pin floating if it is not used.                                                                       | 2-228 |

|                             | The "PTBASE Pass Transistor Base" section was updated to include information about leaving the pin floating if it is not used.                                                           | 2-228 |

|                             | The "PTEM Pass Transistor Emitter" section was updated to include information about leaving the pin floating if it is not used.                                                          | 2-228 |

|                             | The heading was incorrect in the "208-Pin PQFP" table. It should be AFS250 and not AFS090.                                                                                               | 3-8   |