Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Active                                                                    |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | 36864                                                                     |

| Number of I/O                  | 114                                                                       |

| Number of Gates                | 250000                                                                    |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                        |

| Package / Case                 | 256-LBGA                                                                  |

| Supplier Device Package        | 256-FPBGA (17x17)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/afs250-2fgg256i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Temperature Grade Offerings**

| Fusion Devices        | AFS090 | AFS250                | AFS600                | AFS1500                |

|-----------------------|--------|-----------------------|-----------------------|------------------------|

| ARM Cortex-M1 Devices |        | M1AFS250              | M1AFS600              | M1AFS1500              |

| Pigeon Point Devices  |        |                       | P1AFS600 <sup>3</sup> | P1AFS1500 <sup>3</sup> |

| MicroBlade Devices    |        | U1AFS250 <sup>4</sup> | U1AFS600 <sup>4</sup> | U1AFS1500 <sup>4</sup> |

| QN108 <sup>5</sup>    | C, I   | -                     | _                     | _                      |

| QN180 <sup>5</sup>    | C, I   | C, I                  | _                     | _                      |

| PQ208                 | _      | C, I                  | C, I                  | _                      |

| FG256                 | C, I   | C, I                  | C, I                  | C, I                   |

| FG484                 | _      | _                     | C, I                  | C, I                   |

| FG676                 | _      | _                     | _                     | C, I                   |

#### Notes:

- 1. C = Commercial Temperature Range: 0°C to 85°C Junction

- 2. I = Industrial Temperature Range: -40°C to 100°C Junction

- 3. Pigeon Point devices are only offered in FG484 and FG256.

- 4. MicroBlade devices are only offered in FG256.

- 5. Package not available.

# **Speed Grade and Temperature Grade Matrix**

|       | Std. <sup>1</sup> | <b>-1</b> | <b>-2</b> <sup>2</sup> |

|-------|-------------------|-----------|------------------------|

| $C^3$ | ✓                 | ✓         | ✓                      |

| 14    | ✓                 | ✓         | ✓                      |

#### Notes:

- 1. MicroBlade devices are only offered in standard speed grade.

- 2. Pigeon Point devices are only offered in -2 speed grade.

- 3. C = Commercial Temperature Range: 0°C to 85°C Junction

- 4. I = Industrial Temperature Range: -40°C to 100°C Junction

Contact your local Microsemi SoC Products Group representative for device availability:

http://www.microsemi.com/index.php?option=com content&id=137&lang=en&view=article.

# Cortex-M1, Pigeon Point, and MicroBlade Fusion Device Information

This datasheet provides information for all Fusion (AFS), Cortex-M1 (M1), Pigeon Point (P1), and MicroBlade (U1) devices. The remainder of the document will only list the Fusion (AFS) devices. Please apply relevant information to M1, P1, and U1 devices when appropriate. Please note the following:

- Cortex-M1 devices are offered in the same speed grades and packages as basic Fusion devices.

- Pigeon Point devices are only offered in –2 speed grade and FG484 and FG256 packages.

- MicroBlade devices are only offered in standard speed grade and the FG256 package.

IV Revision 6

Fusion Device Family Overview

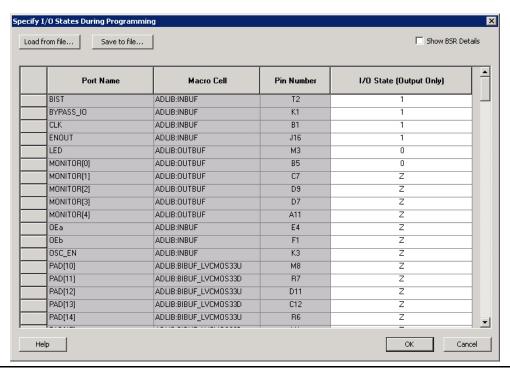

## Specifying I/O States During Programming

You can modify the I/O states during programming in FlashPro. In FlashPro, this feature is supported for PDB files generated from Designer v8.5 or greater. See the *FlashPro User Guide* for more information.

Note: PDB files generated from Designer v8.1 to Designer v8.4 (including all service packs) have limited display of Pin Numbers only.

The I/Os are controlled by the JTAG Boundary Scan register during programming, except for the analog pins (AC, AT and AV). The Boundary Scan register of the AG pin can be used to enable/disable the gate driver in software v9.0.

- Load a PDB from the FlashPro GUI. You must have a PDB loaded to modify the I/O states during programming.

- From the FlashPro GUI, click PDB Configuration. A FlashPoint Programming File Generator window appears.

- 3. Click the **Specify I/O States During Programming** button to display the Specify I/O States During Programming dialog box.

- 4. Sort the pins as desired by clicking any of the column headers to sort the entries by that header. Select the I/Os you wish to modify (Figure 1-3).

- 5. Set the I/O Output State. You can set Basic I/O settings if you want to use the default I/O settings for your pins, or use Custom I/O settings to customize the settings for each pin. Basic I/O state settings:

- 1 I/O is set to drive out logic High

- 0 I/O is set to drive out logic Low

Last Known State – I/O is set to the last value that was driven out prior to entering the programming mode, and then held at that value during programming

Z -Tri-State: I/O is tristated

Figure 1-3 • I/O States During Programming Window

6. Click **OK** to return to the FlashPoint – Programming File Generator window.

$\ensuremath{\mathsf{I/O}}$  States During programming are saved to the ADB and resulting programming files after completing programming file generation.

1-9 Revision 6

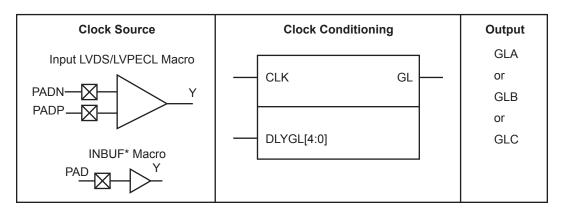

Figure 2-21 • Fusion CCC Options: Global Buffers with Programmable Delay

## **Global Input Selections**

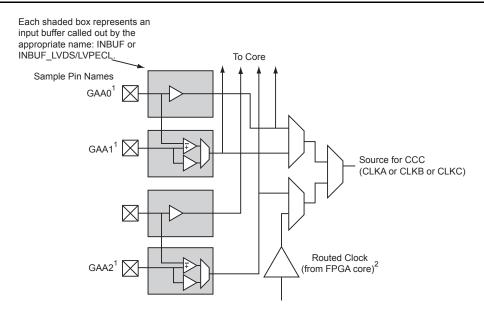

Each global buffer, as well as the PLL reference clock, can be driven from one of the following (Figure 2-22):

- 3 dedicated single-ended I/Os using a hardwired connection

- · 2 dedicated differential I/Os using a hardwired connection

- The FPGA core

GAA[0:2]: GA represents global in the northwest corner of the device. A[0:2]: designates specific A clock source.

#### Notes:

- 1. Represents the global input pins. Globals have direct access to the clock conditioning block and are not routed via the FPGA fabric. Refer to the "User I/O Naming Convention" section on page 2-158 for more information.

- 2. Instantiate the routed clock source input as follows:

- a) Connect the output of a logic element to the clock input of the PLL, CLKDLY, or CLKINT macro.

- b) Do not place a clock source I/O (INBUF or INBUF\_LVPECL/LVDS) in a relevant global pin location.

- 3. LVDS-based clock sources are available in the east and west banks on all Fusion devices.

Figure 2-22 • Clock Input Sources Including CLKBUF, CLKBUF\_LVDS/LVPECL, and CLKINT

2-25 Revision 6

#### PLL Macro

The PLL functionality of the clock conditioning block is supported by the PLL macro. Note that the PLL macro reference clock uses the CLKA input of the CCC block, which is only accessible from the global A[2:0] package pins. Refer to Figure 2-22 on page 2-25 for more information.

The PLL macro provides five derived clocks (three independent) from a single reference clock. The PLL feedback loop can be driven either internally or externally. The PLL macro also provides power-down input and lock output signals. During power-up, POWERDOWN should be asserted Low until VCC is up. See Figure 2-19 on page 2-23 for more information.

#### Inputs:

- · CLKA: selected clock input

- POWERDOWN (active low): disables PLLs. The default state is power-down on (active low).

#### Outputs:

- LOCK (active high): indicates that PLL output has locked on the input reference signal

- GLA, GLB, GLC: outputs to respective global networks

- · YB, YC: allows output from the CCC to be routed back to the FPGA core

As previously described, the PLL allows up to five flexible and independently configurable clock outputs. Figure 2-23 on page 2-26 illustrates the various clock output options and delay elements.

As illustrated, the PLL supports three distinct output frequencies from a given input clock. Two of these (GLB and GLC) can be routed to the B and C global networks, respectively, and/or routed to the device core (YB and YC).

There are five delay elements to support phase control on all five outputs (GLA, GLB, GLC, YB, and YC). There is also a delay element in the feedback loop that can be used to advance the clock relative to the reference clock.

The PLL macro reference clock can be driven by an INBUF macro to create a composite macro, where the I/O macro drives the global buffer (with programmable delay) using a hardwired connection. In this case, the I/O must be placed in one of the dedicated global I/O locations.

The PLL macro reference clock can be driven directly from the FPGA core.

The PLL macro reference clock can also be driven from an I/O routed through the FPGA regular routing fabric. In this case, users must instantiate a special macro, PLLINT, to differentiate it from the hardwired I/O connection described earlier.

The visual PLL configuration in SmartGen, available with the Libero SoC and Designer tools, will derive the necessary internal divider ratios based on the input frequency and desired output frequencies selected by the user. SmartGen allows the user to select the various delays and phase shift values necessary to adjust the phases between the reference clock (CLKA) and the derived clocks (GLA, GLB, GLC, YB, and YC). SmartGen also allows the user to select where the input clock is coming from. SmartGen automatically instantiates the special macro, PLLINT, when needed.

2-27 Revision 6

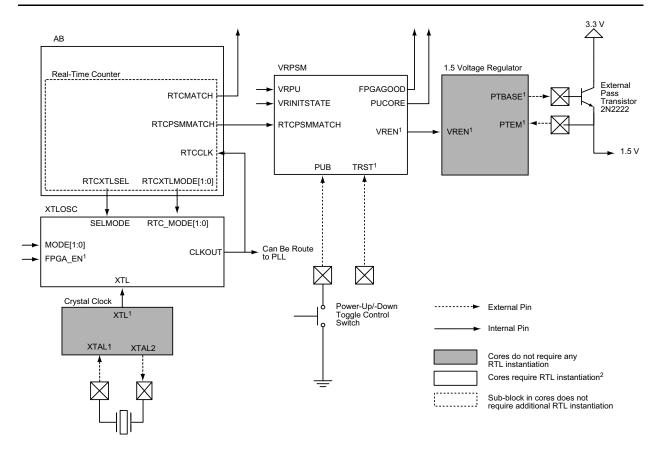

# **Real-Time Counter System**

The RTC system enables Fusion devices to support standby and sleep modes of operation to reduce power consumption in many applications.

- Sleep mode, typical 10 μA

- Standby mode (RTC running), typical 3 mA with 20 MHz

The RTC system is composed of five cores:

- RTC sub-block inside Analog Block (AB)

- Voltage Regulator and Power System Monitor (VRPSM)

- Crystal oscillator (XTLOSC); refer to the "Crystal Oscillator" section in the Fusion Clock Resources chapter of the Fusion FPGA Fabric User Guide for more detail.

- · Crystal clock; does not require instantiation in RTL

- · 1.5 V voltage regulator; does not require instantiation in RTL

All cores are powered by 3.3 V supplies, so the RTC system is operational without a 1.5 V supply during standby mode. Figure 2-27 shows their connection.

#### Notes:

- 1. Signals are hardwired internally and do not exist in the macro core.

- 2. User is only required to instantiate the VRPSM macro if the user wishes to specify PUPO behavior of the voltage regulator to be different from the default, or employ user logic to shut the voltage regulator off.

Figure 2-27 • Real-Time Counter System (not all the signals are shown for the AB macro)

2-31 Revision 6

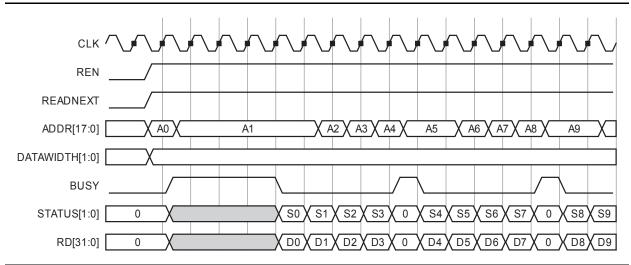

#### **Read Next Operation**

The Read Next operation is a feature by which the next block relative to the block in the Block Buffer is read from the FB Array while performing reads from the Block Buffer. The goal is to minimize wait states during consecutive sequential Read operations.

The Read Next operation is performed in a predetermined manner because it does look-ahead reads. The general look-ahead function is as follows:

- Within a page, the next block fetched will be the next in linear address.

- · When reading the last data block of a page, it will fetch the first block of the next page.

- When reading spare pages, it will read the first block of the next sector's spare page.

- · Reads of the last sector will wrap around to sector 0.

- Reads of Auxiliary blocks will read the next linear page's Auxiliary block.

When an address on the ADDR input does not agree with the predetermined look-ahead address, there is a time penalty for this access. The FB will be busy finishing the current look-ahead read before it can start the next read. The worst case is a total of nine BUSY cycles before data is delivered.

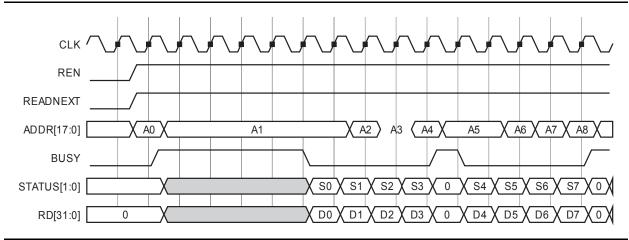

The Non-Pipe Mode and Pipe Mode waveforms for Read Next operations are illustrated in Figure 2-40 and Figure 2-41.

Figure 2-40 • Read Next Waveform (Non-Pipe Mode, 32-bit access)

Figure 2-41 • Read Next WaveForm (Pipe Mode, 32-bit access)

#### **Modes of Operation**

There are two read modes and one write mode:

- Read Nonpipelined (synchronous—1 clock edge): In the standard read mode, new data is driven

onto the RD bus in the same clock cycle following RA and REN valid. The read address is

registered on the read port clock active edge, and data appears at RD after the RAM access time.

Setting PIPE to OFF enables this mode.

- Read Pipelined (synchronous—2 clock edges): The pipelined mode incurs an additional clock delay from the address to the data but enables operation at a much higher frequency. The read address is registered on the read port active clock edge, and the read data is registered and appears at RD after the second read clock edge. Setting PIPE to ON enables this mode.

- Write (synchronous—1 clock edge): On the write clock active edge, the write data is written into

the SRAM at the write address when WEN is High. The setup times of the write address, write

enables, and write data are minimal with respect to the write clock. Write and read transfers are

described with timing requirements in the "SRAM Characteristics" section on page 2-63 and the

"FIFO Characteristics" section on page 2-72.

#### RAM Initialization

Each SRAM block can be individually initialized on power-up by means of the JTAG port using the UJTAG mechanism (refer to the "JTAG IEEE 1532" section on page 2-229 and the *Fusion SRAM/FIFO Blocks* application note). The shift register for a target block can be selected and loaded with the proper bit configuration to enable serial loading. The 4,608 bits of data can be loaded in a single operation.

Fusion Family of Mixed Signal FPGAs

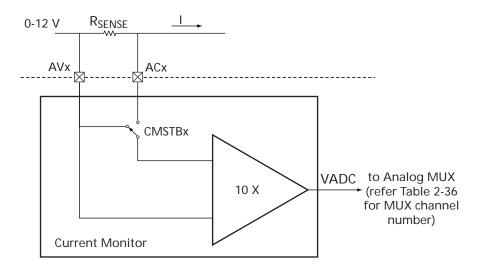

Table 2-36 describes each pin in the Analog Block. Each function within the Analog Block will be explained in detail in the following sections.

Table 2-36 • Analog Block Pin Description

| Signal Name      | Number of Bits                                                                                                                                                                                                                                                                                    | Direction    | Function                                                                                                                                                      | Location of<br>Details |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| VAREF            | 1                                                                                                                                                                                                                                                                                                 | Input/Output | Voltage reference for ADC                                                                                                                                     | ADC                    |

| ADCGNDREF        | 1                                                                                                                                                                                                                                                                                                 | Input        | External ground reference                                                                                                                                     | ADC                    |

| MODE[3:0]        | 4                                                                                                                                                                                                                                                                                                 | Input        | ADC operating mode                                                                                                                                            | ADC                    |

| SYSCLK           | 1                                                                                                                                                                                                                                                                                                 | Input        | External system clock                                                                                                                                         |                        |

| TVC[7:0]         | 8                                                                                                                                                                                                                                                                                                 | Input        | Clock divide control                                                                                                                                          | ADC                    |

| STC[7:0]         | 8                                                                                                                                                                                                                                                                                                 | Input        | Sample time control                                                                                                                                           | ADC                    |

| ADCSTART         | 1                                                                                                                                                                                                                                                                                                 | Input        | Start of conversion                                                                                                                                           | ADC                    |

| PWRDWN           | RDWN  1 Input ADC comparator power-down if 1. When asserted, the ADC will stop functioning, and the digital portion of the analog block will continue operating. This may result in invalid status flags from the analog block. Therefore, Microsemi does not recommend asserting the PWRDWN pin. |              |                                                                                                                                                               | ADC                    |

| ADCRESET         | 1                                                                                                                                                                                                                                                                                                 | Input        | ADC resets and disables Analog Quad – active high                                                                                                             | ADC                    |

| BUSY             | 1                                                                                                                                                                                                                                                                                                 | Output       | 1 – Running conversion                                                                                                                                        | ADC                    |

| CALIBRATE        | 1                                                                                                                                                                                                                                                                                                 | Output       | 1 – Power-up calibration                                                                                                                                      | ADC                    |

| DATAVALID        | 1                                                                                                                                                                                                                                                                                                 | Output       | 1 – Valid conversion result                                                                                                                                   | ADC                    |

| RESULT[11:0]     | 12                                                                                                                                                                                                                                                                                                | Output       | Conversion result                                                                                                                                             | ADC                    |

| TMSTBINT         | 1                                                                                                                                                                                                                                                                                                 | Input        | Internal temp. monitor strobe                                                                                                                                 | ADC                    |

| SAMPLE           | 1                                                                                                                                                                                                                                                                                                 | Output       | <ul> <li>1 – An analog signal is actively being sampled (stays high during signal acquisition only)</li> <li>0 – No analog signal is being sampled</li> </ul> | ADC                    |

| VAREFSEL         | 1                                                                                                                                                                                                                                                                                                 | Input        | 0 = Output internal voltage reference (2.56 V) to VAREF 1 = Input external voltage reference                                                                  | ADC                    |

|                  |                                                                                                                                                                                                                                                                                                   |              | from VAREF and ADCGNDREF                                                                                                                                      |                        |

| CHNUMBER[4:0]    | 5                                                                                                                                                                                                                                                                                                 | Input        | Analog input channel select                                                                                                                                   | Input<br>multiplexer   |

| ACMCLK           | 1                                                                                                                                                                                                                                                                                                 | Input        | ACM clock                                                                                                                                                     | ACM                    |

| ACMWEN           | 1                                                                                                                                                                                                                                                                                                 | Input        | ACM write enable – active high                                                                                                                                | ACM                    |

| ACMRESET         | 1                                                                                                                                                                                                                                                                                                 | Input        | ACM reset – active low                                                                                                                                        | ACM                    |

| ACMWDATA[7:0]    | 8                                                                                                                                                                                                                                                                                                 | Input        | ACM write data                                                                                                                                                | ACM                    |

| ACMRDATA[7:0]    | 8                                                                                                                                                                                                                                                                                                 | Output       | ACM read data                                                                                                                                                 | ACM                    |

| ACMADDR[7:0]     | 8                                                                                                                                                                                                                                                                                                 | Input        | ACM address                                                                                                                                                   | ACM                    |

| CMSTB0 to CMSTB9 | 10                                                                                                                                                                                                                                                                                                | Input        | Current monitor strobe – 1 per quad, active high                                                                                                              | Analog Quad            |

Figure 2-72 • Positive Current Monitor

Care must be taken when choosing the right resistor for current measurement application. Note that because of the  $10\times$  amplification, the maximum measurable difference between the AV and AC pads is  $V_{AREF}$  / 10. A larger AV-to-AC voltage drop will result in ADC saturation; that is, the digital code put out by the ADC will stay fixed at the full scale value. Therefore, the user must select the external sense resistor appropriately. Table 2-38 shows recommended resistor values for different current measurement ranges. When choosing resistor values for a system, there is a trade-off between measurement accuracy and power consumption. Choosing a large resistor will increase the voltage drop and hence increase accuracy of the measurement; however the larger voltage drop dissipates more power (P =  $1^2 \times R$ ).

The Current Monitor is a unipolar system, meaning that the differential voltage swing must be from 0 V to  $V_{AREF}/10$ . Therefore, the Current Monitor only supports differential voltage where  $|V_{AV}-V_{AC}|$  is greater than 0 V. This results in the requirement that the potential of the AV pad must be larger than the potential of the AC pad. This is straightforward for positive voltage systems. For a negative voltage system, it means that the AV pad must be "more negative" than the AC pad. This is shown in Figure 2-73.

In this case, both the AV pad and the AC pad are configured for negative operations and the output of the differential amplifier still falls between 0 V and  $V_{AREF}$  as required.

Table 2-37 • Recommended Resistor for Different Current Range Measurement

| Current Range     | Recommended Minimum Resistor Value (Ohms) |

|-------------------|-------------------------------------------|

| > 5 mA – 10 mA    | 10 – 20                                   |

| > 10 mA – 20 mA   | 5 – 10                                    |

| > 20 mA – 50 mA   | 2.5 – 5                                   |

| > 50 mA – 100 mA  | 1 – 2                                     |

| > 100 mA – 200 mA | 0.5 – 1                                   |

| > 200 mA – 500 mA | 0.3 – 0.5                                 |

| > 500 mA – 1 A    | 0.1 – 0.2                                 |

| > 1 A – 2 A       | 0.05 – 0.1                                |

| > 2 A – 4 A       | 0.025 – 0.05                              |

| > 4 A – 8 A       | 0.0125 – 0.025                            |

| > 8 A – 12 A      | 0.00625 – 0.02                            |

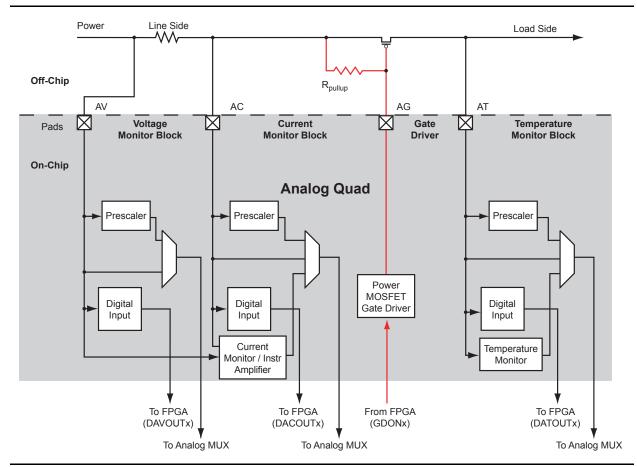

#### Gate Driver

The Fusion Analog Quad includes a Gate Driver connected to the Quad's AG pin (Figure 2-74). Designed to work with external p- or n-channel MOSFETs, the Gate driver is a configurable current sink or source and requires an external pull-up or pull-down resistor. The AG supports 4 selectable gate drive levels: 1  $\mu$ A, 3  $\mu$ A, 10  $\mu$ A, and 30  $\mu$ A (Figure 2-75 on page 2-91). The AG also supports a High Current Drive mode in which it can sink 20 mA; in this mode the switching rate is approximately 1.3 MHz with 100 ns turn-on time and 600 ns turn-off time. Modeled on an open-drain-style output, it does not output a voltage level without an appropriate pull-up or pull-down resistor. If 1 V is forced on the drain, the current sinking/sourcing will exceed the ability of the transistor, and the device could be damaged.

The AG pad is turned on via the corresponding GDONx pin in the Analog Block macro, where x is the number of the corresponding Analog Quad for the AG pad to be enabled (GDON0 to GDON9).

Figure 2-74 • Gate Driver

The gate-to-source voltage ( $V_{gs}$ ) of the external MOSFET is limited to the programmable drive current times the external pull-up or pull-down resistor value (EQ 5).

$$V_{as} \le I_a \times (R_{pullup} \text{ or } R_{pulldown})$$

EQ 5

Fusion Family of Mixed Signal FPGAs

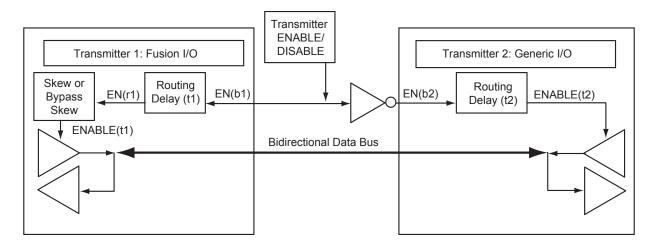

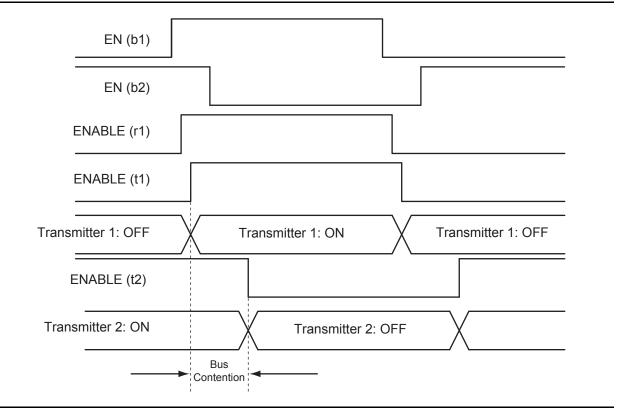

At the system level, the skew circuit can be used in applications where transmission activities on bidirectional data lines need to be coordinated. This circuit, when selected, provides a timing margin that can prevent bus contention and subsequent data loss or transmitter overstress due to transmitter-to-transmitter current shorts. Figure 2-110 presents an example of the skew circuit implementation in a bidirectional communication system. Figure 2-111 shows how bus contention is created, and Figure 2-112 on page 2-151 shows how it can be avoided with the skew circuit.

Figure 2-110 • Example of Implementation of Skew Circuits in Bidirectional Transmission Systems Using Fusion Devices

Figure 2-111 • Timing Diagram (bypasses skew circuit)

Table 2-78 • Fusion Standard I/O Standards—OUT\_DRIVE Settings

|                    | OUT_DRIVE (mA) |   |   |   |      |     |  |  |

|--------------------|----------------|---|---|---|------|-----|--|--|

| I/O Standards      | 2              | 4 | 6 | 8 | Slew |     |  |  |

| LVTTL/LVCMOS 3.3 V | 3              | 3 | 3 | 3 | High | Low |  |  |

| LVCMOS 2.5 V       | 3              | 3 | 3 | 3 | High | Low |  |  |

| LVCMOS 1.8 V       | 3              | 3 | - | - | High | Low |  |  |

| LVCMOS 1.5 V       | 3              | _ | _ | _ | High | Low |  |  |

## Table 2-79 • Fusion Advanced I/O Standards—SLEW and OUT\_DRIVE Settings

|                    |   | OUT_DRIVE (mA) |   |   |    |    |      |     |  |  |

|--------------------|---|----------------|---|---|----|----|------|-----|--|--|

| I/O Standards      | 2 | 4              | 6 | 8 | 12 | 16 | Slew |     |  |  |

| LVTTL/LVCMOS 3.3 V | 3 | 3              | 3 | 3 | 3  | 3  | High | Low |  |  |

| LVCMOS 2.5 V       | 3 | 3              | 3 | 3 | 3  | _  | High | Low |  |  |

| LVCMOS 1.8 V       | 3 | 3              | 3 | 3 | -  | _  | High | Low |  |  |

| LVCMOS 1.5 V       | 3 | 3              | - | - | -  | -  | High | Low |  |  |

Table 2-80 • Fusion Pro I/O Standards—SLEW and OUT\_DRIVE Settings

|                    |   | OUT_DRIVE (mA) |   |   |    |    |    |      |     |  |

|--------------------|---|----------------|---|---|----|----|----|------|-----|--|

| I/O Standards      | 2 | 4              | 6 | 8 | 12 | 16 | 24 | Slew |     |  |

| LVTTL/LVCMOS 3.3 V | 3 | 3              | 3 | 3 | 3  | 3  | 3  | High | Low |  |

| LVCMOS 2.5 V       | 3 | 3              | 3 | 3 | 3  | 3  | 3  | High | Low |  |

| LVCMOS 2.5 V/5.0 V | 3 | 3              | 3 | 3 | 3  | 3  | 3  | High | Low |  |

| LVCMOS 1.8 V       | 3 | 3              | 3 | 3 | 3  | 3  | _  | High | Low |  |

| LVCMOS 1.5 V       | 3 | 3              | 3 | 3 | 3  | _  | _  | High | Low |  |

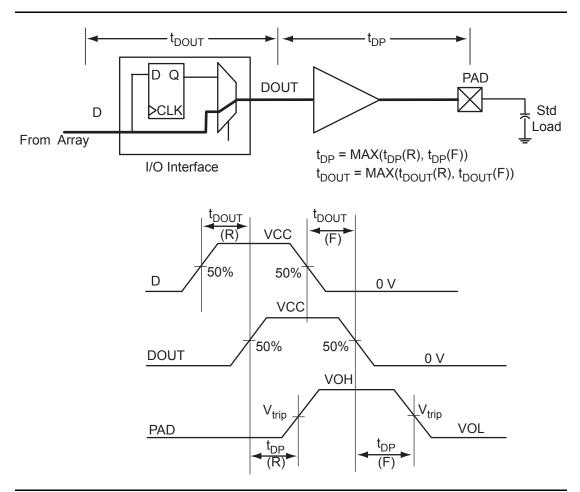

Figure 2-117 • Output Buffer Model and Delays (example)

Table 2-98 • I/O Short Currents IOSH/IOSL

|                                  | Drive Strength | IOSH (mA)* | IOSL (mA)* |

|----------------------------------|----------------|------------|------------|

| Applicable to Pro I/O Banks      | ·              |            |            |

| 3.3 V LVTTL / 3.3 V LVCMOS       | 4 mA           | 25         | 27         |

|                                  | 8 mA           | 51         | 54         |

|                                  | 12 mA          | 103        | 109        |

|                                  | 16 mA          | 132        | 127        |

|                                  | 24 mA          | 268        | 181        |

| 2.5 V LVCMOS                     | 4 mA           | 16         | 18         |

|                                  | 8 mA           | 32         | 37         |

|                                  | 12 mA          | 65         | 74         |

|                                  | 16 mA          | 83         | 87         |

|                                  | 24 mA          | 169        | 124        |

| 1.8 V LVCMOS                     | 2 mA           | 9          | 11         |

|                                  | 4 mA           | 17         | 22         |

|                                  | 6 mA           | 35         | 44         |

|                                  | 8 mA           | 45         | 51         |

|                                  | 12 mA          | 91         | 74         |

|                                  | 16 mA          | 91         | 74         |

| 1.5 V LVCMOS                     | 2 mA           | 13         | 16         |

|                                  | 4 mA           | 25         | 33         |

|                                  | 6 mA           | 32         | 39         |

|                                  | 8 mA           | 66         | 55         |

|                                  | 12 mA          | 66         | 55         |

| Applicable to Advanced I/O Banks | <b>3</b>       |            |            |

| 3.3 V LVTTL / 3.3 V LVCMOS       | 2 mA           | 25         | 27         |

|                                  | 4 mA           | 25         | 27         |

|                                  | 6 mA           | 51         | 54         |

|                                  | 8 mA           | 51         | 54         |

|                                  | 12 mA          | 103        | 109        |

|                                  | 16 mA          | 132        | 127        |

|                                  | 24 mA          | 268        | 181        |

| 3.3 V LVCMOS                     | 2 mA           | 25         | 27         |

|                                  | 4 mA           | 25         | 27         |

|                                  | 6 mA           | 51         | 54         |

|                                  | 8 mA           | 51         | 54         |

|                                  | 12 mA          | 103        | 109        |

|                                  | 16 mA          | 132        | 127        |

|                                  | 24 mA          | 268        | 181        |

Note:  $*T_J = 100^{\circ}C$

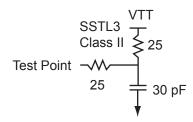

#### SSTL3 Class II

Stub-Speed Terminated Logic for 3.3 V memory bus standard (JESD8-8). Fusion devices support Class II. This provides a differential amplifier input buffer and a push-pull output buffer.

Table 2-165 • Minimum and Maximum DC Input and Output Levels

| SSTL3 Class II |           | VIL        | VIH        |           | VOL       | VOH        | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|----------------|-----------|------------|------------|-----------|-----------|------------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V  | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 21 mA          | -0.3      | VREF – 0.2 | VREF + 0.2 | 3.6       | 0.5       | VCCI - 0.9 | 21  | 21 | 109                     | 103                     | 10                      | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

Figure 2-133 • AC Loading

Table 2-166 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF - 0.2    | VREF + 0.2     | 1.5                  | 1.5             | 1.485          | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### **Timing Characteristics**

Table 2-167 • SSTL3- Class II

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V, VREF = 1.5 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.07            | 0.04             | 1.25            | 0.43              | 2.10            | 1.67            |                 |                 | 4.34             | 3.91             | ns    |

| <b>-1</b>      | 0.56              | 1.76            | 0.04             | 1.06            | 0.36              | 1.79            | 1.42            |                 |                 | 3.69             | 3.32             | ns    |

| -2             | 0.49              | 1.54            | 0.03             | 0.93            | 0.32              | 1.57            | 1.25            |                 |                 | 3.24             | 2.92             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

Fusion Family of Mixed Signal FPGAs

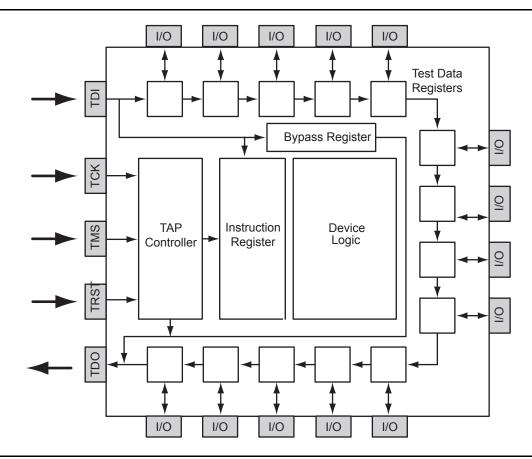

connected to the internal core logic I/O tile and the input, output, and control ports of an I/O buffer to capture and load data into the register to control or observe the logic state of each I/O.

Figure 2-146 • Boundary Scan Chain in Fusion

## Table 2-185 • Boundary Scan Opcodes

|                | Hex Opcode |

|----------------|------------|

| EXTEST         | 00         |

| HIGHZ          | 07         |

| USERCODE       | 0E         |

| SAMPLE/PRELOAD | 01         |

| IDCODE         | 0F         |

| CLAMP          | 05         |

| BYPASS         | FF         |

# 3 - DC and Power Characteristics

# **General Specifications**

## **Operating Conditions**

Stresses beyond those listed in Table 3-1 may cause permanent damage to the device.

Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Devices should not be operated outside the recommended operating ranges specified in Table 3-2 on page 3-3.

Table 3-1 • Absolute Maximum Ratings

| Symbol   | Parameter                                  | Commercial                                                                                                                                                                                  | Industrial                | Units |

|----------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------|

| VCC      | DC core supply voltage                     | -0.3 to 1.65                                                                                                                                                                                | -0.3 to 1.65              | V     |

| VJTAG    | JTAG DC voltage                            | -0.3 to 3.75                                                                                                                                                                                | -0.3 to 3.75              | V     |

| VPUMP    | Programming voltage                        | -0.3 to 3.75                                                                                                                                                                                | -0.3 to 3.75              | V     |

| VCCPLL   | Analog power supply (PLL)                  | -0.3 to 1.65                                                                                                                                                                                | -0.3 to 1.65              | V     |

| VCCI     | DC I/O output buffer supply voltage        | -0.3 to 3.75                                                                                                                                                                                | -0.3 to 3.75              | V     |

| VI       | I/O input voltage <sup>1</sup>             | <ul> <li>-0.3 V to 3.6 V (when I/O hot insertion mode is enabled)</li> <li>-0.3 V to (VCCI + 1 V) or 3.6 V, whichever voltage is lower (when I/O hot-insertion mode is disabled)</li> </ul> |                           |       |

| VCC33A   | +3.3 V power supply                        | -0.3 to 3.75 <sup>2</sup>                                                                                                                                                                   | -0.3 to 3.75 <sup>2</sup> | V     |

| VCC33PMP | +3.3 V power supply                        | -0.3 to 3.75 <sup>2</sup>                                                                                                                                                                   | -0.3 to 3.75 <sup>2</sup> | V     |

| VAREF    | Voltage reference for ADC                  | -0.3 to 3.75                                                                                                                                                                                | -0.3 to 3.75              | V     |

| VCC15A   | Digital power supply for the analog system | -0.3 to 1.65                                                                                                                                                                                | -0.3 to 1.65              | V     |

| VCCNVM   | Embedded flash power supply                | -0.3 to 1.65                                                                                                                                                                                | -0.3 to 1.65              | V     |

| vccosc   | Oscillator power supply                    | -0.3 to 3.75                                                                                                                                                                                | -0.3 to 3.75              | V     |

#### Notes:

<sup>1.</sup> The device should be operated within the limits specified by the datasheet. During transitions, the input signal may undershoot or overshoot according to the limits shown in Table 3-4 on page 3-4.

<sup>2.</sup> Analog data not valid beyond 3.65 V.

<sup>3.</sup> The high current mode has a maximum power limit of 20 mW. Appropriate current limit resistors must be used, based on voltage on the pad.

<sup>4.</sup> For flash programming and retention maximum limits, refer to Table 3-5 on page 3-5. For recommended operating limits refer to Table 3-2 on page 3-3.

Table 3-11 • AFS090 Quiescent Supply Current Characteristics (continued)

| Parameter | Description                 | Conditions                          | Temp.                  | Min | Тур | Max | Unit |

|-----------|-----------------------------|-------------------------------------|------------------------|-----|-----|-----|------|

| ICCNVM    |                             | Reset asserted,<br>VCCNVM = 1.575 V | T <sub>J</sub> = 25°C  |     | 10  | 40  | μΑ   |

|           |                             |                                     | T <sub>J</sub> = 85°C  |     | 14  | 40  | μΑ   |

|           |                             |                                     | T <sub>J</sub> = 100°C |     | 14  | 40  | μΑ   |

| ICCPLL    | 1.5 V PLL quiescent current | VCCPLL = 1.575 V                    | T <sub>J</sub> = 25°C  |     | 65  | 100 | μΑ   |

|           |                             |                                     | T <sub>J</sub> = 85°C  |     | 65  | 100 | μΑ   |

|           |                             |                                     | T <sub>J</sub> = 100°C |     | 65  | 100 | μA   |

#### Notes:

- 1. ICC is the 1.5 V power supplies, ICC, ICCPLL, ICC15A, ICCNVM.

- 2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

- 3. ICCI includes all ICCI0, ICCI1, and ICCI2.

- 4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

- 5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

- 6. Sleep Mode, VCC = VJTAG = VPUMP = 0 V.

3-17 Revision 6

Fusion Family of Mixed Signal FPGAs

| FG676                       |                 |  |  |  |

|-----------------------------|-----------------|--|--|--|

| Pin Number AFS1500 Function |                 |  |  |  |

| G13                         | IO22NDB1V0      |  |  |  |

| G14                         | IO22PDB1V0      |  |  |  |

| G15                         | GND             |  |  |  |

| G16                         | IO32PPB1V1      |  |  |  |

| G17                         | IO36NPB1V2      |  |  |  |

| G18                         | VCCIB1          |  |  |  |

| G19                         | GND             |  |  |  |

| G20                         | IO47NPB2V0      |  |  |  |

| G21                         | IO49PDB2V0      |  |  |  |

| G22                         | VCCIB2          |  |  |  |

| G23                         | IO46NDB2V0      |  |  |  |

| G24                         | GBC2/IO46PDB2V0 |  |  |  |

| G25                         | IO48NPB2V0      |  |  |  |

| G26                         | NC              |  |  |  |

| H1                          | GND             |  |  |  |

| H2                          | NC              |  |  |  |

| НЗ                          | IO118NDB4V0     |  |  |  |

| H4                          | IO118PDB4V0     |  |  |  |

| H5                          | IO119NPB4V0     |  |  |  |

| H6                          | IO124NDB4V0     |  |  |  |

| H7                          | GND             |  |  |  |

| H8                          | VCOMPLA         |  |  |  |

| H9                          | VCCPLA          |  |  |  |

| H10                         | VCCIB0          |  |  |  |

| H11                         | IO12NDB0V1      |  |  |  |

| H12                         | IO12PDB0V1      |  |  |  |

| H13                         | VCCIB0          |  |  |  |

| H14                         | VCCIB1          |  |  |  |

| H15                         | IO30NDB1V1      |  |  |  |

| H16                         | IO30PDB1V1      |  |  |  |

| H17                         | VCCIB1          |  |  |  |

| H18                         | IO36PPB1V2      |  |  |  |

| H19                         | IO38NPB1V2      |  |  |  |

| H20                         | GND             |  |  |  |

| H21                         | IO49NDB2V0      |  |  |  |

| H22                         | IO50PDB2V0      |  |  |  |

| FG676      |                  |  |  |  |

|------------|------------------|--|--|--|

| Pin Number | AFS1500 Function |  |  |  |

| H23        | IO50NDB2V0       |  |  |  |

| H24        | IO51PDB2V0       |  |  |  |

| H25        | NC               |  |  |  |

| H26        | GND              |  |  |  |

| J1         | NC               |  |  |  |

| J2         | VCCIB4           |  |  |  |

| J3         | IO115PDB4V0      |  |  |  |

| J4         | GND              |  |  |  |

| J5         | IO116NDB4V0      |  |  |  |

| J6         | IO116PDB4V0      |  |  |  |

| J7         | VCCIB4           |  |  |  |

| J8         | IO117PDB4V0      |  |  |  |

| J9         | VCCIB4           |  |  |  |

| J10        | GND              |  |  |  |

| J11        | IO06NDB0V1       |  |  |  |

| J12        | IO06PDB0V1       |  |  |  |

| J13        | IO16NDB0V2       |  |  |  |

| J14        | IO16PDB0V2       |  |  |  |

| J15        | IO28NDB1V1       |  |  |  |

| J16        | IO28PDB1V1       |  |  |  |

| J17        | GND              |  |  |  |

| J18        | IO38PPB1V2       |  |  |  |

| J19        | IO53PDB2V0       |  |  |  |

| J20        | VCCIB2           |  |  |  |

| J21        | IO52PDB2V0       |  |  |  |

| J22        | IO52NDB2V0       |  |  |  |

| J23        | GND              |  |  |  |

| J24        | IO51NDB2V0       |  |  |  |

| J25        | VCCIB2           |  |  |  |

| J26        | NC               |  |  |  |

| K1         | NC               |  |  |  |

| K2         | NC               |  |  |  |

| K3         | IO115NDB4V0      |  |  |  |

| K4         | IO113PDB4V0      |  |  |  |

| K5         | VCCIB4           |  |  |  |

| K6         | IO114NDB4V0      |  |  |  |

| FG676                       |                  |  |  |  |

|-----------------------------|------------------|--|--|--|

| Pin Number AFS1500 Function |                  |  |  |  |

|                             |                  |  |  |  |

| K7                          | IO114PDB4V0      |  |  |  |

| K8                          | IO117NDB4V0      |  |  |  |

| K9                          | GND              |  |  |  |

| K10                         | VCC              |  |  |  |

| K11                         | VCCIB0           |  |  |  |

| K12                         | GND              |  |  |  |

| K13                         | VCCIB0           |  |  |  |

| K14                         | VCCIB1           |  |  |  |

| K15                         | GND              |  |  |  |

| K16                         | VCCIB1           |  |  |  |

| K17                         | GND              |  |  |  |

| K18                         | GND              |  |  |  |

| K19                         | IO53NDB2V0       |  |  |  |

| K20                         | IO57PDB2V0       |  |  |  |

| K21                         | GCA2/IO59PDB2V0  |  |  |  |

| K22                         | VCCIB2           |  |  |  |

| K23                         | IO54NDB2V0       |  |  |  |

| K24                         | IO54PDB2V0       |  |  |  |

| K25                         | NC               |  |  |  |

| K26                         | NC               |  |  |  |

| L1                          | GND              |  |  |  |

| L2                          | NC               |  |  |  |

| L3                          | IO112PPB4V0      |  |  |  |

| L4                          | IO113NDB4V0      |  |  |  |

| L5                          | GFB2/IO109PDB4V0 |  |  |  |

| L6                          | GFA2/IO110PDB4V0 |  |  |  |

| L7                          | IO112NPB4V0      |  |  |  |

| L8                          | IO104PDB4V0      |  |  |  |

| L9                          | IO111PDB4V0      |  |  |  |

| L10                         | VCCIB4           |  |  |  |

| L11                         | GND              |  |  |  |

| L12                         | VCC              |  |  |  |

| L13                         | GND              |  |  |  |

| L14                         | VCC              |  |  |  |

| L15                         | GND              |  |  |  |

| L16                         | VCC              |  |  |  |

## Datasheet Information

| Revision                       | Changes                                                                                                                                                                                                                                                           | Page       |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Advance v1.0 (continued)       | This change table states that in the "208-Pin PQFP" table listed under the Advance v0.8 changes, the AFS090 device had a pin change. That is incorrect. Pin 102 was updated for AFS250 and AFS600. The function name changed from $V_{CC33ACAP}$ to $V_{CC33A}$ . | 3-8        |

| Advance v0.9<br>(October 2007) | In the "Package I/Os: Single-/Double-Ended (Analog)" table, the AFS1500/M7AFS1500 I/O counts were updated for the following devices: FG484: 223/109 FG676: 252/126                                                                                                | II         |

|                                | In the "108-Pin QFN" table, the function changed from $V_{CC33ACAP}$ to $V_{CC33A}$ for the following pin: B25                                                                                                                                                    | 3-2        |

|                                | In the "180-Pin QFN" table, the function changed from $V_{CC33ACAP}$ to $V_{CC33A}$ for the following pins: AFS090: B29 AFS250: B29                                                                                                                               | 3-4        |

|                                | In the "208-Pin PQFP" table, the function changed from $V_{CC33ACAP}$ to $V_{CC33A}$ for the following pins: AFS090: 102 AFS250: 102                                                                                                                              | 3-8        |

|                                | In the "256-Pin FBGA" table, the function changed from V <sub>CC33ACAP</sub> to V <sub>CC33A</sub> for the following pins:  AFS090: T14  AFS250: T14  AFS600: T14  AFS1500: T14                                                                                   | 3-12       |

| Advance v0.9 (continued)       | In the "484-Pin FBGA" table, the function changed from V <sub>CC33ACAP</sub> to V <sub>CC33A</sub> for the following pins:  AFS600: AB18  AFS1500: AB18                                                                                                           | 3-20       |

|                                | In the "676-Pin FBGA" table, the function changed from $V_{CC33ACAP}$ to $V_{CC33A}$ for the following pins: AFS1500: AD20                                                                                                                                        | 3-28       |

| Advance v0.8<br>(June 2007)    | Figure 2-16 • Fusion Clocking Options and the "RC Oscillator" section were updated to change GND_OSC and VCC_OSC to GNDOSC and VCCOSC.                                                                                                                            | 2-20, 2-21 |

|                                | Figure 2-19 • Fusion CCC Options: Global Buffers with the PLL Macro was updated to change the positions of OADIVRST and OADIVHALF, and a note was added.                                                                                                          | 2-25       |

|                                | The "Crystal Oscillator" section was updated to include information about controlling and enabling/disabling the crystal oscillator.                                                                                                                              | 2-22       |

|                                | Table 2-11 · Electrical Characteristics of the Crystal Oscillator was updated to change the typical value of I <sub>DYNXTAL</sub> for 0.032–0.2 MHz to 0.19.                                                                                                      | 2-24       |

|                                | The "1.5 V Voltage Regulator" section was updated to add "or floating" in the paragraph stating that an external pull-down is required on TRST to power down the VR.                                                                                              | 2-41       |

|                                | The "1.5 V Voltage Regulator" section was updated to include information on powering down with the VR.                                                                                                                                                            | 2-41       |

5-11 Revision 6