Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Active                                                                      |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | -                                                                           |

| Total RAM Bits                 | 276480                                                                      |

| Number of I/O                  | 252                                                                         |

| Number of Gates                | 1500000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 676-BGA                                                                     |

| Supplier Device Package        | 676-FBGA (27x27)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1afs1500-1fg676i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Fusion Device Family Overview

#### Instant On

Flash-based Fusion devices are Level 0 Instant On. Instant On Fusion devices greatly simplify total system design and reduce total system cost by eliminating the need for CPLDs. The Fusion Instant On clocking (PLLs) replaces off-chip clocking resources. The Fusion mix of Instant On clocking and analog resources makes these devices an excellent choice for both system supervisor and system management functions. Instant On from a single 3.3 V source enables Fusion devices to initiate, control, and monitor multiple voltage supplies while also providing system clocks. In addition, glitches and brownouts in system power will not corrupt the Fusion device flash configuration. Unlike SRAM-based FPGAs, the device will not have to be reloaded when system power is restored. This enables reduction or complete removal of expensive voltage monitor and brownout detection devices from the PCB design.

Flash-based Fusion devices simplify total system design and reduce cost and design risk, while increasing system reliability.

#### Firm Errors

Firm errors occur most commonly when high-energy neutrons, generated in the upper atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O behavior in an unpredictable way. Another source of radiation-induced firm errors is alpha particles. For an alpha to cause a soft or firm error, its source must be in very close proximity to the affected circuit. The alpha source must be in the package molding compound or in the die itself. While low-alpha molding compounds are being used increasingly, this helps reduce but does not entirely eliminate alpha-induced firm errors.

Firm errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not occur in Fusion flash-based FPGAs. Once it is programmed, the flash cell configuration element of Fusion FPGAs cannot be altered by high-energy neutrons and is therefore immune to errors from them.

Recoverable (or soft) errors occur in the user data SRAMs of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

#### Low Power

Flash-based Fusion devices exhibit power characteristics similar to those of an ASIC, making them an ideal choice for power-sensitive applications. With Fusion devices, there is no power-on current surge and no high current transition, both of which occur on many FPGAs.

Fusion devices also have low dynamic power consumption and support both low power standby mode and very low power sleep mode, offering further power savings.

# **Advanced Flash Technology**

The Fusion family offers many benefits, including nonvolatility and reprogrammability through an advanced flash-based, 130-nm LVCMOS process with seven layers of metal. Standard CMOS design techniques are used to implement logic and control functions. The combination of fine granularity, enhanced flexible routing resources, and abundant flash switches allows very high logic utilization (much higher than competing SRAM technologies) without compromising device routability or performance. Logic functions within the device are interconnected through a four-level routing hierarchy.

1-3 Revision 6

#### Global Clocking

Fusion devices have extensive support for multiple clocking domains. In addition to the CCC and PLL support described above, there are on-chip oscillators as well as a comprehensive global clock distribution network.

The integrated RC oscillator generates a 100 MHz clock. It is used internally to provide a known clock source to the flash memory read and write control. It can also be used as a source for the PLLs.

The crystal oscillator supports the following operating modes:

- Crystal (32.768 KHz to 20 MHz)

- · Ceramic (500 KHz to 8 MHz)

- RC (32.768 KHz to 4 MHz)

Each VersaTile input and output port has access to nine VersaNets: six main and three quadrant global networks. The VersaNets can be driven by the CCC or directly accessed from the core via MUXes. The VersaNets can be used to distribute low-skew clock signals or for rapid distribution of high-fanout nets.

# Digital I/Os with Advanced I/O Standards

The Fusion family of FPGAs features a flexible digital I/O structure, supporting a range of voltages (1.5 V, 1.8 V, 2.5 V, and 3.3 V). Fusion FPGAs support many different digital I/O standards, both single-ended and differential.

The I/Os are organized into banks, with four or five banks per device. The configuration of these banks determines the I/O standards supported. The banks along the east and west sides of the device support the full range of I/O standards (single-ended and differential). The south bank supports the Analog Quads (analog I/O). In the family's two smaller devices, the north bank supports multiple single-ended digital I/O standards. In the family's larger devices, the north bank is divided into two banks of digital Pro I/Os, supporting a wide variety of single-ended, differential, and voltage-referenced I/O standards.

Each I/O module contains several input, output, and enable registers. These registers allow the implementation of the following applications:

- · Single-Data-Rate (SDR) applications

- Double-Data-Rate (DDR) applications—DDR LVDS I/O for chip-to-chip communications

- Fusion banks support LVPECL, LVDS, BLVDS, and M-LVDS with 20 multi-drop points.

#### **VersaTiles**

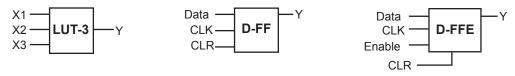

The Fusion core consists of VersaTiles, which are also used in the successful ProASIC3 family. The Fusion VersaTile supports the following:

- · All 3-input logic functions—LUT-3 equivalent

- · Latch with clear or set

- D-flip-flop with clear or set and optional enable

Refer to Figure 1-2 for the VersaTile configuration arrangement.

# LUT-3 Equivalent D-Flip-Flop with Clear or Set Enable D-Flip-Flop with Clear or Set

Figure 1-2 • VersaTile Configurations

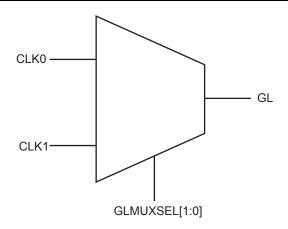

The NGMUX macro is simplified to show the two clock options that have been selected by the GLMUXCFG[1:0] bits. Figure 2-25 illustrates the NGMUX macro. During design, the two clock sources are connected to CLK0 and CLK1 and are controlled by GLMUXSEL[1:0] to determine which signal is to be passed through the MUX.

Figure 2-25 • NGMUX Macro

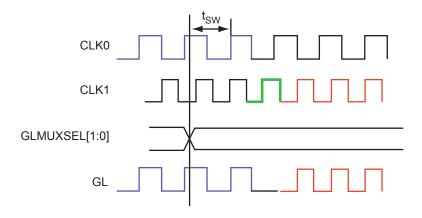

The sequence of switching between two clock sources (from CLK0 to CLK1) is as follows (Figure 2-26):

- GLMUXSEL[1:0] transitions to initiate a switch.

- GL drives one last complete CLK0 positive pulse (i.e., one rising edge followed by one falling edge).

- · From that point, GL stays Low until the second rising edge of CLK1 occurs.

- At the second CLK1 rising edge, GL will begin to continuously deliver the CLK1 signal.

- Minimum t<sub>sw</sub> = 0.05 ns at 25°C (typical conditions)

For examples of NGMUX operation, refer to the Fusion FPGA Fabric User Guide.

Figure 2-26 • NGMUX Waveform

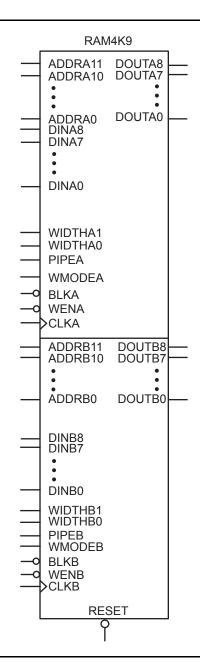

# **RAM4K9 Description**

Figure 2-48 • RAM4K9

2-57 Revision 6

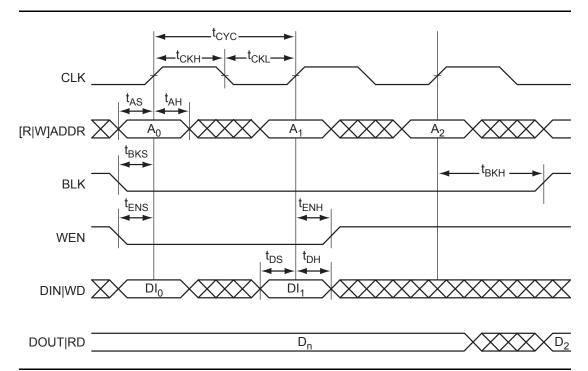

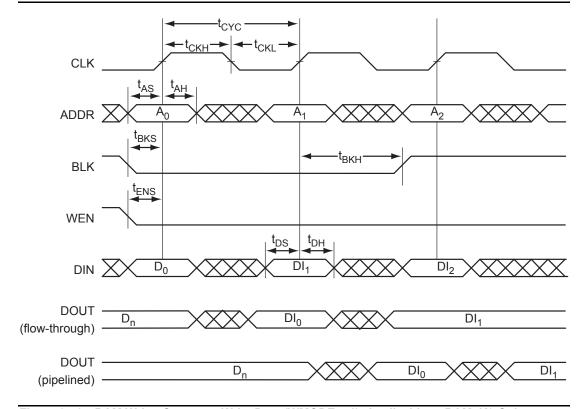

Figure 2-52 • RAM Write, Output Retained. Applicable to both RAM4K9 and RAM512x18.

Figure 2-53 • RAM Write, Output as Write Data (WMODE = 1). Applicable to RAM4K9 Only.

The following signals are used to configure the FIFO4K18 memory element.

#### WW and RW

These signals enable the FIFO to be configured in one of the five allowable aspect ratios (Table 2-33).

Table 2-33 • Aspect Ratio Settings for WW[2:0]

| WW2, WW1, WW0 | RW2, RW1, RW0 | D×W      |

|---------------|---------------|----------|

| 000           | 000           | 4k×1     |

| 001           | 001           | 2k×2     |

| 010           | 010           | 1k×4     |

| 011           | 011           | 512×9    |

| 100           | 100           | 256×18   |

| 101, 110, 111 | 101, 110, 111 | Reserved |

#### WBLK and RBLK

These signals are active low and will enable the respective ports when Low. When the RBLK signal is High, the corresponding port's outputs hold the previous value.

#### **WEN** and **REN**

Read and write enables. WEN is active low and REN is active high by default. These signals can be configured as active high or low.

#### WCLK and RCLK

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

#### **RPIPE**

This signal is used to specify pipelined read on the output. A Low on RPIPE indicates a nonpipelined read, and the data appears on the output in the same clock cycle. A High indicates a pipelined read, and data appears on the output in the next clock cycle.

#### RESET

This active low signal resets the output to zero when asserted. It resets the FIFO counters. It also sets all the RD pins Low, the FULL and AFULL pins Low, and the EMPTY and AEMPTY pins High (Table 2-34).

Table 2-34 • Input Data Signal Usage for Different Aspect Ratios

| D×W    | WD/RD Unused       |

|--------|--------------------|

| 4k×1   | WD[17:1], RD[17:1] |

| 2k×2   | WD[17:2], RD[17:2] |

| 1k×4   | WD[17:4], RD[17:4] |

| 512×9  | WD[17:9], RD[17:9] |

| 256×18 | -                  |

#### WD

This is the input data bus and is 18 bits wide. Not all 18 bits are valid in all configurations. When a data width less than 18 is specified, unused higher-order signals must be grounded (Table 2-34).

#### RD

This is the output data bus and is 18 bits wide. Not all 18 bits are valid in all configurations. Like the WD bus, high-order bits become unusable if the data width is less than 18. The output data on unused pins is undefined (Table 2-34).

2-69 Revision 6

#### ESTOP, FSTOP

ESTOP is used to stop the FIFO read counter from further counting once the FIFO is empty (i.e., the EMPTY flag goes High). A High on this signal inhibits the counting.

FSTOP is used to stop the FIFO write counter from further counting once the FIFO is full (i.e., the FULL flag goes High). A High on this signal inhibits the counting.

For more information on these signals, refer to the "ESTOP and FSTOP Usage" section on page 2-70.

#### **FULL, EMPTY**

When the FIFO is full and no more data can be written, the FULL flag asserts High. The FULL flag is synchronous to WCLK to inhibit writing immediately upon detection of a full condition and to prevent overflows. Since the write address is compared to a resynchronized (and thus time-delayed) version of the read address, the FULL flag will remain asserted until two WCLK active edges after a read operation eliminates the full condition.

When the FIFO is empty and no more data can be read, the EMPTY flag asserts High. The EMPTY flag is synchronous to RCLK to inhibit reading immediately upon detection of an empty condition and to prevent underflows. Since the read address is compared to a resynchronized (and thus time-delayed) version of the write address, the EMPTY flag will remain asserted until two RCLK active edges after a write operation removes the empty condition.

For more information on these signals, refer to the "FIFO Flag Usage Considerations" section on page 2-70.

#### AFULL, AEMPTY

These are programmable flags and will be asserted on the threshold specified by AFVAL and AEVAL, respectively.

When the number of words stored in the FIFO reaches the amount specified by AEVAL while reading, the AEMPTY output will go High. Likewise, when the number of words stored in the FIFO reaches the amount specified by AFVAL while writing, the AFULL output will go High.

#### AFVAL, AEVAL

The AEVAL and AFVAL pins are used to specify the almost-empty and almost-full threshold values, respectively. They are 12-bit signals. For more information on these signals, refer to "FIFO Flag Usage Considerations" section.

## ESTOP and FSTOP Usage

The ESTOP pin is used to stop the read counter from counting any further once the FIFO is empty (i.e., the EMPTY flag goes High). Likewise, the FSTOP pin is used to stop the write counter from counting any further once the FIFO is full (i.e., the FULL flag goes High).

The FIFO counters in the Fusion device start the count at 0, reach the maximum depth for the configuration (e.g., 511 for a 512×9 configuration), and then restart at 0. An example application for the ESTOP, where the read counter keeps counting, would be writing to the FIFO once and reading the same content over and over without doing another write.

#### FIFO Flag Usage Considerations

The AEVAL and AFVAL pins are used to specify the 12-bit AEMPTY and AFULL threshold values, respectively. The FIFO contains separate 12-bit write address (WADDR) and read address (RADDR) counters. WADDR is incremented every time a write operation is performed, and RADDR is incremented every time a read operation is performed. Whenever the difference between WADDR and RADDR is greater than or equal to AFVAL, the AFULL output is asserted. Likewise, whenever the difference between WADDR and RADDR is less than or equal to AEVAL, the AEMPTY output is asserted. To handle different read and write aspect ratios, AFVAL and AEVAL are expressed in terms of total data bits instead of total data words. When users specify AFVAL and AEVAL in terms of read or write words, the SmartGen tool translates them into bit addresses and configures these signals automatically. SmartGen configures the AFULL flag to assert when the write address exceeds the read address by at least a predefined value. In a 2k×8 FIFO, for example, a value of 1,500 for AFVAL means that the AFULL flag will be asserted after a write when the difference between the write address and the read address reaches 1,500 (there have been at least 1500 more writes than reads). It will stay asserted until the difference between the write and read addresses drops below 1,500.

Fusion Family of Mixed Signal FPGAs

Table 2-36 describes each pin in the Analog Block. Each function within the Analog Block will be explained in detail in the following sections.

Table 2-36 • Analog Block Pin Description

| Signal Name      | Number of Bits | Direction    | Function                                                                                                                                                                                                                                                                            | Location of<br>Details |

|------------------|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| VAREF            | 1              | Input/Output | Voltage reference for ADC                                                                                                                                                                                                                                                           | ADC                    |

| ADCGNDREF        | 1              | Input        | External ground reference                                                                                                                                                                                                                                                           | ADC                    |

| MODE[3:0]        | 4              | Input        | ADC operating mode                                                                                                                                                                                                                                                                  | ADC                    |

| SYSCLK           | 1              | Input        | External system clock                                                                                                                                                                                                                                                               |                        |

| TVC[7:0]         | 8              | Input        | Clock divide control                                                                                                                                                                                                                                                                | ADC                    |

| STC[7:0]         | 8              | Input        | Sample time control                                                                                                                                                                                                                                                                 | ADC                    |

| ADCSTART         | 1              | Input        | Start of conversion                                                                                                                                                                                                                                                                 | ADC                    |

| PWRDWN           | 1              | Input        | ADC comparator power-down if 1. When asserted, the ADC will stop functioning, and the digital portion of the analog block will continue operating. This may result in invalid status flags from the analog block. Therefore, Microsemi does not recommend asserting the PWRDWN pin. | ADC                    |

| ADCRESET         | 1              | Input        | ADC resets and disables Analog Quad – active high                                                                                                                                                                                                                                   | ADC                    |

| BUSY             | 1              | Output       | 1 – Running conversion                                                                                                                                                                                                                                                              | ADC                    |

| CALIBRATE        | 1              | Output       | 1 – Power-up calibration                                                                                                                                                                                                                                                            | ADC                    |

| DATAVALID        | 1              | Output       | 1 – Valid conversion result                                                                                                                                                                                                                                                         | ADC                    |

| RESULT[11:0]     | 12             | Output       | Conversion result                                                                                                                                                                                                                                                                   | ADC                    |

| TMSTBINT         | 1              | Input        | Internal temp. monitor strobe                                                                                                                                                                                                                                                       | ADC                    |

| SAMPLE           | 1              | Output       | <ul> <li>1 – An analog signal is actively being sampled (stays high during signal acquisition only)</li> <li>0 – No analog signal is being sampled</li> </ul>                                                                                                                       | ADC                    |

| VAREFSEL         | 1              | Input        | 0 = Output internal voltage reference (2.56 V) to VAREF 1 = Input external voltage reference                                                                                                                                                                                        | ADC                    |

|                  |                |              | from VAREF and ADCGNDREF                                                                                                                                                                                                                                                            |                        |

| CHNUMBER[4:0]    | 5              | Input        | Analog input channel select                                                                                                                                                                                                                                                         | Input<br>multiplexer   |

| ACMCLK           | 1              | Input        | ACM clock                                                                                                                                                                                                                                                                           | ACM                    |

| ACMWEN           | 1              | Input        | ACM write enable – active high                                                                                                                                                                                                                                                      | ACM                    |

| ACMRESET         | 1              | Input        | ACM reset – active low                                                                                                                                                                                                                                                              | ACM                    |

| ACMWDATA[7:0]    | 8              | Input        | ACM write data                                                                                                                                                                                                                                                                      | ACM                    |

| ACMRDATA[7:0]    | 8              | Output       | ACM read data                                                                                                                                                                                                                                                                       | ACM                    |

| ACMADDR[7:0]     | 8              | Input        | ACM address                                                                                                                                                                                                                                                                         | ACM                    |

| CMSTB0 to CMSTB9 | 10             | Input        | Current monitor strobe – 1 per quad, active high                                                                                                                                                                                                                                    | Analog Quad            |

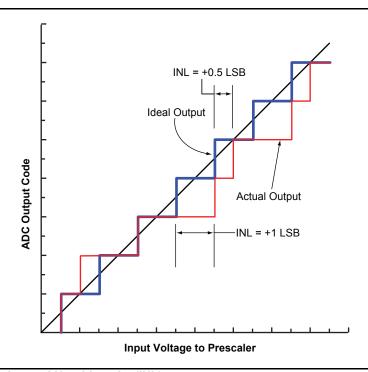

#### INL - Integral Non-Linearity

INL is the deviation of an actual transfer function from a straight line. After nullifying offset and gain errors, the straight line is either a best-fit straight line or a line drawn between the end points of the transfer function (Figure 2-85).

Figure 2-85 • Integral Non-Linearity (INL)

#### LSB - Least Significant Bit

In a binary number, the LSB is the least weighted bit in the group. Typically, the LSB is the furthest right bit. For an ADC, the weight of an LSB equals the full-scale voltage range of the converter divided by  $2^N$ , where N is the converter's resolution.

EQ 13 shows the calculation for a 10-bit ADC with a unipolar full-scale voltage of 2.56 V:

$$1 LSB = (2.56 V / 2^{10}) = 2.5 mV$$

EQ 13

#### No Missing Codes

An ADC has no missing codes if it produces all possible digital codes in response to a ramp signal applied to the analog input.

# User I/Os

#### Introduction

Fusion devices feature a flexible I/O structure, supporting a range of mixed voltages (1.5 V, 1.8 V, 2.5 V, and 3.3 V) through a bank-selectable voltage. Table 2-68, Table 2-69, Table 2-70, and Table 2-71 on page 2-135 show the voltages and the compatible I/O standards. I/Os provide programmable slew rates, drive strengths, weak pull-up, and weak pull-down circuits. 3.3 V PCI and 3.3 V PCI-X are 5 V-tolerant. See the "5 V Input Tolerance" section on page 2-144 for possible implementations of 5 V tolerance.

All I/Os are in a known state during power-up, and any power-up sequence is allowed without current impact. Refer to the "I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)" section on page 3-5 for more information. In low power standby or sleep mode (VCC is OFF, VCC33A is ON, VCCI is ON) or when the resource is not used, digital inputs are tristated, digital outputs are tristated, and digital bibufs (input/output) are tristated.

I/O Tile

The Fusion I/O tile provides a flexible, programmable structure for implementing a large number of I/O standards. In addition, the registers available in the I/O tile in selected I/O banks can be used to support high-performance register inputs and outputs, with register enable if desired (Figure 2-99 on page 2-133). The registers can also be used to support the JESD-79C DDR standard within the I/O structure (see the "Double Data Rate (DDR) Support" section on page 2-139 for more information).

As depicted in Figure 2-100 on page 2-138, all I/O registers share one CLR port. The output register and output enable register share one CLK port. Refer to the "I/O Registers" section on page 2-138 for more information.

## I/O Banks and I/O Standards Compatibility

The digital I/Os are grouped into I/O voltage banks. There are three digital I/O banks on the AFS090 and AFS250 devices and four digital I/O banks on the AFS600 and AFS1500 devices. Figure 2-113 on page 2-158 and Figure 2-114 on page 2-159 show the bank configuration by device. The north side of the I/O in the AFS600 and AFS1500 devices comprises two banks of Pro I/Os. The Pro I/Os support a wide number of voltage-referenced I/O standards in addition to the multitude of single-ended and differential I/O standards common throughout all Microsemi digital I/Os. Each I/O voltage bank has dedicated I/O supply and ground voltages (VCCI/GNDQ for input buffers and VCCI/GND for output buffers). Because of these dedicated supplies, only I/Os with compatible standards can be assigned to the same I/O voltage bank. Table 2-69 and Table 2-70 on page 2-134 show the required voltage compatibility values for each of these voltages.

For more information about I/O and global assignments to I/O banks, refer to the specific pin table of the device in the "Package Pin Assignments" on page 4-1 and the "User I/O Naming Convention" section on page 2-158.

Each Pro I/O bank is divided into minibanks. Any user I/O in a VREF minibank (a minibank is the region of scope of a VREF pin) can be configured as a VREF pin (Figure 2-99 on page 2-133). Only one VREF pin is needed to control the entire VREF minibank. The location and scope of the VREF minibanks can be determined by the I/O name. For details, see the "User I/O Naming Convention" section on page 2-158.

Table 2-70 on page 2-134 shows the I/O standards supported by Fusion devices and the corresponding voltage levels.

I/O standards are compatible if the following are true:

- · Their VCCI values are identical.

- If both of the standards need a VREF, their VREF values must be identical (Pro I/O only).

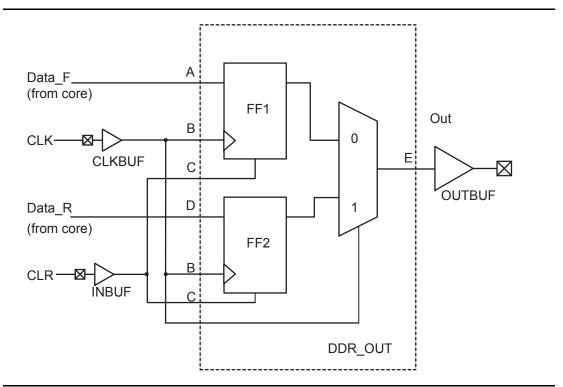

Figure 2-102 • DDR Output Support in Fusion Devices

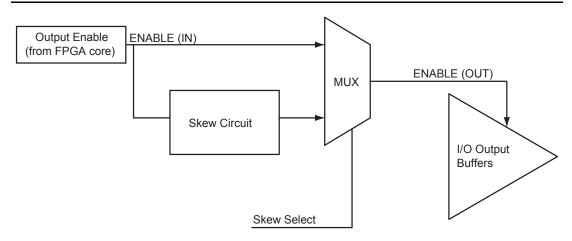

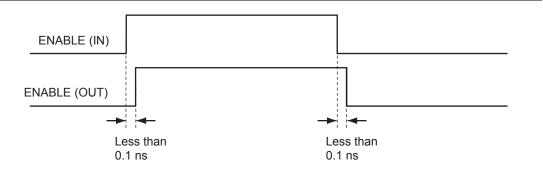

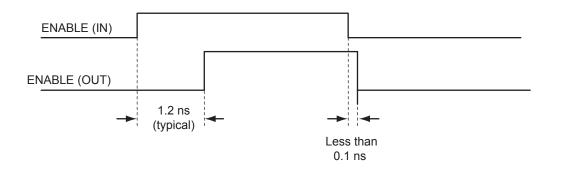

# Selectable Skew between Output Buffer Enable/Disable Time

The configurable skew block is used to delay the output buffer assertion (enable) without affecting deassertion (disable) time.

Figure 2-107 • Block Diagram of Output Enable Path

Figure 2-108 • Timing Diagram (option1: bypasses skew circuit)

Figure 2-109 • Timing Diagram (option 2: enables skew circuit)

2-149 Revision 6

Fusion Family of Mixed Signal FPGAs

Table 2-109 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,

Worst-Case VCCI = 3.0 V

Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade  | <b>t</b>          | <b>t</b>        | <b>t</b>         | <b>t</b>        | <b>t</b>          | <b>+</b>        | t               | t               | t               | Units  |

|-------------------|-----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|--------|

| Strength          | Grade           | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Ullita |

| 2 mA              | Std.            | 0.66              | 7.07            | 0.04             | 1.00            | 0.43              | 7.20            | 6.23            | 2.07            | 2.15            | ns     |

|                   | -1              | 0.56              | 6.01            | 0.04             | 0.85            | 0.36              | 6.12            | 5.30            | 1.76            | 1.83            | ns     |

|                   | -2 <sup>2</sup> | 0.49              | 5.28            | 0.03             | 0.75            | 0.32              | 5.37            | 4.65            | 1.55            | 1.60            | ns     |

| 4 mA              | Std.            | 0.66              | 7.07            | 0.04             | 1.00            | 0.43              | 7.20            | 6.23            | 2.07            | 2.15            | ns     |

|                   | -1              | 0.56              | 6.01            | 0.04             | 0.85            | 0.36              | 6.12            | 5.30            | 1.76            | 1.83            | ns     |

|                   | -2              | 0.49              | 5.28            | 0.03             | 0.75            | 0.32              | 5.37            | 4.65            | 1.55            | 1.60            | ns     |

| 6 mA              | Std.            | 0.66              | 4.41            | 0.04             | 1.00            | 0.43              | 4.49            | 3.75            | 2.39            | 2.69            | ns     |

|                   | -1              | 0.56              | 3.75            | 0.04             | 0.85            | 0.36              | 3.82            | 3.19            | 2.04            | 2.29            | ns     |

|                   | -2              | 0.49              | 3.29            | 0.03             | 0.75            | 0.32              | 3.36            | 2.80            | 1.79            | 2.01            | ns     |

| 8 mA              | Std.            | 0.66              | 4.41            | 0.04             | 1.00            | 0.43              | 4.49            | 3.75            | 2.39            | 2.69            | ns     |

|                   | <b>–</b> 1      | 0.56              | 3.75            | 0.04             | 0.85            | 0.36              | 3.82            | 3.19            | 2.04            | 2.29            | ns     |

|                   | -2              | 0.49              | 3.29            | 0.03             | 0.75            | 0.32              | 3.36            | 2.80            | 1.79            | 2.01            | ns     |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

#### VCC Core Supply Voltage

Supply voltage to the FPGA core, nominally 1.5 V. VCC is also required for powering the JTAG state machine, in addition to VJTAG. Even when a Fusion device is in bypass mode in a JTAG chain of interconnected devices, both VCC and VJTAG must remain powered to allow JTAG signals to pass through the Fusion device.

#### VCCIBx I/O Supply Voltage

Supply voltage to the bank's I/O output buffers and I/O logic. Bx is the I/O bank number. There are either four (AFS090 and AFS250) or five (AFS600 and AFS1500) I/O banks on the Fusion devices plus a dedicated VJTAG bank.

Each bank can have a separate VCCI connection. All I/Os in a bank will run off the same VCCIBx supply. VCCI can be 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VCCI pins tied to GND.

#### VCCPLA/B PLL Supply Voltage

Supply voltage to analog PLL, nominally 1.5 V, where A and B refer to the PLL. AFS090 and AFS250 each have a single PLL. The AFS600 and AFS1500 devices each have two PLLs. Microsemi recommends tying VCCPLX to VCC and using proper filtering circuits to decouple VCC noise from PLL. If unused, VCCPLA/B should be tied to GND.

#### VCOMPLA/B Ground for West and East PLL

VCOMPLA is the ground of the west PLL (CCC location F) and VCOMPLB is the ground of the east PLL (CCC location C).

#### VJTAG JTAG Supply Voltage

Fusion devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). Isolating the JTAG power supply in a separate I/O bank gives greater flexibility in supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned to be used, the VJTAG pin together with the TRST pin could be tied to GND. It should be noted that VCC is required to be powered for JTAG operation; VJTAG alone is insufficient. If a Fusion device is in a JTAG chain of interconnected boards and it is desired to power down the board containing the Fusion device, this may be done provided both VJTAG and VCC to the Fusion part remain powered; otherwise, JTAG signals will not be able to transition the Fusion device, even in bypass mode.

#### VPUMP Programming Supply Voltage

Fusion devices support single-voltage ISP programming of the configuration flash and FlashROM. For programming, VPUMP should be in the 3.3 V +/-5% range. During normal device operation, VPUMP can be left floating or can be tied to any voltage between 0 V and 3.6 V.

When the VPUMP pin is tied to ground, it shuts off the charge pump circuitry, resulting in no sources of oscillation from the charge pump circuitry.

For proper programming, 0.01  $\mu$ F and 0.33  $\mu$ F capacitors (both rated at 16 V) are to be connected in parallel across VPUMP and GND, and positioned as close to the FPGA pins as possible.

Table 3-5 • FPGA Programming, Storage, and Operating Limits

| Product<br>Grade | Storage<br>Temperature      | Element        | Grade Programming Cycles | Retention |

|------------------|-----------------------------|----------------|--------------------------|-----------|

| Commercial       | Min. T <sub>J</sub> = 0°C   | FPGA/FlashROM  | 500                      | 20 years  |

|                  | Max. T <sub>J</sub> = 85°C  | Embedded Flash | < 1,000                  | 20 years  |

|                  |                             |                | < 10,000                 | 10 years  |

|                  |                             |                | < 15,000                 | 5 years   |

| Industrial       | Min. $T_J = -40^{\circ}C$   | FPGA/FlashROM  | 500                      | 20 years  |

|                  | Max. T <sub>J</sub> = 100°C | Embedded Flash | < 1,000                  | 20 years  |

|                  |                             |                | < 10,000                 | 10 years  |

|                  |                             |                | < 15,000                 | 5 years   |

# I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)

Sophisticated power-up management circuitry is designed into every Fusion device. These circuits ensure easy transition from the powered off state to the powered up state of the device. The many different supplies can power up in any sequence with minimized current spikes or surges. In addition, the I/O will be in a known state through the power-up sequence. The basic principle is shown in Figure 3-1 on page 3-6.

There are five regions to consider during power-up.

Fusion I/Os are activated only if ALL of the following three conditions are met:

- 1. VCC and VCCI are above the minimum specified trip points (Figure 3-1).

- 2. VCCI > VCC 0.75 V (typical).

- 3. Chip is in the operating mode.

#### **V<sub>CCI</sub> Trip Point:**

Ramping up: 0.6 V < trip\_point\_up < 1.2 V Ramping down: 0.5 V < trip\_point\_down < 1.1 V

**V<sub>CC</sub>** Trip Point:

Ramping up: 0.6 V < trip\_point\_up < 1.1 V Ramping down: 0.5 V < trip\_point\_down < 1 V

VCC and VCCI ramp-up trip points are about 100 mV higher than ramp-down trip points. This specifically built-in hysteresis prevents undesirable power-up oscillations and current surges. Note the following:

- During programming, I/Os become tristated and weakly pulled up to VCCI.

- JTAG supply, PLL power supplies, and charge pump VPUMP supply have no influence on I/O behavior.

#### Internal Power-Up Activation Sequence

- 1. Core

- 2. Input buffers

- 3. Output buffers, after 200 ns delay from input buffer activation

#### PLL Behavior at Brownout Condition

Microsemi recommends using monotonic power supplies or voltage regulators to ensure proper power-up behavior. Power ramp-up should be monotonic at least until VCC and VCCPLX exceed brownout activation levels. The  $V_{CC}$  activation level is specified as 1.1 V worst-case (see Figure 3-1 on page 3-6 for more details).

When PLL power supply voltage and/or VCC levels drop below the VCC brownout levels  $(0.75~V\pm0.25~V)$ , the PLL output lock signal goes low and/or the output clock is lost.

3-5 Revision 6

Table 3-9 • AFS600 Quiescent Supply Current Characteristics (continued)

| Parameter | Description                 | Conditions                                                         | Temp.                  | Min            | Тур | Max | Unit |

|-----------|-----------------------------|--------------------------------------------------------------------|------------------------|----------------|-----|-----|------|

| IPP       | Programming supply          | Non-programming mode,                                              | $T_J = 25^{\circ}C$    |                | 36  | 80  | μA   |

|           | current                     | VPUMP = 3.63 V                                                     | T <sub>J</sub> = 85°C  |                | 36  | 80  | μA   |

|           |                             |                                                                    | T <sub>J</sub> = 100°C |                | 36  | 80  | μΑ   |

|           |                             | Standby mode <sup>5</sup> or Sleep mode <sup>6</sup> , VPUMP = 0 V |                        |                | 0   | 0   | μA   |

| ICCNVM    | Embedded NVM current        | Reset asserted,                                                    | $T_J = 25^{\circ}C$    | J = 25°C 22 80 |     | 80  | μA   |

|           |                             | VCCNVM = 1.575 V                                                   | T <sub>J</sub> = 85°C  |                | 24  | 80  | μΑ   |

|           |                             |                                                                    | T <sub>J</sub> = 100°C |                | 25  | 80  | μA   |

| ICCPLL    | 1.5 V PLL quiescent current |                                                                    | $T_J = 25^{\circ}C$    |                | 130 | 200 | μΑ   |

|           |                             | VCCPLL = 1.575 V                                                   | T <sub>J</sub> = 85°C  |                | 130 | 200 | μΑ   |

|           |                             |                                                                    | T <sub>J</sub> = 100°C |                | 130 | 200 | μA   |

#### Notes:

- 1. ICC is the 1.5 V power supplies, ICC and ICC15A.

- 2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

- 3. ICCI includes all ICCI0, ICCI1, ICCI2, and ICCI4.

- 4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

- 5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

- 6. Sleep Mode, VCC = VJTAG = VPUMP = 0 V.

3-13 Revision 6

# **Dynamic Power Consumption of Various Internal Resources**

Table 3-14 • Different Components Contributing to the Dynamic Power Consumption in Fusion Devices

|           | Power Supply Device-Specific Dynamic Contributions                       |        |                             |            | 6          |           |        |        |

|-----------|--------------------------------------------------------------------------|--------|-----------------------------|------------|------------|-----------|--------|--------|

| Parameter | Definition                                                               | Name   | Setting                     | AFS1500    | AFS600     | AFS250    | AFS090 | Units  |

| PAC1      | Clock contribution of a Global<br>Rib                                    | VCC    | 1.5 V                       | 14.5       | 12.8       | 11        | 11     | µW/MHz |

| PAC2      | Clock contribution of a Global<br>Spine                                  | VCC    | 1.5 V                       | 2.5        | 1.9        | 1.6       | 0.8    | µW/MHz |

| PAC3      | Clock contribution of a VersaTile row                                    | VCC    | 1.5 V                       |            | 0.8        | 1         |        | μW/MHz |

| PAC4      | Clock contribution of a VersaTile used as a sequential module            | VCC    | 1.5 V                       |            | 0.1        | 1         |        | μW/MHz |

| PAC5      | First contribution of a VersaTile used as a sequential module            | VCC    | 1.5 V                       |            | 0.0        | 7         |        | μW/MHz |

| PAC6      | Second contribution of a<br>VersaTile used as a sequential<br>module     |        | 1.5 V                       |            | 0.2        | 9         |        | µW/MHz |

| PAC7      | Contribution of a VersaTile used as a combinatorial module               | VCC    | 1.5 V                       | 0.29       |            |           |        | μW/MHz |

| PAC8      | Average contribution of a routing net                                    | VCC    | 1.5 V                       | 0.70       |            |           |        | μW/MHz |

| PAC9      | Contribution of an I/O input pin (standard dependent)                    | VCCI   | See Table 3-12 on page 3-18 |            |            |           |        |        |

| PAC10     | Contribution of an I/O output pin (standard dependent)                   | VCCI   |                             | See        | Table 3-13 | on page 3 | -20    |        |

| PAC11     | Average contribution of a RAM block during a read operation              | VCC    | 1.5 V                       |            | 25         | j         |        | μW/MHz |

| PAC12     | Average contribution of a RAM block during a write operation             | VCC    | 1.5 V                       |            | 30         | )         |        | μW/MHz |

| PAC13     | Dynamic Contribution for PLL                                             | VCC    | 1.5 V                       |            | 2.6        | 3         |        | µW/MHz |

| PAC15     | Contribution of NVM block during a read operation (F < 33MHz)            | VCC    | 1.5 V                       |            | 358        | 8         |        | μW/MHz |

| PAC16     | 1st contribution of NVM block<br>during a read operation (F > 33<br>MHz) |        | 1.5 V                       | 12.88      |            |           |        | mW     |

| PAC17     | 2nd contribution of NVM block<br>during a read operation (F > 33<br>MHz) |        | 1.5 V                       | V 4.8      |            |           | μW/MHz |        |

| PAC18     | Crystal Oscillator contribution                                          | VCC33A | 3.3 V                       | 3.3 V 0.63 |            |           |        | mW     |

| PAC19     | RC Oscillator contribution                                               | VCC33A | 3.3 V                       |            | 3.3        | 3         |        | mW     |

| PAC20     | Analog Block dynamic power contribution of ADC                           | VCC    | 1.5 V                       |            | 3          |           |        | mW     |

|            |                 | FG256           |                 |                  |

|------------|-----------------|-----------------|-----------------|------------------|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |

| R5         | AV0             | AV0             | AV2             | AV2              |

| R6         | AT0             | AT0             | AT2             | AT2              |

| R7         | AV1             | AV1             | AV3             | AV3              |

| R8         | AT3             | AT3             | AT5             | AT5              |

| R9         | AV4             | AV4             | AV6             | AV6              |

| R10        | NC              | AT5             | AT7             | AT7              |

| R11        | NC              | AV5             | AV7             | AV7              |

| R12        | NC              | NC              | AT9             | AT9              |

| R13        | NC              | NC              | AG9             | AG9              |

| R14        | NC              | NC              | AC9             | AC9              |

| R15        | PUB             | PUB             | PUB             | PUB              |

| R16        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |

| T1         | GND             | GND             | GND             | GND              |

| T2         | NCAP            | NCAP            | NCAP            | NCAP             |

| Т3         | VCC33N          | VCC33N          | VCC33N          | VCC33N           |

| T4         | NC              | NC              | ATRTN0          | ATRTN0           |

| T5         | AT1             | AT1             | AT3             | AT3              |

| T6         | ATRTN0          | ATRTN0          | ATRTN1          | ATRTN1           |

| T7         | AT2             | AT2             | AT4             | AT4              |

| Т8         | ATRTN1          | ATRTN1          | ATRTN2          | ATRTN2           |

| Т9         | AT4             | AT4             | AT6             | AT6              |

| T10        | ATRTN2          | ATRTN2          | ATRTN3          | ATRTN3           |

| T11        | NC              | NC              | AT8             | AT8              |

| T12        | NC              | NC              | ATRTN4          | ATRTN4           |

| T13        | GNDA            | GNDA            | GNDA            | GNDA             |

| T14        | VCC33A          | VCC33A          | VCC33A          | VCC33A           |

| T15        | VAREF           | VAREF           | VAREF           | VAREF            |

| T16        | GND             | GND             | GND             | GND              |

### Datasheet Information

| Revision                       | Changes                                                                                                                                                                                                                                                           | Page       |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Advance v1.0 (continued)       | This change table states that in the "208-Pin PQFP" table listed under the Advance v0.8 changes, the AFS090 device had a pin change. That is incorrect. Pin 102 was updated for AFS250 and AFS600. The function name changed from $V_{CC33ACAP}$ to $V_{CC33A}$ . |            |

| Advance v0.9<br>(October 2007) | In the "Package I/Os: Single-/Double-Ended (Analog)" table, the AFS1500/M7AFS1500 I/O counts were updated for the following devices: FG484: 223/109 FG676: 252/126                                                                                                | II         |

|                                | In the "108-Pin QFN" table, the function changed from $V_{\text{CC33ACAP}}$ to $V_{\text{CC33A}}$ for the following pin: B25                                                                                                                                      | 3-2        |

|                                | In the "180-Pin QFN" table, the function changed from $V_{CC33ACAP}$ to $V_{CC33A}$ for the following pins: AFS090: B29 AFS250: B29                                                                                                                               | 3-4        |

|                                | In the "208-Pin PQFP" table, the function changed from $V_{CC33ACAP}$ to $V_{CC33A}$ for the following pins: AFS090: 102 AFS250: 102                                                                                                                              | 3-8        |

|                                | In the "256-Pin FBGA" table, the function changed from V <sub>CC33ACAP</sub> to V <sub>CC33A</sub> for the following pins:  AFS090: T14  AFS250: T14  AFS600: T14  AFS1500: T14                                                                                   | 3-12       |

| Advance v0.9 (continued)       | In the "484-Pin FBGA" table, the function changed from V <sub>CC33ACAP</sub> to V <sub>CC33A</sub> for the following pins:  AFS600: AB18  AFS1500: AB18                                                                                                           | 3-20       |

|                                | In the "676-Pin FBGA" table, the function changed from $V_{CC33ACAP}$ to $V_{CC33A}$ for the following pins: AFS1500: AD20                                                                                                                                        | 3-28       |

| Advance v0.8 (June 2007)       | Figure 2-16 • Fusion Clocking Options and the "RC Oscillator" section were updated to change GND_OSC and VCC_OSC to GNDOSC and VCCOSC.                                                                                                                            | 2-20, 2-21 |

|                                | Figure 2-19 • Fusion CCC Options: Global Buffers with the PLL Macro was updated to change the positions of OADIVRST and OADIVHALF, and a note was added.                                                                                                          | 2-25       |

|                                | The "Crystal Oscillator" section was updated to include information about controlling and enabling/disabling the crystal oscillator.                                                                                                                              | 2-22       |

|                                | Table 2-11 · Electrical Characteristics of the Crystal Oscillator was updated to change the typical value of I <sub>DYNXTAL</sub> for 0.032–0.2 MHz to 0.19.                                                                                                      | 2-24       |

|                                | The "1.5 V Voltage Regulator" section was updated to add "or floating" in the paragraph stating that an external pull-down is required on TRST to power down the VR.                                                                                              |            |

|                                | The "1.5 V Voltage Regulator" section was updated to include information on powering down with the VR.                                                                                                                                                            | 2-41       |

5-11 Revision 6

# Fusion Family of Mixed Signal FPGAs

| Revision                 | Changes                                                                                                                                | Page  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------|

| Advance v0.3 (continued) | The "Temperature Monitor" section was updated.                                                                                         | 2-96  |

| (continued)              | EQ 2 is new.                                                                                                                           | 2-103 |

|                          | The "ADC Description" section was updated.                                                                                             | 2-102 |

|                          | Figure 2-16 • Fusion Clocking Options was updated.                                                                                     | 2-20  |

|                          | Table 2-46 · Analog Channel Specifications was updated.                                                                                | 2-118 |

|                          | The notes in Table 2-72 • Fusion Standard and Advanced I/O – Hot-Swap and 5 V Input Tolerance Capabilities were updated.               | 2-144 |

|                          | The "Simultaneously Switching Outputs and PCB Layout" section is new.                                                                  | 2-149 |

|                          | LVPECL and LVDS were updated in Table 2-81 • Fusion Standard and Advanced I/O Attributes vs. I/O Standard Applications.                | 2-157 |

|                          | LVPECL and LVDS were updated in Table 2-82 • Fusion Pro I/O Attributes vs. I/O Standard Applications.                                  | 2-158 |

|                          | The "Timing Model" was updated.                                                                                                        | 2-161 |

|                          | All voltage-referenced Minimum and Maximum DC Input and Output Level tables were updated.                                              |       |

|                          | All Timing Characteristic tables were updated                                                                                          | N/A   |

|                          | Table 2-83 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions was updated. | 2-165 |

|                          | Table 2-79 • Summary of I/O Timing Characteristics – Software Default Settings was updated.                                            | 2-134 |

|                          | Table 2-93 • I/O Output Buffer Maximum Resistances <sup>1</sup> was updated.                                                           | 2-171 |

|                          | The "BLVDS/M-LVDS" section is new. BLVDS and M-LVDS are two new I/O standards included in the datasheet.                               | 2-211 |

|                          | The "CoreMP7 and Cortex-M1 Software Tools" section is new.                                                                             | 2-257 |

|                          | Table 2-83 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions was updated. | 2-165 |

|                          | Table 2-79 • Summary of I/O Timing Characteristics – Software Default Settings was updated.                                            | 2-134 |

|                          | Table 2-93 • I/O Output Buffer Maximum Resistances <sup>1</sup> was updated.                                                           | 2-171 |

|                          | The "BLVDS/M-LVDS" section is new. BLVDS and M-LVDS are two new I/O standards included in the datasheet.                               | 2-211 |

|                          | The "108-Pin QFN" table for the AFS090 device is new.                                                                                  | 3-2   |

|                          | The "180-Pin QFN" table for the AFS090 device is new.                                                                                  | 3-4   |

|                          | The "208-Pin PQFP" table for the AFS090 device is new.                                                                                 | 3-8   |

|                          | The "256-Pin FBGA" table for the AFS090 device is new.                                                                                 | 3-12  |

|                          | The "256-Pin FBGA" table for the AFS250 device is new.                                                                                 | 3-12  |