Welcome to E-XFL.COM

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Product Status                 | Active                                                                     |

|--------------------------------|----------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells |                                                                            |

| Total RAM Bits                 | 276480                                                                     |

| Number of I/O                  | 119                                                                        |

| Number of Gates                | 1500000                                                                    |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                            |

| Package / Case                 | 256-LBGA                                                                   |

| Supplier Device Package        | 256-FPBGA (17x17)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1afs1500-2fg256 |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Device Architecture

### Timing Characteristics

Table 2-1 Combinatorial Cell Propagation Delays

Commercial Temperature Range Conditions: T J = 70°C, Worst-Case VCC = 1.425 V

| Combinatorial Cell | Equation                    | Parameter       | -2   | –1   | Std. | Units |

|--------------------|-----------------------------|-----------------|------|------|------|-------|

| INV                | Y = !A                      | t <sub>PD</sub> | 0.40 | 0.46 | 0.54 | ns    |

| AND2               | $Y = A \bullet B$           | фD              | 0.47 | 0.54 | 0.63 | ns    |

| NAND2              | $Y = !(A \bullet B)$        | μ <sub>D</sub>  | 0.47 | 0.54 | 0.63 | ns    |

| OR2                | Y = A + B                   | ₽D              | 0.49 | 0.55 | 0.65 | ns    |

| NOR2               | Y = !(A + B)                | ₽́D             | 0.49 | 0.55 | 0.65 | ns    |

| XOR2               | Y = A B                     | t <sub>PD</sub> | 0.74 | 0.84 | 0.99 | ns    |

| MAJ3               | Y = MAJ(A, B, C)            | ₽́D             | 0.70 | 0.79 | 0.93 | ns    |

| XOR3               | Y = A B C                   | t <sub>PD</sub> | 0.87 | 1.00 | 1.17 | ns    |

| MUX2               | Y = A ! S + B S             | μ <sub>D</sub>  | 0.51 | 0.58 | 0.68 | ns    |

| AND3               | $Y = A \bullet B \bullet C$ | РÐ              | 0.56 | 0.64 | 0.75 | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

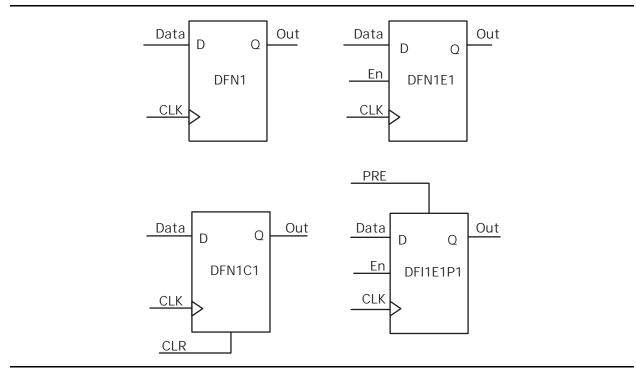

### Sample VersaTile Specifications Sequential Module

The Fusion library offers a wide variety of sequenterial including flip-flops and latches. Each has a data input and optional enable, clear, or preset. Institution, timing characteristics are presented for a representative sample from the librarigu(re 2-5). For more details, refer to tlbacOO, ProASIC3, SmartFusion and Fusion Macro Library Guide.

Figure 2-5 Sample of Sequential Cells

### VersaNet Timing Characteristics

Global clock delays include the central rib delay, the spine delay, and the row delay. Delays do not include I/O input buffer clock delays, as thesedapendent upon I/O standard, and the clock may be driven and conditioned internally by the CCC mod**Lable** 2-5 Table 2-6 Table 2-7, and Table 2-8 on page 2-17 present minimum and maximum global clock delays within the device Minimum and maximum delays are measured with minimum and maximum loading, respectively.

Timing Characteristics

Table 2-5 AFS1500 Global Resource Timing Commercial Temperature Range Conditions: T \_1 = 70°C, Worst-Case VCC = 1.425 V

| Parameter                | Description                               | _                 | 2                 | -                 | 1                 | S                 | td.               | Linita |  |

|--------------------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------|--|

| Falametei                | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units  |  |

| <b>t</b> RCKL            | Input Low Delay for Global Cloc           | 1.53              | 1.75              | 1.74              | 1.99              | 2.05              | 5 2.34            | 4 ns   |  |

| ŧ <sub>КСКН</sub>        | Input High Delay for Global Color         | 1.53              | 1.79              | 1.75              | 2.04              | 2.0               | 5 2.4             | 0 ns   |  |

|                          | Minimum Pulse Width High for Global Clock | i.                |                   |                   |                   |                   |                   | ns     |  |

|                          | Minimum Pulse Width Low for Global Clock  |                   |                   |                   |                   |                   |                   | ns     |  |

| <b>t<sub>RCKSW</sub></b> | Maximum Skew for Global Clock             |                   | 0.2               | 6                 | 0.2               | 9                 | 0.3               | 34 n   |  |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element located in a lightly loaded row (single element is connected to the global net).

- 2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element located in a fully loaded row (all available flip-flops are connected to the global net in the row).

- 3. For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

### Table 2-6 AFS600 Global Resource Timing

Commercial Temperature Range Conditions: T J = 70°C, Worst-Case VCC = 1.425 V

| Parameter      | Description                               | -2                | 2                 | -                 | -1                | S                 | td.               | Units |    |

|----------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------|----|

|                | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |    |

| <b>t</b> RCKL  | Input Low Delay for Global Clock          | 1.2               | 7 1.4             | 9 1.              | 44 1.             | 70 1              | .69 2             | 2.00  | ns |

| <b>₽</b> RCKH  | Input High Delay for Global Clock         | 1.26              | 1.54              | 1.44              | 1.75              | 1.69              | 2.0               | 6 n   | IS |

|                | Minimum Pulse Width High for Global Clock | (                 |                   |                   |                   |                   |                   | l     | ns |

|                | Minimum Pulse Width Low for Global Clock  |                   |                   |                   |                   |                   |                   |       | ns |

| <b>t</b> RCKSW | Maximum Skew for Global Clock             |                   | 0.2               | 7                 | 0.3               | 31                | 0.                | 36    | ns |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

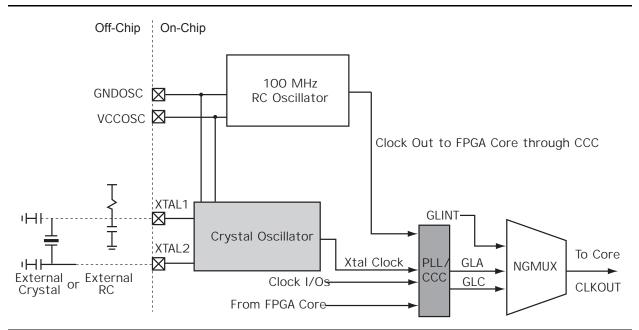

# **Clocking Resources**

The Fusion family has a robust collection of clocking peripherals, as shown in the block diagram in Figure 2-16 These on-chip resources enable the creationanipulation, and distribution of many clock signals. The Fusion integrated RC oscillatoroquices a 100 MHz clock source with no external components. For systems requiring meroprecise clock signals, the **sion** family supports an on-chip crystal oscillator circuit. The integrated PLLsaith Fusion device can use the RC oscillator, crystal oscillator, or another on-chip clock signal as a southese PLLs offer a variety of capabilities to modify the clock source (multiply, divide, synchronize, advanor delay). Utilizing the CCC found in the popular ProASIC3 family, Fusion incorporates six CCC blockse CCCs allow access trusion global and local clock distribution nets, as described in "Chebal Resources (VersaNets)" section on page 2-11

Figure 2-16 Fusion Clocking Options

# **Clock Conditioning Circuits**

In Fusion devices, the CCCs are used to implement division, frequency multiplication, phase shifting, and delay operations.

The CCCs are available in six chip locations each define four chip corneasd the middle of the east and west chip sides.

Each CCC can implement up to three independent buffers (with orthogiut programmable delay), or a PLL function (programmable frequency division programmable frequency din the programmable fre

A global buffer can be placed in any of the three global locations (CLKA-GLA, CLKB-GLB, and CLKC-GLC) of a given CCC.

A PLL macro uses the CLKA CCC input to drive its nearfice clock. It uses the GLA and, optionally, the GLB and GLC global outputs to drive the global networks. A PLL macro can also drive the YB and YC regular core outputs. The GLB (or GLC) global output in the reused if the YB (or YC) output is used (Figure 2-19). Refer to the PLL Macro" section on page 2-20 r more information.

Each global buffer, as well as the PLL reference, can be driven from one of the following:

- 3 dedicated single-ended I/Os using a hardwired connection

- 2 dedicated differential I/Os using a hardwired connection

The FPGA core

The CCC block is fully configurable, either via flassifiguration bits set in the programming bitstream or through an asynchronous interface. This asynchronous interface is dynamically accessible from inside the Fusion device to permit changes of parameters (such as divide ratios) during device operation. To increase the versatility and flexibility her dlock conditioning system, the CCC configuration is determined either by the user during the designers ovith configuration data ing stored in flash memory as part of the device prangming procedure, or by writing into a dedicated shift register during normal device operation. This latter motherwas the user to dynamily reconfigure the CCC without the need for core programming. The shiftereignatcessed through a simple serial interface. Refer to the "UJTAG Applications in Microsemi s Low-Power Flash Devider" of the device FPGA Fabric User Guide and the CCC and PLL Characteristics" section on page 2f@8moreinformation.

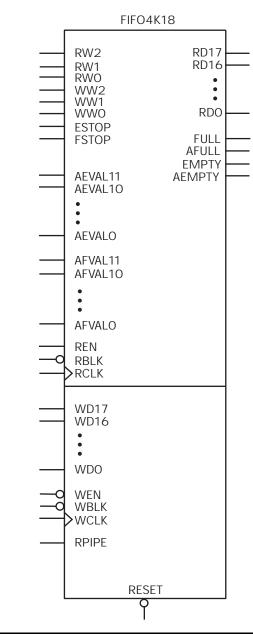

# FIFO4K18 Description

Figure 2-56 FIFO4KX18

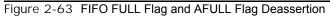

Table 2-36 describes each pin in the Analog Block. Each function within the Analog Block will be explained in detail in the following sections.

Table 2-36 Analog Block Pin Description

| Signal Name      | Number<br>of Bits | Direction    | Function                                                                                                                                                                                                                                                                                 | Location of<br>Details                 |

|------------------|-------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| VAREF            | 1                 | Input/Output | Voltage reference for ADC                                                                                                                                                                                                                                                                | ADC                                    |

| ADCGNDREF        | 1                 | Input        | External ground reference                                                                                                                                                                                                                                                                | ADC                                    |

| MODE[3:0]        | 4                 | Input        | ADC operating mode                                                                                                                                                                                                                                                                       | ADC                                    |

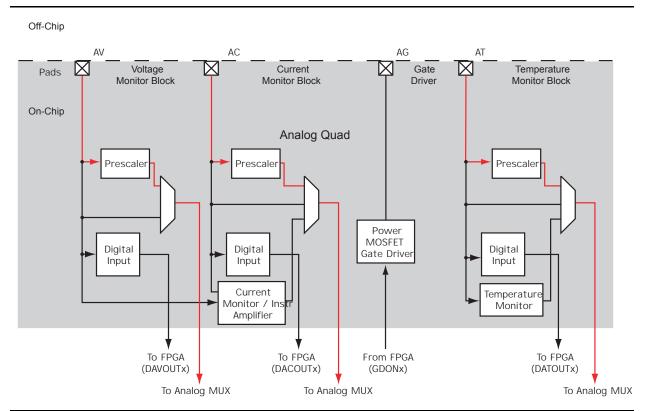

| SYSCLK           | 1                 | Input        | External system clock                                                                                                                                                                                                                                                                    |                                        |

| TVC[7:0]         | 8                 | Input        | Clock divide control                                                                                                                                                                                                                                                                     | ADC                                    |

| STC[7:0]         | 8                 | Input        | Sample time control                                                                                                                                                                                                                                                                      | ADC                                    |

| ADCSTART         | 1                 | Input        | Start of conversion                                                                                                                                                                                                                                                                      | ADC                                    |

| PWRDWN           | 1                 | Input        | ADC comparator power-down if<br>When asserted, the ADC will st<br>functioning, and the digital portion<br>the analog block will contir<br>operating. This may result in inva-<br>status flags from the analog bl<br>Therefore, Microsemi does r<br>recommend asserting the PWRDW<br>pin. | op<br>n of<br>ue<br>alid<br>ock.<br>ot |

| ADCRESET         | 1                 | Input        | ADC resets and disables Analog Qua<br>active high                                                                                                                                                                                                                                        | d ADC                                  |

| BUSY             | 1                 | Output       | 1 Running conversion                                                                                                                                                                                                                                                                     | ADC                                    |

| CALIBRATE        | 1                 | Output       | 1 Power-up calibration                                                                                                                                                                                                                                                                   | ADC                                    |

| DATAVALID        | 1                 | Output       | 1 Valid conversion result                                                                                                                                                                                                                                                                | ADC                                    |

| RESULT[11:0]     | 12                | Output       | Conversion result                                                                                                                                                                                                                                                                        | ADC                                    |

| TMSTBINT         | 1                 | Input        | Internal temp. monitor strobe                                                                                                                                                                                                                                                            | ADC                                    |

| SAMPLE           | 1                 | Output       | <ol> <li>An analog signal is actively be<br/>sampled (stays high during sig<br/>acquisition only)</li> <li>No analog signal is being sample</li> </ol>                                                                                                                                   | nal                                    |

| VAREFSEL         | 1                 | Input        | O = Output internal voltage referen<br>(2.56 V) to VAREF<br>1 = Input external voltage referen<br>from VAREF and ADCGNDREF                                                                                                                                                               |                                        |

| CHNUMBER[4:0]    | 5                 | Input        | Analog input channel select                                                                                                                                                                                                                                                              | Input<br>multiplexer                   |

| ACMCLK           | 1                 | Input        | ACM clock                                                                                                                                                                                                                                                                                | ACM                                    |

| ACMWEN           | 1                 | Input        | ACM write enable active high                                                                                                                                                                                                                                                             | ACM                                    |

| ACMRESET         | 1                 | Input        | ACM reset active low                                                                                                                                                                                                                                                                     | ACM                                    |

| ACMWDATA[7:0]    | 8                 | Input        | ACM write data                                                                                                                                                                                                                                                                           | ACM                                    |

| ACMRDATA[7:0]    | 8                 | Output       | ACM read data                                                                                                                                                                                                                                                                            | ACM                                    |

| ACMADDR[7:0]     | 8                 | Input        | ACM address                                                                                                                                                                                                                                                                              | ACM                                    |

| CMSTBO to CMSTB9 | 10                | Input        | Current monitor strobe 1 per active high                                                                                                                                                                                                                                                 | q <b>Aad</b> log Quad                  |

Typical scaling factors are givenTable 2-57 on page 2-13@nd the gain error (which contributes to the minimum and maximum) is iTable 2-49 on page 2-117

### Figure 2-67 Analog Quad Prescaler Input Configuration

### Terminology

### BW Bandwidth

BW is a range of frequencies that a Channel can handle.

### Channel

A channel is define as an analog input configured as one of the Prescaler range strated and page 2-130 The channel includes the Prescaler circuit and the ADC.

### Channel Gain

Channel Gain is a measured of the deviation the factual slope from the ideal slope. The slope is measured from the 20% and 80% point.

= .

=

EQ 1

### Channel Gain Error

Channel Gain Error is a deviation from the ideal stoppe transfer function. The Prescaler Gain Error is expressed as the percent difference between the actual and ideal, as  $s \overline{s} \overline{\omega} w$  in

u

EQ 2

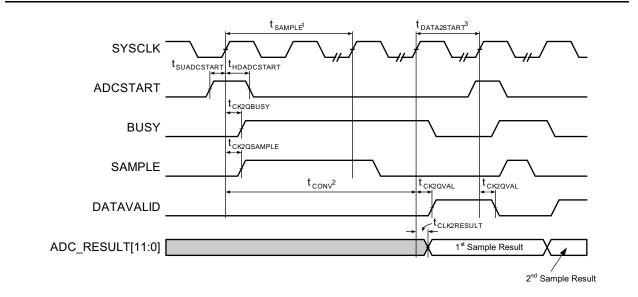

### Figure 2-90 Input Setup Time

Standard Conversion

### Notes:

1. Refer to EQ 20 on page 2-109 for the calculation on the sample time,  $t_{SAMPLE}$ .

2. See EQ 23 on page 2-109 for calculation of the conversion time, t<sub>CONV</sub>.

3. Minimum time to issue an ADCSTART after DATAVALID is 1 SYSCLK period

Figure 2-91 Standard Conversion Status Signal Timing Diagram

# Table 2-78 Fusion Standard I/O St andards—OUT\_DRIVE Settings

|                    | OUT_DRIVE (mA) |   |   |   |      |     |  |  |  |  |  |

|--------------------|----------------|---|---|---|------|-----|--|--|--|--|--|

| I/O Standards      | 2              | 4 | 6 | 8 | Slew |     |  |  |  |  |  |

| LVTTL/LVCMOS 3.3 V | 3              | 3 | 3 | 3 | High | Low |  |  |  |  |  |

| LVCMOS 2.5 V       | 3              | 3 | 3 | 3 | High | Low |  |  |  |  |  |

| LVCMOS 1.8 V       | 3              | 3 |   |   | High | Low |  |  |  |  |  |

| LVCMOS 1.5 V       | 3              |   |   |   | High | Low |  |  |  |  |  |

Table 2-79 Fusion Advanced I/O Standards—SLEW and OUT\_DRIVE Settings

|                    |   | OUT_DRIVE (mA) |   |   |    |    |      |     |  |  |  |  |

|--------------------|---|----------------|---|---|----|----|------|-----|--|--|--|--|

| I/O Standards      | 2 | 4              | 6 | 8 | 12 | 16 | Slew |     |  |  |  |  |

| LVTTL/LVCMOS 3.3 V | 3 | 3              | 3 | 3 | 3  | 3  | High | Low |  |  |  |  |

| LVCMOS 2.5 V       | 3 | 3              | 3 | 3 | 3  |    | High | Low |  |  |  |  |

| LVCMOS 1.8 V       | 3 | 3              | 3 | 3 |    |    | High | Low |  |  |  |  |

| LVCMOS 1.5 V       | 3 | 3              |   |   |    |    | High | Low |  |  |  |  |

| Table 2-80 Fusion Pro I/O Standards— S | SLEW and OUT_DRIVE Settings |

|----------------------------------------|-----------------------------|

|----------------------------------------|-----------------------------|

| I/O Standards      | 2 | 4 | 6 | 8 | 12 | 16 | 24 | Slew |       |

|--------------------|---|---|---|---|----|----|----|------|-------|

| LVTTL/LVCMOS 3.3 V | 3 | 3 | 3 | 3 | 3  | 3  | 3  | High | Low   |

| LVCMOS 2.5 V       | 3 | 3 | 3 | 3 | 3  | 3  | 3  | High | Low   |

| LVCMOS 2.5 V/5.0 V | 3 | 3 | 3 | 3 | 3  | 3  | 3  | Higł | ו Lov |

| LVCMOS 1.8 V       | 3 | 3 | 3 | 3 | 3  | 3  |    | High | Low   |

| LVCMOS 1.5 V       | 3 | 3 | 3 | 3 | 3  |    |    | High | Low   |

# I/O Software Support

In the Fusion development software, defaultn**sstti**ave been defined for the various I/O standards supported. Changes can be made to the defaultinsstvia the use of attributes; however, not all I/O attributes are applicable for all I/O standards 2-84 and Table 2-85 list the valid I/O attributes that can be manipulated by the user for each I/O standard.

Single-ended I/O standards in Fusion support up to five different drive strengths.

Table 2-84 Fusion Standard and Advanced I/O Attributes vs. I/O Standard Applications

| I/O Standards       | SLEW<br>(output<br>only) | OUT_DRIVE<br>(output only) | SKEW<br>(all macros<br>with OE)* | RES_PULL | OUT_LOAD<br>(output only) | OMBINE_REGISTER |

|---------------------|--------------------------|----------------------------|----------------------------------|----------|---------------------------|-----------------|

| LVTTL/LVCMOS 3.3 V  | 3                        | 3                          | 3                                | 3        | 3                         | 3               |

| LVCMOS 2.5 V        | 3                        | 3                          | 3                                | 3        | 3                         | 3               |

| LVCMOS 2.5/5.0 V    | 3                        | 3                          | 3                                | 3        | 3                         | 3               |

| LVCMOS 1.8 V        | 3                        | 3                          | 3                                | 3        | 3                         | 3               |

| LVCMOS 1.5 V        | 3                        | 3                          | 3                                | 3        | 3                         | 3               |

| PCI (3.3 V)         |                          |                            | 3                                |          | 3                         | 3               |

| PCI-X (3.3 V)       | 3                        |                            | 3                                |          | 3                         | 3               |

| LVDS, BLVDS, M-LVDS |                          |                            | 3                                |          |                           | 3               |

| LVPECL              |                          |                            |                                  |          |                           | 3               |

Note: \* This feature does not apply to the standard I/O banks, which are the north I/O banks of AFS090 and AFS250 devices

# **Timing Characteristics**

| Table 2-112 2.5 V LVCMOS Low Slev | V                                                                |

|-----------------------------------|------------------------------------------------------------------|

| Commercial Temperature            | Range Conditions: T $_{\rm J}$ = 70°C, Worst-Case VCC = 1.425 V, |

| Worst-Case VCCI = 2.3 V           |                                                                  |

| Applicable to Pro I/Os            |                                                                  |

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>ZHS</sub>  | Units |    |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|-------------------|-------|----|

| 4 mA              | Std.           | 0.60              | 12.0            |                  |                 |                  |                   |                 |                 |                 | 2.72            | 2.20             | 14.46             | 13.85 | ns |

|                   | 1              | 0.51              | 10.21           | 0.04             | 1.29            | 9 1.4            | 1 0.3             | 6 10            | .40 9           | 88 2            | 31 1            | .87 1            | 2.30              | 11.78 | ns |

|                   | 2              | 0.45              | 8.96            | 0.0              | 3 1.1           | 3 1.2            | 4 0.3             | 329.13          | 8.67            | 2.03            | 1.64            | 10.80            | 10.34             | ns    | -  |

| 8 mA              | Std.           | 0.60              | 8.73            | 3 0.0            | 4 1.5           | 1 1.0            | 643D.             | 8.89            | 8.01            | 3.10            | ) 2.9           | 3 11.1           | 3 10              | 25    | ns |

|                   | 1              | 0.51              | 7.43            | 0.04             | 1.29            | 9 1.4            | 1 0.3             | 67.57           | 6.82            | 2.64            | 2.4             | 9 9.4            | 78.               | 72    | ns |

|                   | 2              | 0.45              | 6.52            | 0.0              | 3 1.1           | B 1.2            | 4 0.3             | 326.64          | 5.98            | 2.32            | 2 2.1           | 9 8.3            | 1 7.6             | 5     | ns |

| 12 mA             | Std.           | 0.66              | 6.7             | 7 0.0            | 4 1.5           | 1 1.0            | 6430.             | 6.90            | 6.11            | 3.3             | 3.3             | 9 9.1            | 4 8.              | 84    | ns |

|                   | 1              | 0.56              | 5.76            | 0.04             | 1.2             | 9 1.4            | 1 0.3             | 65.87           | 5.20            | 2.86            | 2.8             | 97.7             | 77.2              | ı 01  | is |

|                   | 2              | 0.49              | 5.06            | 0.0              | 3 1.1           | 3 1.2            | 4 0.3             | 325.15          | 4.56            | 2.51            | 2.53            | 3 6.8            | 2 6.2             | 23    | ns |

| 16 mA             | Std.           | 0.66              | 6.3             | 1 0.0            | 4 1.5           | 1 1.0            | 6430.             | 6.42            | 5.73            | 3.4             | 2 3.5           | 2 8.             | 66 7              | .96   | ns |

|                   | 1              | 0.56              | 5.37            | 0.04             | 1.2             | 9 1.4            | 1 0.3             | 65.46           | 4.87            | 2.91            | 3.00            | ) 7.3            | 7 6.              | 77 i  | is |

|                   | 2              | 0.49              | 4.71            | 0.03             | 1.13            | 3 1.2            | 4 0.3             | 24.80           | 4.28            | 2.56            | 2.6             | 3 6.4            | 7 5.              | 95    | ns |

| 24 mA             | Std.           | 0.66              | 5.9             | 3 0.0            | 1.              | 51 1.            | 66430             | 6.04            | 5.70            | 3.4             | 9 4.C           | 0 8.             | 28 7              | 94    | ns |

|                   | 1              | 0.56              | 5.05            | 0.04             | 1.2             | 9 1.4            | 1 0.3             | 65.14           | 4.85            | 2.97            | 3.40            | D 7.C            | 4 6. <sup>°</sup> | 75    | ns |

|                   | 2              | 0.49              | 4.43            | 0.0              | 3 1.1           | 3 1.2            | 4 0.3             | 324.51          | 4.26            | 2.61            | 2.99            | 9 6.1            | 8 5.9             | 93 I  | ns |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

#### TMS Test Mode Select

The TMS pin controls the usetone IEEE1532 boundary scapins (TCK, TDI, TDO, TRST). There is an internal weak pull-up resistor on the TMS pin.

### TRST Boundary Scan Reset Pin

The TRST pin functions as an active low input to asynchronously initialize (or reset) the boundary scan circuitry. There is an internal weak pull-up restort the TARPItis in reset mode. The resistor values must be chosen fromTable 2-183 and must satisfy the parallel resistance value requirement. The values in Table 2-183 correspond to the resistor recommended when a single device is used and to the equivalent parallel resistor when multiple devices are connected via a JTAG chain.

In critical applications, an upsettime JTAG circuit could allow entering an undesired JTAG state. In such cases, Microsemi recommends tying off TRST to  $\mathbf{GIND}$  ugh a resistor placed close to the FPGA pin. Note that to operate at all VJTAG voltages,  $5000 \ 1 \ k$ : will satisfy the requirements.

# **Special Function Pins**

### NC No Connect

This pin is not connected to circuitry within the device pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

### DC Don't Connect

This pin should not be connected to any signal then PCB. These pins should be left unconnected.

### NCAP Negative Capacitor

Negative Capacitor is where the negative treatmost the charge pump capacitor is connected. A capacitor, with a 2.2  $\mu$ F recommended value, is required to connect between PCAP and NCAP.

### PCAP Positive Capacitor

Positive Capacitor is where the positive terminal of the gehaump capacitor is onnected. A capacitor, with a 2.2  $\mu$ F recommended value, is required to connect between PCAP and NCAP.

### PUB Push Button

Push button is the connection for the external momentaritch used to turn on the 1.5 V voltage regulator and can be floating if not used.

### PTBASE Pass Transistor Base

Pass Transistor Base is the control signal of the voltage regulator. This pin should be connected to the base of the external pass transistor used with the internal voltage regulator and can be floating if not used.

### PTEM Pass Transistor Emitter

Pass Transistor Emitter is the feedback input of the voltage regulator.

This pin should be connected to the externation of the externation of the externation of the transistor used with the 1.5 V internal voltage regulator and can be floating if not used.

### XTAL1 Crystal Oscillator Circuit Input

Input to crystal oscillator circuit. Pin for ctingeexternal crystal, ceramic resonator, RC network, or external clock input. When using an external crystal or ceramic oscillator, external capacitors are also recommended (Please refer to the crystal oscillator for proper capacitor value).

If using external RC network or clock input, XTAL1 should be used and XTAL2 left unconnected. In the case where the Crystal Oscillator block is not used, the XTAL1 pin should be connected to GND and the XTAL2 pin should be left floating.

# Theta-JA

Junction-to-ambient thermal resistance) (is determined under standa conditions specified by JEDEC (JESD-51), but it has little relevance in active afformance of the product. It should be used with caution but is useful for comparing the mathematic performance of one package to another.

A sample calculation showing the maximum power dissipation allowed for the AFS600-FG484 package under forced convection of 1.0 m/s ant zero being temperature is as follows:

Maximum Power Allowed:

$$\frac{T_{J(MAX)} - T_{A(MAX)}}{T_{JA}}$$

EQ 4

where

$J_A = 19.00^{\circ}C/W$  (taken from ble 3-6 on page 3)7

$T_A = 75.00^{\circ}C$

Maximum Power Allowed  $\frac{100.00^{\circ}\text{C}-75.00^{\circ}\text{C}}{19.00^{\circ}\text{C/W}} = 1.3 \text{ W}$

EQ 5

The power consumption of a device can be cated using the Microsenpower calculator. The device's power consumption must be lower than the calculated maximum power dissipation by the package. If the power consumption is higher threadevice's maximum allowable power dissipation, a heat sink can be attached onp toof the case, or the airflowide the system must be increased.

### Theta-JB

Junction-to-board thermal resistant (measures the ability of the page to dissipate heat from the surface of the chip to the PCB. As defined hey EDEC (JESD-51) standard, the thermal resistance from junction to board uses an isothermal ring table zone concept. The ring cold plate is simply a means to generate an isothermal boundary condition the perimeter. The cold plate is mounted on a JEDEC standard board with a minimum distance 5.0 mm away from the package edge.

## Theta-JC

Junction-to-case thermal resistance  $t_{\rm C}$  measures the ability of a device dissipate heat from the surface of the chip to the topodetom surface of the sage. It is applicable for packages used with external heat sinks. Constant temperature is adpute the surface in consideration and acts as a boundary condition. This only applies to situations and the or nearly all of the heat is dissipated through the surface in consideration.

## Calculation for Heat Sink

For example, in a design implemented in an AFS6DD484 package with 2.5 m/s airflow, the power consumption value using the power calculated is 3.00 W. The user-dependent and T<sub>j</sub> are given as follows:

$T_J = 100.00^{\circ}C$

$T_A = 70.00^{\circ}C$

From the datasheet:

$J_A = 17.00^{\circ}C/W$

$T_{C} = 8.28$ °C/W

$$P = \frac{T_J - T_A}{T_{JA}} = \frac{100^{\circ}C - 70^{\circ}C}{17.00 \text{ W}} = 1.76 \text{ W}$$

EQ 6

DC and Power Characteristics

| Parameter | Description                    | Conditions                                          | Temp.                  | Min. | Тур. | Max. | Unit |

|-----------|--------------------------------|-----------------------------------------------------|------------------------|------|------|------|------|

| IJTAG     | JTAG I/O quiescent<br>current  | Operational standb <sup>4</sup> y<br>VJTAG = 3.63 V | T <sub>J</sub> = 25°C  |      | 80   | 100  | μA   |

|           |                                |                                                     | T <sub>J</sub> = 85°C  |      | 80   | 100  | μA   |

|           |                                |                                                     | T <sub>J</sub> = 100°C |      | 80   | 100  | μA   |

|           |                                | Standby mod휻 or Sleep modê,<br>VJTAG = O V          |                        |      | 0    | 0    | μA   |

| IPP       | Programming supply<br>current  | Non-programming mode,<br>VPUMP = 3.63 V             | T <sub>J</sub> = 25°C  |      | 39   | 80   | μA   |

|           |                                |                                                     | T <sub>J</sub> = 85°C  |      | 40   | 80   | μA   |

|           |                                |                                                     | T <sub>J</sub> = 100°C |      | 40   | 80   | μA   |

|           |                                | Standby mod휻 or Sleep modê,<br>VPUMP = 0 V          |                        |      | 0    | 0    | μA   |

| ICCNVM    | Embedded NVM<br>current        | Reset asserted, $ eq_{CNVM} = 1.575 V$              | Ţ = 25°C               |      | 50   | 150  | μA   |

|           |                                |                                                     | T <sub>J</sub> =85°C   |      | 50   | 150  | μA   |

|           |                                |                                                     | T <sub>J</sub> = 100°C |      | 50   | 150  | μA   |

| ICCPLL    | 1.5 V PLL quiescent<br>current | Operational standby<br>, VCCPLL = 1.575 V           | T <sub>J</sub> = 25°C  |      | 130  | 200  | μA   |

|           |                                |                                                     | T <sub>J</sub> = 85°C  |      | 130  | 200  | μA   |

|           |                                |                                                     | T <sub>J</sub> = 100°C |      | 130  | 200  | μA   |

| Table 3-8 | AFS1500 Quiescent Supply Current Characteristics (continued) |

|-----------|--------------------------------------------------------------|

|-----------|--------------------------------------------------------------|

Notes:

2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

3. ICCI includes all ICCI0, ICCI1, ICCI2, and ICCI4.

4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

6. Sleep Mode, VCC = VJTAG = VPUMP = 0 V.

<sup>1.</sup> ICC is the 1.5 V power supplies, ICC and ICC15A.

| Symbol                        | Parameter                                          | Commercial    | Industrial    | Units |

|-------------------------------|----------------------------------------------------|---------------|---------------|-------|

| AV, AC                        | Unpowered, ADC reset asserted or unconfigured      | -11.0 to 12.6 | -11.0 to 12.0 | V     |

|                               | Analog input (+16 V to +2 V prescaler range)       | -0.4 to 12.6  | -0.4 to 12.0  | V     |

|                               | Analog input (+1 V to +0.125 V prescaler range)    | -0.4 to 3.75  | -0.4 to 3.75  | V     |

|                               | Analog input (–16 V to –2 V prescaler range)       | -11.0 to 0.4  | -11.0 to 0.4  | V     |

|                               | Analog input (–1 V to –0.125 V prescaler range)    | -3.75 to 0.4  | -3.75 to 0.4  | V     |

|                               | Analog input (direct input to ADC)                 | -0.4 to 3.75  | -0.4 to 3.75  | V     |

|                               | Digital input                                      | -0.4 to 12.6  | -0.4 to 12.0  | V     |

| AG                            | Unpowered, ADC reset asserted or unconfigured      | -11.0 to 12.6 | -11.0 to 12.0 | V     |

|                               | Low Current Mode (1 µA, 3 µA, 10 µA, 30 µA)        | -0.4 to 12.6  | -0.4 to 12.0  | V     |

|                               | Low Current Mode (–1 μΑ, –3 μΑ, –10 μΑ, –30<br>μΑ) | -11.0 to 0.4  | -11.0 to 0.4  | V     |

|                               | High Current Mode <sup>3</sup>                     | -11.0 to 12.6 | -11.0 to 12.0 | V     |

| AT                            | Unpowered, ADC reset asserted or unconfigured      | -0.4 to 16.0  | –0.4 to 15.0  | V     |

|                               | Analog input (+16 V, 4 V prescaler range)          | -0.4 to 16.0  | -0.4 to 15.0  | V     |

|                               | Analog input (direct input to ADC)                 | -0.4 to 3.75  | -0.4 to 3.75  | V     |

|                               | Digital input                                      | -0.4 to 16.0  | -0.4 to 15.0  | V     |

| T <sub>STG</sub> <sup>4</sup> | Storage temperature                                | -65           | °C            |       |

| T <sub>J</sub> <sup>4</sup>   | Junction temperature                               | +125          |               | °C    |

| Table 3-1 • | Absolute | Maximum | Ratings | (continued) |

|-------------|----------|---------|---------|-------------|

|-------------|----------|---------|---------|-------------|

Notes:

1. The device should be operated within the limits specified by the datasheet. During transitions, the input signal may undershoot or overshoot according to the limits shown in Table 3-4 on page 3-4.

2. Analog data not valid beyond 3.65 V.

3. The high current mode has a maximum power limit of 20 mW. Appropriate current limit resistors must be used, based on voltage on the pad.

4. For flash programming and retention maximum limits, refer to Table 3-5 on page 3-5. For recommended operating limits refer to Table 3-2 on page 3-3.