Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                      |

|--------------------------------|-----------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | ·                                                                           |

| Total RAM Bits                 | 276480                                                                      |

| Number of I/O                  | 119                                                                         |

| Number of Gates                | 1500000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                             |

| Package / Case                 | 256-LBGA                                                                    |

| Supplier Device Package        | 256-FPBGA (17x17)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1afs1500-2fgg256 |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                             |   | Byte Number in Bank |    |    |    |    | 4  | 4 LSB of ADDR (READ) |   |   |   |   |   |   |   |   |   |

|-----------------------------|---|---------------------|----|----|----|----|----|----------------------|---|---|---|---|---|---|---|---|---|

|                             |   | 15                  | 14 | 13 | 12 | 11 | 10 | 9                    | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Ba<br>3 N                   | 7 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| Bank Number<br>3 MSB of ADI | 6 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| of                          | 5 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| AD                          | 4 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

|                             | 3 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| (R                          | 2 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| lumber<br>of ADDR (READ)    | 1 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

| 9                           | 0 |                     |    |    |    |    |    |                      |   |   |   |   |   |   |   |   |   |

### Figure 2-45 • FlashROM Architecture

# FlashROM Characteristics

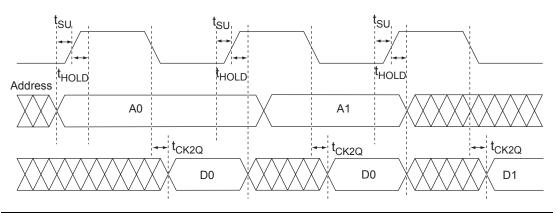

Figure 2-46 • FlashROM Timing Diagram

#### Table 2-26 • FlashROM Access Time

# Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter         | Description             | -2    | -1    | Std.  | Units |

|-------------------|-------------------------|-------|-------|-------|-------|

| t <sub>SU</sub>   | Address Setup Time      | 0.53  | 0.61  | 0.71  | ns    |

| t <sub>HOLD</sub> | Address Hold Time       | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>CK2Q</sub> | Clock to Out            | 21.42 | 24.40 | 28.68 | ns    |

| F <sub>MAX</sub>  | Maximum Clock frequency | 15.00 | 15.00 | 15.00 | MHz   |

# **SRAM** and **FIFO**

All Fusion devices have SRAM blocks along the north side of the device. Additionally, AFS600 and AFS1500 devices have an SRAM block on the south side of the device. To meet the needs of high-performance designs, the memory blocks operate strictly in synchronous mode for both read and write operations. The read and write clocks are completely independent, and each may operate at any desired frequency less than or equal to 350 MHz. The following configurations are available:

- 4k×1, 2k×2, 1k×4, 512×9 (dual-port RAM—two read, two write or one read, one write)

- 512×9, 256×18 (two-port RAM—one read and one write)

- Sync write, sync pipelined/nonpipelined read

The Fusion SRAM memory block includes dedicated FIFO control logic to generate internal addresses and external flag logic (FULL, EMPTY, AFULL, AEMPTY).

During RAM operation, addresses are sourced by the user logic, and the FIFO controller is ignored. In FIFO mode, the internal addresses are generated by the FIFO controller and routed to the RAM array by internal MUXes. Refer to Figure 2-47 for more information about the implementation of the embedded FIFO controller.

The Fusion architecture enables the read and write sizes of RAMs to be organized independently, allowing for bus conversion. This is done with the WW (write width) and RW (read width) pins. The different D×W configurations are  $256 \times 18$ ,  $512 \times 9$ ,  $1k \times 4$ ,  $2k \times 2$ , and  $4k \times 1$ . For example, the write size can be set to  $256 \times 18$  and the read size to  $512 \times 9$ .

Both the write and read widths for the RAM blocks can be specified independently with the WW (write width) and RW (read width) pins. The different D×W configurations are 256×18, 512×9, 1k×4, 2k×2, and 4k×1.

Refer to the allowable RW and WW values supported for each of the RAM macro types in Table 2-27 on page 2-58.

When a width of one, two, or four is selected, the ninth bit is unused. For example, when writing 9-bit values and reading 4-bit values, only the first four bits and the second four bits of each 9-bit value are addressable for read operations. The ninth bit is not accessible.

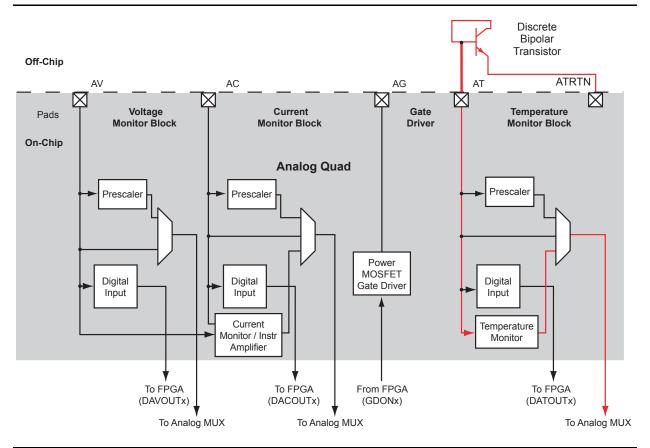

# **Temperature Monitor**

The final pin in the Analog Quad is the Analog Temperature (AT) pin. The AT pin is used to implement an accurate temperature monitor in conjunction with an external diode-connected bipolar transistor (Figure 2-76). For improved temperature measurement accuracy, it is important to use the ATRTN pin for the return path of the current sourced by the AT pin. Each ATRTN pin is shared between two adjacent Analog Quads. Additionally, if not used for temperature monitoring, the AT pin can provide functionality similar to that of the AV pad. However, in this mode only positive voltages can be applied to the AT pin, and only two prescaler factors are available (16 V and 4 V ranges—refer to Table 2-57 on page 2-130).

Figure 2-76 • Temperature Monitor Quad

Device Architecture

#### Integrated Voltage Reference

The Fusion device has an integrated on-chip 2.56 V reference voltage for the ADC. The value of this reference voltage was chosen to make the prescaling and postscaling factors for the prescaler blocks change in a binary fashion. However, if desired, an external reference voltage of up to 3.3 V can be connected between the VAREF and ADCGNDREF pins. The VAREFSEL control pin is used to select the reference voltage.

Table 2-42 • VAREF Bit Function

| Name  | Bit | Function                                                           |

|-------|-----|--------------------------------------------------------------------|

| VAREF | 0   | Reference voltage selection                                        |

|       |     | 0 – Internal voltage reference selected. VAREF pin outputs 2.56 V. |

|       |     | 1 – Input external voltage reference from VAREF and ADCGNDREF      |

#### ADC Clock

The speed of the ADC depends on its internal clock, ADCCLK, which is not accessible to users. The ADCCLK is derived from SYSCLK. Input signal TVC[7:0], Time Divider Control, determines the speed of the ADCCLK in relationship to SYSCLK, based on EQ 15.

$$t_{ADCCLK} = 4 \times (1 + TVC) \times t_{SYSCLK}$$

EQ 15

TVC: Time Divider Control (0-255)

$t_{\text{ADCCLK}}$  is the period of ADCCLK, and must be between 0.5 MHz and 10 MHz  $t_{\text{SYSCLK}}$  is the period of SYSCLK

#### Table 2-43 • TVC Bits Function

| Name | Bits  | Function               |

|------|-------|------------------------|

| TVC  | [7:0] | SYSCLK divider control |

The frequency of ADCCLK, f<sub>ADCCLK</sub>, must be within 0.5 Hz to 10 MHz.

The inputs to the ADC are synchronized to SYSCLK. A conversion is initiated by asserting the ADCSTART signal on a rising edge of SYSCLK. Figure 2-90 on page 2-112 and Figure 2-91 on page 2-112 show the timing diagram for the ADC.

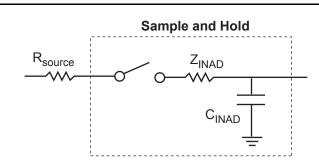

#### Acquisition Time or Sample Time Control

Acquisition time (t<sub>SAMPLE</sub>) specifies how long an analog input signal has to charge the internal capacitor array. Figure 2-88 shows a simplified internal input sampling mechanism of a SAR ADC.

#### Figure 2-88 • Simplified Sample and Hold Circuitry

The internal impedance ( $Z_{INAD}$ ), external source resistance ( $R_{SOURCE}$ ), and sample capacitor ( $C_{INAD}$ ) form a simple RC network. As a result, the accuracy of the ADC can be affected if the ADC is given insufficient time to charge the capacitor. To resolve this problem, you can either reduce the source resistance or increase the sampling time by changing the acquisition time using the STC signal.

# Features Supported on Pro I/Os

Table 2-72 lists all features supported by transmitter/receiver for single-ended and differential I/Os.

#### Table 2-72 • Fusion Pro I/O Features

| Feature                                             | Description                                                                                                                                                                                                                            |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single-ended and voltage-<br>referenced transmitter | <ul> <li>Hot insertion in every mode except PCI or 5 V input tolerant (these modes use<br/>clamp diodes and do not allow hot insertion)</li> </ul>                                                                                     |

| features                                            | Activation of hot insertion (disabling the clamp diode) is selectable by I/Os.                                                                                                                                                         |

|                                                     | Weak pull-up and pull-down                                                                                                                                                                                                             |

|                                                     | Two slew rates                                                                                                                                                                                                                         |

|                                                     | <ul> <li>Skew between output buffer enable/disable time: 2 ns delay (rising edge) and<br/>0 ns delay (falling edge); see "Selectable Skew between Output Buffer<br/>Enable/Disable Time" on page 2-149 for more information</li> </ul> |

|                                                     | Five drive strengths                                                                                                                                                                                                                   |

|                                                     | 5 V-tolerant receiver ("5 V Input Tolerance" section on page 2-144)                                                                                                                                                                    |

|                                                     | <ul> <li>LVTTL/LVCMOS 3.3 V outputs compatible with 5 V TTL inputs ("5 V Output<br/>Tolerance" section on page 2-148)</li> </ul>                                                                                                       |

|                                                     | High performance (Table 2-76 on page 2-143)                                                                                                                                                                                            |

| Single-ended receiver features                      | Schmitt trigger option                                                                                                                                                                                                                 |

|                                                     | ESD protection                                                                                                                                                                                                                         |

|                                                     | <ul> <li>Programmable delay: 0 ns if bypassed, 0.625 ns with '000' setting, 6.575 ns with '111' setting, 0.85-ns intermediate delay increments (at 25°C, 1.5 V)</li> </ul>                                                             |

|                                                     | High performance (Table 2-76 on page 2-143)                                                                                                                                                                                            |

|                                                     | <ul> <li>Separate ground planes, GND/GNDQ, for input buffers only to avoid output-<br/>induced noise in the input circuitry</li> </ul>                                                                                                 |

| Voltage-referenced differential receiver features   | <ul> <li>Programmable Delay: 0 ns if bypassed, 0.625 ns with '000' setting, 6.575 ns with '111' setting, 0.85-ns intermediate delay increments (at 25°C, 1.5 V)</li> </ul>                                                             |

|                                                     | High performance (Table 2-76 on page 2-143)                                                                                                                                                                                            |

|                                                     | <ul> <li>Separate ground planes, GND/GNDQ, for input buffers only to avoid output-<br/>induced noise in the input circuitry</li> </ul>                                                                                                 |

| CMOS-style LVDS, BLVDS,<br>M-LVDS, or LVPECL        | <ul> <li>Two I/Os and external resistors are used to provide a CMOS-style LVDS,<br/>BLVDS, M-LVDS, or LVPECL transmitter solution.</li> </ul>                                                                                          |

| transmitter                                         | Activation of hot insertion (disabling the clamp diode) is selectable by I/Os.                                                                                                                                                         |

|                                                     | Weak pull-up and pull-down                                                                                                                                                                                                             |

|                                                     | Fast slew rate                                                                                                                                                                                                                         |

| LVDS/LVPECL differential                            | ESD protection                                                                                                                                                                                                                         |

| receiver features                                   | High performance (Table 2-76 on page 2-143)                                                                                                                                                                                            |

|                                                     | <ul> <li>Programmable delay: 0.625 ns with '000' setting, 6.575 ns with '111' setting, 0.85-ns intermediate delay increments (at 25°C, 1.5 V)</li> </ul>                                                                               |

|                                                     | <ul> <li>Separate input buffer ground and power planes to avoid output-induced noise<br/>in the input circuitry</li> </ul>                                                                                                             |

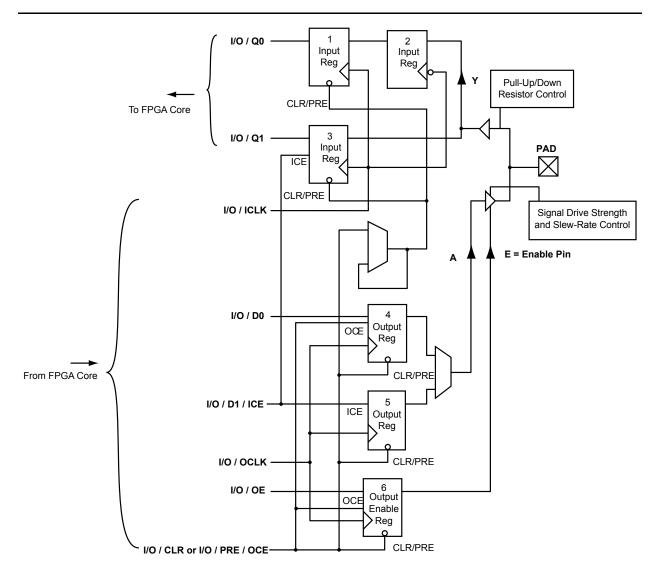

# **I/O Registers**

Each I/O module contains several input, output, and enable registers. Refer to Figure 2-100 for a simplified representation of the I/O block.

The number of input registers is selected by a set of switches (not shown in Figure 2-100) between registers to implement single or differential data transmission to and from the FPGA core. The Designer software sets these switches for the user.

A common CLR/PRE signal is employed by all I/O registers when I/O register combining is used. Input register 2 does not have a CLR/PRE pin, as this register is used for DDR implementation. The I/O register combining must satisfy some rules.

Note: Fusion I/Os have registers to support DDR functionality (see the "Double Data Rate (DDR) Support" section on page 2-139 for more information).

Figure 2-100 • I/O Block Logical Representation

Device Architecture

#### Table 2-81 • Fusion Pro I/O Default Attributes

| I/O Standards           | SLEW<br>(output only)                                                                          | OUT_DRIVE<br>(output only)                                  | SKEW (tribuf and bibuf only) | RES_PULL | OUT_LOAD (output only) | COMBINE_REGISTER | IN_DELAY (input only) | IN_DELAY_VAL (input only) | SCHMITT_TRIGGER (input only) |

|-------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------|----------|------------------------|------------------|-----------------------|---------------------------|------------------------------|

| LVTTL/LVCMO<br>S 3.3 V  | Refer to the following tables for more                                                         | Refer to the following tables for more information:         | Off                          | None     | 35 pF                  | -                | Off                   | 0                         | Off                          |

| LVCMOS 2.5 V            | information:<br>Table 2-78 on page 2-152                                                       | Table 2-78 on page 2-152                                    | Off                          | None     | 35 pF                  | -                | Off                   | 0                         | Off                          |

| LVCMOS<br>2.5/5.0 V     | Table 2-79 on page 2-152           Table 2-79 on page 2-152           Table 2-80 on page 2-152 | Table 2-79 on page 2-152           Table 2-80 on page 2-152 | Off                          | None     | 35 pF                  | -                | Off                   | 0                         | Off                          |

| LVCMOS 1.8 V            | 1able 2-00 011 page 2-152                                                                      | Table 2-00 off page 2-152                                   | Off                          | None     | 35 pF                  | -                | Off                   | 0                         | Off                          |

| LVCMOS 1.5 V            |                                                                                                |                                                             | Off                          | None     | 35 pF                  | -                | Off                   | 0                         | Off                          |

| PCI (3.3 V)             |                                                                                                |                                                             | Off                          | None     | 10 pF                  | -                | Off                   | 0                         | Off                          |

| PCI-X (3.3 V)           |                                                                                                |                                                             | Off                          | None     | 10 pF                  | -                | Off                   | 0                         | Off                          |

| GTL+ (3.3 V)            |                                                                                                |                                                             | Off                          | None     | 10 pF                  | —                | Off                   | 0                         | Off                          |

| GTL+ (2.5 V)            |                                                                                                |                                                             | Off                          | None     | 10 pF                  | _                | Off                   | 0                         | Off                          |

| GTL (3.3 V)             |                                                                                                |                                                             | Off                          | None     | 10 pF                  | -                | Off                   | 0                         | Off                          |

| GTL (2.5 V)             |                                                                                                |                                                             | Off                          | None     | 10 pF                  | -                | Off                   | 0                         | Off                          |

| HSTL Class I            |                                                                                                |                                                             | Off                          | None     | 20 pF                  | -                | Off                   | 0                         | Off                          |

| HSTL Class II           |                                                                                                |                                                             | Off                          | None     | 20 pF                  | -                | Off                   | 0                         | Off                          |

| SSTL2<br>Class I and II |                                                                                                |                                                             | Off                          | None     | 30 pF                  | -                | Off                   | 0                         | Off                          |

| SSTL3<br>Class I and II |                                                                                                |                                                             | Off                          | None     | 30 pF                  | -                | Off                   | 0                         | Off                          |

| LVDS, BLVDS,<br>M-LVDS  |                                                                                                |                                                             | Off                          | None     | 0 pF                   | -                | Off                   | 0                         | Off                          |

| LVPECL                  |                                                                                                |                                                             | Off                          | None     | 0 pF                   | -                | Off                   | 0                         | Off                          |

## Summary of I/O Timing Characteristics – Default I/O Software Settings

# Table 2-90 • Summary of AC Measuring Points Applicable to All I/O Bank Types

| Standard                   | Input Reference Voltage<br>(VREF_TYP) | Board Termination Voltage<br>(VTT_REF) | Measuring Trip Point<br>(Vtrip)         |  |  |

|----------------------------|---------------------------------------|----------------------------------------|-----------------------------------------|--|--|

| 3.3 V LVTTL / 3.3 V LVCMOS | -                                     | _                                      | 1.4 V                                   |  |  |

| 2.5 V LVCMOS               | _                                     | -                                      | 1.2 V                                   |  |  |

| 1.8 V LVCMOS               | _                                     | -                                      | 0.90 V                                  |  |  |

| 1.5 V LVCMOS               | _                                     | -                                      | 0.75 V                                  |  |  |

| 3.3 V PCI                  | -                                     | -                                      | 0.285 * VCCI (RR)<br>0.615 * VCCI (FF)) |  |  |

| 3.3 V PCI-X                | -                                     | -                                      | 0.285 * VCCI (RR)<br>0.615 * VCCI (FF)  |  |  |

| 3.3 V GTL                  | 0.8 V                                 | 1.2 V                                  | VREF                                    |  |  |

| 2.5 V GTL                  | 0.8 V                                 | 1.2 V                                  | VREF                                    |  |  |

| 3.3 V GTL+                 | 1.0 V                                 | 1.5 V                                  | VREF                                    |  |  |

| 2.5 V GTL+                 | 1.0 V                                 | 1.5 V                                  | VREF                                    |  |  |

| HSTL (I)                   | 0.75 V                                | 0.75 V                                 | VREF                                    |  |  |

| HSTL (II)                  | 0.75 V                                | 0.75 V                                 | VREF                                    |  |  |

| SSTL2 (I)                  | 1.25 V                                | 1.25 V                                 | VREF                                    |  |  |

| SSTL2 (II)                 | 1.25 V                                | 1.25 V                                 | VREF                                    |  |  |

| SSTL3 (I)                  | 1.5 V                                 | 1.485 V                                | VREF                                    |  |  |

| SSTL3 (II)                 | 1.5 V                                 | 1.485 V                                | VREF                                    |  |  |

| LVDS                       | _                                     | -                                      | Cross point                             |  |  |

| LVPECL                     | _                                     | -                                      | Cross point                             |  |  |

#### Table 2-91 • I/O AC Parameter Definitions

| Parameter         | Definition                                                                  |

|-------------------|-----------------------------------------------------------------------------|

| t <sub>DP</sub>   | Data to Pad delay through the Output Buffer                                 |

| t <sub>PY</sub>   | Pad to Data delay through the Input Buffer with Schmitt trigger disabled    |

| t <sub>DOUT</sub> | Data to Output Buffer delay through the I/O interface                       |

| t <sub>EOUT</sub> | Enable to Output Buffer Tristate Control delay through the I/O interface    |

| t <sub>DIN</sub>  | Input Buffer to Data delay through the I/O interface                        |

| t <sub>PYS</sub>  | Pad to Data delay through the Input Buffer with Schmitt trigger enabled     |

| t <sub>HZ</sub>   | Enable to Pad delay through the Output Buffer—High to Z                     |

| t <sub>ZH</sub>   | Enable to Pad delay through the Output Buffer—Z to High                     |

| t <sub>LZ</sub>   | Enable to Pad delay through the Output Buffer—Low to Z                      |

| t <sub>ZL</sub>   | Enable to Pad delay through the Output Buffer—Z to Low                      |

| t <sub>ZHS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to High |

| t <sub>ZLS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to Low  |

# Table 2-96 • I/O Output Buffer Maximum Resistances <sup>1</sup> (continued)

| Standard                      | Drive Strength              | R <sub>PULL-DOWN</sub><br>(ohms) <sup>2</sup> | R <sub>PULL-UP</sub><br>(ohms) <sup>3</sup> |

|-------------------------------|-----------------------------|-----------------------------------------------|---------------------------------------------|

| HSTL (I)                      | 8 mA                        | 50                                            | 50                                          |

| HSTL (II)                     | 15 mA                       | 25                                            | 25                                          |

| SSTL2 (I)                     | 17 mA                       | 27                                            | 31                                          |

| SSTL2 (II)                    | 21 mA                       | 13                                            | 15                                          |

| SSTL3 (I)                     | 16 mA                       | 44                                            | 69                                          |

| SSTL3 (II)                    | 24 mA                       | 18                                            | 32                                          |

| Applicable to Advanced I/O Ba | inks                        | I                                             |                                             |

| 3.3 V LVTTL / 3.3 V LVCMOS    | 2 mA                        | 100                                           | 300                                         |

|                               | 4 mA                        | 100                                           | 300                                         |

|                               | 6 mA                        | 50                                            | 150                                         |

|                               | 8 mA                        | 50                                            | 150                                         |

|                               | 12 mA                       | 25                                            | 75                                          |

|                               | 16 mA                       | 17                                            | 50                                          |

|                               | 24 mA                       | 11                                            | 33                                          |

| 2.5 V LVCMOS                  | 2 mA                        | 100                                           | 200                                         |

|                               | 4 mA                        | 100                                           | 200                                         |

|                               | 6 mA                        | 50                                            | 100                                         |

|                               | 8 mA                        | 50                                            | 100                                         |

|                               | 12 mA                       | 25                                            | 50                                          |

|                               | 16 mA                       | 20                                            | 40                                          |

|                               | 24 mA                       | 11                                            | 22                                          |

| 1.8 V LVCMOS                  | 2 mA                        | 200                                           | 225                                         |

|                               | 4 mA                        | 100                                           | 112                                         |

|                               | 6 mA                        | 50                                            | 56                                          |

|                               | 8 mA                        | 50                                            | 56                                          |

|                               | 12 mA                       | 20                                            | 22                                          |

|                               | 16 mA                       | 20                                            | 22                                          |

| 1.5 V LVCMOS                  | 2 mA                        | 200                                           | 224                                         |

|                               | 4 mA                        | 100                                           | 112                                         |

|                               | 6 mA                        | 67                                            | 75                                          |

|                               | 8 mA                        | 33                                            | 37                                          |

|                               | 12 mA                       | 33                                            | 37                                          |

| 3.3 V PCI/PCI-X               | Per PCI/PCI-X specification | 25                                            | 75                                          |

Notes:

These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCC, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website: http://www.microsemi.com/soc/techdocs/models/ibis.html.

2. R<sub>(PULL-DOWN-MAX)</sub> = VOLspec / I<sub>OLspec</sub>

3. R<sub>(PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / IOHspec

# Table 2-117 • 2.5 V LVCMOS High Slew<br/>Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,<br/>Worst-Case VCCI = 2.3 V<br/>Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 8.20            | 0.04             | 1.29            | 0.43              | 7.24            | 8.20            | 2.03            | 1.91            | ns    |

|                   | -1             | 0.56              | 6.98            | 0.04             | 1.10            | 0.36              | 6.16            | 6.98            | 1.73            | 1.62            | ns    |

|                   | -2             | 0.49              | 6.13            | 0.03             | 0.96            | 0.32              | 5.41            | 6.13            | 1.52            | 1.43            | ns    |

| 4 mA              | Std.           | 0.66              | 8.20            | 0.04             | 1.29            | 0.43              | 7.24            | 8.20            | 2.03            | 1.91            | ns    |

|                   | -1             | 0.56              | 6.98            | 0.04             | 1.10            | 0.36              | 6.16            | 6.98            | 1.73            | 1.62            | ns    |

|                   | -2             | 0.49              | 6.13            | 0.03             | 0.96            | 0.32              | 5.41            | 6.13            | 1.52            | 1.43            | ns    |

| 6 mA              | Std.           | 0.66              | 4.77            | 0.04             | 1.29            | 0.43              | 4.55            | 4.77            | 2.38            | 2.55            | ns    |

|                   | -1             | 0.56              | 4.05            | 0.04             | 1.10            | 0.36              | 3.87            | 4.05            | 2.03            | 2.17            | ns    |

|                   | -2             | 0.49              | 3.56            | 0.03             | 0.96            | 0.32              | 3.40            | 3.56            | 1.78            | 1.91            | ns    |

| 8 mA              | Std.           | 0.66              | 4.77            | 0.04             | 1.29            | 0.43              | 4.55            | 4.77            | 2.38            | 2.55            | ns    |

|                   | -1             | 0.56              | 4.05            | 0.04             | 1.10            | 0.36              | 3.87            | 4.05            | 2.03            | 2.17            | ns    |

|                   | -2             | 0.49              | 3.56            | 0.03             | 0.96            | 0.32              | 3.40            | 3.56            | 1.78            | 1.91            | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

#### Table 2-122 • 1.8 V LVCMOS Low Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V Applicable to Advanced I/Os

| Drive<br>Strength | Speed<br>Grade  | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|-----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.            | 0.66              | 15.53           | 0.04             | 1.31            | 0.43              | 14.11           | 15.53           | 2.78            | 1.60            | 16.35            | 17.77            | ns    |

|                   | -1              | 0.56              | 13.21           | 0.04             | 1.11            | 0.36              | 12.01           | 13.21           | 2.36            | 1.36            | 13.91            | 15.11            | ns    |

|                   | -2 <sup>2</sup> | 0.49              | 11.60           | 0.03             | 0.98            | 0.32              | 10.54           | 11.60           | 2.07            | 1.19            | 12.21            | 13.27            | ns    |

| 4 mA              | Std.            | 0.66              | 10.48           | 0.04             | 1.31            | 0.43              | 10.41           | 10.48           | 3.23            | 2.73            | 12.65            | 12.71            | ns    |

|                   | -1              | 0.56              | 8.91            | 0.04             | 1.11            | 0.36              | 8.86            | 8.91            | 2.75            | 2.33            | 10.76            | 10.81            | ns    |

|                   | -2              | 0.49              | 7.82            | 0.03             | 0.98            | 0.32              | 7.77            | 7.82            | 2.41            | 2.04            | 9.44             | 9.49             | ns    |

| 8 mA              | Std.            | 0.66              | 8.05            | 0.04             | 1.31            | 0.43              | 8.20            | 7.84            | 3.54            | 3.27            | 10.43            | 10.08            | ns    |

|                   | -1              | 0.56              | 6.85            | 0.04             | 1.11            | 0.36              | 6.97            | 6.67            | 3.01            | 2.78            | 8.88             | 8.57             | ns    |

|                   | -2              | 0.49              | 6.01            | 0.03             | 0.98            | 0.32              | 6.12            | 5.86            | 2.64            | 2.44            | 7.79             | 7.53             | ns    |

| 12 mA             | Std.            | 0.66              | 7.50            | 0.04             | 1.31            | 0.43              | 7.64            | 7.30            | 3.61            | 3.41            | 9.88             | 9.53             | ns    |

|                   | -1              | 0.56              | 6.38            | 0.04             | 1.11            | 0.36              | 6.50            | 6.21            | 3.07            | 2.90            | 8.40             | 8.11             | ns    |

|                   | -2              | 0.49              | 5.60            | 0.03             | 0.98            | 0.32              | 5.71            | 5.45            | 2.69            | 2.55            | 7.38             | 7.12             | ns    |

| 16 mA             | Std.            | 0.66              | 7.29            | 0.04             | 1.31            | 0.43              | 7.23            | 7.29            | 3.71            | 3.95            | 9.47             | 9.53             | ns    |

|                   | -1              | 0.56              | 6.20            | 0.04             | 1.11            | 0.36              | 6.15            | 6.20            | 3.15            | 3.36            | 8.06             | 8.11             | ns    |

|                   | -2              | 0.49              | 5.45            | 0.03             | 0.98            | 0.32              | 5.40            | 5.45            | 2.77            | 2.95            | 7.07             | 7.12             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

#### Timing Characteristics

Table 2-128 • 1.5 V LVCMOS Low Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Pro I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 14.11           | 0.04             | 1.70            | 2.14             | 0.43              | 14.37           | 13.14           | 3.40            | 2.68            | 16.61            | 15.37            | ns    |

|                   | -1             | 0.56              | 12.00           | 0.04             | 1.44            | 1.82             | 0.36              | 12.22           | 11.17           | 2.90            | 2.28            | 14.13            | 13.08            | ns    |

|                   | -2             | 0.49              | 10.54           | 0.03             | 1.27            | 1.60             | 0.32              | 10.73           | 9.81            | 2.54            | 2.00            | 12.40            | 11.48            | ns    |

| 4 mA              | Std.           | 0.66              | 11.23           | 0.04             | 1.70            | 2.14             | 0.43              | 11.44           | 9.87            | 3.77            | 3.36            | 13.68            | 12.10            | ns    |

|                   | -1             | 0.56              | 9.55            | 0.04             | 1.44            | 1.82             | 0.36              | 9.73            | 8.39            | 3.21            | 2.86            | 11.63            | 10.29            | ns    |

|                   | -2             | 0.49              | 8.39            | 0.03             | 1.27            | 1.60             | 0.32              | 8.54            | 7.37            | 2.81            | 2.51            | 10.21            | 9.04             | ns    |

| 8 mA              | Std.           | 0.66              | 10.45           | 0.04             | 1.70            | 2.14             | 0.43              | 10.65           | 9.24            | 3.84            | 3.55            | 12.88            | 11.48            | ns    |

|                   | -1             | 0.56              | 8.89            | 0.04             | 1.44            | 1.82             | 0.36              | 9.06            | 7.86            | 3.27            | 3.02            | 10.96            | 9.76             | ns    |

|                   | -2             | 0.49              | 7.81            | 0.03             | 1.27            | 1.60             | 0.32              | 7.95            | 6.90            | 2.87            | 2.65            | 9.62             | 8.57             | ns    |

| 12 mA             | Std.           | 0.66              | 10.02           | 0.04             | 1.70            | 2.14             | 0.43              | 10.20           | 9.23            | 3.97            | 4.22            | 12.44            | 11.47            | ns    |

|                   | –1             | 0.56              | 8.52            | 0.04             | 1.44            | 1.82             | 0.36              | 8.68            | 7.85            | 3.38            | 3.59            | 10.58            | 9.75             | ns    |

|                   | -2             | 0.49              | 7.48            | 0.03             | 1.27            | 1.60             | 0.32              | 7.62            | 6.89            | 2.97            | 3.15            | 9.29             | 8.56             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

#### Table 2-129 • 1.5 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V Applicable to Pro I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOU</sub><br>т | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-----------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 8.53            | 0.04             | 1.70            | 2.14             | 0.43                  | 7.26            | 8.53            | 3.39            | 2.79            | 9.50             | 10.77            | ns    |

|                   | -1             | 0.56              | 7.26            | 0.04             | 1.44            | 1.82             | 0.36                  | 6.18            | 7.26            | 2.89            | 2.37            | 8.08             | 9.16             | ns    |

|                   | -2             | 0.49              | 6.37            | 0.03             | 1.27            | 1.60             | 0.32                  | 5.42            | 6.37            | 2.53            | 2.08            | 7.09             | 8.04             | ns    |

| 4 mA              | Std.           | 0.66              | 5.41            | 0.04             | 1.70            | 2.14             | 0.43                  | 5.22            | 5.41            | 3.75            | 3.48            | 7.45             | 7.65             | ns    |

|                   | -1             | 0.56              | 4.60            | 0.04             | 1.44            | 1.82             | 0.36                  | 4.44            | 4.60            | 3.19            | 2.96            | 6.34             | 6.50             | ns    |

|                   | -2             | 0.49              | 4.04            | 0.03             | 1.27            | 1.60             | 0.32                  | 3.89            | 4.04            | 2.80            | 2.60            | 5.56             | 5.71             | ns    |

| 8 mA              | Std.           | 0.66              | 4.80            | 0.04             | 1.70            | 2.14             | 0.43                  | 4.89            | 4.75            | 3.83            | 3.67            | 7.13             | 6.98             | ns    |

|                   | -1             | 0.56              | 4.09            | 0.04             | 1.44            | 1.82             | 0.36                  | 4.16            | 4.04            | 3.26            | 3.12            | 6.06             | 5.94             | ns    |

|                   | -2             | 0.49              | 3.59            | 0.03             | 1.27            | 1.60             | 0.32                  | 3.65            | 3.54            | 2.86            | 2.74            | 5.32             | 5.21             | ns    |

| 12 mA             | Std.           | 0.66              | 4.42            | 0.04             | 1.70            | 2.14             | 0.43                  | 4.50            | 3.62            | 3.96            | 4.37            | 6.74             | 5.86             | ns    |

|                   | -1             | 0.56              | 3.76            | 0.04             | 1.44            | 1.82             | 0.36                  | 3.83            | 3.08            | 3.37            | 3.72            | 5.73             | 4.98             | ns    |

|                   | -2             | 0.49              | 3.30            | 0.03             | 1.27            | 1.60             | 0.32                  | 3.36            | 2.70            | 2.96            | 3.27            | 5.03             | 4.37             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

| Parameter          | Description                | Conditions                                                            | Temp.                  | Min | Тур  | Мах | Unit |

|--------------------|----------------------------|-----------------------------------------------------------------------|------------------------|-----|------|-----|------|

| ICC <sup>1</sup>   | 1.5 V quiescent current    | Operational standby <sup>4</sup> ,                                    | T <sub>J</sub> = 25°C  |     | 13   | 25  | mA   |

|                    |                            | VCC = 1.575 V                                                         | T <sub>J</sub> = 85°C  |     | 20   | 45  | mA   |

|                    |                            |                                                                       | T <sub>J</sub> =100°C  |     | 25   | 75  | mA   |

|                    |                            | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , VCC = 0 V   |                        |     | 0    | 0   | μA   |

| ICC33 <sup>2</sup> | 3.3 V analog supplies      | Operational standby <sup>4</sup> ,                                    | T <sub>J</sub> = 25°C  |     | 9.8  | 13  | mA   |

|                    | current                    | VCC33 = 3.63 V                                                        | T <sub>J</sub> = 85°C  |     | 10.7 | 14  | mA   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 10.8 | 15  | mA   |

|                    |                            | Operational standby,                                                  | T <sub>J</sub> = 25°C  |     | 0.31 | 2   | mA   |

|                    |                            | only Analog Quad and -3.3 V<br>output ON, VCC33 = 3.63 V              | T <sub>J</sub> = 85°C  |     | 0.35 | 2   | mA   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 0.45 | 2   | mA   |

|                    |                            | Standby mode <sup>5</sup> ,                                           | T <sub>J</sub> = 25°C  |     | 2.8  | 3.6 | mA   |

|                    |                            | VCC33 = 3.63 V                                                        | T <sub>J</sub> = 85°C  |     | 2.9  | 4   | mA   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 3.5  | 6   | mA   |

|                    |                            | Sleep mode <sup>6</sup> , V <sub>CC33</sub> = 3.63 V                  | T <sub>J</sub> = 25°C  |     | 17   | 19  | μA   |

|                    |                            |                                                                       | T <sub>J</sub> = 85°C  |     | 18   | 20  | μA   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 24   | 25  | μA   |

| ICCI <sup>3</sup>  | I/O quiescent current      | Operational standby <sup>4</sup> ,                                    | T <sub>J</sub> = 25°C  |     | 417  | 648 | μA   |

|                    |                            | VCCIx = 3.63 V                                                        | T <sub>J</sub> = 85°C  |     | 417  | 648 | μA   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 417  | 649 | μA   |

| IJTAG              | JTAG I/O quiescent current | Operational standby <sup>4</sup> ,                                    | T <sub>J</sub> = 25°C  |     | 80   | 100 | μA   |

|                    |                            | VJTAG = 3.63 V                                                        | T <sub>J</sub> = 85°C  |     | 80   | 100 | μA   |

|                    |                            |                                                                       | T <sub>J</sub> = 100°C |     | 80   | 100 | μA   |

|                    |                            | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , VJTAG = 0 V |                        |     | 0    | 0   | μA   |

Notes:

1. ICC is the 1.5 V power supplies, ICC and ICC15A.

2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

3. ICCI includes all ICCI0, ICCI1, ICCI2, and ICCI4.

4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

6. Sleep Mode, VCC = VJTAG = VPUMP = 0 V.

|            |                 | FG256           |                 |                  |

|------------|-----------------|-----------------|-----------------|------------------|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |

| K9         | VCC             | VCC             | VCC             | VCC              |

| K10        | GND             | GND             | GND             | GND              |

| K11        | NC              | GDC2/IO57PPB1V0 | GDC2/IO57PPB2V0 | GDC2/IO84PPB2V0  |

| K12        | GND             | GND             | GND             | GND              |

| K13        | NC              | GDA0/IO54NDB1V0 | GDA0/IO54NDB2V0 | GDA0/IO81NDB2V0  |

| K14        | NC              | GDA2/IO55PPB1V0 | GDA2/IO55PPB2V0 | GDA2/IO82PPB2V0  |

| K15        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |

| K16        | NC              | GDB1/IO53PPB1V0 | GDB1/IO53PPB2V0 | GDB1/IO80PPB2V0  |

| L1         | NC              | GEC1/IO63PDB3V0 | GEC1/IO63PDB4V0 | GEC1/IO90PDB4V0  |

| L2         | NC              | GEC0/IO63NDB3V0 | GEC0/IO63NDB4V0 | GEC0/IO90NDB4V0  |

| L3         | NC              | GEB1/IO62PDB3V0 | GEB1/IO62PDB4V0 | GEB1/IO89PDB4V0  |

| L4         | NC              | GEB0/IO62NDB3V0 | GEB0/IO62NDB4V0 | GEB0/IO89NDB4V0  |

| L5         | NC              | IO60NDB3V0      | IO60NDB4V0      | IO87NDB4V0       |

| L6         | NC              | GEC2/IO60PDB3V0 | GEC2/IO60PDB4V0 | GEC2/IO87PDB4V0  |

| L7         | GNDA            | GNDA            | GNDA            | GNDA             |

| L8         | AC0             | AC0             | AC2             | AC2              |

| L9         | AV2             | AV2             | AV4             | AV4              |

| L10        | AC3             | AC3             | AC5             | AC5              |

| L11        | PTEM            | PTEM            | PTEM            | PTEM             |

| L12        | TDO             | TDO             | TDO             | TDO              |

| L13        | VJTAG           | VJTAG           | VJTAG           | VJTAG            |

| L14        | NC              | IO57NPB1V0      | IO57NPB2V0      | IO84NPB2V0       |

| L15        | GDB2/IO41PPB1V0 | GDB2/IO56PPB1V0 | GDB2/IO56PPB2V0 | GDB2/IO83PPB2V0  |

| L16        | NC              | IO55NPB1V0      | IO55NPB2V0      | IO82NPB2V0       |

| M1         | GND             | GND             | GND             | GND              |

| M2         | NC              | GEA1/IO61PDB3V0 | GEA1/IO61PDB4V0 | GEA1/IO88PDB4V0  |

| M3         | NC              | GEA0/IO61NDB3V0 | GEA0/IO61NDB4V0 | GEA0/IO88NDB4V0  |

| M4         | VCCIB3          | VCCIB3          | VCCIB4          | VCCIB4           |

| M5         | NC              | IO58NPB3V0      | IO58NPB4V0      | IO85NPB4V0       |

| M6         | NC              | NC              | AV0             | AV0              |

| M7         | NC              | NC              | AC1             | AC1              |

| M8         | AG1             | AG1             | AG3             | AG3              |

| M9         | AC2             | AC2             | AC4             | AC4              |

| M10        | AC4             | AC4             | AC6             | AC6              |

| M11        | NC              | AG5             | AG7             | AG7              |

| M12        | VPUMP           | VPUMP           | VPUMP           | VPUMP            |

| M13        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |

| M14        | TMS             | TMS             | TMS             | TMS              |

# **Microsemi**

Package Pin Assignments

| FG676      |                  |            | FG676            |            | FG676            |  |  |  |

|------------|------------------|------------|------------------|------------|------------------|--|--|--|

| Pin Number | AFS1500 Function | Pin Number | AFS1500 Function | Pin Number | AFS1500 Function |  |  |  |

| A1         | NC               | AA11       | AV2              | AB21       | PTBASE           |  |  |  |

| A2         | GND              | AA12       | GNDA             | AB22       | GNDNVM           |  |  |  |

| A3         | NC               | AA13       | AV3              | AB23       | VCCNVM           |  |  |  |

| A4         | NC               | AA14       | AV6              | AB24       | VPUMP            |  |  |  |

| A5         | GND              | AA15       | GNDA             | AB25       | NC               |  |  |  |

| A6         | NC               | AA16       | AV7              | AB26       | GND              |  |  |  |

| A7         | NC               | AA17       | AV8              | AC1        | NC               |  |  |  |

| A8         | GND              | AA18       | GNDA             | AC2        | NC               |  |  |  |

| A9         | IO17NDB0V2       | AA19       | AV9              | AC3        | NC               |  |  |  |

| A10        | IO17PDB0V2       | AA20       | VCCIB2           | AC4        | GND              |  |  |  |

| A11        | GND              | AA21       | IO68PPB2V0       | AC5        | VCCIB4           |  |  |  |

| A12        | IO18NDB0V2       | AA22       | ТСК              | AC6        | VCCIB4           |  |  |  |

| A13        | IO18PDB0V2       | AA23       | GND              | AC7        | PCAP             |  |  |  |

| A14        | IO20NDB0V2       | AA24       | IO76PPB2V0       | AC8        | AG0              |  |  |  |

| A15        | IO20PDB0V2       | AA25       | VCCIB2           | AC9        | GNDA             |  |  |  |

| A16        | GND              | AA26       | NC               | AC10       | AG1              |  |  |  |

| A17        | IO21PDB0V2       | AB1        | GND              | AC11       | AG2              |  |  |  |

| A18        | IO21NDB0V2       | AB2        | NC               | AC12       | GNDA             |  |  |  |

| A19        | GND              | AB3        | GEC2/IO87PDB4V0  | AC13       | AG3              |  |  |  |

| A20        | IO39NDB1V2       | AB4        | IO87NDB4V0       | AC14       | AG6              |  |  |  |

| A21        | IO39PDB1V2       | AB5        | GEA2/IO85PDB4V0  | AC15       | GNDA             |  |  |  |

| A22        | GND              | AB6        | IO85NDB4V0       | AC16       | AG7              |  |  |  |

| A23        | NC               | AB7        | NCAP             | AC17       | AG8              |  |  |  |

| A24        | NC               | AB8        | AC0              | AC18       | GNDA             |  |  |  |

| A25        | GND              | AB9        | VCC33A           | AC19       | AG9              |  |  |  |

| A26        | NC               | AB10       | AC1              | AC20       | VAREF            |  |  |  |

| AA1        | NC               | AB11       | AC2              | AC21       | VCCIB2           |  |  |  |

| AA2        | VCCIB4           | AB12       | VCC33A           | AC22       | PTEM             |  |  |  |

| AA3        | IO93PDB4V0       | AB13       | AC3              | AC23       | GND              |  |  |  |

| AA4        | GND              | AB14       | AC6              | AC24       | NC               |  |  |  |

| AA5        | IO93NDB4V0       | AB15       | VCC33A           | AC25       | NC               |  |  |  |

| AA6        | GEB2/IO86PDB4V0  | AB16       | AC7              | AC26       | NC               |  |  |  |

| AA7        | IO86NDB4V0       | AB17       | AC8              | AD1        | NC               |  |  |  |

| AA8        | AV0              | AB18       | VCC33A           | AD2        | NC               |  |  |  |

| AA9        | GNDA             | AB19       | AC9              | AD3        | GND              |  |  |  |

| AA10       | AV1              | AB20       | ADCGNDREF        | AD4        | NC               |  |  |  |

# 🌜 Microsemi.

Package Pin Assignments

|            | FG676            |            | FG676            |            | FG676            |

|------------|------------------|------------|------------------|------------|------------------|

| Pin Number | AFS1500 Function | Pin Number | AFS1500 Function | Pin Number | AFS1500 Function |

| L17        | VCCIB2           | N1         | NC               | P11        | VCC              |

| L18        | GCB2/IO60PDB2V0  | N2         | NC               | P12        | GND              |

| L19        | IO58NDB2V0       | N3         | IO108NDB4V0      | P13        | VCC              |

| L20        | IO57NDB2V0       | N4         | VCCOSC           | P14        | GND              |

| L21        | IO59NDB2V0       | N5         | VCCIB4           | P15        | VCC              |

| L22        | GCC2/IO61PDB2V0  | N6         | XTAL2            | P16        | GND              |

| L23        | IO55PPB2V0       | N7         | GFC1/IO107PDB4V0 | P17        | VCCIB2           |

| L24        | IO56PDB2V0       | N8         | VCCIB4           | P18        | IO70NDB2V0       |

| L25        | IO55NPB2V0       | N9         | GFB1/IO106PDB4V0 | P19        | VCCIB2           |

| L26        | GND              | N10        | VCCIB4           | P20        | IO69NDB2V0       |

| M1         | NC               | N11        | GND              | P21        | GCA0/IO64NDB2V0  |

| M2         | VCCIB4           | N12        | VCC              | P22        | VCCIB2           |

| M3         | GFC2/IO108PDB4V0 | N13        | GND              | P23        | GCB0/IO63NDB2V0  |

| M4         | GND              | N14        | VCC              | P24        | GCB1/IO63PDB2V0  |

| M5         | IO109NDB4V0      | N15        | GND              | P25        | IO66NDB2V0       |

| M6         | IO110NDB4V0      | N16        | VCC              | P26        | IO67PDB2V0       |

| M7         | GND              | N17        | VCCIB2           | R1         | NC               |

| M8         | IO104NDB4V0      | N18        | IO70PDB2V0       | R2         | VCCIB4           |

| M9         | IO111NDB4V0      | N19        | VCCIB2           | R3         | IO103NDB4V0      |

| M10        | GND              | N20        | IO69PDB2V0       | R4         | GND              |

| M11        | VCC              | N21        | GCA1/IO64PDB2V0  | R5         | IO101PDB4V0      |

| M12        | GND              | N22        | VCCIB2           | R6         | IO100NPB4V0      |

| M13        | VCC              | N23        | GCC0/IO62NDB2V0  | R7         | GND              |

| M14        | GND              | N24        | GCC1/IO62PDB2V0  | R8         | IO99PDB4V0       |

| M15        | VCC              | N25        | IO66PDB2V0       | R9         | IO97PDB4V0       |

| M16        | GND              | N26        | IO65NDB2V0       | R10        | GND              |

| M17        | GND              | P1         | NC               | R11        | GND              |

| M18        | IO60NDB2V0       | P2         | NC               | R12        | VCC              |

| M19        | IO58PDB2V0       | P3         | IO103PDB4V0      | R13        | GND              |

| M20        | GND              | P4         | XTAL1            | R14        | VCC              |

| M21        | IO68NPB2V0       | P5         | VCCIB4           | R15        | GND              |

| M22        | IO61NDB2V0       | P6         | GNDOSC           | R16        | VCC              |

| M23        | GND              | P7         | GFC0/IO107NDB4V0 | R17        | GND              |

| M24        | IO56NDB2V0       | P8         | VCCIB4           | R18        | GDB2/IO83PDB2V0  |

| M25        | VCCIB2           | P9         | GFB0/IO106NDB4V0 | R19        | IO78PDB2V0       |

| M26        | IO65PDB2V0       | P10        | VCCIB4           | R20        | GND              |

Fusion Family of Mixed Signal FPGAs

|            | FG676            |            | FG676            |            | FG676            |

|------------|------------------|------------|------------------|------------|------------------|

| Pin Number | AFS1500 Function | Pin Number | AFS1500 Function | Pin Number | AFS1500 Function |

| R21        | IO72NDB2V0       | U5         | VCCIB4           | V15        | AC5              |

| R22        | IO72PDB2V0       | U6         | IO91PDB4V0       | V16        | NC               |

| R23        | GND              | U7         | IO91NDB4V0       | V17        | GNDA             |

| R24        | IO71PDB2V0       | U8         | IO92PDB4V0       | V18        | IO77PPB2V0       |

| R25        | VCCIB2           | U9         | GND              | V19        | IO74PDB2V0       |

| R26        | IO67NDB2V0       | U10        | GND              | V20        | VCCIB2           |

| T1         | GND              | U11        | VCC33A           | V21        | IO82NDB2V0       |

| T2         | NC               | U12        | GNDA             | V22        | GDA2/IO82PDB2V0  |

| Т3         | GFA1/IO105PDB4V0 | U13        | VCC33A           | V23        | GND              |

| T4         | GFA0/IO105NDB4V0 | U14        | GNDA             | V24        | GDC1/IO79PDB2V0  |

| Т5         | IO101NDB4V0      | U15        | VCC33A           | V25        | VCCIB2           |

| Т6         | IO96PDB4V0       | U16        | GNDA             | V26        | NC               |

| Τ7         | IO96NDB4V0       | U17        | VCC              | W1         | GND              |

| Т8         | IO99NDB4V0       | U18        | GND              | W2         | IO94PPB4V0       |

| Т9         | IO97NDB4V0       | U19        | IO74NDB2V0       | W3         | IO98PDB4V0       |

| T10        | VCCIB4           | U20        | GDA0/IO81NDB2V0  | W4         | IO98NDB4V0       |

| T11        | VCC              | U21        | GDB0/IO80NDB2V0  | W5         | GEC1/IO90PDB4V0  |

| T12        | GND              | U22        | VCCIB2           | W6         | GEC0/IO90NDB4V0  |

| T13        | VCC              | U23        | IO75NDB2V0       | W7         | GND              |

| T14        | GND              | U24        | IO75PDB2V0       | W8         | VCCNVM           |

| T15        | VCC              | U25        | NC               | W9         | VCCIB4           |

| T16        | GND              | U26        | NC               | W10        | VCC15A           |

| T17        | VCCIB2           | V1         | NC               | W11        | GNDA             |

| T18        | IO83NDB2V0       | V2         | VCCIB4           | W12        | AC4              |

| T19        | IO78NDB2V0       | V3         | IO100PPB4V0      | W13        | VCC33A           |

| T20        | GDA1/IO81PDB2V0  | V4         | GND              | W14        | GNDA             |

| T21        | GDB1/IO80PDB2V0  | V5         | IO95PDB4V0       | W15        | AG5              |

| T22        | IO73NDB2V0       | V6         | IO95NDB4V0       | W16        | GNDA             |

| T23        | IO73PDB2V0       | V7         | VCCIB4           | W17        | PUB              |

| T24        | IO71NDB2V0       | V8         | IO92NDB4V0       | W18        | VCCIB2           |

| T25        | NC               | V9         | GNDNVM           | W19        | TDI              |

| T26        | GND              | V10        | GNDA             | W20        | GND              |

| U1         | NC               | V11        | NC               | W21        | IO84NDB2V0       |

| U2         | NC               | V12        | AV4              | W22        | GDC2/IO84PDB2V0  |

| U3         | IO102PDB4V0      | V13        | NC               | W23        | IO77NPB2V0       |

| U4         | IO102NDB4V0      | V14        | AV5              | W24        | GDC0/IO79NDB2V0  |

| Revision                    | Changes                                                                                                                                                                                               | Page  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Advance v1.5<br>(continued) | This bullet was added to the "Integrated A/D Converter (ADC) and Analog I/O" section: ADC Accuracy is Better than 1%                                                                                  | I     |

|                             | In the "Integrated Analog Blocks and Analog I/Os" section, ±4 LSB was changed to 0.72. The following sentence was deleted:                                                                            | 1-4   |

|                             | The input range for voltage signals is from $-12$ V to $+12$ V with full-scale output values from 0.125 V to 16 V.                                                                                    |       |

|                             | In addition, 2°C was changed to 3°C:                                                                                                                                                                  |       |

|                             | "One analog input in each quad can be connected to an external temperature monitor diode and achieves detection accuracy of $\pm 3^{\circ}$ C."                                                       |       |

|                             | The following sentence was deleted:                                                                                                                                                                   |       |

|                             | The input range for voltage signals is from $-12$ V to $+12$ V with full-scale output values from 0.125 V to 16 V.                                                                                    |       |

|                             | The title of the datasheet changed from Actel Programmable System Chips to Actel Fusion Mixed Signal FPGAs. In addition, all instances of programmable system chip were changed to mixed signal FPGA. | N/A   |

| Advance v1.4<br>(July 2008) | In Table 3-8 · Quiescent Supply Current Characteristics (IDDQ)1, footnote references were updated for I <sub>DC2</sub> and I <sub>DC3</sub> .<br>Footnote 3 and 4 were updated and footnote 5 is new. | 3-11  |

| Advance v1.3<br>(July 2008) | The "ADC Description" section was significantly updated. Please review carefully.                                                                                                                     | 2-102 |

| Advance v1.2                | Table 2-25 • Flash Memory Block Timing was significantly updated.                                                                                                                                     | 2-55  |

| (May 2008)                  | The "V <sub>AREF</sub> Analog Reference Voltage" pin description section was significantly update. Please review it carefully.                                                                        | 2-226 |

|                             | Table 2-45 • ADC Interface Timing was significantly updated.                                                                                                                                          | 2-110 |