Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Detailo                        |                                                                              |

|--------------------------------|------------------------------------------------------------------------------|

| Product Status                 | Active                                                                       |

| Number of LABs/CLBs            | -                                                                            |

| Number of Logic Elements/Cells | -                                                                            |

| Total RAM Bits                 | 276480                                                                       |

| Number of I/O                  | 119                                                                          |

| Number of Gates                | 1500000                                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                                              |

| Mounting Type                  | Surface Mount                                                                |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                           |

| Package / Case                 | 256-LBGA                                                                     |

| Supplier Device Package        | 256-FPBGA (17x17)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1afs1500-2fgg256i |

|                                |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

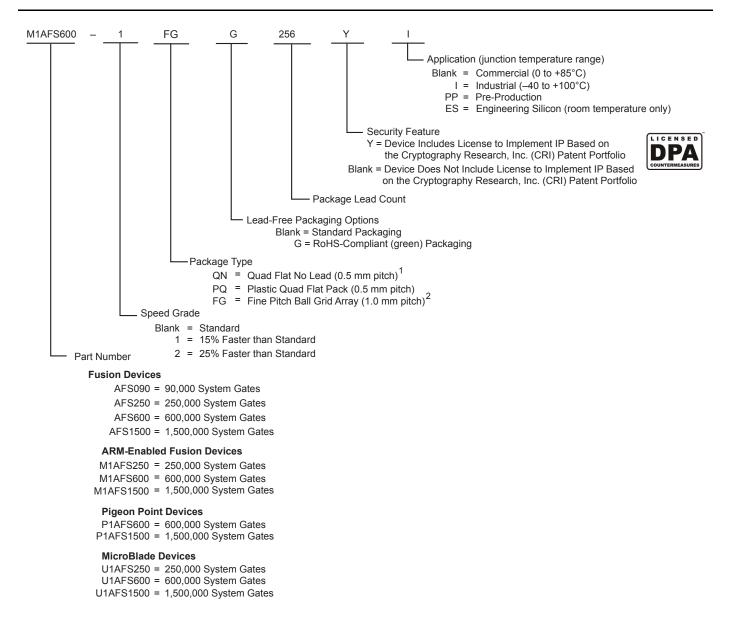

# **Product Ordering Codes**

#### Notes:

- 1. For Fusion devices, Quad Flat No Lead packages are only offered as RoHS compliant, QNG packages.

- 2. MicroBlade and Pigeon Point devices only support FG packages.

# **Fusion Device Status**

| Fusion  | Status     | Cortex-M1 | Status     | Pigeon Point | Status     | MicroBlade | Status     |

|---------|------------|-----------|------------|--------------|------------|------------|------------|

| AFS090  | Production |           |            |              |            |            |            |

| AFS250  | Production | M1AFS250  | Production |              |            | U1AFS250   | Production |

| AFS600  | Production | M1AFS600  | Production | P1AFS600     | Production | U1AFS600   | Production |

| AFS1500 | Production | M1AFS1500 | Production | P1AFS1500    | Production | U1AFS1500  | Production |

# **Related Documents**

## Datasheet

Core8051 www.microsemi.com/soc/ipdocs/Core8051\_DS.pdf

# **Application Notes**

Fusion FlashROM http://www.microsemi.com/soc/documents/Fusion\_FROM\_AN.pdf Fusion SRAM/FIFO Blocks http://www.microsemi.com/soc/documents/Fusion\_RAM\_FIFO\_AN.pdf Using DDR in Fusion Devices http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=129938 Fusion Security http://www.microsemi.com/soc/documents/Fusion\_Security\_AN.pdf Using Fusion RAM as Multipliers http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=129940

# Handbook

Cortex-M1 Handbook www.microsemi.com/soc/documents/CortexM1\_HB.pdf

# **User Guides**

Designer User Guide http://www.microsemi.com/soc/documents/designer\_UG.pdf Fusion FPGA Fabric User Guide http://www.microsemi.com/index.php?option=com\_docman&task=doc\_download&gid=130817 IGLOO, ProASIC3, SmartFusion and Fusion Macro Library Guide http://www.microsemi.com/soc/documents/pa3\_libguide\_ug.pdf SmartGen, FlashROM, Flash Memory System Builder, and Analog System Builder User Guide http://www.microsemi.com/soc/documents/genguide\_ug.pdf

# **White Papers**

Fusion Technology http://www.microsemi.com/soc/documents/Fusion\_Tech\_WP.pdf The system application, Level 3, is the larger user application that utilizes one or more applets. Designing at the highest level of abstraction supported by the Fusion technology stack, the application can be easily created in FPGA gates by importing and configuring multiple applets.

In fact, in some cases an entire FPGA system design can be created without any HDL coding.

An optional MCU enables a combination of software and HDL-based design methodologies. The MCU can be on-chip or off-chip as system requirements dictate. System portioning is very flexible, allowing the MCU to reside above the applets or to absorb applets, or applets and backbone, if desired.

The Fusion technology stack enables a very flexible design environment. Users can engage in design across a continuum of abstraction from very low to very high.

# **Core Architecture**

### VersaTile

Based upon successful ProASIC3/E logic architecture, Fusion devices provide granularity comparable to gate arrays. The Fusion device core consists of a sea-of-VersaTiles architecture.

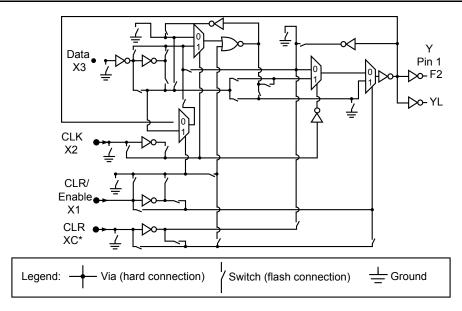

As illustrated in Figure 2-2, there are four inputs in a logic VersaTile cell, and each VersaTile can be configured using the appropriate flash switch connections:

- Any 3-input logic function

- Latch with clear or set

- · D-flip-flop with clear or set

- Enable D-flip-flop with clear or set (on a 4th input)

VersaTiles can flexibly map the logic and sequential gates of a design. The inputs of the VersaTile can be inverted (allowing bubble pushing), and the output of the tile can connect to high-speed, very-long-line routing resources. VersaTiles and larger functions are connected with any of the four levels of routing hierarchy.

When the VersaTile is used as an enable D-flip-flop, the SET/CLR signal is supported by a fourth input, which can only be routed to the core cell over the VersaNet (global) network.

The output of the VersaTile is F2 when the connection is to the ultra-fast local lines, or YL when the connection is to the efficient long-line or very-long-line resources (Figure 2-2).

*Note:* \*This input can only be connected to the global clock distribution network.

Figure 2-2 • Fusion Core VersaTile

### VersaTile Characteristics

#### Sample VersaTile Specifications—Combinatorial Module

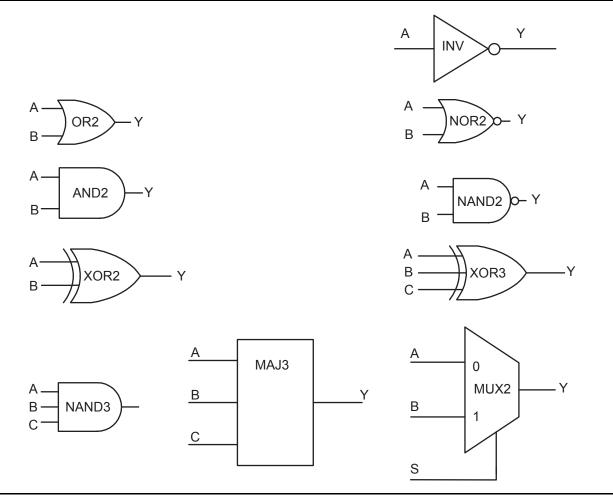

The Fusion library offers all combinations of LUT-3 combinatorial functions. In this section, timing characteristics are presented for a sample of the library (Figure 2-3). For more details, refer to the *IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide*.

Figure 2-3 • Sample of Combinatorial Cells

## **RC Oscillator**

The RC oscillator is an on-chip free-running clock source generating a 100 MHz clock. It can be used as a source clock for both on-chip and off-chip resources. When used in conjunction with the Fusion PLL and CCC circuits, the RC oscillator clock source can be used to generate clocks of varying frequency and phase.

The Fusion RC oscillator is very accurate at  $\pm 1\%$  over commercial temperature ranges and and  $\pm 3\%$  over industrial temperature ranges. It is an automated clock, requiring no setup or configuration by the user. It requires only that the power and GNDOSC pins be connected; no external components are required. The RC oscillator can be used to drive either a PLL or another internal signal.

### **RC Oscillator Characteristics**

| Parameter          | Description         | Conditions                                                                                | Min. | Тур. | Max. | Units |

|--------------------|---------------------|-------------------------------------------------------------------------------------------|------|------|------|-------|

|                    | Operating Frequency |                                                                                           |      | 100  |      | MHz   |

|                    | Accuracy            | Temperature: 0°C to 85°C<br>Voltage: 3.3 V ± 5%                                           |      | 1    |      | %     |

|                    |                     | Temperature: –40°C to 125°C<br>Voltage: 3.3 V ± 5%                                        |      | 3    |      | %     |

| F <sub>RC</sub>    | Output Jitter       | Period Jitter (at 5 k cycles)                                                             |      | 100  |      | ps    |

| · KC               |                     | Cycle–Cycle Jitter (at 5 k cycles)                                                        |      | 100  |      | ps    |

|                    |                     | Period Jitter (at 5 k cycles) with 1 KHz / 300 mV peak-to-peak noise on power supply      |      | 150  |      | ps    |

|                    |                     | Cycle–Cycle Jitter (at 5 k cycles) with 1 KHz / 300 mV peak-to-peak noise on power supply |      | 150  |      | ps    |

|                    | Output Duty Cycle   |                                                                                           |      | 50   |      | %     |

| I <sub>DYNRC</sub> | Operating Current   |                                                                                           |      | 1    |      | mA    |

#### Table 2-9 • Electrical Characteristics of RC Oscillator

# **Embedded Memories**

Fusion devices include four types of embedded memory: flash block, FlashROM, SRAM, and FIFO.

# **Flash Memory Block**

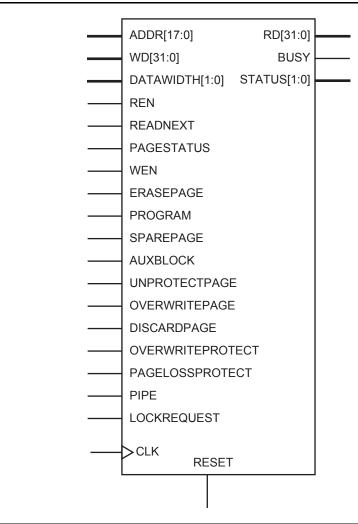

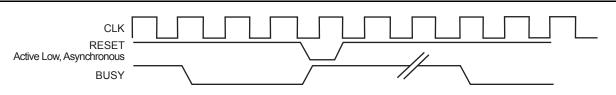

Fusion is the first FPGA that offers a flash memory block (FB). Each FB block stores 2 Mbits of data. The flash memory block macro is illustrated in Figure 2-32. The port pin name and descriptions are detailed on Table 2-19 on page 2-40. All flash memory block signals are active high, except for CLK and active low RESET. All flash memory operations are synchronous to the rising edge of CLK.

Figure 2-32 • Flash Memory Block

## Flash Memory Block Diagram

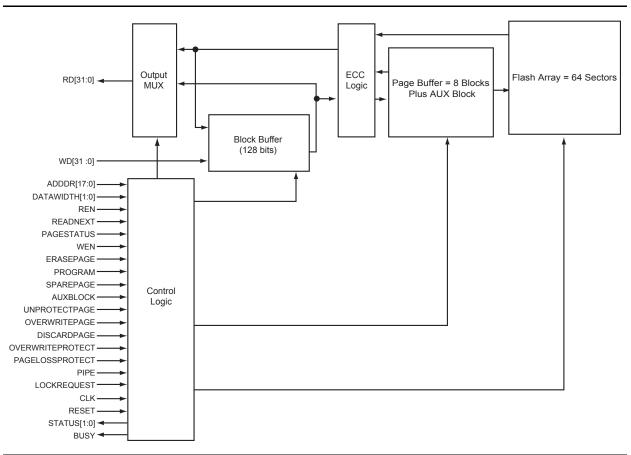

A simplified diagram of the flash memory block is shown in Figure 2-33.

The logic consists of the following sub-blocks:

Flash Array

Contains all stored data. The flash array contains 64 sectors, and each sector contains 33 pages of data.

Page Buffer

A page-wide volatile register. A page contains 8 blocks of data and an AUX block.

- Block Buffer

- Contains the contents of the last block accessed. A block contains 128 data bits.

- ECC Logic

The FB stores error correction information with each block to perform single-bit error correction and double-bit error detection on all data blocks.

# Flash Memory Block Characteristics

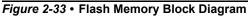

### Figure 2-44 • Reset Timing Diagram

# Table 2-25 • Flash Memory Block TimingCommercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter                  | Description                                        | -2    | -1    | Std.  | Units |

|----------------------------|----------------------------------------------------|-------|-------|-------|-------|

| t                          | Clock-to-Q in 5-cycle read mode of the Read Data   | 7.99  | 9.10  | 10.70 | ns    |

| t <sub>CLK2RD</sub>        | Clock-to-Q in 6-cycle read mode of the Read Data   | 5.03  | 5.73  | 6.74  | ns    |

| +                          | Clock-to-Q in 5-cycle read mode of BUSY            | 4.95  | 5.63  | 6.62  | ns    |

| t <sub>CLK2BUSY</sub>      | Clock-to-Q in 6-cycle read mode of BUSY            | 4.45  | 5.07  | 5.96  | ns    |

| +                          | Clock-to-Status in 5-cycle read mode               | 11.24 | 12.81 | 15.06 | ns    |

| <sup>t</sup> CLK2STATUS    | Clock-to-Status in 6-cycle read mode               | 4.48  | 5.10  | 6.00  | ns    |

| t <sub>DSUNVM</sub>        | Data Input Setup time for the Control Logic        | 1.92  | 2.19  | 2.57  | ns    |

| t <sub>DHNVM</sub>         | Data Input Hold time for the Control Logic         | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>ASUNVM</sub>        | Address Input Setup time for the Control Logic     | 2.76  | 3.14  | 3.69  | ns    |

| t <sub>AHNVM</sub>         | Address Input Hold time for the Control Logic      | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUDWNVM</sub>       | Data Width Setup time for the Control Logic        | 1.85  | 2.11  | 2.48  | ns    |

| t <sub>HDDWNVM</sub>       | Data Width Hold time for the Control Logic         | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SURENNVM</sub>      | Read Enable Setup time for the Control Logic       | 3.85  | 4.39  | 5.16  | ns    |

| t <sub>HDRENNVM</sub>      | Read Enable Hold Time for the Control Logic        | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUWENNVM</sub>      | Write Enable Setup time for the Control Logic      | 2.37  | 2.69  | 3.17  | ns    |

| t <sub>HDWENNVM</sub>      | Write Enable Hold Time for the Control Logic       | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUPROGNVM</sub>     | Program Setup time for the Control Logic           | 2.16  | 2.46  | 2.89  | ns    |

| t <sub>HDPROGNVM</sub>     | Program Hold time for the Control Logic            | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUSPAREPAGE</sub>   | SparePage Setup time for the Control Logic         | 3.74  | 4.26  | 5.01  | ns    |

| t <sub>HDSPAREPAGE</sub>   | SparePage Hold time for the Control Logic          | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUAUXBLK</sub>      | Auxiliary Block Setup Time for the Control Logic   | 3.74  | 4.26  | 5.00  | ns    |

| t <sub>HDAUXBLK</sub>      | Auxiliary Block Hold Time for the Control Logic    | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SURDNEXT</sub>      | ReadNext Setup Time for the Control Logic          | 2.17  | 2.47  | 2.90  | ns    |

| t <sub>HDRDNEXT</sub>      | ReadNext Hold Time for the Control Logic           | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUERASEPG</sub>     | Erase Page Setup Time for the Control Logic        | 3.76  | 4.28  | 5.03  | ns    |

| t <sub>HDERASEPG</sub>     | Erase Page Hold Time for the Control Logic         | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUUNPROTECTPG</sub> | Unprotect Page Setup Time for the Control Logic    | 2.01  | 2.29  | 2.69  | ns    |

| t <sub>HDUNPROTECTPG</sub> | Unprotect Page Hold Time for the Control Logic     | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUDISCARDPG</sub>   | Discard Page Setup Time for the Control Logic      | 1.88  | 2.14  | 2.52  | ns    |

| t <sub>HDDISCARDPG</sub>   | Discard Page Hold Time for the Control Logic       | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUOVERWRPRO</sub>   | Overwrite Protect Setup Time for the Control Logic | 1.64  | 1.86  | 2.19  | ns    |

| t <sub>HDOVERWRPRO</sub>   | Overwrite Protect Hold Time for the Control Logic  | 0.00  | 0.00  | 0.00  | ns    |

Device Architecture

#### DINA and DINB

These are the input data signals, and they are nine bits wide. Not all nine bits are valid in all configurations. When a data width less than nine is specified, unused high-order signals must be grounded (Table 2-29).

#### **DOUTA and DOUTB**

These are the nine-bit output data signals. Not all nine bits are valid in all configurations. As with DINA and DINB, high-order bits may not be used (Table 2-29). The output data on unused pins is undefined.

Table 2-29 • Unused/Used Input and Output Data Pins for Various Supported Bus Widths

| D×W   | DINx/DOUTx |       |  |  |  |  |

|-------|------------|-------|--|--|--|--|

| D~W   | Unused     | Used  |  |  |  |  |

| 4k×1  | [8:1]      | [0]   |  |  |  |  |

| 2k×2  | [8:2]      | [1:0] |  |  |  |  |

| 1k×4  | [8:4]      | [3:0] |  |  |  |  |

| 512×9 | None       | [8:0] |  |  |  |  |

Note: The "x" in DINx and DOUTx implies A or B.

## SRAM Characteristics

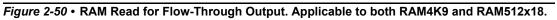

**Timing Waveforms**

*Figure 2-51* • RAM Read for Pipelined Output. Applicable to both RAM4K9 and RAM512x18.

# User I/Os

## Introduction

Fusion devices feature a flexible I/O structure, supporting a range of mixed voltages (1.5 V, 1.8 V, 2.5 V, and 3.3 V) through a bank-selectable voltage. Table 2-68, Table 2-69, Table 2-70, and Table 2-71 on page 2-135 show the voltages and the compatible I/O standards. I/Os provide programmable slew rates, drive strengths, weak pull-up, and weak pull-down circuits. 3.3 V PCI and 3.3 V PCI-X are 5 V–tolerant. See the "5 V Input Tolerance" section on page 2-144 for possible implementations of 5 V tolerance.

All I/Os are in a known state during power-up, and any power-up sequence is allowed without current impact. Refer to the "I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)" section on page 3-5 for more information. In low power standby or sleep mode (VCC is OFF, VCC33A is ON, VCCI is ON) or when the resource is not used, digital inputs are tristated, digital outputs are tristated, and digital bibufs (input/output) are tristated.

I/O Tile

The Fusion I/O tile provides a flexible, programmable structure for implementing a large number of I/O standards. In addition, the registers available in the I/O tile in selected I/O banks can be used to support high-performance register inputs and outputs, with register enable if desired (Figure 2-99 on page 2-133). The registers can also be used to support the JESD-79C DDR standard within the I/O structure (see the "Double Data Rate (DDR) Support" section on page 2-139 for more information).

As depicted in Figure 2-100 on page 2-138, all I/O registers share one CLR port. The output register and output enable register share one CLK port. Refer to the "I/O Registers" section on page 2-138 for more information.

## I/O Banks and I/O Standards Compatibility

The digital I/Os are grouped into I/O voltage banks. There are three digital I/O banks on the AFS090 and AFS250 devices and four digital I/O banks on the AFS600 and AFS1500 devices. Figure 2-113 on page 2-158 and Figure 2-114 on page 2-159 show the bank configuration by device. The north side of the I/O in the AFS600 and AFS1500 devices comprises two banks of Pro I/Os. The Pro I/Os support a wide number of voltage-referenced I/O standards in addition to the multitude of single-ended and differential I/O standards common throughout all Microsemi digital I/Os. Each I/O voltage bank has dedicated I/O supply and ground voltages (VCCI/GNDQ for input buffers and VCCI/GND for output buffers). Because of these dedicated supplies, only I/Os with compatible standards can be assigned to the same I/O voltage bank. Table 2-69 and Table 2-70 on page 2-134 show the required voltage compatibility values for each of these voltages.

For more information about I/O and global assignments to I/O banks, refer to the specific pin table of the device in the "Package Pin Assignments" on page 4-1 and the "User I/O Naming Convention" section on page 2-158.

Each Pro I/O bank is divided into minibanks. Any user I/O in a VREF minibank (a minibank is the region of scope of a VREF pin) can be configured as a VREF pin (Figure 2-99 on page 2-133). Only one VREF pin is needed to control the entire VREF minibank. The location and scope of the VREF minibanks can be determined by the I/O name. For details, see the "User I/O Naming Convention" section on page 2-158.

Table 2-70 on page 2-134 shows the I/O standards supported by Fusion devices and the corresponding voltage levels.

I/O standards are compatible if the following are true:

- Their VCCI values are identical.

- If both of the standards need a VREF, their VREF values must be identical (Pro I/O only).

Device Architecture

### Table 2-71 • Fusion Standard and Advanced I/O Features

| I/O Bank Voltage (typical) | Minibank Voltage (typical) | LVTTL/LVCMOS 3.3 V | LVCMOS 2.5 V | LVCMOS 1.8 V | LVCMOS 1.5 V | 3.3 V PCI / PCI-X | GTL + (3.3 V) | GTL + (2.5 V) | GTL (3.3 V) | GTL (2.5 V) | HSTL Class I and II (1.5 V) | SSTL2 Class I and II (2.5 V) | SSTL3 Class I and II (3.3 V) | LVDS (2.5 V ± 5%) | LVPECL (3.3 V) |

|----------------------------|----------------------------|--------------------|--------------|--------------|--------------|-------------------|---------------|---------------|-------------|-------------|-----------------------------|------------------------------|------------------------------|-------------------|----------------|

| 3.3 V                      | -                          |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

|                            | 0.80 V                     |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

|                            | 1.00 V                     |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

|                            | 1.50 V                     |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

| 2.5 V                      | -                          |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

|                            | 0.80 V                     |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

|                            | 1.00 V                     |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

|                            | 1.25 V                     |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

| 1.8 V                      | -                          |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

| 1.5 V                      | -                          |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

|                            | 0.75 V                     |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

Note: White box: Allowable I/O standard combinations Gray box: Illegal I/O standard combinations

## **Electrostatic Discharge (ESD) Protection**

Fusion devices are tested per JEDEC Standard JESD22-A114-B.

Fusion devices contain clamp diodes at every I/O, global, and power pad. Clamp diodes protect all device pads against damage from ESD as well as from excessive voltage transients.

Each I/O has two clamp diodes. One diode has its positive (P) side connected to the pad and its negative (N) side connected to VCCI. The second diode has its P side connected to GND and its N side connected to the pad. During operation, these diodes are normally biased in the Off state, except when transient voltage is significantly above VCCI or below GND levels.

By selecting the appropriate I/O configuration, the diode is turned on or off. Refer to Table 2-75 and Table 2-76 on page 2-143 for more information about I/O standards and the clamp diode.

The second diode is always connected to the pad, regardless of the I/O configuration selected.

|                                                             | Clamp Diode     |                 | Hot In          | Hot Insertion   |                  | Folerance <sup>1</sup> |                 |                  |

|-------------------------------------------------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------------|-----------------|------------------|

| I/O Assignment                                              | Standard<br>I/O | Advanced<br>I/O | Standard<br>I/O | Advanced<br>I/O | Standard<br>I/O  | Advanced<br>I/O        | Input<br>Buffer | Output<br>Buffer |

| 3.3 V LVTTL/LVCMOS                                          | No              | Yes             | Yes             | No              | Yes <sup>1</sup> | Yes <sup>1</sup>       | Enabled/        | Disabled         |

| 3.3 V PCI, 3.3 V PCI-X                                      | N/A             | Yes             | N/A             | No              | N/A              | Yes <sup>1</sup>       | Enabled/        | Disabled         |

| LVCMOS 2.5 V                                                | No              | Yes             | Yes             | No              | No               | No                     | Enabled/        | Disabled         |

| LVCMOS 2.5 V / 5.0 V                                        | N/A             | Yes             | N/A             | No              | N/A              | Yes <sup>2</sup>       | Enabled/        | Disabled         |

| LVCMOS 1.8 V                                                | No              | Yes             | Yes             | No              | No               | No                     | Enabled/        | Disabled         |

| LVCMOS 1.5 V                                                | No              | Yes             | Yes             | No              | No               | No                     | Enabled/        | Disabled         |

| Differential,<br>LVDS/BLVDS/M-<br>LVDS/ LVPECL <sup>3</sup> | N/A             | Yes             | N/A             | No              | N/A              | No                     | Enabled/        | Disabled         |

Table 2-75 • Fusion Standard and Advanced I/O – Hot-Swap and 5 V Input Tolerance Capabilities

Notes:

1. Can be implemented with an external IDT bus switch, resistor divider, or Zener with resistor.

2. Can be implemented with an external resistor and an internal clamp diode.

3. Bidirectional LVPECL buffers are not supported. I/Os can be configured as either input buffers or output buffers.

#### Table 2-76 • Fusion Pro I/O – Hot-Swap and 5 V Input Tolerance Capabilities

| I/O Assignment                                      | Clamp<br>Diode | Hot<br>Insertion | 5 V Input<br>Tolerance | Input Buffer     | Output Buffer |

|-----------------------------------------------------|----------------|------------------|------------------------|------------------|---------------|

| 3.3 V LVTTL/LVCMOS                                  | No             | Yes              | Yes <sup>1</sup>       | Enabled          | I/Disabled    |

| 3.3 V PCI, 3.3 V PCI-X                              | Yes            | No               | Yes <sup>1</sup>       | Enabled          | I/Disabled    |

| LVCMOS 2.5 V <sup>3</sup>                           | No             | Yes              | No                     | Enabled/Disabled |               |

| LVCMOS 2.5 V / 5.0 V <sup>3</sup>                   | Yes            | No               | Yes <sup>2</sup>       | Enabled          | I/Disabled    |

| LVCMOS 1.8 V                                        | No             | Yes              | No                     | Enabled          | I/Disabled    |

| LVCMOS 1.5 V                                        | No             | Yes              | No                     | Enabled          | I/Disabled    |

| Voltage-Referenced Input Buffer                     | No             | Yes              | No                     | Enabled          | l/Disabled    |

| Differential, LVDS/BLVDS/M-LVDS/LVPECL <sup>4</sup> | No             | Yes              | No                     | Enabled          | l/Disabled    |

Notes:

1. Can be implemented with an external IDT bus switch, resistor divider, or Zener with resistor.

- 2. Can be implemented with an external resistor and an internal clamp diode.

- 3. In the SmartGen, FlashROM, Flash Memory System Builder, and Analog System Builder User Guide, select the LVCMOS5 macro for the LVCMOS 2.5 V / 5.0 V I/O standard or the LVCMOS25 macro for the LVCMOS 2.5 V / 0 standard.

4. Bidirectional LVPECL buffers are not supported. I/Os can be configured as either input buffers or output buffers.

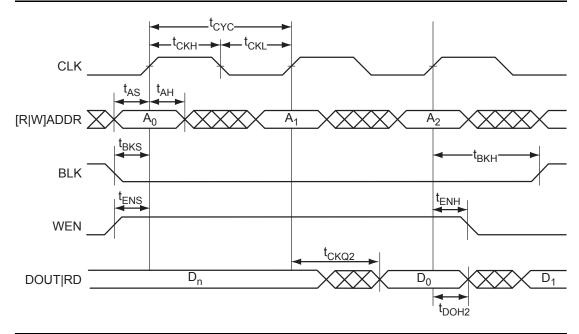

#### Table 2-174 • Parameter Definitions and Measuring Nodes

| Parameter<br>Name     | Parameter Definition                                             | Measuring Nodes<br>(from, to)* |

|-----------------------|------------------------------------------------------------------|--------------------------------|

| t <sub>OCLKQ</sub>    | Clock-to-Q of the Output Data Register                           | H, DOUT                        |

| tosud                 | Data Setup Time for the Output Data Register                     | F, H                           |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                      | F, H                           |

| t <sub>OSUE</sub>     | Enable Setup Time for the Output Data Register                   | G, H                           |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                    | G, H                           |

| t <sub>OPRE2Q</sub>   | Asynchronous Preset-to-Q of the Output Data Register             | L,DOUT                         |

| t <sub>OREMPRE</sub>  | Asynchronous Preset Removal Time for the Output Data Register    | L, H                           |

| t <sub>ORECPRE</sub>  | Asynchronous Preset Recovery Time for the Output Data Register   | L, H                           |

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                         | H, EOUT                        |

| t <sub>OESUD</sub>    | Data Setup Time for the Output Enable Register                   | J, H                           |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                    | J, H                           |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                 | К, Н                           |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                  | К, Н                           |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register           | I, EOUT                        |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register  | I, H                           |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register | I, H                           |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                            | A, E                           |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                      | C, A                           |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                       | C, A                           |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                    | B, A                           |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                     | B, A                           |

| t <sub>IPRE2Q</sub>   | Asynchronous Preset-to-Q of the Input Data Register              | D, E                           |

| t <sub>IREMPRE</sub>  | Asynchronous Preset Removal Time for the Input Data Register     | D, A                           |

| t <sub>IRECPRE</sub>  | Asynchronous Preset Recovery Time for the Input Data Register    | D, A                           |

*Note:* \*See Figure 2-137 on page 2-212 for more information.

Device Architecture

### **Output Register**

#### **Timing Characteristics**

Table 2-177 • Output Data Register Propagation DelaysCommercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                          | -2   | -1   | Std. | Units |

|----------------------|----------------------------------------------------------------------|------|------|------|-------|

| t <sub>OCLKQ</sub>   | Clock-to-Q of the Output Data Register                               | 0.59 | 0.67 | 0.79 | ns    |

| t <sub>OSUD</sub>    | Data Setup Time for the Output Data Register                         | 0.31 | 0.36 | 0.42 | ns    |

| t <sub>OHD</sub>     | Data Hold Time for the Output Data Register                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>OSUE</sub>    | Enable Setup Time for the Output Data Register                       | 0.44 | 0.50 | 0.59 | ns    |

| t <sub>OHE</sub>     | Enable Hold Time for the Output Data Register                        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>OCLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Data Register                  | 0.80 | 0.91 | 1.07 | ns    |

| t <sub>OPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Data Register                 | 0.80 | 0.91 | 1.07 | ns    |

| t <sub>OREMCLR</sub> | Asynchronous Clear Removal Time for the Output Data Register         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ORECCLR</sub> | Asynchronous Clear Recovery Time for the Output Data Register        | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OREMPRE</sub> | Asynchronous Preset Removal Time for the Output Data Register        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ORECPRE</sub> | Asynchronous Preset Recovery Time for the Output Data Register       | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Data Register  | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Data Register | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>OCKMPWH</sub> | Clock Minimum Pulse Width High for the Output Data Register          | 0.36 | 0.41 | 0.48 | ns    |

| t <sub>OCKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Data Register           | 0.32 | 0.37 | 0.43 | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

The 1.76 W power is less than the required 3.00 W. The design therefore requires a heat sink, or the airflow where the device is mounted should be increased. The design's total junction-to-air thermal resistance requirement can be estimated by EQ 7:

$$\theta_{ja(total)} = \frac{T_J - T_A}{P} = \frac{100^{\circ}C - 70^{\circ}C}{3.00 \text{ W}} = 10.00^{\circ}\text{C/W}$$

Determining the heat sink's thermal performance proceeds as follows:

$$\theta_{\text{JA(TOTAL)}} = \theta_{\text{JC}} + \theta_{\text{CS}} + \theta_{\text{SA}}$$

EQ 8

EQ 7

where

- $\theta_{JA} = 0.37^{\circ}C/W$

- Thermal resistance of the interface material between the case and the heat sink, usually provided by the thermal interface manufacturer

$\theta_{SA}$  = Thermal resistance of the heat sink in °C/W

$$\theta_{SA} = \theta_{JA(TOTAL)} - \theta_{JC} - \theta_{CS}$$

EQ 9

$$\theta_{SA} = 13.33^{\circ}C/W - 8.28^{\circ}C/W - 0.37^{\circ}C/W = 5.01^{\circ}C/W$$

A heat sink with a thermal resistance of 5.01°C/W or better should be used. Thermal resistance of heat sinks is a function of airflow. The heat sink performance can be significantly improved with increased airflow.

Carefully estimating thermal resistance is important in the long-term reliability of an Microsemi FPGA. Design engineers should always correlate the power consumption of the device with the maximum allowable power dissipation of the package selected for that device.

Note: The junction-to-air and junction-to-board thermal resistances are based on JEDEC standard (JESD-51) and assumptions made in building the model. It may not be realized in actual application and therefore should be used with a degree of caution. Junction-to-case thermal resistance assumes that all power is dissipated through the case.

### Temperature and Voltage Derating Factors

Table 3-7 • Temperature and Voltage Derating Factors for Timing Delays<br/>(normalized to  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V)

| Array Voltage | Junction Temperature (°C) |      |      |      |      |       |  |  |  |

|---------------|---------------------------|------|------|------|------|-------|--|--|--|

| VCC (V)       | –40°C                     | 0°C  | 25°C | 70°C | 85°C | 100°C |  |  |  |

| 1.425         | 0.88                      | 0.93 | 0.95 | 1.00 | 1.02 | 1.05  |  |  |  |

| 1.500         | 0.83                      | 0.88 | 0.90 | 0.95 | 0.96 | 0.99  |  |  |  |

| 1.575         | 0.80                      | 0.85 | 0.87 | 0.91 | 0.93 | 0.96  |  |  |  |

# Power per I/O Pin

### Table 3-12 • Summary of I/O Input Buffer Power (per pin)—Default I/O Software Settings

|                                           | VCCI (V) | Static Power<br>PDC7 (mW) <sup>1</sup> | Dynamic Power<br>PAC9 (µW/MHz) <sup>2</sup> |

|-------------------------------------------|----------|----------------------------------------|---------------------------------------------|

| Applicable to Pro I/O Banks               |          |                                        |                                             |

| Single-Ended                              |          |                                        |                                             |

| 3.3 V LVTTL/LVCMOS                        | 3.3      | -                                      | 17.39                                       |

| 3.3 V LVTTL/LVCMOS – Schmitt trigger      | 3.3      | _                                      | 25.51                                       |

| 2.5 V LVCMOS                              | 2.5      | _                                      | 5.76                                        |

| 2.5 V LVCMOS – Schmitt trigger            | 2.5      | _                                      | 7.16                                        |

| 1.8 V LVCMOS                              | 1.8      | _                                      | 2.72                                        |

| 1.8 V LVCMOS – Schmitt trigger            | 1.8      | _                                      | 2.80                                        |

| 1.5 V LVCMOS (JESD8-11)                   | 1.5      | _                                      | 2.08                                        |

| 1.5 V LVCMOS (JESD8-11) – Schmitt trigger | 1.5      | _                                      | 2.00                                        |

| 3.3 V PCI                                 | 3.3      | _                                      | 18.82                                       |

| 3.3 V PCI – Schmitt trigger               | 3.3      | _                                      | 20.12                                       |

| 3.3 V PCI-X                               | 3.3      | _                                      | 18.82                                       |

| 3.3 V PCI-X – Schmitt trigger             | 3.3      | _                                      | 20.12                                       |

| Voltage-Referenced                        |          |                                        |                                             |

| 3.3 V GTL                                 | 3.3      | 2.90                                   | 8.23                                        |

| 2.5 V GTL                                 | 2.5      | 2.13                                   | 4.78                                        |

| 3.3 V GTL+                                | 3.3      | 2.81                                   | 4.14                                        |

| 2.5 V GTL+                                | 2.5      | 2.57                                   | 3.71                                        |

| HSTL (I)                                  | 1.5      | 0.17                                   | 2.03                                        |

| HSTL (II)                                 | 1.5      | 0.17                                   | 2.03                                        |

| SSTL2 (I)                                 | 2.5      | 1.38                                   | 4.48                                        |

| SSTL2 (II)                                | 2.5      | 1.38                                   | 4.48                                        |

| SSTL3 (I)                                 | 3.3      | 3.21                                   | 9.26                                        |

| SSTL3 (II)                                | 3.3      | 3.21                                   | 9.26                                        |

| Differential                              | •        |                                        | •                                           |

| LVDS                                      | 2.5      | 2.26                                   | 1.50                                        |

| LVPECL                                    | 3.3      | 5.71                                   | 2.17                                        |

Notes:

1. PDC7 is the static power (where applicable) measured on VCCI.

2. PAC9 is the total dynamic power measured on VCC and VCCI.

Package Pin Assignments

|               | PQ208           |                 |               | PQ208           |                 |  |  |

|---------------|-----------------|-----------------|---------------|-----------------|-----------------|--|--|

| Pin<br>Number | AFS250 Function | AFS600 Function | Pin<br>Number | AFS250 Function | AFS600 Function |  |  |

| 147           | GCC1/IO47PDB1V0 | IO39NDB2V0      | 184           | IO18RSB0V0      | IO10PPB0V1      |  |  |

| 148           | IO42NDB1V0      | GCA2/IO39PDB2V0 | 185           | IO17RSB0V0      | IO09PPB0V1      |  |  |

| 149           | GBC2/IO42PDB1V0 | IO31NDB2V0      | 186           | IO16RSB0V0      | IO10NPB0V1      |  |  |

| 150           | VCCIB1          | GBB2/IO31PDB2V0 | 187           | IO15RSB0V0      | IO09NPB0V1      |  |  |

| 151           | GND             | IO30NDB2V0      | 188           | VCCIB0          | IO08PPB0V1      |  |  |

| 152           | VCC             | GBA2/IO30PDB2V0 | 189           | GND             | IO07PPB0V1      |  |  |

| 153           | IO41NDB1V0      | VCCIB2          | 190           | VCC             | IO08NPB0V1      |  |  |

| 154           | GBB2/IO41PDB1V0 | GNDQ            | 191           | IO14RSB0V0      | IO07NPB0V1      |  |  |

| 155           | IO40NDB1V0      | VCOMPLB         | 192           | IO13RSB0V0      | IO06PPB0V0      |  |  |

| 156           | GBA2/IO40PDB1V0 | VCCPLB          | 193           | IO12RSB0V0      | IO05PPB0V0      |  |  |

| 157           | GBA1/IO39RSB0V0 | VCCIB1          | 194           | IO11RSB0V0      | IO06NPB0V0      |  |  |

| 158           | GBA0/IO38RSB0V0 | GNDQ            | 195           | IO10RSB0V0      | IO04PPB0V0      |  |  |

| 159           | GBB1/IO37RSB0V0 | GBB1/IO27PPB1V1 | 196           | IO09RSB0V0      | IO05NPB0V0      |  |  |

| 160           | GBB0/IO36RSB0V0 | GBA1/IO28PPB1V1 | 197           | IO08RSB0V0      | IO04NPB0V0      |  |  |

| 161           | GBC1/IO35RSB0V0 | GBB0/IO27NPB1V1 | 198           | IO07RSB0V0      | GAC1/IO03PDB0V0 |  |  |

| 162           | VCCIB0          | GBA0/IO28NPB1V1 | 199           | IO06RSB0V0      | GAC0/IO03NDB0V0 |  |  |

| 163           | GND             | VCCIB1          | 200           | GAC1/IO05RSB0V0 | VCCIB0          |  |  |

| 164           | VCC             | GND             | 201           | VCCIB0          | GND             |  |  |

| 165           | GBC0/IO34RSB0V0 | VCC             | 202           | GND             | VCC             |  |  |

| 166           | IO33RSB0V0      | GBC1/IO26PDB1V1 | 203           | VCC             | GAB1/IO02PDB0V0 |  |  |

| 167           | IO32RSB0V0      | GBC0/IO26NDB1V1 | 204           | GAC0/IO04RSB0V0 | GAB0/IO02NDB0V0 |  |  |

| 168           | IO31RSB0V0      | IO24PPB1V1      | 205           | GAB1/IO03RSB0V0 | GAA1/IO01PDB0V0 |  |  |

| 169           | IO30RSB0V0      | IO23PPB1V1      | 206           | GAB0/IO02RSB0V0 | GAA0/IO01NDB0V0 |  |  |

| 170           | IO29RSB0V0      | IO24NPB1V1      | 207           | GAA1/IO01RSB0V0 | GNDQ            |  |  |

| 171           | IO28RSB0V0      | IO23NPB1V1      | 208           | GAA0/IO00RSB0V0 | VCCIB0          |  |  |

| 172           | IO27RSB0V0      | IO22PPB1V0      |               |                 |                 |  |  |

| 173           | IO26RSB0V0      | IO21PPB1V0      |               |                 |                 |  |  |

| 174           | IO25RSB0V0      | IO22NPB1V0      |               |                 |                 |  |  |

| 175           | VCCIB0          | IO21NPB1V0      |               |                 |                 |  |  |

| 176           | GND             | IO20PSB1V0      |               |                 |                 |  |  |

| 177           | VCC             | IO19PSB1V0      |               |                 |                 |  |  |

| 178           | IO24RSB0V0      | IO14NSB0V1      |               |                 |                 |  |  |

| 179           | IO23RSB0V0      | IO12PDB0V1      |               |                 |                 |  |  |

| 180           | IO22RSB0V0      | IO12NDB0V1      |               |                 |                 |  |  |

| 181           | IO21RSB0V0      | VCCIB0          |               |                 |                 |  |  |

| 182           | IO20RSB0V0      | GND             |               |                 |                 |  |  |

| 183           | IO19RSB0V0      | VCC             |               |                 |                 |  |  |

| FG256      |                 |                 |                 |                  |  |  |  |

|------------|-----------------|-----------------|-----------------|------------------|--|--|--|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |  |  |  |

| C7         | IO09RSB0V0      | IO12RSB0V0      | IO06NDB0V0      | IO09NDB0V1       |  |  |  |

| C8         | IO14RSB0V0      | IO22RSB0V0      | IO16PDB1V0      | IO23PDB1V0       |  |  |  |

| C9         | IO15RSB0V0      | IO23RSB0V0      | IO16NDB1V0      | IO23NDB1V0       |  |  |  |

| C10        | IO22RSB0V0      | IO30RSB0V0      | IO25NDB1V1      | IO31NDB1V1       |  |  |  |

| C11        | IO20RSB0V0      | IO31RSB0V0      | IO25PDB1V1      | IO31PDB1V1       |  |  |  |

| C12        | VCCIB0          | VCCIB0          | VCCIB1          | VCCIB1           |  |  |  |

| C13        | GBB1/IO28RSB0V0 | GBC1/IO35RSB0V0 | GBC1/IO26PPB1V1 | GBC1/IO40PPB1V2  |  |  |  |

| C14        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |  |  |  |

| C15        | GND             | GND             | GND             | GND              |  |  |  |

| C16        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |  |  |  |

| D1         | GFC2/IO50NPB3V0 | IO75NDB3V0      | IO84NDB4V0      | IO124NDB4V0      |  |  |  |

| D2         | GFA2/IO51NDB3V0 | GAB2/IO75PDB3V0 | GAB2/IO84PDB4V0 | GAB2/IO124PDB4V0 |  |  |  |

| D3         | GAC2/IO51PDB3V0 | IO76NDB3V0      | IO85NDB4V0      | IO125NDB4V0      |  |  |  |

| D4         | GAA2/IO52PDB3V0 | GAA2/IO76PDB3V0 | GAA2/IO85PDB4V0 | GAA2/IO125PDB4V0 |  |  |  |

| D5         | GAB2/IO52NDB3V0 | GAB0/IO02RSB0V0 | GAB0/IO02NPB0V0 | GAB0/IO02NPB0V0  |  |  |  |

| D6         | GAC0/IO04RSB0V0 | GAC0/IO04RSB0V0 | GAC0/IO03NDB0V0 | GAC0/IO03NDB0V0  |  |  |  |

| D7         | IO08RSB0V0      | IO13RSB0V0      | IO06PDB0V0      | IO09PDB0V1       |  |  |  |

| D8         | NC              | IO20RSB0V0      | IO14NDB0V1      | IO15NDB0V2       |  |  |  |

| D9         | NC              | IO21RSB0V0      | IO14PDB0V1      | IO15PDB0V2       |  |  |  |

| D10        | IO21RSB0V0      | IO28RSB0V0      | IO23PDB1V1      | IO37PDB1V2       |  |  |  |

| D11        | IO23RSB0V0      | GBB0/IO36RSB0V0 | GBB0/IO27NDB1V1 | GBB0/IO41NDB1V2  |  |  |  |

| D12        | NC              | NC              | VCCIB1          | VCCIB1           |  |  |  |

| D13        | GBA2/IO31PDB1V0 | GBA2/IO40PDB1V0 | GBA2/IO30PDB2V0 | GBA2/IO44PDB2V0  |  |  |  |

| D14        | GBB2/IO31NDB1V0 | IO40NDB1V0      | IO30NDB2V0      | IO44NDB2V0       |  |  |  |

| D15        | GBC2/IO32PDB1V0 | GBB2/IO41PDB1V0 | GBB2/IO31PDB2V0 | GBB2/IO45PDB2V0  |  |  |  |

| D16        | GCA2/IO32NDB1V0 | IO41NDB1V0      | IO31NDB2V0      | IO45NDB2V0       |  |  |  |

| E1         | GND             | GND             | GND             | GND              |  |  |  |

| E2         | GFB0/IO48NPB3V0 | IO73NDB3V0      | IO81NDB4V0      | IO118NDB4V0      |  |  |  |

| E3         | GFB2/IO50PPB3V0 | IO73PDB3V0      | IO81PDB4V0      | IO118PDB4V0      |  |  |  |

| E4         | VCCIB3          | VCCIB3          | VCCIB4          | VCCIB4           |  |  |  |

| E5         | NC              | IO74NPB3V0      | IO83NPB4V0      | IO123NPB4V0      |  |  |  |

| E6         | NC              | IO08RSB0V0      | IO04NPB0V0      | IO05NPB0V1       |  |  |  |

| E7         | GND             | GND             | GND             | GND              |  |  |  |

| E8         | NC              | IO18RSB0V0      | IO08PDB0V1      | IO11PDB0V1       |  |  |  |

| E9         | NC              | NC              | IO20NDB1V0      | IO27NDB1V1       |  |  |  |

| E10        | GND             | GND             | GND             | GND              |  |  |  |

| E11        | IO24RSB0V0      | GBB1/IO37RSB0V0 | GBB1/IO27PDB1V1 | GBB1/IO41PDB1V2  |  |  |  |

| E12        | NC              | IO50PPB1V0      | IO33PSB2V0      | IO48PSB2V0       |  |  |  |

# **Datasheet Categories**

### Categories

In order to provide the latest information to designers, some datasheet parameters are published before data has been fully characterized from silicon devices. The data provided for a given device, as highlighted in the "Fusion Device Status" table, is designated as either "Product Brief," "Advance," "Preliminary," or "Production." The definitions of these categories are as follows:

### **Product Brief**

The product brief is a summarized version of a datasheet (advance or production) and contains general product information. This document gives an overview of specific device and family information.

### Advance

This version contains initial estimated information based on simulation, other products, devices, or speed grades. This information can be used as estimates, but not for production. This label only applies to the DC and Switching Characteristics chapter of the datasheet and will only be used when the data has not been fully characterized.

### Preliminary

The datasheet contains information based on simulation and/or initial characterization. The information is believed to be correct, but changes are possible.

### Production

This version contains information that is considered to be final.

## **Export Administration Regulations (EAR)**

The products described in this document are subject to the Export Administration Regulations (EAR). They could require an approved export license prior to export from the United States. An export includes release of product or disclosure of technology to a foreign national inside or outside the United States.

# Safety Critical, Life Support, and High-Reliability Applications Policy

The products described in this advance status document may not have completed the Microsemi qualification process. Products may be amended or enhanced during the product introduction and qualification process, resulting in changes in device functionality or performance. It is the responsibility of each customer to ensure the fitness of any product (but especially a new product) for a particular purpose, including appropriateness for safety-critical, life-support, and other high-reliability applications. Consult the Microsemi SoC Products Group Terms and Conditions for specific liability exclusions relating to life-support applications. A reliability report covering all of the SoC Products Group's products is available at http://www.microsemi.com/soc/documents/ORT\_Report.pdf. Microsemi also offers a variety of enhanced qualification and lot acceptance screening procedures. Contact your local sales office for additional reliability information.