Welcome to E-XFL.COM

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

E·XFI

| Product Status                 | Active                                                                    |

|--------------------------------|---------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | 276480                                                                    |

| Number of I/O                  | 119                                                                       |

| Number of Gates                | 1500000                                                                   |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                           |

| Package / Case                 | 256-LBGA                                                                  |

| Supplier Device Package        | 256-FPBGA (17x17)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1afs1500-fg256 |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

RAM512X18 exhibits slightly different behavior from RAM4K9, as it has dedicated read and write ports.

### WW and RW

These signals enable the RAM to be configured in one of the two allowable aspect ratios (Table 2-30).

### Table 2-30 • Aspect Ratio Settings for WW[1:0]

| WW[1:0] | RW[1:0] | D×W      |

|---------|---------|----------|

| 01      | 01      | 512×9    |

| 10      | 10      | 256×18   |

| 00, 11  | 00, 11  | Reserved |

### WD and RD

These are the input and output data signals, and they are 18 bits wide. When a 512×9 aspect ratio is used for write, WD[17:9] are unused and must be grounded. If this aspect ratio is used for read, then RD[17:9] are undefined.

### WADDR and RADDR

These are read and write addresses, and they are nine bits wide. When the 256×18 aspect ratio is used for write or read, WADDR[8] or RADDR[8] are unused and must be grounded.

### WCLK and RCLK

These signals are the write and read clocks, respectively. They are both active high.

### WEN and REN

These signals are the write and read enables, respectively. They are both active low by default. These signals can be configured as active high.

### RESET

This active low signal resets the output to zero, disables reads and/or writes from the SRAM block, and clears the data hold registers when asserted. It does not reset the contents of the memory.

### PIPE

This signal is used to specify pipelined read on the output. A Low on PIPE indicates a nonpipelined read, and the data appears on the output in the same clock cycle. A High indicates a pipelined read, and data appears on the output in the next clock cycle.

### Clocking

The dual-port SRAM blocks are only clocked on the rising edge. SmartGen allows falling-edge-triggered clocks by adding inverters to the netlist, hence achieving dual-port SRAM blocks that are clocked on either edge (rising or falling). For dual-port SRAM, each port can be clocked on either edge or by separate clocks, by port.

Fusion devices support inversion (bubble pushing) throughout the FPGA architecture, including the clock input to the SRAM modules. Inversions added to the SRAM clock pin on the design schematic or in the HDL code will be automatically accounted for during design compile without incurring additional delay in the clock path.

The two-port SRAM can be clocked on the rising edge or falling edge of WCLK and RCLK.

If negative-edge RAM and FIFO clocking is selected for memory macros, clock edge inversion management (bubble pushing) is automatically used within the Fusion development tools, without performance penalty.

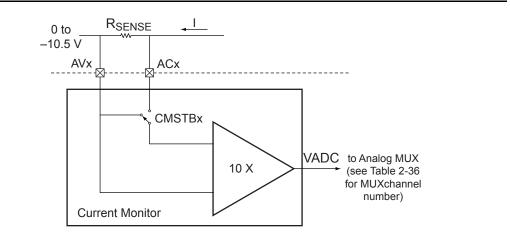

Figure 2-73 • Negative Current Monitor

### Terminology

### Accuracy

The accuracy of Fusion Current Monitor is  $\pm 2 \text{ mV}$  minimum plus 5% of the differential voltage at the input. The input accuracy can be translated to error at the ADC output by using EQ 4. The 10 V/V gain is the gain of the Current Monitor Circuit, as described in the "Current Monitor" section on page 2-86. For 8-bit mode, N = 8,  $V_{AREF} = 2.56$  V, zero differential voltage between AV and AC, the Error ( $E_{ADC}$ ) is equal to 2 LSBs.

$$E_{ADC} = (2mV + 0.05 |V_{AV} - V_{AC}|) \times (10V) / V \times \frac{2^{N}}{V_{AREF}}$$

EQ 4

where

N is the number of bits

$V_{AREF}$  is the Reference voltage

$V_{AV}$  is the voltage at AV pad

V<sub>AC</sub> is the voltage at AC pad

# Analog-to-Digital Converter Block

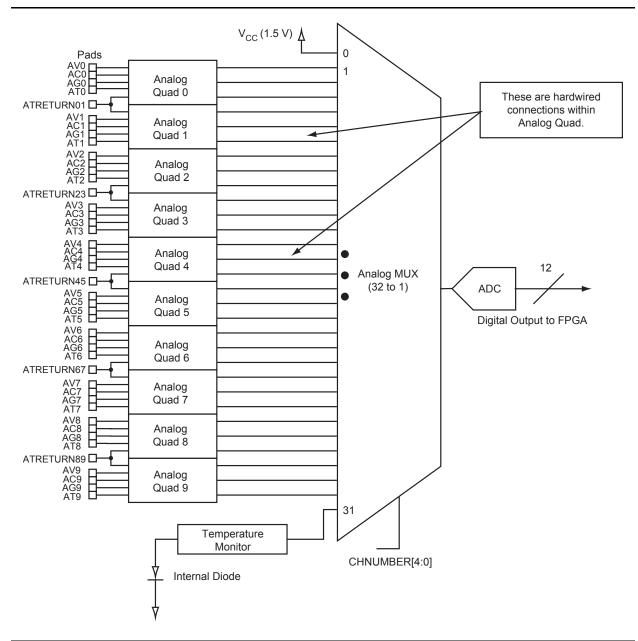

At the heart of the Fusion analog system is a programmable Successive Approximation Register (SAR) ADC. The ADC can support 8-, 10-, or 12-bit modes of operation. In 12-bit mode, the ADC can resolve 500 ksps. All results are MSB-justified in the ADC. The input to the ADC is a large 32:1 analog input multiplexer. A simplified block diagram of the Analog Quads, analog input multiplexer, and ADC is shown in Figure 2-79. The ADC offers multiple self-calibrating modes to ensure consistent high performance both at power-up and during runtime.

Figure 2-79 • ADC Block Diagram

There are several popular ADC architectures, each with advantages and limitations.

The analog-to-digital converter in Fusion devices is a switched-capacitor Successive Approximation Register (SAR) ADC. It supports 8-, 10-, and 12-bit modes of operation with a cumulative sample rate up to 600 k samples per second (ksps). Built-in bandgap circuitry offers 1% internal voltage reference accuracy or an external reference voltage can be used.

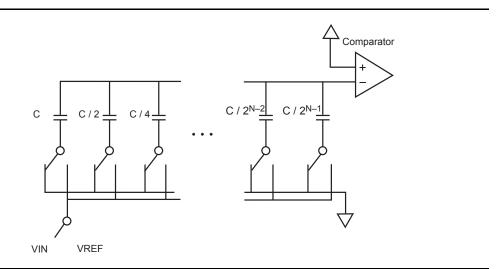

As shown in Figure 2-81, a SAR ADC contains N capacitors with binary-weighted values.

Figure 2-81 • Example SAR ADC Architecture

To begin a conversion, all of the capacitors are quickly discharged. Then VIN is applied to all the capacitors for a period of time (acquisition time) during which the capacitors are charged to a value very close to VIN. Then all of the capacitors are switched to ground, and thus –VIN is applied across the comparator. Now the conversion process begins. First, C is switched to VREF Because of the binary weighting of the capacitors, the voltage at the input of the comparator is then shown by EQ 11.

Voltage at input of comparator = -VIN + VREF / 2

EQ 11

If VIN is greater than VREF / 2, the output of the comparator is 1; otherwise, the comparator output is 0. A register is clocked to retain this value as the MSB of the result. Next, if the MSB is 0, C is switched back to ground; otherwise, it remains connected to VREF, and C / 2 is connected to VREF. The result at the comparator input is now either –VIN + VREF / 4 or –VIN + 3 VREF / 4 (depending on the state of the MSB), and the comparator output now indicates the value of the next most significant bit. This bit is likewise registered, and the process continues for each subsequent bit until a conversion is complete. The conversion process requires some acquisition time plus N + 1 ADC clock cycles to complete.

| Analog MUX Channel | Signal                       | Analog Quad Number |

|--------------------|------------------------------|--------------------|

| 16                 | AV5                          |                    |

| 17                 | AC5                          | Analog Quad 5      |

| 18                 | AT5                          |                    |

| 19                 | AV6                          |                    |

| 20                 | AC6                          | Analog Quad 6      |

| 21                 | AT6                          |                    |

| 22                 | AV7                          |                    |

| 23                 | AC7                          | Analog Quad 7      |

| 24                 | AT7                          |                    |

| 25                 | AV8                          |                    |

| 26                 | AC8                          | Analog Quad 8      |

| 27                 | AT8                          |                    |

| 28                 | AV9                          |                    |

| 29                 | AC9                          | Analog Quad 9      |

| 30                 | AT9                          |                    |

| 31                 | Internal temperature monitor |                    |

### Table 2-40 • Analog MUX Channels (continued)

The ADC can be powered down independently of the FPGA core, as an additional control or for powersaving considerations, via the PWRDWN pin of the Analog Block. The PWRDWN pin controls only the comparators in the ADC.

### **ADC Modes**

The Fusion ADC can be configured to operate in 8-, 10-, or 12-bit modes, power-down after conversion, and dynamic calibration. This is controlled by MODE[3:0], as defined in Table 2-41 on page 2-106.

The output of the ADC is the RESULT[11:0] signal. In 8-bit mode, the Most Significant 8 Bits RESULT[11:4] are used as the ADC value and the Least Significant 4 Bits RESULT[3:0] are logical '0's. In 10-bit mode, RESULT[11:2] are used the ADC value and RESULT[1:0] are logical 0s.

| Name | Bits | Function                                                                                          |

|------|------|---------------------------------------------------------------------------------------------------|

| MODE | 3    | 0 – Internal calibration after every conversion; two ADCCLK cycles are used after the conversion. |

|      |      | 1 – No calibration after every conversion                                                         |

| MODE | 2    | 0 – Power-down after conversion                                                                   |

|      |      | 1 – No Power-down after conversion                                                                |

| MODE | 1:0  | 00 – 10-bit                                                                                       |

|      |      | 01 – 12-bit                                                                                       |

|      |      | 10 – 8-bit                                                                                        |

|      |      | 11 – Unused                                                                                       |

EQ 16 through EQ 18 can be used to calculate the acquisition time required for a given input. The STC signal gives the number of sample periods in ADCCLK for the acquisition time of the desired signal. If the actual acquisition time is higher than the STC value, the settling time error can affect the accuracy of the ADC, because the sampling capacitor is only partially charged within the given sampling cycle. Example acquisition times are given in Table 2-44 and Table 2-45. When controlling the sample time for the ADC along with the use of the active bipolar prescaler, current monitor, or temperature monitor, the minimum sample time(s) for each must be obeyed. EQ 19 can be used to determine the appropriate value of STC.

You can calculate the minimum actual acquisition time by using EQ 16:

EQ 16

EQ 17

For 0.5 LSB gain error, VOUT should be replaced with (VIN –(0.5 × LSB Value)): (VIN – 0.5 × LSB Value) = VIN(1 –  $e^{-t/RC}$ )

$$1 - e^{-e^{-1}}$$

Solving EQ 17:

EQ 18

where  $R = Z_{INAD} + R_{SOURCE}$  and  $C = C_{INAD}$ . Calculate the value of STC by using EQ 19.

t<sub>SAMPLE</sub> = (2 + STC) x (1 / ADCCLK) or t<sub>SAMPLE</sub> = (2 + STC) x (ADC Clock Period)

EQ 19

where ADCCLK = ADC clock frequency in MHz.

where VIN is the ADC reference voltage (VREF)

$t_{SAMPLE}$  = 0.449 µs from bit resolution in Table 2-44.

ADC Clock frequency = 10 MHz or a 100 ns period.

STC = (t<sub>SAMPLE</sub> / (1 / 10 MHz)) - 2 = 4.49 - 2 = 2.49.

You must round up to 3 to accommodate the minimum sample time.

### Table 2-44 • Acquisition Time Example with VAREF = 2.56 V

|                                                                                  | VIN = 2.56V, R = 4K (R <sub>SOURCE</sub> ~ 0), C = 18 pF |       |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------|----------------------------------------------------------|-------|--|--|--|--|--|--|--|--|

| Resolution         LSB Value (mV)         Min. Sample/Hold Time for 0.5 LSB (μs) |                                                          |       |  |  |  |  |  |  |  |  |

| 8                                                                                | 10                                                       | 0.449 |  |  |  |  |  |  |  |  |

| 10                                                                               | 2.5                                                      | 0.549 |  |  |  |  |  |  |  |  |

| 12                                                                               | 0.625                                                    | 0.649 |  |  |  |  |  |  |  |  |

|                                                                                  | VIN = 3.3V, R = 4K (R <sub>SOURCE</sub> ~ 0), C = 18 pF |       |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------|---------------------------------------------------------|-------|--|--|--|--|--|--|--|--|

| Resolution         LSB Value (mV)         Min. Sample/Hold time for 0.5 LSB (μs) |                                                         |       |  |  |  |  |  |  |  |  |

| 8                                                                                | 12.891                                                  | 0.449 |  |  |  |  |  |  |  |  |

| 10                                                                               | 3.223                                                   | 0.549 |  |  |  |  |  |  |  |  |

| 12                                                                               | 0.806                                                   | 0.649 |  |  |  |  |  |  |  |  |

### Sample Phase

A conversion is performed in three phases. In the first phase, the analog input voltage is sampled on the input capacitor. This phase is called sample phase. During the sample phase, the output signals BUSY and SAMPLE change from '0' to '1', indicating the ADC is busy and sampling the analog signal. The sample time can be controlled by input signals STC[7:0]. The sample time can be calculated by EQ 20. When controlling the sample time for the ADC along with the use of Prescaler or Current Monitor or Temperature Monitor, the minimum sample time for each must be obeyed.

# **Typical Performance Characteristics**

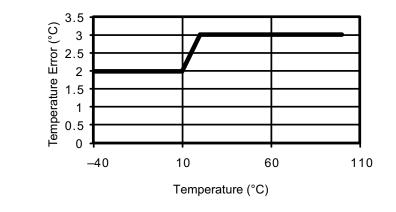

Temperature Errror vs. Die Temperature

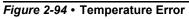

Figure 2-95 • Effect of External Sensor Capacitance

Similarly,

Min. Output Voltage = (Max. Negative input offset) + (Input Voltage x Max. Negative Channel Gain) =  $(-88 \text{ mV}) + (5 \text{ V} \times 0.96) = 4.712 \text{ V}$

### Calculating Accuracy for a Calibrated Analog Channel

### Formula

For a given prescaler range, EQ 31 gives the output voltage.

Output Voltage = Channel Error in V + Input Voltage

EQ 31

where

Channel Error in V = Total Channel Error in LSBs x Equivalent voltage per LSB

### Example

Input Voltage = 5 VChosen Prescaler range = 8 V range Refer to Table 2-52 on page 2-123.

Max. Output Voltage = Max. Positive Channel Error in V + Input Voltage Max. Positive Channel Error in V = (6 LSB) × (8 mV per LSB in 10-bit mode) = 48 mV Max. Output Voltage = 48 mV + 5 V = **5.048 V**

Similarly,

Min. Output Voltage = Max. Negative Channel Error in V + Input Voltage = (-48 mV) + 5 V = 4.952 V

### Calculating LSBs from a Given Error Budget

### Formula

For a given prescaler range, LSB count = ± (Input Voltage × Required % error) / (Equivalent voltage per LSB)

### Example

Input Voltage =  $3.3 \vee$ Required error margin= 1% Refer to Table 2-52 on page 2-123. Equivalent voltage per LSB = 16 mV for a 16V prescaler, with ADC in 10-bit mode LSB Count =  $\pm (5.0 \vee \times 1\%) / (0.016)$ LSB Count =  $\pm 3.125$ Equivalent voltage per LSB = 8 mV for an  $8 \vee$  prescaler, with ADC in 10-bit mode LSB Count =  $\pm (5.0 \vee \times 1\%) / (0.008)$ LSB Count =  $\pm (5.0 \vee \times 1\%) / (0.008)$ LSB Count =  $\pm 6.25$ The  $8 \vee$  prescaler satisfies the calculated LSB count accuracy requirement (see Table 2-52 on page 2-123).

# Table 2-88 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions

|                               |                   |              | VIL       |             | VIH         |           | VOL         | VOH         | IOL | IOH |

|-------------------------------|-------------------|--------------|-----------|-------------|-------------|-----------|-------------|-------------|-----|-----|

| I/O Standard                  | Drive<br>Strength | Slew<br>Rate | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA  |

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 8 mA              | High         | -0.3      | 0.8         | 2           | 3.6       | 0.4         | 2.4         | 8   | 8   |

| 2.5 V LVCMOS                  | 8 mA              | High         | -0.3      | 0.7         | 1.7         | 3.6       | 0.7         | 1.7         | 8   | 8   |

| 1.8 V LVCMOS                  | 4 mA              | High         | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.45        | VCCI-0.45   | 4   | 4   |

| 1.5 V LVCMOS                  | 2 mA              | High         | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 2   | 2   |

Applicable to Standard I/Os

*Note:* Currents are measured at 85°C junction temperature.

### Table 2-89 • Summary of Maximum and Minimum DC Input Levels Applicable to Commercial and Industrial Conditions

Applicable to All I/O Bank Types

|                            | Comr             | nercial <sup>1</sup> | Indu             | strial <sup>2</sup> |

|----------------------------|------------------|----------------------|------------------|---------------------|

|                            | IIL <sup>3</sup> | IIH <sup>4</sup>     | IIL <sup>3</sup> | IIH <sup>4</sup>    |

| DC I/O Standards           | μA               | μA                   | μA               | μA                  |

| 3.3 V LVTTL / 3.3 V LVCMOS | 10               | 10                   | 15               | 15                  |

| 2.5 V LVCMOS               | 10               | 10                   | 15               | 15                  |

| 1.8 V LVCMOS               | 10               | 10                   | 15               | 15                  |

| 1.5 V LVCMOS               | 10               | 10                   | 15               | 15                  |

| 3.3 V PCI                  | 10               | 10                   | 15               | 15                  |

| 3.3 V PCI-X                | 10               | 10                   | 15               | 15                  |

| 3.3 V GTL                  | 10               | 10                   | 15               | 15                  |

| 2.5 V GTL                  | 10               | 10                   | 15               | 15                  |

| 3.3 V GTL+                 | 10               | 10                   | 15               | 15                  |

| 2.5 V GTL+                 | 10               | 10                   | 15               | 15                  |

| HSTL (I)                   | 10               | 10                   | 15               | 15                  |

| HSTL (II)                  | 10               | 10                   | 15               | 15                  |

| SSTL2 (I)                  | 10               | 10                   | 15               | 15                  |

| SSTL2 (II)                 | 10               | 10                   | 15               | 15                  |

| SSTL3 (I)                  | 10               | 10                   | 15               | 15                  |

| SSTL3 (II)                 | 10               | 10                   | 15               | 15                  |

Notes:

1. Commercial range ( $0^{\circ}C < T_J < 85^{\circ}C$ )

2. Industrial range  $(-40^{\circ}C < T_{J} < 100^{\circ}C)$

3. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

4. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

### Table 2-105 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Pro I/Os

| Drive    | Speed |                   |                 |                  |                 |                  | t <sub>EOU</sub> |                 |                 |                 |                 |                  |                  |       |

|----------|-------|-------------------|-----------------|------------------|-----------------|------------------|------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Strength | Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | т                | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

| 4 mA     | Std.  | 0.66              | 7.88            | 0.04             | 1.20            | 1.57             | 0.43             | 8.03            | 6.70            | 2.69            | 2.59            | 10.26            | 8.94             | ns    |

|          | -1    | 0.56              | 6.71            | 0.04             | 1.02            | 1.33             | 0.36             | 6.83            | 5.70            | 2.29            | 2.20            | 8.73             | 7.60             | ns    |

|          | -2    | 0.49              | 5.89            | 0.03             | 0.90            | 1.17             | 0.32             | 6.00            | 5.01            | 2.01            | 1.93            | 7.67             | 6.67             | ns    |

| 8 mA     | Std.  | 0.66              | 5.08            | 0.04             | 1.20            | 1.57             | 0.43             | 5.17            | 4.14            | 3.05            | 3.21            | 7.41             | 6.38             | ns    |

|          | -1    | 0.56              | 4.32            | 0.04             | 1.02            | 1.33             | 0.36             | 4.40            | 3.52            | 2.59            | 2.73            | 6.30             | 5.43             | ns    |

|          | -2    | 0.49              | 3.79            | 0.03             | 0.90            | 1.17             | 0.32             | 3.86            | 3.09            | 2.28            | 2.40            | 5.53             | 4.76             | ns    |

| 12 mA    | Std.  | 0.66              | 3.67            | 0.04             | 1.20            | 1.57             | 0.43             | 3.74            | 2.87            | 3.28            | 3.61            | 5.97             | 5.11             | ns    |

|          | -1    | 0.56              | 3.12            | 0.04             | 1.02            | 1.33             | 0.36             | 3.18            | 2.44            | 2.79            | 3.07            | 5.08             | 4.34             | ns    |

|          | -2    | 0.49              | 2.74            | 0.03             | 0.90            | 1.17             | 0.32             | 2.79            | 2.14            | 2.45            | 2.70            | 4.46             | 3.81             | ns    |

| 16 mA    | Std.  | 0.66              | 3.46            | 0.04             | 1.20            | 1.57             | 0.43             | 3.53            | 2.61            | 3.33            | 3.72            | 5.76             | 4.84             | ns    |

|          | -1    | 0.56              | 2.95            | 0.04             | 1.02            | 1.33             | 0.36             | 3.00            | 2.22            | 2.83            | 3.17            | 4.90             | 4.12             | ns    |

|          | -2    | 0.49              | 2.59            | 0.03             | 0.90            | 1.17             | 0.32             | 2.63            | 1.95            | 2.49            | 2.78            | 4.30             | 3.62             | ns    |

| 24 mA    | Std.  | 0.66              | 3.21            | 0.04             | 1.20            | 1.57             | 0.43             | 3.27            | 2.16            | 3.39            | 4.13            | 5.50             | 4.39             | ns    |

|          | -1    | 0.56              | 2.73            | 0.04             | 1.02            | 1.33             | 0.36             | 2.78            | 1.83            | 2.88            | 3.51            | 4.68             | 3.74             | ns    |

|          | -2    | 0.49              | 2.39            | 0.03             | 0.90            | 1.17             | 0.32             | 2.44            | 1.61            | 2.53            | 3.08            | 4.11             | 3.28             | ns    |

### Table 2-109 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade  | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|-----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.            | 0.66              | 7.07            | 0.04             | 1.00            | 0.43              | 7.20            | 6.23            | 2.07            | 2.15            | ns    |

|                   | –1              | 0.56              | 6.01            | 0.04             | 0.85            | 0.36              | 6.12            | 5.30            | 1.76            | 1.83            | ns    |

|                   | -2 <sup>2</sup> | 0.49              | 5.28            | 0.03             | 0.75            | 0.32              | 5.37            | 4.65            | 1.55            | 1.60            | ns    |

| 4 mA              | Std.            | 0.66              | 7.07            | 0.04             | 1.00            | 0.43              | 7.20            | 6.23            | 2.07            | 2.15            | ns    |

|                   | -1              | 0.56              | 6.01            | 0.04             | 0.85            | 0.36              | 6.12            | 5.30            | 1.76            | 1.83            | ns    |

|                   | -2              | 0.49              | 5.28            | 0.03             | 0.75            | 0.32              | 5.37            | 4.65            | 1.55            | 1.60            | ns    |

| 6 mA              | Std.            | 0.66              | 4.41            | 0.04             | 1.00            | 0.43              | 4.49            | 3.75            | 2.39            | 2.69            | ns    |

|                   | -1              | 0.56              | 3.75            | 0.04             | 0.85            | 0.36              | 3.82            | 3.19            | 2.04            | 2.29            | ns    |

|                   | -2              | 0.49              | 3.29            | 0.03             | 0.75            | 0.32              | 3.36            | 2.80            | 1.79            | 2.01            | ns    |

| 8 mA              | Std.            | 0.66              | 4.41            | 0.04             | 1.00            | 0.43              | 4.49            | 3.75            | 2.39            | 2.69            | ns    |

|                   | -1              | 0.56              | 3.75            | 0.04             | 0.85            | 0.36              | 3.82            | 3.19            | 2.04            | 2.29            | ns    |

|                   | -2              | 0.49              | 3.29            | 0.03             | 0.75            | 0.32              | 3.36            | 2.80            | 1.79            | 2.01            | ns    |

### Table 2-114 • 2.5 V LVCMOS Low Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Advanced I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.66              | 11.40           | 0.04             | 1.31            | 0.43              | 11.22           | 11.40           | 2.68            | 2.20            | 13.45            | 13.63            | ns    |

|                   | -1             | 0.56              | 9.69            | 0.04             | 1.11            | 0.36              | 9.54            | 9.69            | 2.28            | 1.88            | 11.44            | 11.60            | ns    |

|                   | -2             | 0.49              | 8.51            | 0.03             | 0.98            | 0.32              | 8.38            | 8.51            | 2.00            | 1.65            | 10.05            | 10.18            | ns    |

| 8 mA              | Std.           | 0.66              | 7.96            | 0.04             | 1.31            | 0.43              | 8.11            | 7.81            | 3.05            | 2.89            | 10.34            | 10.05            | ns    |

|                   | -1             | 0.56              | 6.77            | 0.04             | 1.11            | 0.36              | 6.90            | 6.65            | 2.59            | 2.46            | 8.80             | 8.55             | ns    |

|                   | -2             | 0.49              | 5.94            | 0.03             | 0.98            | 0.32              | 6.05            | 5.84            | 2.28            | 2.16            | 7.72             | 7.50             | ns    |

| 12 mA             | Std.           | 0.66              | 6.18            | 0.04             | 1.31            | 0.43              | 6.29            | 5.92            | 3.30            | 3.32            | 8.53             | 8.15             | ns    |

|                   | -1             | 0.56              | 5.26            | 0.04             | 1.11            | 0.36              | 5.35            | 5.03            | 2.81            | 2.83            | 7.26             | 6.94             | ns    |

|                   | -2             | 0.49              | 4.61            | 0.03             | 0.98            | 0.32              | 4.70            | 4.42            | 2.47            | 2.48            | 6.37             | 6.09             | ns    |

| 16 mA             | Std.           | 0.66              | 6.18            | 0.04             | 1.31            | 0.43              | 6.29            | 5.92            | 3.30            | 3.32            | 8.53             | 8.15             | ns    |

|                   | -1             | 0.56              | 5.26            | 0.04             | 1.11            | 0.36              | 5.35            | 5.03            | 2.81            | 2.83            | 7.26             | 6.94             | ns    |

|                   | -2             | 0.49              | 4.61            | 0.03             | 0.98            | 0.32              | 4.70            | 4.42            | 2.47            | 2.48            | 6.37             | 6.09             | ns    |

| 24 mA             | Std.           | 0.66              | 6.18            | 0.04             | 1.31            | 0.43              | 6.29            | 5.92            | 3.30            | 3.32            | 8.53             | 8.15             | ns    |

|                   | -1             | 0.56              | 5.26            | 0.04             | 1.11            | 0.36              | 5.35            | 5.03            | 2.81            | 2.83            | 7.26             | 6.94             | ns    |

|                   | -2             | 0.49              | 4.61            | 0.03             | 0.98            | 0.32              | 4.70            | 4.42            | 2.47            | 2.48            | 6.37             | 6.09             | ns    |

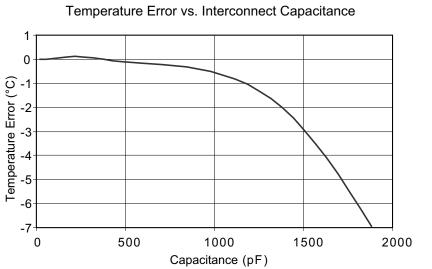

### Figure 2-143 • Input DDR Timing Diagram

### Timing Characteristics

| Table 2-180 • Input DDR Propagation Delays                                             |   |

|----------------------------------------------------------------------------------------|---|

| Commercial Temperature Range Conditions: T <sub>J</sub> = 70°C, Worst-Case VCC = 1.425 | V |

| Parameter               | Description                                          | -2   | -1   | Std. | Units |

|-------------------------|------------------------------------------------------|------|------|------|-------|

| t <sub>DDRICLKQ1</sub>  | Clock-to-Out Out_QR for Input DDR                    | 0.39 | 0.44 | 0.52 | ns    |

| t <sub>DDRICLKQ2</sub>  | Clock-to-Out Out_QF for Input DDR                    | 0.27 | 0.31 | 0.37 | ns    |

| t <sub>DDRISUD</sub>    | Data Setup for Input DDR                             | 0.28 | 0.32 | 0.38 | ns    |

| t <sub>DDRIHD</sub>     | Data Hold for Input DDR                              | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DDRICLR2Q1</sub> | Asynchronous Clear-to-Out Out_QR for Input DDR       | 0.57 | 0.65 | 0.76 | ns    |

| t <sub>DDRICLR2Q2</sub> | Asynchronous Clear-to-Out Out_QF for Input DDR       | 0.46 | 0.53 | 0.62 | ns    |

| t <sub>DDRIREMCLR</sub> | Asynchronous Clear Removal Time for Input DDR        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>DDRIRECCLR</sub> | Asynchronous Clear Recovery Time for Input DDR       | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>DDRIWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for Input DDR | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>DDRICKMPWH</sub> | Clock Minimum Pulse Width High for Input DDR         | 0.36 | 0.41 | 0.48 | ns    |

| t <sub>DDRICKMPWL</sub> | Clock Minimum Pulse Width Low for Input DDR          | 0.32 | 0.37 | 0.43 | ns    |

| F <sub>DDRIMAX</sub>    | Maximum Frequency for Input DDR                      | 1404 | 1232 | 1048 | MHz   |

#### ATRTNx Temperature Monitor Return

AT returns are the returns for the temperature sensors. The cathode terminal of the external diodes should be connected to these pins. There is one analog return pin for every two Analog Quads. The x in the ATRTNx designator indicates the quad pairing (x = 0 for AQ1 and AQ2, x = 1 for AQ2 and AQ3, ..., x = 4 for AQ8 and AQ9). The signals that drive these pins are called out as ATRETURNxy in the software (where x and y refer to the quads that share the return signal). ATRTN is internally connected to ground. It can be left floating when it is unused. The maximum capacitance allowed across the AT pins is 500 pF.

#### GL Globals

GL I/Os have access to certain clock conditioning circuitry (and the PLL) and/or have direct access to the global network (spines). Additionally, the global I/Os can be used as Pro I/Os since they have identical capabilities. Unused GL pins are configured as inputs with pull-up resistors. See more detailed descriptions of global I/O connectivity in the "Clock Conditioning Circuits" section on page 2-22.

Refer to the "User I/O Naming Convention" section on page 2-158 for a description of naming of global pins.

# JTAG Pins

Fusion devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). VCC must also be powered for the JTAG state machine to operate, even if the device is in bypass mode; VJTAG alone is insufficient. Both VJTAG and VCC to the Fusion part must be supplied to allow JTAG signals to transition the Fusion device.

Isolating the JTAG power supply in a separate I/O bank gives greater flexibility with supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned to be used, the VJTAG pin together with the TRST pin could be tied to GND.

#### TCK Test Clock

Test clock input for JTAG boundary scan, ISP, and UJTAG. The TCK pin does not have an internal pullup/-down resistor. If JTAG is not used, Microsemi recommends tying off TCK to GND or VJTAG through a resistor placed close to the FPGA pin. This prevents JTAG operation in case TMS enters an undesired state.

Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements. Refer to Table 2-183 for more information.

| VJTAG          | Tie-Off Resistance <sup>2, 3</sup> |

|----------------|------------------------------------|

| VJTAG at 3.3 V | 200 Ω to 1 kΩ                      |

| VJTAG at 2.5 V | 200 Ω to 1 kΩ                      |

| VJTAG at 1.8 V | 500 Ω to 1 kΩ                      |

| VJTAG at 1.5 V | 500 Ω to 1 kΩ                      |

Table 2-183 • Recommended Tie-Off Values for the TCK and TRST Pins

Notes:

- 1. Equivalent parallel resistance if more than one device is on JTAG chain.

- 2. The TCK pin can be pulled up/down.

- 3. The TRST pin can only be pulled down.

#### TDI Test Data Input

Serial input for JTAG boundary scan, ISP, and UJTAG usage. There is an internal weak pull-up resistor on the TDI pin.

#### TDO Test Data Output

Serial output for JTAG boundary scan, ISP, and UJTAG usage.

#### TMS Test Mode Select

The TMS pin controls the use of the IEEE1532 boundary scan pins (TCK, TDI, TDO, TRST). There is an internal weak pull-up resistor on the TMS pin.

### TRST Boundary Scan Reset Pin

The TRST pin functions as an active low input to asynchronously initialize (or reset) the boundary scan circuitry. There is an internal weak pull-up resistor on the TRST pin. If JTAG is not used, an external pull-down resistor could be included to ensure the TAP is held in reset mode. The resistor values must be chosen from Table 2-183 and must satisfy the parallel resistance value requirement. The values in Table 2-183 correspond to the resistor recommended when a single device is used and to the equivalent parallel resistor when multiple devices are connected via a JTAG chain.

In critical applications, an upset in the JTAG circuit could allow entering an undesired JTAG state. In such cases, Microsemi recommends tying off TRST to GND through a resistor placed close to the FPGA pin. Note that to operate at all VJTAG voltages, 500  $\Omega$  to 1 k $\Omega$  will satisfy the requirements.

# **Special Function Pins**

#### NC No Connect

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

#### DC Don't Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

#### NCAP Negative Capacitor

Negative Capacitor is where the negative terminal of the charge pump capacitor is connected. A capacitor, with a 2.2  $\mu$ F recommended value, is required to connect between PCAP and NCAP.

### PCAP Positive Capacitor

*Positive Capacitor* is where the positive terminal of the charge pump capacitor is connected. A capacitor, with a 2.2  $\mu$ F recommended value, is required to connect between PCAP and NCAP.

#### PUB Push Button

*Push button* is the connection for the external momentary switch used to turn on the 1.5 V voltage regulator and can be floating if not used.

#### PTBASE Pass Transistor Base

*Pass Transistor Base* is the control signal of the voltage regulator. This pin should be connected to the base of the external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.

#### PTEM Pass Transistor Emitter

Pass Transistor Emitter is the feedback input of the voltage regulator.

This pin should be connected to the emitter of the external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.

### XTAL1 Crystal Oscillator Circuit Input

Input to crystal oscillator circuit. Pin for connecting external crystal, ceramic resonator, RC network, or external clock input. When using an external crystal or ceramic oscillator, external capacitors are also recommended (Please refer to the crystal oscillator manufacturer for proper capacitor value).

If using external RC network or clock input, XTAL1 should be used and XTAL2 left unconnected. In the case where the Crystal Oscillator block is not used, the XTAL1 pin should be connected to GND and the XTAL2 pin should be left floating.

### XTAL2 Crystal Oscillator Circuit Input

Input to crystal oscillator circuit. Pin for connecting external crystal, ceramic resonator, RC network, or external clock input. When using an external crystal or ceramic oscillator, external capacitors are also recommended (Please refer to the crystal oscillator manufacturer for proper capacitor value).

If using external RC network or clock input, XTAL1 should be used and XTAL2 left unconnected. In the case where the Crystal Oscillator block is not used, the XTAL1 pin should be connected to GND and the XTAL2 pin should be left floating.

# Security

Fusion devices have a built-in 128-bit AES decryption core. The decryption core facilitates highly secure, in-system programming of the FPGA core array fabric and the FlashROM. The FlashROM and the FPGA core fabric can be programmed independently from each other, allowing the FlashROM to be updated without the need for change to the FPGA core fabric. The AES master key is stored in on-chip nonvolatile memory (flash). The AES master key can be preloaded into parts in a security-protected programming environment (such as the Microsemi in-house programming center), and then "blank" parts can be shipped to an untrusted programming or manufacturing center for final personalization with an AES-encrypted bitstream. Late stage product changes or personalization can be implemented easily and with high level security by simply sending a STAPL file with AES-encrypted data. Highly secure remote field updates over public networks (such as the Internet) are possible by sending and programming a STAPL file with AES-encrypted data. For more information, refer to the *Fusion Security* application note.

## 128-Bit AES Decryption

The 128-bit AES standard (FIPS-197) block cipher is the National Institute of Standards and Technology (NIST) replacement for DES (Data Encryption Standard FIPS46-2). AES has been designed to protect sensitive government information well into the 21st century. It replaces the aging DES, which NIST adopted in 1977 as a Federal Information Processing Standard used by federal agencies to protect sensitive, unclassified information. The 128-bit AES standard has 3.4 × 10<sup>38</sup> possible 128-bit key variants, and it has been estimated that it would take 1,000 trillion years to crack 128-bit AES cipher text using exhaustive techniques. Keys are stored (protected with security) in Fusion devices in nonvolatile flash memory. All programming files sent to the device can be authenticated by the part prior to programming to ensure that bad programming data is not loaded into the part that may possibly damage it. All programming verification is performed on-chip, ensuring that the contents of Fusion devices remain as secure as possible.

AES decryption can also be used on the 1,024-bit FlashROM to allow for remote updates of the FlashROM contents. This allows for easy support of subscription model products and protects them with measures designed to provide the highest level of security available. See the application note *Fusion Security* for more details.

# AES for Flash Memory

AES decryption can also be used on the flash memory blocks. This provides the best available security during update of the flash memory blocks. During runtime, the encrypted data can be clocked in via the JTAG interface. The data can be passed through the internal AES decryption engine, and the decrypted data can then be stored in the flash memory block.

# Programming

Programming can be performed using various programming tools, such as Silicon Sculptor II (BP Micro Systems) or FlashPro3 (Microsemi).

The user can generate STP programming files from the Designer software and can use these files to program a device.

Fusion devices can be programmed in-system. During programming, VCCOSC is needed in order to power the internal 100 MHz oscillator. This oscillator is used as a source for the 20 MHz oscillator that is used to drive the charge pump for programming.

| Parameter          | Description                | Conditions                                                                      | Temp.                  | Min | Тур  | Мах                                                                                                                                  | Unit |

|--------------------|----------------------------|---------------------------------------------------------------------------------|------------------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------|------|

| ICC <sup>1</sup>   | 1.5 V quiescent current    | Operational standby <sup>4</sup> ,                                              | T <sub>J</sub> = 25°C  |     | 5    | 7.5                                                                                                                                  | mA   |

|                    |                            | VCC = 1.575 V                                                                   | T <sub>J</sub> = 85°C  |     | 6.5  | 20                                                                                                                                   | mA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 14   | 48                                                                                                                                   | mA   |

|                    |                            | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , V <sub>CC</sub> = 0 V |                        |     | 0    | 0                                                                                                                                    | μA   |

| ICC33 <sup>2</sup> | 3.3 V analog supplies      | Operational standby <sup>4</sup> ,                                              | T <sub>J</sub> = 25°C  |     | 9.8  | .8 12                                                                                                                                | mA   |

|                    | current                    | VCC33 = 3.63 V                                                                  | T <sub>J</sub> = 85°C  |     | 9.8  | 12                                                                                                                                   | mA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 10.7 | 15                                                                                                                                   | mA   |

|                    |                            | Operational standby, only                                                       | T <sub>J</sub> = 25°C  |     | 0.30 | 2                                                                                                                                    | mA   |

|                    |                            | Analog Quad and –3.3 V<br>output ON, VCC33 = 3.63 V                             | T <sub>J</sub> = 85°C  |     | 0.30 | 2                                                                                                                                    | mA   |

|                    |                            | ····                                                                            | T <sub>J</sub> = 100°C |     | 0.45 | 2                                                                                                                                    | mA   |

|                    |                            | Standby mode <sup>5</sup> ,                                                     | T <sub>J</sub> = 25°C  |     | 2.9  | 2.9                                                                                                                                  | mA   |

|                    |                            | VCC33 = 3.63 V                                                                  | T <sub>J</sub> = 85°C  |     | 2.9  | 3.0                                                                                                                                  | mA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 3.5  | 6                                                                                                                                    | mA   |

|                    |                            | Sleep mode <sup>6</sup> , VCC33 = 3.63 V                                        | T <sub>J</sub> = 25°C  |     | 17   | 18                                                                                                                                   | μA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 85°C  |     | 18   | 20                                                                                                                                   | μA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 24   | 25                                                                                                                                   | μA   |

| ICCI <sup>3</sup>  | I/O quiescent current      | Operational standby <sup>6</sup> ,                                              | T <sub>J</sub> = 25°C  |     | 260  | 437                                                                                                                                  | μA   |

|                    |                            | VCCIx = 3.63 V                                                                  | T <sub>J</sub> = 85°C  |     | 260  | 437                                                                                                                                  | μA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 260  | 12         15         2         2         2         2         2.9         3.0         6         18         20         25         437 | μA   |

| IJTAG              | JTAG I/O quiescent current | Operational standby <sup>4</sup> ,                                              | T <sub>J</sub> = 25°C  |     | 80   | 100                                                                                                                                  | μA   |

|                    |                            | VJTAG = 3.63 V                                                                  | T <sub>J</sub> = 85°C  |     | 80   | 100                                                                                                                                  | μA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 80   | 100                                                                                                                                  | μA   |

|                    |                            | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , VJTAG = 0 V           |                        |     | 0    | 0                                                                                                                                    | μA   |

| IPP                | Programming supply current | Non-programming mode,<br>VPUMP = 3.63 V                                         | T <sub>J</sub> = 25°C  |     | 37   | 80                                                                                                                                   | μA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 85°C  |     | 37   | 80                                                                                                                                   | μA   |

|                    |                            |                                                                                 | T <sub>J</sub> = 100°C |     | 80   | 100                                                                                                                                  | μA   |

|                    |                            | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , VPUMP = 0 V           |                        |     | 0    | 0                                                                                                                                    | μA   |

Notes:

1. ICC is the 1.5 V power supplies, ICC, ICCPLL, ICC15A, ICCNVM.

2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

3. ICCI includes all ICCI0, ICCI1, and ICCI2.

4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

6. Sleep Mode, VCC = VJTAG = VPUMP = 0 V.

# *Table 3-13* • Summary of I/O Output Buffer Power (per pin)—Default I/O Software Settings<sup>1</sup> (continued)

|                                | C <sub>LOAD</sub> (pF) | VCCI (V) | Static Power<br>PDC8 (mW) <sup>2</sup> | Dynamic Power<br>PAC10 (μW/MHz) <sup>3</sup> |

|--------------------------------|------------------------|----------|----------------------------------------|----------------------------------------------|

| Differential                   |                        |          | •                                      | •                                            |

| LVDS                           | -                      | 2.5      | 7.74                                   | 88.92                                        |

| LVPECL                         | -                      | 3.3      | 19.54                                  | 166.52                                       |

| Applicable to Standard I/O Ban | s                      |          |                                        |                                              |

| Single-Ended                   |                        |          |                                        |                                              |

| 3.3 V LVTTL / 3.3 V LVCMOS     | 35                     | 3.3      | -                                      | 431.08                                       |

| 2.5 V LVCMOS                   | 35                     | 2.5      | -                                      | 247.36                                       |

| 1.8 V LVCMOS                   | 35                     | 1.8      | _                                      | 128.46                                       |

| 1.5 V LVCMOS (JESD8-11)        | 35                     | 1.5      | -                                      | 89.46                                        |

Notes:

1. Dynamic power consumption is given for standard load and software-default drive strength and output slew.

2. PDC8 is the static power (where applicable) measured on VCCI.

3. PAC10 is the total dynamic power measured on VCC and VCCI.

Package Pin Assignments

| FG256      |                 |                 |                 |                  |  |  |  |

|------------|-----------------|-----------------|-----------------|------------------|--|--|--|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |  |  |  |

| H3         | XTAL2           | XTAL2           | XTAL2           | XTAL2            |  |  |  |

| H4         | XTAL1           | XTAL1           | XTAL1           | XTAL1            |  |  |  |

| H5         | GNDOSC          | GNDOSC          | GNDOSC          | GNDOSC           |  |  |  |

| H6         | VCCOSC          | VCCOSC          | VCCOSC          | VCCOSC           |  |  |  |

| H7         | VCC             | VCC             | VCC             | VCC              |  |  |  |

| H8         | GND             | GND             | GND             | GND              |  |  |  |

| H9         | VCC             | VCC             | VCC             | VCC              |  |  |  |

| H10        | GND             | GND             | GND             | GND              |  |  |  |

| H11        | GDC0/IO38NDB1V0 | IO51NDB1V0      | IO47NDB2V0      | IO69NDB2V0       |  |  |  |

| H12        | GDC1/IO38PDB1V0 | IO51PDB1V0      | IO47PDB2V0      | IO69PDB2V0       |  |  |  |

| H13        | GDB1/IO39PDB1V0 | GCA1/IO49PDB1V0 | GCA1/IO45PDB2V0 | GCA1/IO64PDB2V0  |  |  |  |

| H14        | GDB0/IO39NDB1V0 | GCA0/IO49NDB1V0 | GCA0/IO45NDB2V0 | GCA0/IO64NDB2V0  |  |  |  |

| H15        | GCA0/IO36NDB1V0 | GCB0/IO48NDB1V0 | GCB0/IO44NDB2V0 | GCB0/IO63NDB2V0  |  |  |  |

| H16        | GCA1/IO36PDB1V0 | GCB1/IO48PDB1V0 | GCB1/IO44PDB2V0 | GCB1/IO63PDB2V0  |  |  |  |

| J1         | GEA0/IO44NDB3V0 | GFA0/IO66NDB3V0 | GFA0/IO70NDB4V0 | GFA0/IO105NDB4V0 |  |  |  |

| J2         | GEA1/IO44PDB3V0 | GFA1/IO66PDB3V0 | GFA1/IO70PDB4V0 | GFA1/IO105PDB4V0 |  |  |  |

| J3         | IO43NDB3V0      | GFB0/IO67NDB3V0 | GFB0/IO71NDB4V0 | GFB0/IO106NDB4V0 |  |  |  |

| J4         | GEC2/IO43PDB3V0 | GFB1/IO67PDB3V0 | GFB1/IO71PDB4V0 | GFB1/IO106PDB4V0 |  |  |  |

| J5         | NC              | GFC0/IO68NDB3V0 | GFC0/IO72NDB4V0 | GFC0/IO107NDB4V0 |  |  |  |

| J6         | NC              | GFC1/IO68PDB3V0 | GFC1/IO72PDB4V0 | GFC1/IO107PDB4V0 |  |  |  |

| J7         | GND             | GND             | GND             | GND              |  |  |  |

| J8         | VCC             | VCC             | VCC             | VCC              |  |  |  |

| J9         | GND             | GND             | GND             | GND              |  |  |  |

| J10        | VCC             | VCC             | VCC             | VCC              |  |  |  |

| J11        | GDC2/IO41NPB1V0 | IO56NPB1V0      | IO56NPB2V0      | IO83NPB2V0       |  |  |  |

| J12        | NC              | GDB0/IO53NPB1V0 | GDB0/IO53NPB2V0 | GDB0/IO80NPB2V0  |  |  |  |

| J13        | NC              | GDA1/IO54PDB1V0 | GDA1/IO54PDB2V0 | GDA1/IO81PDB2V0  |  |  |  |

| J14        | GDA0/IO40PDB1V0 | GDC1/IO52PPB1V0 | GDC1/IO52PPB2V0 | GDC1/IO79PPB2V0  |  |  |  |

| J15        | NC              | IO50NPB1V0      | IO51NSB2V0      | IO77NSB2V0       |  |  |  |

| J16        | GDA2/IO40NDB1V0 | GDC0/IO52NPB1V0 | GDC0/IO52NPB2V0 | GDC0/IO79NPB2V0  |  |  |  |

| K1         | NC              | IO65NPB3V0      | IO67NPB4V0      | IO92NPB4V0       |  |  |  |

| K2         | VCCIB3          | VCCIB3          | VCCIB4          | VCCIB4           |  |  |  |

| K3         | NC              | IO65PPB3V0      | IO67PPB4V0      | IO92PPB4V0       |  |  |  |

| K4         | NC              | IO64PDB3V0      | IO65PDB4V0      | IO96PDB4V0       |  |  |  |

| K5         | GND             | GND             | GND             | GND              |  |  |  |

| K6         | NC              | IO64NDB3V0      | IO65NDB4V0      | IO96NDB4V0       |  |  |  |

| K7         | VCC             | VCC             | VCC             | VCC              |  |  |  |

| K8         | GND             | GND             | GND             | GND              |  |  |  |

| Revision                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page              |  |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|

| v2.0, Revision 1<br>(continued) | The data in the 2.5 V LCMOS and LVCMOS 2.5 V / 5.0 V rows were updated in Table 2-75 $\bullet$ Fusion Standard and Advanced I/O – Hot-Swap and 5 V Input Tolerance Capabilities.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-143             |  |  |

|                                 | In Table 2-78 • Fusion Standard I/O Standards—OUT_DRIVE Settings, LVCMOS 1.5 V, for OUT_DRIVE 2, was changed from a dash to a check mark.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-152             |  |  |

|                                 | The "VCC15A Analog Power Supply (1.5 V)" definition was changed from "A 1.5 V analog power supply input should be used to provide this input" to "1.5 V clean analog power supply input for use by the 1.5 V portion of the analog circuitry."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |  |  |

|                                 | In the "VCC33PMP Analog Power Supply (3.3 V)" pin description, the following text was changed from "VCC33PMP should be powered up before or simultaneously with VCC33A" to "VCC33PMP should be powered up simultaneously with or after VCC33A."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |  |  |

|                                 | The "VCCOSC Oscillator Power Supply (3.3 V)" section was updated to include information about when to power the pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-223             |  |  |

|                                 | In the "128-Bit AES Decryption" section, FIPS-192 was incorrect and changed to FIPS-197.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-228             |  |  |

|                                 | The note in Table 2-84 • Fusion Standard and Advanced I/O Attributes vs. I/O Standard Applications was updated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-156             |  |  |

|                                 | For 1.5 V LVCMOS, the VIL and VIH parameters, 0.30 * VCCI was changed to 0.35 * VCCI and 0.70 * VCCI was changed to 0.65 * VCCI in Table 2-86 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions, Table 2-87 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions, and Table 2-88 • Summary of Maximum and Minimum DC Input and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions, and Table 2-88 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions, and Table 2-88 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions. | 2-164 to<br>2-165 |  |  |

|                                 | In Table 2-87 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions, the VIH max column was updated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |  |  |

|                                 | Table 2-89 • Summary of Maximum and Minimum DC Input Levels Applicable to Commercial and Industrial Conditions was updated to include notes 3 and 4. The temperature ranges were also updated in notes 1 and 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-165             |  |  |

|                                 | The titles in Table 2-92 • Summary of I/O Timing Characteristics – Software Default<br>Settings to Table 2-94 • Summary of I/O Timing Characteristics – Software Default<br>Settings were updated to "VCCI = I/O Standard Dependent."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-167 to<br>2-168 |  |  |

|                                 | Below Table 2-98 • I/O Short Currents IOSH/IOSL, the paragraph was updated to change 110°C to 100°C and three months was changed to six months.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-172             |  |  |

|                                 | Table 2-99 • Short Current Event Duration before Failure was updated to remove 110°C data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-174             |  |  |

|                                 | In Table 2-101 • I/O Input Rise Time, Fall Time, and Related I/O Reliability, LVTTL/LVCMOS rows were changed from 110°C to 100°C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-174             |  |  |

|                                 | VCC33PMP was added to Table 3-1 • Absolute Maximum Ratings. In addition, conditions for AV, AC, AG, and AT were also updated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-1               |  |  |

|                                 | VCC33PMP was added to Table 3-2 • Recommended Operating Conditions1. In addition, conditions for AV, AC, AG, and AT were also updated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-3               |  |  |