Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                     |

|--------------------------------|----------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | -                                                                          |

| Total RAM Bits                 | 276480                                                                     |

| Number of I/O                  | 119                                                                        |

| Number of Gates                | 1500000                                                                    |

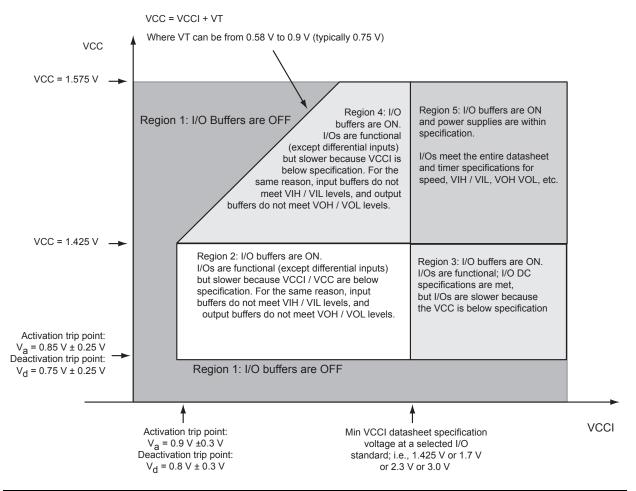

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                            |

| Package / Case                 | 256-LBGA                                                                   |

| Supplier Device Package        | 256-FPBGA (17x17)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1afs1500-fgg256 |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

## Fusion Device Family Overview

| Introduction              | 1-1  |

|---------------------------|------|

| General Description       | 1-1  |

| Unprecedented Integration | 1-4  |

| Related Documents         | 1-10 |

# **Device Architecture**

| Fusion Stack Architecture |  |

|---------------------------|--|

| Core Architecture         |  |

| Clocking Resources        |  |

| Real-Time Counter System  |  |

| Embedded Memories         |  |

| Analog Block              |  |

| Analog Configuration MUX  |  |

| User I/Os                 |  |

| Pin Descriptions          |  |

| Security                  |  |

# DC and Power Characteristics

| General Specifications        | 3-1  |

|-------------------------------|------|

| Calculating Power Dissipation | 3-10 |

| Power Consumption             | 3-32 |

# Package Pin Assignments

| QN108 | <br>    | <br> | <br>      | <br> | <br> | <br>    | <br>    | <br> | <br> |     | <br> | <br>. 4- | 1 |

|-------|------|------|------|------|------|------|---------|------|-----------|------|------|---------|---------|------|------|-----|------|----------|---|

| QN180 |      |      |      |      |      |      |         |      |           |      |      |         |         |      |      |     |      |          |   |

| PQ208 |      |      |      |      |      |      |         |      |           |      |      |         |         |      |      |     |      |          |   |

| FG256 |      |      |      |      |      |      |         |      |           |      |      |         |         |      |      |     |      |          |   |

| FG484 |      |      |      |      |      |      |         |      |           |      |      |         |         |      |      |     |      |          |   |

| FG676 | <br> | <br> | <br> | <br> | <br> | <br> | <br>••• | <br> | <br>• • • | <br> | <br> | <br>• • | <br>• • | <br> | <br> | ••• | <br> | <br>4-2  | 7 |

### **Datasheet Information**

| List of Changes                                                         |   |

|-------------------------------------------------------------------------|---|

| Datasheet Categories                                                    |   |

| Safety Critical, Life Support, and High-Reliability Applications Policy | / |

### VersaTile Characteristics

#### Sample VersaTile Specifications—Combinatorial Module

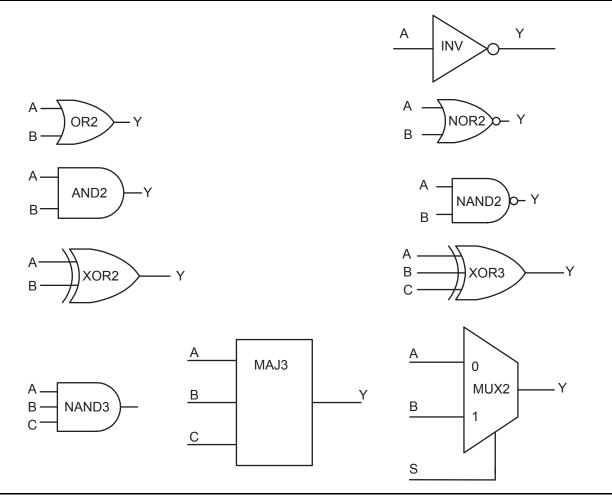

The Fusion library offers all combinations of LUT-3 combinatorial functions. In this section, timing characteristics are presented for a sample of the library (Figure 2-3). For more details, refer to the *IGLOO, ProASIC3, SmartFusion, and Fusion Macro Library Guide*.

Figure 2-3 • Sample of Combinatorial Cells

# **Routing Architecture**

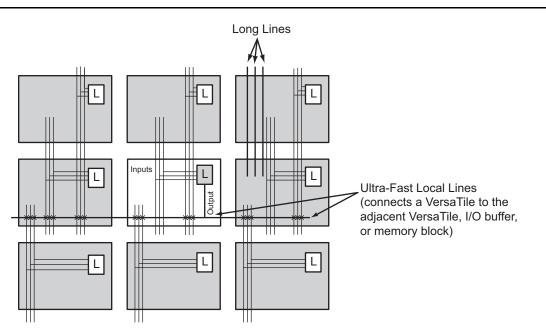

The routing structure of Fusion devices is designed to provide high performance through a flexible four-level hierarchy of routing resources: ultra-fast local resources; efficient long-line resources; high-speed very-long-line resources; and the high-performance VersaNet networks.

The ultra-fast local resources are dedicated lines that allow the output of each VersaTile to connect directly to every input of the eight surrounding VersaTiles (Figure 2-8). The exception to this is that the SET/CLR input of a VersaTile configured as a D-flip-flop is driven only by the VersaNet global network.

The efficient long-line resources provide routing for longer distances and higher-fanout connections. These resources vary in length (spanning one, two, or four VersaTiles), run both vertically and horizontally, and cover the entire Fusion device (Figure 2-9 on page 2-9). Each VersaTile can drive signals onto the efficient long-line resources, which can access every input of every VersaTile. Active buffers are inserted automatically by routing software to limit loading effects.

The high-speed very-long-line resources, which span the entire device with minimal delay, are used to route very long or high-fanout nets: length  $\pm 12$  VersaTiles in the vertical direction and length  $\pm 16$  in the horizontal direction from a given core VersaTile (Figure 2-10 on page 2-10). Very long lines in Fusion devices, like those in ProASIC3 devices, have been enhanced. This provides a significant performance boost for long-reach signals.

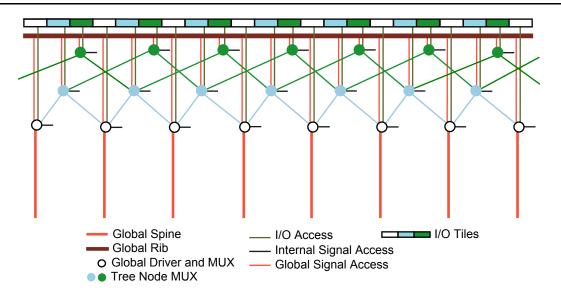

The high-performance VersaNet global networks are low-skew, high-fanout nets that are accessible from external pins or from internal logic (Figure 2-11 on page 2-11). These nets are typically used to distribute clocks, reset signals, and other high-fanout nets requiring minimum skew. The VersaNet networks are implemented as clock trees, and signals can be introduced at any junction. These can be employed hierarchically, with signals accessing every input on all VersaTiles.

## **Clock Aggregation**

Clock aggregation allows for multi-spine clock domains. A MUX tree provides the necessary flexibility to allow long lines or I/Os to access domains of one, two, or four global spines. Signal access to the clock aggregation system is achieved through long-line resources in the central rib, and also through local resources in the north and south ribs, allowing I/Os to feed directly into the clock system. As Figure 2-14 indicates, this access system is contiguous.

There is no break in the middle of the chip for north and south I/O VersaNet access. This is different from the quadrant clocks, located in these ribs, which only reach the middle of the rib. Refer to the *Using Global Resources in Actel Fusion Devices* application note.

Figure 2-14 • Clock Aggregation Tree Architecture

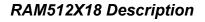

Figure 2-49 • RAM512X18

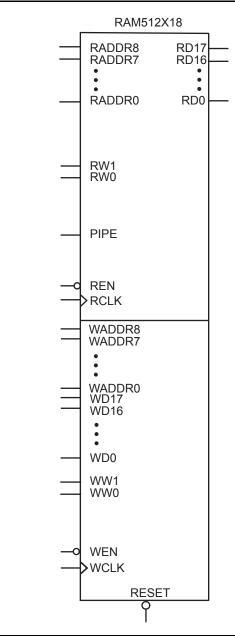

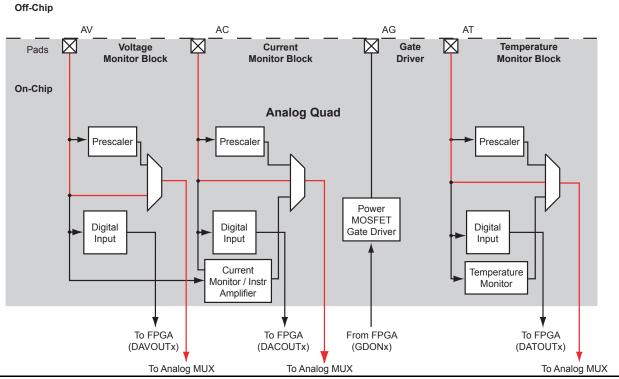

The third part of the Analog Quad is called the Gate Driver Block, and its output pin is named AG. This section is used to drive an external FET. There are two modes available: a High Current Drive mode and a Current Source Control mode. Both negative and positive voltage polarities are available, and in the current source control mode, four different current levels are available.

The fourth section of the Analog Quad is called the Temperature Monitor Block, and its input pin name is AT. This block is similar to the Voltage Monitor Block, except that it has an additional function: it can be used to monitor the temperature of an external diode-connected transistor. It has a modified prescaler and is limited to positive voltages only.

The Analog Quad can be configured during design time by Libero SoC; however, the ACM can be used to change the parameters of any of these I/Os during runtime. This type of change is referred to as a context switch. The Analog Quad is a modular structure that is replicated to generate the analog I/O resources. Each Fusion device supports between 5 and 10 Analog Quads.

The analog pads are numbered to clearly identify both the type of pad (voltage, current, gate driver, or temperature pad) and its corresponding Analog Quad (AV0, AC0, AG0, AT0, AV1, ..., AC9, AG9, and AT9). There are three types of input pads (AVx, ACx, and ATx) and one type of analog output pad (AGx). Since there can be up to 10 Analog Quads on a device, there can be a maximum of 30 analog input pads and 10 analog output pads.

Figure 2-65 • Analog Quad

### Voltage Monitor

The Fusion Analog Quad offers a robust set of voltage-monitoring capabilities unique in the FPGA industry. The Analog Quad comprises three analog input pads— Analog Voltage (AV), Analog Current (AC), and Analog Temperature (AT)—and a single gate driver output pad, Analog Gate (AG). There are many common characteristics among the analog input pads. Each analog input can be configured to connect directly to the input MUX of the ADC. When configured in this manner (Figure 2-66), there will be no prescaling of the input signal. Care must be taken in this mode not to drive the ADC into saturation by applying an input voltage greater than the reference voltage. The internal reference voltage of the ADC is 2.56 V. Optionally, an external reference can be supplied by the user. The external reference can be a maximum of 3.3 V DC.

Figure 2-66 • Analog Quad Direct Connect

The Analog Quad offers a wide variety of prescaling options to enable the ADC to resolve the input signals. Figure 2-67 shows the path through the Analog Quad for a signal that is to be prescaled prior to conversion. The ADC internal reference voltage and the prescaler factors were selected to make both prescaling and postscaling of the signals easy binary calculations (refer to Table 2-57 on page 2-130 for details). When an analog input pad is configured with a prescaler, there will be a 1 M $\Omega$  resistor to ground. This occurs even when the device is in power-down mode. In low power standby or sleep mode (VCC is OFF, VCC33A is ON, VCCI is ON) or when the resource is not used, analog inputs are pulled down to ground through a 1 M $\Omega$  resistor. The gate driver output is floating (or tristated), and there is no extra current on VCC33A.

These scaling factors hold true whether the particular pad is configured to accept a positive or negative voltage. Note that whereas the AV and AC pads support the same prescaling factors, the AT pad supports a reduced set of prescaling factors and supports positive voltages only.

| Analog MUX Channel | Signal                       | Analog Quad Number |  |  |  |  |  |

|--------------------|------------------------------|--------------------|--|--|--|--|--|

| 16                 | AV5                          |                    |  |  |  |  |  |

| 17                 | AC5                          | Analog Quad 5      |  |  |  |  |  |

| 18                 | AT5                          |                    |  |  |  |  |  |

| 19                 | AV6                          |                    |  |  |  |  |  |

| 20                 | AC6                          | Analog Quad 6      |  |  |  |  |  |

| 21                 | AT6                          |                    |  |  |  |  |  |

| 22                 | AV7                          |                    |  |  |  |  |  |

| 23                 | AC7                          | Analog Quad 7      |  |  |  |  |  |

| 24                 | AT7                          |                    |  |  |  |  |  |

| 25                 | AV8                          |                    |  |  |  |  |  |

| 26                 | AC8                          | Analog Quad 8      |  |  |  |  |  |

| 27                 | AT8                          |                    |  |  |  |  |  |

| 28                 | AV9                          |                    |  |  |  |  |  |

| 29                 | AC9                          | Analog Quad 9      |  |  |  |  |  |

| 30                 | AT9                          |                    |  |  |  |  |  |

| 31                 | Internal temperature monitor |                    |  |  |  |  |  |

#### Table 2-40 • Analog MUX Channels (continued)

The ADC can be powered down independently of the FPGA core, as an additional control or for powersaving considerations, via the PWRDWN pin of the Analog Block. The PWRDWN pin controls only the comparators in the ADC.

#### **ADC Modes**

The Fusion ADC can be configured to operate in 8-, 10-, or 12-bit modes, power-down after conversion, and dynamic calibration. This is controlled by MODE[3:0], as defined in Table 2-41 on page 2-106.

The output of the ADC is the RESULT[11:0] signal. In 8-bit mode, the Most Significant 8 Bits RESULT[11:4] are used as the ADC value and the Least Significant 4 Bits RESULT[3:0] are logical '0's. In 10-bit mode, RESULT[11:2] are used the ADC value and RESULT[1:0] are logical 0s.

| Table 2-41 • Mode | Bits Function |

|-------------------|---------------|

|-------------------|---------------|

| Name | Bits | Function                                                                                          |

|------|------|---------------------------------------------------------------------------------------------------|

| MODE | 3    | 0 – Internal calibration after every conversion; two ADCCLK cycles are used after the conversion. |

|      |      | 1 – No calibration after every conversion                                                         |

| MODE | 2    | 0 – Power-down after conversion                                                                   |

|      |      | 1 – No Power-down after conversion                                                                |

| MODE | 1:0  | 00 – 10-bit                                                                                       |

|      |      | 01 – 12-bit                                                                                       |

|      |      | 10 – 8-bit                                                                                        |

|      |      | 11 – Unused                                                                                       |

Table 2-61 details the settings available to either power down or enable the prescaler associated with the analog inputs AV, AC, and AT.

#### Table 2-61 • Prescaler Op Amp Power-Down Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)

| Control Lines Bx[7] | Prescaler Op Amp |

|---------------------|------------------|

| 0                   | Power-down       |

| 1                   | Operational      |

Table 2-62 details the settings available to enable the Current Monitor Block associated with the AC pin.

#### Table 2-62 • Current Monitor Input Switch Control Truth Table—AV (x = 0)

| Control Lines B0[4] | Current Monitor Input Switch |

|---------------------|------------------------------|

| 0                   | Off                          |

| 1                   | On                           |

Table 2-63 details the settings available to configure the drive strength of the gate drive when not in highdrive mode.

#### Table 2-63 • Low-Drive Gate Driver Current Truth Table (AG)

| Control Lines B2[3] | Control Lines B2[2] | Current (µA) |

|---------------------|---------------------|--------------|

| 0                   | 0                   | 1            |

| 0                   | 1                   | 3            |

| 1                   | 0                   | 10           |

| 1                   | 1                   | 30           |

Table 2-64 details the settings available to set the polarity of the gate driver (either p-channel- or n-channel-type devices).

#### Table 2-64 • Gate Driver Polarity Truth Table (AG)

| Control Lines B2[6] | Gate Driver Polarity |

|---------------------|----------------------|

| 0                   | Positive             |

| 1                   | Negative             |

Table 2-65 details the settings available to turn on the Gate Driver and set whether high-drive mode is on or off.

#### Table 2-65 • Gate Driver Control Truth Table (AG)

| Control Lines B2[7] | GDON | Gate Driver   |

|---------------------|------|---------------|

| 0                   | 0    | Off           |

| 0                   | 1    | Low drive on  |

| 1                   | 0    | Off           |

| 1                   | 1    | High drive on |

Table 2-66 details the settings available to turn on and off the chip internal temperature monitor.

Note: For the internal temperature monitor to function, Bit 0 of Byte 2 for all 10 Quads must be set.

#### Table 2-66 • Internal Temperature Monitor Control Truth Table

| Control Lines B2[0] | PDTMB | Chip Internal Temperature Monitor |

|---------------------|-------|-----------------------------------|

| 0                   | 0     | Off                               |

| 1                   | 1     | On                                |

### Table 2-71 • Fusion Standard and Advanced I/O Features

| I/O Bank Voltage (typical) | Minibank Voltage (typical) | LVTTL/LVCMOS 3.3 V | LVCMOS 2.5 V | LVCMOS 1.8 V | LVCMOS 1.5 V | 3.3 V PCI / PCI-X | GTL + (3.3 V) | GTL + (2.5 V) | GTL (3.3 V) | GTL (2.5 V) | HSTL Class I and II (1.5 V) | SSTL2 Class I and II (2.5 V) | SSTL3 Class I and II (3.3 V) | LVDS (2.5 V ± 5%) | LVPECL (3.3 V) |

|----------------------------|----------------------------|--------------------|--------------|--------------|--------------|-------------------|---------------|---------------|-------------|-------------|-----------------------------|------------------------------|------------------------------|-------------------|----------------|

| 3.3 V                      | -                          |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

|                            | 0.80 V                     |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

|                            | 1.00 V                     |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

|                            | 1.50 V                     |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

| 2.5 V                      | -                          |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

|                            | 0.80 V                     |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

|                            | 1.00 V                     |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

|                            | 1.25 V                     |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

| 1.8 V                      | -                          |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

| 1.5 V                      | -                          |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

|                            | 0.75 V                     |                    |              |              |              |                   |               |               |             |             |                             |                              |                              |                   |                |

Note: White box: Allowable I/O standard combinations Gray box: Illegal I/O standard combinations

# Features Supported on Pro I/Os

Table 2-72 lists all features supported by transmitter/receiver for single-ended and differential I/Os.

### Table 2-72 • Fusion Pro I/O Features

| Feature                                             | Description                                                                                                                                                                                                                            |  |  |  |  |  |  |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Single-ended and voltage-<br>referenced transmitter | <ul> <li>Hot insertion in every mode except PCI or 5 V input tolerant (these modes use<br/>clamp diodes and do not allow hot insertion)</li> </ul>                                                                                     |  |  |  |  |  |  |

| features                                            | Activation of hot insertion (disabling the clamp diode) is selectable by I/Os.                                                                                                                                                         |  |  |  |  |  |  |

|                                                     | Weak pull-up and pull-down                                                                                                                                                                                                             |  |  |  |  |  |  |

|                                                     | Two slew rates                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                                                     | <ul> <li>Skew between output buffer enable/disable time: 2 ns delay (rising edge) and<br/>0 ns delay (falling edge); see "Selectable Skew between Output Buffer<br/>Enable/Disable Time" on page 2-149 for more information</li> </ul> |  |  |  |  |  |  |

|                                                     | Five drive strengths                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                                                     | 5 V-tolerant receiver ("5 V Input Tolerance" section on page 2-144)                                                                                                                                                                    |  |  |  |  |  |  |

|                                                     | <ul> <li>LVTTL/LVCMOS 3.3 V outputs compatible with 5 V TTL inputs ("5 V Output<br/>Tolerance" section on page 2-148)</li> </ul>                                                                                                       |  |  |  |  |  |  |

|                                                     | High performance (Table 2-76 on page 2-143)                                                                                                                                                                                            |  |  |  |  |  |  |

| Single-ended receiver features                      | Schmitt trigger option                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                                                     | SD protection                                                                                                                                                                                                                          |  |  |  |  |  |  |

|                                                     | <ul> <li>Programmable delay: 0 ns if bypassed, 0.625 ns with '000' setting, 6.575 ns<br/>with '111' setting, 0.85-ns intermediate delay increments (at 25°C, 1.5 V)</li> </ul>                                                         |  |  |  |  |  |  |

|                                                     | High performance (Table 2-76 on page 2-143)                                                                                                                                                                                            |  |  |  |  |  |  |

|                                                     | <ul> <li>Separate ground planes, GND/GNDQ, for input buffers only to avoid output-<br/>induced noise in the input circuitry</li> </ul>                                                                                                 |  |  |  |  |  |  |

| Voltage-referenced differential receiver features   | <ul> <li>Programmable Delay: 0 ns if bypassed, 0.625 ns with '000' setting, 6.575 ns<br/>with '111' setting, 0.85-ns intermediate delay increments (at 25°C, 1.5 V)</li> </ul>                                                         |  |  |  |  |  |  |

|                                                     | High performance (Table 2-76 on page 2-143)                                                                                                                                                                                            |  |  |  |  |  |  |

|                                                     | <ul> <li>Separate ground planes, GND/GNDQ, for input buffers only to avoid output-<br/>induced noise in the input circuitry</li> </ul>                                                                                                 |  |  |  |  |  |  |

| CMOS-style LVDS, BLVDS,<br>M-LVDS, or LVPECL        | <ul> <li>Two I/Os and external resistors are used to provide a CMOS-style LVDS,<br/>BLVDS, M-LVDS, or LVPECL transmitter solution.</li> </ul>                                                                                          |  |  |  |  |  |  |

| transmitter                                         | Activation of hot insertion (disabling the clamp diode) is selectable by I/Os.                                                                                                                                                         |  |  |  |  |  |  |

|                                                     | Weak pull-up and pull-down                                                                                                                                                                                                             |  |  |  |  |  |  |

|                                                     | Fast slew rate                                                                                                                                                                                                                         |  |  |  |  |  |  |

| LVDS/LVPECL differential                            | ESD protection                                                                                                                                                                                                                         |  |  |  |  |  |  |

| receiver features                                   | High performance (Table 2-76 on page 2-143)                                                                                                                                                                                            |  |  |  |  |  |  |

|                                                     | <ul> <li>Programmable delay: 0.625 ns with '000' setting, 6.575 ns with '111' setting,<br/>0.85-ns intermediate delay increments (at 25°C, 1.5 V)</li> </ul>                                                                           |  |  |  |  |  |  |

|                                                     | Separate input buffer ground and power planes to avoid output-induced noise     in the input circuitry                                                                                                                                 |  |  |  |  |  |  |

# **Hot-Swap Support**

Hot-swapping (also called hot plugging) is the operation of hot insertion or hot removal of a card in (or from) a powered-up system. The levels of hot-swap support and examples of related applications are described in Table 2-74. The I/Os also need to be configured in hot insertion mode if hot plugging compliance is required.

Table 2-74 • Levels of Hot-Swap Support

| Hot<br>Swapping<br>Level | Description                     | Power<br>Applied<br>to Device | Bus State                                                                                                                   | Card<br>Ground<br>Connection                                                                        | Device<br>Circuitry<br>Connected<br>to Bus Pins | Example of<br>Application with<br>Cards that Contain<br>Fusion Devices                                                                                                                        | Compliance of<br>Fusion Devices                                                                            |

|--------------------------|---------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 1                        | Cold-swap                       | No                            | _                                                                                                                           | _                                                                                                   | _                                               | System and card with<br>Microsemi FPGA chip<br>are powered down,<br>then card gets<br>plugged into system,<br>then power supplies<br>are turned on for<br>system but not for<br>FPGA on card. | Compliant I/Os<br>can but do not<br>have to be set to<br>hot insertion<br>mode.                            |

| 2                        | Hot-swap<br>while reset         | Yes                           | Held in<br>reset state                                                                                                      | Must be made<br>and<br>maintained for<br>1 ms before,<br>during, and<br>after insertion/<br>removal | _                                               | In PCI hot plug<br>specification, reset<br>control circuitry<br>isolates the card<br>busses until the card<br>supplies are at their<br>nominal operating<br>levels and stable.                | Compliant I/Os<br>can but do not<br>have to be set to<br>hot insertion<br>mode.                            |

| 3                        | Hot-swap<br>while bus<br>idle   |                               | Held idle<br>(no ongoing<br>I/O<br>processes<br>during<br>insertion/re<br>moval)                                            | Same as<br>Level 2                                                                                  | glitch-free<br>during<br>power-up or            | no toggling activity on bus. It is critical that                                                                                                                                              | Compliant with<br>cards with two<br>levels of staging.<br>I/Os have to be<br>set to hot<br>insertion mode. |

| 4                        | Hot-swap on<br>an active<br>bus | Yes                           | Bus may<br>have active<br>I/O<br>processes<br>ongoing,<br>but device<br>being<br>inserted or<br>removed<br>must be<br>idle. | Same as<br>Level 2                                                                                  | Same as<br>Level 3                              | is critical that the logic<br>states set on the bus<br>signal do not get                                                                                                                      | Compliant with<br>cards with two<br>levels of staging.<br>I/Os have to be<br>set to hot<br>insertion mode. |

Device Architecture

#### Table 2-123 • 1.8 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V Applicable to Advanced I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.           | 0.66              | 11.86           | 0.04             | 1.22            | 0.43              | 9.14            | 11.86           | 2.77            | 1.66            | 11.37            | 14.10            | ns    |

|                   | -1             | 0.56              | 10.09           | 0.04             | 1.04            | 0.36              | 7.77            | 10.09           | 2.36            | 1.41            | 9.67             | 11.99            | ns    |

|                   | -2             | 0.49              | 8.86            | 0.03             | 0.91            | 0.32              | 6.82            | 8.86            | 2.07            | 1.24            | 8.49             | 10.53            | ns    |

| 4 mA              | Std.           | 0.66              | 6.91            | 0.04             | 1.22            | 0.43              | 5.86            | 6.91            | 3.22            | 2.84            | 8.10             | 9.15             | ns    |

|                   | -1             | 0.56              | 5.88            | 0.04             | 1.04            | 0.36              | 4.99            | 5.88            | 2.74            | 2.41            | 6.89             | 7.78             | ns    |

|                   | -2             | 0.49              | 5.16            | 0.03             | 0.91            | 0.32              | 4.38            | 5.16            | 2.41            | 2.12            | 6.05             | 6.83             | ns    |

| 8 mA              | Std.           | 0.66              | 4.45            | 0.04             | 1.22            | 0.43              | 4.18            | 4.45            | 3.53            | 3.38            | 6.42             | 6.68             | ns    |

|                   | -1             | 0.56              | 3.78            | 0.04             | 1.04            | 0.36              | 3.56            | 3.78            | 3.00            | 2.88            | 5.46             | 5.69             | ns    |

|                   | -2             | 0.49              | 3.32            | 0.03             | 0.91            | 0.32              | 3.12            | 3.32            | 2.64            | 2.53            | 4.79             | 4.99             | ns    |

| 12 mA             | Std.           | 0.66              | 3.92            | 0.04             | 1.22            | 0.43              | 3.93            | 3.92            | 3.60            | 3.52            | 6.16             | 6.16             | ns    |

|                   | -1             | 0.56              | 3.34            | 0.04             | 1.04            | 0.36              | 3.34            | 3.34            | 3.06            | 3.00            | 5.24             | 5.24             | ns    |

|                   | -2             | 0.49              | 2.93            | 0.03             | 0.91            | 0.32              | 2.93            | 2.93            | 2.69            | 2.63            | 4.60             | 4.60             | ns    |

| 16 mA             | Std.           | 0.66              | 3.53            | 0.04             | 1.22            | 0.43              | 3.60            | 3.04            | 3.70            | 4.08            | 5.84             | 5.28             | ns    |

|                   | -1             | 0.56              | 3.01            | 0.04             | 1.04            | 0.36              | 3.06            | 2.59            | 3.15            | 3.47            | 4.96             | 4.49             | ns    |

|                   | -2             | 0.49              | 2.64            | 0.03             | 0.91            | 0.32              | 2.69            | 2.27            | 2.76            | 3.05            | 4.36             | 3.94             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

#### Table 2-124 • 1.8 V LVCMOS Low Slew

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 15.01           | 0.04             | 1.20            | 0.43              | 13.15           | 15.01           | 1.99            | 1.99            | ns    |

|                   | -1             | 0.56              | 12.77           | 0.04             | 1.02            | 0.36              | 11.19           | 12.77           | 1.70            | 1.70            | ns    |

|                   | -2             | 0.49              | 11.21           | 0.03             | 0.90            | 0.32              | 9.82            | 11.21           | 1.49            | 1.49            | ns    |

| 4 mA              | Std.           | 0.66              | 10.10           | 0.04             | 1.20            | 0.43              | 9.55            | 10.10           | 2.41            | 2.37            | ns    |

|                   | -1             | 0.56              | 8.59            | 0.04             | 1.02            | 0.36              | 8.13            | 8.59            | 2.05            | 2.02            | ns    |

|                   | -2             | 0.49              | 7.54            | 0.03             | 0.90            | 0.32              | 7.13            | 7.54            | 1.80            | 1.77            | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

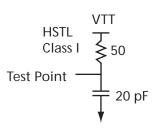

### HSTL Class I

High-Speed Transceiver Logic is a general-purpose high-speed 1.5 V bus standard (EIA/JESD8-6). Fusion devices support Class I. This provides a differential amplifier input buffer and a push-pull output buffer.

| HSTL<br>Class I   | VIL              |            | VIH        |           | VOL VOH   |            | IOL | юн | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|------------------|------------|------------|-----------|-----------|------------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength | Min. Max.<br>V V |            | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V  | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 8 mA              | -0.3             | VREF – 0.1 | VREF + 0.1 | 3.6       | 0.4       | VCCI – 0.4 | 8   | 8  | 39                      | 32                      | 10               | 10               |

Table 2-150 • Minimum and Maximum DC Input and Output Levels

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

#### Figure 2-128 • AC Loading

Table 2-151 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.1    | VREF + 0.1     | 0.75                 | 0.75            | 0.75           | 20                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

Table 2-152 • HSTL Class I

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.4 V, VREF = 0.75 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 3.18            | 0.04             | 2.12            | 0.43              | 3.24            | 3.14            |                 |                 | 5.47             | 5.38             | ns    |

| -1             | 0.56              | 2.70            | 0.04             | 1.81            | 0.36              | 2.75            | 2.67            |                 |                 | 4.66             | 4.58             | ns    |

| -2             | 0.49              | 2.37            | 0.03             | 1.59            | 0.32              | 2.42            | 2.35            |                 |                 | 4.09             | 4.02             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

### Table 2-175 • Parameter Definitions and Measuring Nodes

| Parameter Name        | Parameter Definition                                            | Measuring Nodes<br>(from, to)* |

|-----------------------|-----------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                          | HH, DOUT                       |

| tosud                 | Data Setup Time for the Output Data Register                    | FF, HH                         |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                     | FF, HH                         |

| t <sub>OSUE</sub>     | Enable Setup Time for the Output Data Register                  | GG, HH                         |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                   | GG, HH                         |

| t <sub>OCLR2Q</sub>   | Asynchronous Clear-to-Q of the Output Data Register             | LL, DOUT                       |

| t <sub>OREMCLR</sub>  | Asynchronous Clear Removal Time for the Output Data Register    | LL, HH                         |

| t <sub>ORECCLR</sub>  | Asynchronous Clear Recovery Time for the Output Data Register   | LL, HH                         |

| t <sub>oeclkq</sub>   | Clock-to-Q of the Output Enable Register                        | HH, EOUT                       |

| tOESUD                | Data Setup Time for the Output Enable Register                  | JJ, HH                         |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                   | JJ, HH                         |

| tOESUE                | Enable Setup Time for the Output Enable Register                | KK, HH                         |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                 | KK, HH                         |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register           | II, EOUT                       |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register  | II, HH                         |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register | II, HH                         |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                           | AA, EE                         |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                     | CC, AA                         |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                      | CC, AA                         |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                   | BB, AA                         |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                    | BB, AA                         |

| t <sub>ICLR2Q</sub>   | Asynchronous Clear-to-Q of the Input Data Register              | DD, EE                         |

| t <sub>IREMCLR</sub>  | Asynchronous Clear Removal Time for the Input Data Register     | DD, AA                         |

| t <sub>IRECCLR</sub>  | Asynchronous Clear Recovery Time for the Input Data Register    | DD, AA                         |

*Note:* \*See Figure 2-138 on page 2-214 for more information.

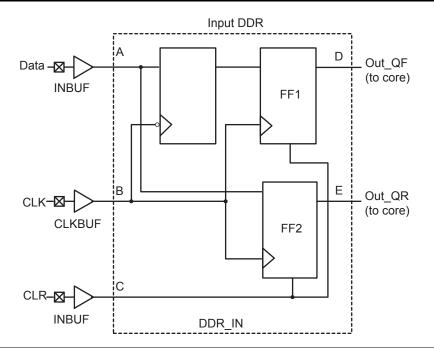

# DDR Module Specifications

Input DDR Module

### Figure 2-142 • Input DDR Timing Model

### Table 2-179 • Parameter Definitions

| Parameter Name          | Parameter Definition         | Measuring Nodes (from, to) |  |  |

|-------------------------|------------------------------|----------------------------|--|--|

| t <sub>DDRICLKQ1</sub>  | Clock-to-Out Out_QR          | B, D                       |  |  |

| t <sub>DDRICLKQ2</sub>  | Clock-to-Out Out_QF          | B, E                       |  |  |

| t <sub>DDRISUD</sub>    | Data Setup Time of DDR Input | A, B                       |  |  |

| t <sub>DDRIHD</sub>     | Data Hold Time of DDR Input  | A, B                       |  |  |

| t <sub>DDRICLR2Q1</sub> | Clear-to-Out Out_QR          | C, D                       |  |  |

| t <sub>DDRICLR2Q2</sub> | Clear-to-Out Out_QF          | C, E                       |  |  |

| t <sub>DDRIREMCLR</sub> | Clear Removal                | С, В                       |  |  |

| t <sub>DDRIRECCLR</sub> | Clear Recovery               | С, В                       |  |  |

| Symbol              | Parameter <sup>2</sup>                        |                               | Commercial     | Industrial     | Units |

|---------------------|-----------------------------------------------|-------------------------------|----------------|----------------|-------|

| Τ <sub>J</sub>      | Junction temperature                          |                               | 0 to +85       | -40 to +100    | °C    |

| VCC                 | 1.5 V DC core supply voltage                  |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VJTAG               | JTAG DC voltage                               |                               | 1.4 to 3.6     | 1.4 to 3.6     | V     |

| VPUMP               | Programming voltage                           | Programming mode <sup>3</sup> | 3.15 to 3.45   | 3.15 to 3.45   | V     |

|                     |                                               | Operation <sup>4</sup>        | 0 to 3.6       | 0 to 3.6       | V     |

| VCCPLL              | Analog power supply (PLL)                     |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VCCI                | 1.5 V DC supply voltage                       |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

|                     | 1.8 V DC supply voltage                       |                               | 1.7 to 1.9     | 1.7 to 1.9     | V     |

|                     | 2.5 V DC supply voltage                       |                               | 2.3 to 2.7     | 2.3 to 2.7     | V     |

|                     | 3.3 V DC supply voltage                       |                               | 3.0 to 3.6     | 3.0 to 3.6     | V     |

|                     | LVDS differential I/O                         |                               | 2.375 to 2.625 | 2.375 to 2.625 | V     |

|                     | LVPECL differential I/O                       |                               | 3.0 to 3.6     | 3.0 to 3.6     | V     |

| VCC33A              | +3.3 V power supply                           |                               | 2.97 to 3.63   | 2.97 to 3.63   | V     |

| VCC33PMP            | +3.3 V power supply                           | -                             |                | 2.97 to 3.63   | V     |

| VAREF               | Voltage reference for ADC                     |                               | 2.527 to 2.593 | 2.527 to 2.593 | V     |

| VCC15A <sup>5</sup> | Digital power supply for the analog system    |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VCCNVM              | Embedded flash power supply                   |                               | 1.425 to 1.575 | 1.425 to 1.575 | V     |

| VCCOSC              | Oscillator power supply                       |                               | 2.97 to 3.63   | 2.97 to 3.63   | V     |

| AV, AC <sup>6</sup> | Unpowered, ADC reset asserted of              | -10.5 to 12.0                 | -10.5 to 11.6  | V              |       |

|                     | Analog input (+16 V to +2 V presca            | -0.3 to 12.0                  | –0.3 to 11.6   | V              |       |

|                     | Analog input (+1 V to + 0.125 V pre           | -0.3 to 3.6                   | -0.3 to 3.6    | V              |       |

|                     | Analog input (–16 V to –2 V presca            | -10.5 to 0.3                  | -10.5 to 0.3   | V              |       |

|                     | Analog input (-1 V to -0.125 V pre            | -3.6 to 0.3                   | -3.6 to 0.3    | V              |       |

|                     | Analog input (direct input to ADC)            | -0.3 to 3.6                   | -0.3 to 3.6    | V              |       |

|                     | Digital input                                 |                               | -0.3 to 12.0   | –0.3 to 11.6   | V     |

| AG <sup>6</sup>     | Unpowered, ADC reset asserted of              | r unconfigured                | -10.5 to 12.0  | -10.5 to 11.6  | V     |

|                     | Low Current Mode (1 µA, 3 µA, 10              | -0.3 to 12.0                  | –0.3 to 11.6   | V              |       |

|                     | Low Current Mode (-1 µA, -3 µA, -             | -10.5 to 0.3                  | –10.5 to 0.3   | V              |       |

|                     | High Current Mode <sup>7</sup>                |                               | -10.5 to 12.0  | -10.5 to 11.6  | V     |

|                     | Unpowered, ADC reset asserted or unconfigured |                               | –0.3 to 15.5   | -0.3 to 14.5   | V     |

|                     | Analog input (+16 V, +4 V prescale            | –0.3 to 15.5                  | -0.3 to 14.5   | V              |       |

|                     | Analog input (direct input to ADC)            | -0.3 to 3.6                   | -0.3 to 3.6    | V              |       |

|                     | Digital input                                 |                               | -0.3 to 15.5   | -0.3 to 14.5   | V     |

#### Table 3-2 • Recommended Operating Conditions<sup>1</sup>

Notes:

1. The ranges given here are for power supplies only. The recommended input voltage ranges specific to each I/O standard are given in Table 2-85 on page 2-157.

- 2. All parameters representing voltages are measured with respect to GND unless otherwise specified.

- 3. The programming temperature range supported is  $T_{ambient} = 0^{\circ}C$  to 85°C.

- 4. VPUMP can be left floating during normal operation (not programming mode).

- 5. Violating the V<sub>CC15A</sub> recommended voltage supply during an embedded flash program cycle can corrupt the page being programmed.

6. The input voltage may overshoot by up to 500 mV above the Recommended Maximum (150 mV in Direct mode), provided the duration of the overshoot is less than 50% of the operating lifetime of the device.

7. The AG pad should also conform to the limits as specified in Table 2-48 on page 2-114.

Figure 3-1 • I/O State as a Function of VCCI and VCC Voltage Levels

# **Thermal Characteristics**

### Introduction

The temperature variable in the Microsemi Designer software refers to the junction temperature, not the ambient, case, or board temperatures. This is an important distinction because dynamic and static power consumption will cause the chip's junction temperature to be higher than the ambient, case, or board temperatures. EQ 1 through EQ 3 give the relationship between thermal resistance, temperature gradient, and power.

$$\theta_{\mathsf{J}\mathsf{A}} = \frac{\mathsf{T}_{\mathsf{J}} - \theta_{\mathsf{A}}}{\mathsf{P}}$$

EQ 1

$$\theta_{\mathsf{JB}} = \frac{\mathsf{T}_{\mathsf{J}} - \mathsf{T}_{\mathsf{B}}}{\mathsf{P}}$$

EQ 2

EQ 3

$$\theta_{JC} = \frac{T_J - T_C}{P}$$

where

- $\theta_{JA}$  = Junction-to-air thermal resistance

- $\theta_{JB}$  = Junction-to-board thermal resistance

- $\theta_{JC}$  = Junction-to-case thermal resistance

- T<sub>J</sub> = Junction temperature

- T<sub>A</sub> = Ambient temperature

- T<sub>B</sub> = Board temperature (measured 1.0 mm away from the package edge)

T<sub>C</sub> = Case temperature

P = Total power dissipated by the device

#### Table 3-6 • Package Thermal Resistance

| ΑL <sup>θ</sup> |           |         |         |      |               |       |

|-----------------|-----------|---------|---------|------|---------------|-------|

| Product         | Still Air | 1.0 m/s | 2.5 m/s | θJC  | $\theta_{JB}$ | Units |

| AFS090-QN108    | 34.5      | 30.0    | 27.7    | 8.1  | 16.7          | °C/W  |

| AFS090-QN180    | 33.3      | 27.6    | 25.7    | 9.2  | 21.2          | °C/W  |

| AFS250-QN180    | 32.2      | 26.5    | 24.7    | 5.7  | 15.0          | °C/W  |

| AFS250-PQ208    | 42.1      | 38.4    | 37      | 20.5 | 36.3          | °C/W  |

| AFS600-PQ208    | 23.9      | 21.3    | 20.48   | 6.1  | 16.5          | °C/W  |

| AFS090-FG256    | 37.7      | 33.9    | 32.2    | 11.5 | 29.7          | °C/W  |

| AFS250-FG256    | 33.7      | 30.0    | 28.3    | 9.3  | 24.8          | °C/W  |

| AFS600-FG256    | 28.9      | 25.2    | 23.5    | 6.8  | 19.9          | °C/W  |

| AFS1500-FG256   | 23.3      | 19.6    | 18.0    | 4.3  | 14.2          | °C/W  |

| AFS600-FG484    | 21.8      | 18.2    | 16.7    | 7.7  | 16.8          | °C/W  |

| AFS1500-FG484   | 21.6      | 16.8    | 15.2    | 5.6  | 14.9          | °C/W  |

| AFS1500-FG676   | TBD       | TBD     | TBD     | TBD  | TBD           | °C/W  |

| FG256      |                 |                 |                 |                  |

|------------|-----------------|-----------------|-----------------|------------------|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |

| H3         | XTAL2           | XTAL2           | XTAL2           | XTAL2            |

| H4         | XTAL1           | XTAL1           | XTAL1           | XTAL1            |

| H5         | GNDOSC          | GNDOSC          | GNDOSC          | GNDOSC           |

| H6         | VCCOSC          | VCCOSC          | VCCOSC          | VCCOSC           |

| H7         | VCC             | VCC             | VCC             | VCC              |

| H8         | GND             | GND             | GND             | GND              |

| H9         | VCC             | VCC             | VCC             | VCC              |

| H10        | GND             | GND             | GND             | GND              |

| H11        | GDC0/IO38NDB1V0 | IO51NDB1V0      | IO47NDB2V0      | IO69NDB2V0       |

| H12        | GDC1/IO38PDB1V0 | IO51PDB1V0      | IO47PDB2V0      | IO69PDB2V0       |

| H13        | GDB1/IO39PDB1V0 | GCA1/IO49PDB1V0 | GCA1/IO45PDB2V0 | GCA1/IO64PDB2V0  |

| H14        | GDB0/IO39NDB1V0 | GCA0/IO49NDB1V0 | GCA0/IO45NDB2V0 | GCA0/IO64NDB2V0  |

| H15        | GCA0/IO36NDB1V0 | GCB0/IO48NDB1V0 | GCB0/IO44NDB2V0 | GCB0/IO63NDB2V0  |

| H16        | GCA1/IO36PDB1V0 | GCB1/IO48PDB1V0 | GCB1/IO44PDB2V0 | GCB1/IO63PDB2V0  |

| J1         | GEA0/IO44NDB3V0 | GFA0/IO66NDB3V0 | GFA0/IO70NDB4V0 | GFA0/IO105NDB4V0 |

| J2         | GEA1/IO44PDB3V0 | GFA1/IO66PDB3V0 | GFA1/IO70PDB4V0 | GFA1/IO105PDB4V0 |

| J3         | IO43NDB3V0      | GFB0/IO67NDB3V0 | GFB0/IO71NDB4V0 | GFB0/IO106NDB4V0 |

| J4         | GEC2/IO43PDB3V0 | GFB1/IO67PDB3V0 | GFB1/IO71PDB4V0 | GFB1/IO106PDB4V0 |

| J5         | NC              | GFC0/IO68NDB3V0 | GFC0/IO72NDB4V0 | GFC0/IO107NDB4V0 |

| J6         | NC              | GFC1/IO68PDB3V0 | GFC1/IO72PDB4V0 | GFC1/IO107PDB4V0 |

| J7         | GND             | GND             | GND             | GND              |

| J8         | VCC             | VCC             | VCC             | VCC              |

| J9         | GND             | GND             | GND             | GND              |

| J10        | VCC             | VCC             | VCC             | VCC              |

| J11        | GDC2/IO41NPB1V0 | IO56NPB1V0      | IO56NPB2V0      | IO83NPB2V0       |

| J12        | NC              | GDB0/IO53NPB1V0 | GDB0/IO53NPB2V0 | GDB0/IO80NPB2V0  |

| J13        | NC              | GDA1/IO54PDB1V0 | GDA1/IO54PDB2V0 | GDA1/IO81PDB2V0  |

| J14        | GDA0/IO40PDB1V0 | GDC1/IO52PPB1V0 | GDC1/IO52PPB2V0 | GDC1/IO79PPB2V0  |

| J15        | NC              | IO50NPB1V0      | IO51NSB2V0      | IO77NSB2V0       |

| J16        | GDA2/IO40NDB1V0 | GDC0/IO52NPB1V0 | GDC0/IO52NPB2V0 | GDC0/IO79NPB2V0  |

| K1         | NC              | IO65NPB3V0      | IO67NPB4V0      | IO92NPB4V0       |

| K2         | VCCIB3          | VCCIB3          | VCCIB4          | VCCIB4           |

| K3         | NC              | IO65PPB3V0      | IO67PPB4V0      | IO92PPB4V0       |

| K4         | NC              | IO64PDB3V0      | IO65PDB4V0      | IO96PDB4V0       |

| K5         | GND             | GND             | GND             | GND              |

| K6         | NC              | IO64NDB3V0      | IO65NDB4V0      | IO96NDB4V0       |

| K7         | VCC             | VCC             | VCC             | VCC              |

| K8         | GND             | GND             | GND             | GND              |