Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                             |

|--------------------------------|-----------------------------------------------------------------------------|

| Product Status                 | Active                                                                      |

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | -                                                                           |

| Total RAM Bits                 | 276480                                                                      |

| Number of I/O                  | 119                                                                         |

| Number of Gates                | 1500000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 256-LBGA                                                                    |

| Supplier Device Package        | 256-FPBGA (17x17)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1afs1500-fgg256i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Array Coordinates**

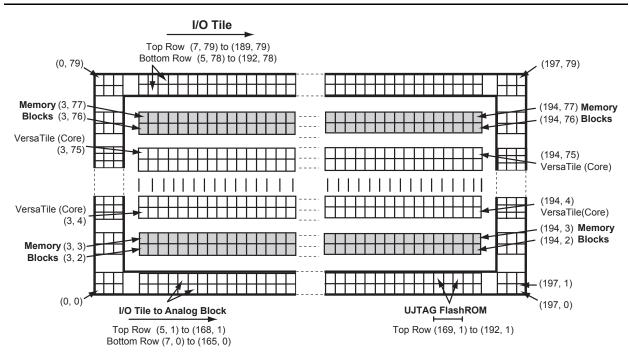

During many place-and-route operations in the Microsemi Designer software tool, it is possible to set constraints that require array coordinates. Table 2-3 is provided as a reference. The array coordinates are measured from the lower left (0, 0). They can be used in region constraints for specific logic groups/blocks, designated by a wildcard, and can contain core cells, memories, and I/Os.

Table 2-3 provides array coordinates of core cells and memory blocks.

I/O and cell coordinates are used for placement constraints. Two coordinate systems are needed because there is not a one-to-one correspondence between I/O cells and edge core cells. In addition, the I/O coordinate system changes depending on the die/package combination. It is not listed in Table 2-3. The Designer ChipPlanner tool provides array coordinates of all I/O locations. I/O and cell coordinates are used for placement constraints. However, I/O placement is easier by package pin assignment.

Figure 2-7 illustrates the array coordinates of an AFS600 device. For more information on how to use array coordinates for region/placement constraints, see the *Designer User's Guide* or online help (available in the software) for Fusion software tools.

Table 2-3 • Array Coordinates

|         |   | Vers | saTiles |     | Memor  | y Rows   | All    |            |  |

|---------|---|------|---------|-----|--------|----------|--------|------------|--|

| Device  | М | in.  | M       | ax. | Bottom | Тор      | Min.   | Max.       |  |

|         | х | у    | х       | у   | (x, y) | (x, y)   | (x, y) | (x, y)     |  |

| AFS090  | 3 | 2    | 98      | 25  | None   | (3, 26)  | (0, 0) | (101, 29)  |  |

| AFS250  | 3 | 2    | 130     | 49  | None   | (3, 50)  | (0, 0) | (133, 53)  |  |

| AFS600  | 3 | 4    | 194     | 75  | (3, 2) | (3, 76)  | (0, 0) | (197, 79)  |  |

| AFS1500 | 3 | 4    | 322     | 123 | (3, 2) | (3, 124) | (0, 0) | (325, 129) |  |

Note: The vertical I/O tile coordinates are not shown. West side coordinates are {(0, 2) to (2, 2)} to {(0, 77) to (2, 77)}; east side coordinates are {(195, 2) to (197, 2)} to {(195, 77) to (197, 77)}.

Figure 2-7 • Array Coordinates for AFS600

2-7 Revision 6

## Global Resource Characteristics

### AFS600 VersaNet Topology

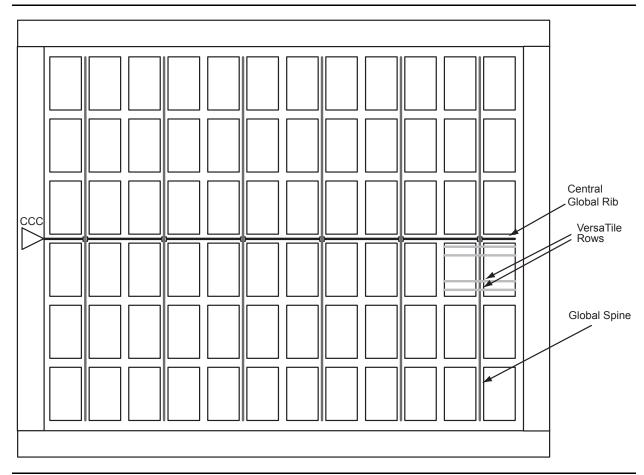

Clock delays are device-specific. Figure 2-15 is an example of a global tree used for clock routing. The global tree presented in Figure 2-15 is driven by a CCC located on the west side of the AFS600 device. It is used to drive all D-flip-flops in the device.

Figure 2-15 • Example of Global Tree Use in an AFS600 Device for Clock Routing

2-15 Revision 6

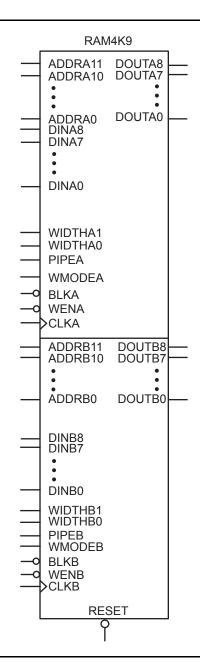

## **RAM4K9 Description**

Figure 2-48 • RAM4K9

2-57 Revision 6

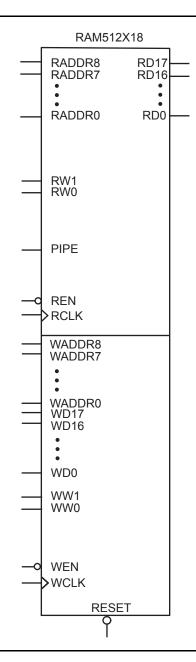

## RAM512X18 Description

Figure 2-49 • RAM512X18

The following signals are used to configure the FIFO4K18 memory element.

#### WW and RW

These signals enable the FIFO to be configured in one of the five allowable aspect ratios (Table 2-33).

Table 2-33 • Aspect Ratio Settings for WW[2:0]

| WW2, WW1, WW0 | RW2, RW1, RW0 | D×W      |

|---------------|---------------|----------|

| 000           | 000           | 4k×1     |

| 001           | 001           | 2k×2     |

| 010           | 010           | 1k×4     |

| 011           | 011           | 512×9    |

| 100           | 100           | 256×18   |

| 101, 110, 111 | 101, 110, 111 | Reserved |

#### WBLK and RBLK

These signals are active low and will enable the respective ports when Low. When the RBLK signal is High, the corresponding port's outputs hold the previous value.

#### **WEN and REN**

Read and write enables. WEN is active low and REN is active high by default. These signals can be configured as active high or low.

#### WCLK and RCLK

These are the clock signals for the synchronous read and write operations. These can be driven independently or with the same driver.

#### **RPIPE**

This signal is used to specify pipelined read on the output. A Low on RPIPE indicates a nonpipelined read, and the data appears on the output in the same clock cycle. A High indicates a pipelined read, and data appears on the output in the next clock cycle.

#### RESET

This active low signal resets the output to zero when asserted. It resets the FIFO counters. It also sets all the RD pins Low, the FULL and AFULL pins Low, and the EMPTY and AEMPTY pins High (Table 2-34).

Table 2-34 • Input Data Signal Usage for Different Aspect Ratios

| D×W    | WD/RD Unused       |

|--------|--------------------|

| 4k×1   | WD[17:1], RD[17:1] |

| 2k×2   | WD[17:2], RD[17:2] |

| 1k×4   | WD[17:4], RD[17:4] |

| 512×9  | WD[17:9], RD[17:9] |

| 256×18 | -                  |

#### WD

This is the input data bus and is 18 bits wide. Not all 18 bits are valid in all configurations. When a data width less than 18 is specified, unused higher-order signals must be grounded (Table 2-34).

#### RD

This is the output data bus and is 18 bits wide. Not all 18 bits are valid in all configurations. Like the WD bus, high-order bits become unusable if the data width is less than 18. The output data on unused pins is undefined (Table 2-34).

2-69 Revision 6

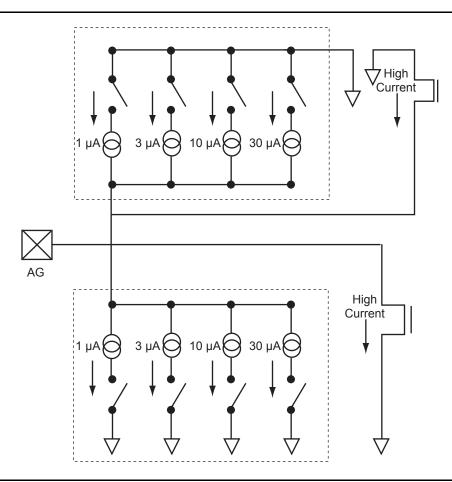

The rate at which the gate voltage of the external MOSFET slews is determined by the current,  $I_g$ , sourced or sunk by the AG pin and the gate-to-source capacitance,  $C_{GS}$ , of the external MOSFET. As an approximation, the slew rate is given by EQ 6.

$$dv/dt = I_g / C_{GS}$$

EQ6

$C_{GS}$  is not a fixed capacitance but, depending on the circuitry connected to its drain terminal, can vary significantly during the course of a turn-on or turn-off transient. Thus, EQ 6 on page 2-91 can only be used for a first-order estimate of the switching speed of the external MOSFET.

Figure 2-75 • Gate Driver Example

2-91 Revision 6

The diode's voltage is measured at each current level and the temperature is calculated based on EQ 7.

$$V_{\text{TMSLO}} - V_{\text{TMSHI}} = n \frac{kT}{q} \left( \ln \frac{I_{\text{TMSLO}}}{I_{\text{TMSHI}}} \right)$$

EQ7

where

$I_{TMSLO}$  is the current when the Temperature Strobe is Low, typically 100  $\mu A$

$I_{TMSHI}$  is the current when the Temperature Strobe is High, typically 10  $\mu$ A

V<sub>TMSLO</sub> is diode voltage while Temperature Strobe is Low

*V*<sub>TMSHI</sub> is diode voltage while Temperature Strobe is High

*n* is the non-ideality factor of the diode-connected transistor. It is typically 1.004 for the Microsemi-recommended transistor type 2N3904.

$K = 1.3806 \times 10^{-23} \text{ J/K}$  is the Boltzman constant

$Q = 1.602 \times 10^{-19} C$  is the charge of a proton

When  $I_{TMSLO} / I_{TMSHI} = 10$ , the equation can be simplified as shown in EQ 8.

$$\Delta V = V_{\text{TMSLO}} - V_{\text{TMSHI}} = 1.986 \times 10^{-4} nT$$

EQ8

In the Fusion TMB, the ideality factor n for 2N3904 is 1.004 and  $\Delta V$  is amplified 12.5 times by an internal amplifier; hence the voltage before entering the ADC is as given in EQ 9.

$$V_{ADC} = \Delta V \times 12.5 = 2.5 \text{ mV}/(K \times T)$$

EQ9

This means the temperature to voltage relationship is 2.5 mV per degree Kelvin. The unique design of Fusion has made the Temperature Monitor System simple for the user. When the 10-bit mode ADC is used, each LSB represents 1 degree Kelvin, as shown in EQ 10. That is, e. 25°C is equal to 293°K and is represented by decimal 293 counts from the ADC.

$$1K = 2.5 \text{ mV} \times \frac{2^{10}}{2.56 \text{ V}} = 1 \text{ LSB}$$

EQ 10

If 8-bit mode is used for the ADC resolution, each LSB represents 4 degrees Kelvin; however, the resolution remains as 1 degree Kelvin per LSB, even for 12-bit mode, due to the Temperature Monitor design. An example of the temperature data format for 10-bit mode is shown in Table 2-38.

Table 2-38 • Temperature Data Format

| Temperature | Temperature (K) | Digital Output (ADC 10-bit mode) |

|-------------|-----------------|----------------------------------|

| –40°C       | 233             | 00 1110 1001                     |

| –20°C       | 253             | 00 1111 1101                     |

| 0°C         | 273             | 01 0001 0001                     |

| 1°C         | 274             | 01 0001 0010                     |

| 10 °C       | 283             | 01 0001 1011                     |

| 25°C        | 298             | 01 0010 1010                     |

| 50 °C       | 323             | 01 0100 0011                     |

| 85 °C       | 358             | 01 0110 0110                     |

|             |                 |                                  |

EQ 16 through EQ 18 can be used to calculate the acquisition time required for a given input. The STC signal gives the number of sample periods in ADCCLK for the acquisition time of the desired signal. If the actual acquisition time is higher than the STC value, the settling time error can affect the accuracy of the ADC, because the sampling capacitor is only partially charged within the given sampling cycle. Example acquisition times are given in Table 2-44 and Table 2-45. When controlling the sample time for the ADC along with the use of the active bipolar prescaler, current monitor, or temperature monitor, the minimum sample time(s) for each must be obeyed. EQ 19 can be used to determine the appropriate value of STC.

$$VOUT = VIN(1 - e^{-t/RC})$$

EQ 16

For 0.5 LSB gain error, VOUT should be replaced with (VIN –(0.5 × LSB Value)):

You can calculate the minimum actual acquisition time by using EQ 16:

$$(VIN - 0.5 \times LSB \ Value) = VIN(1 - e^{-t/RC})$$

EQ 17

where VIN is the ADC reference voltage (VREF)

Solving EQ 17:

$$t = RC \times In (VIN / (0.5 \times LSB \ Value))$$

EQ 18

where  $R = Z_{INAD} + R_{SOURCE}$  and  $C = C_{INAD}$ .

Calculate the value of STC by using EQ 19.

$$t_{SAMPLE}$$

= (2 + STC) x (1 / ADCCLK) or  $t_{SAMPLE}$  = (2 + STC) x (ADC Clock Period)

EQ 19

where ADCCLK = ADC clock frequency in MHz.

$t_{SAMPLE}$  = 0.449 µs from bit resolution in Table 2-44.

ADC Clock frequency = 10 MHz or a 100 ns period.

STC =  $(t_{SAMPLE} / (1 / 10 \text{ MHz})) - 2 = 4.49 - 2 = 2.49.$

You must round up to 3 to accommodate the minimum sample time.

Table 2-44 • Acquisition Time Example with VAREF = 2.56 V

|                                                                  | $VIN = 2.56V, R = 4K (R_{SOURCE} \sim 0), C = 18 pF$ |       |  |  |  |  |

|------------------------------------------------------------------|------------------------------------------------------|-------|--|--|--|--|

| Resolution LSB Value (mV) Min. Sample/Hold Time for 0.5 LSB (µs) |                                                      |       |  |  |  |  |

| 8                                                                | 10                                                   | 0.449 |  |  |  |  |

| 10                                                               | 2.5                                                  | 0.549 |  |  |  |  |

| 12                                                               | 0.625                                                | 0.649 |  |  |  |  |

Table 2-45 • Acquisition Time Example with VAREF = 3.3 V

| VIN = 3.3V, R = 4K (R <sub>SOURCE</sub> ~ 0), C = 18 pF          |        |       |  |  |  |

|------------------------------------------------------------------|--------|-------|--|--|--|

| Resolution LSB Value (mV) Min. Sample/Hold time for 0.5 LSB (μs) |        |       |  |  |  |

| 8                                                                | 12.891 | 0.449 |  |  |  |

| 10                                                               | 3.223  | 0.549 |  |  |  |

| 12                                                               | 0.806  | 0.649 |  |  |  |

#### Sample Phase

A conversion is performed in three phases. In the first phase, the analog input voltage is sampled on the input capacitor. This phase is called sample phase. During the sample phase, the output signals BUSY and SAMPLE change from '0' to '1', indicating the ADC is busy and sampling the analog signal. The sample time can be controlled by input signals STC[7:0]. The sample time can be calculated by EQ 20. When controlling the sample time for the ADC along with the use of Prescaler or Current Monitor or Temperature Monitor, the minimum sample time for each must be obeyed.

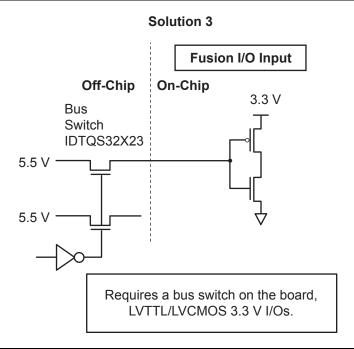

### Solution 3

The board-level design must ensure that the reflected waveform at the pad does not exceed limits provided in Table 3-4 on page 3-4. This is a long-term reliability requirement.

This scheme will also work for a 3.3 V PCI/PCIX configuration, but the internal diode should not be used for clamping, and the voltage must be limited by the bus switch, as shown in Figure 2-105. Relying on the diode clamping would create an excessive pad DC voltage of 3.3 V + 0.7 V = 4 V.

Figure 2-105 • Solution 3

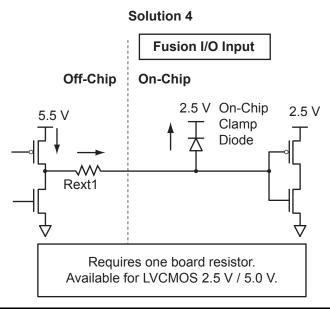

### Solution 4

Figure 2-106 • Solution 4

## **5 V Output Tolerance**

Fusion I/Os must be set to 3.3 V LVTTL or 3.3 V LVCMOS mode to reliably drive 5 V TTL receivers. It is also critical that there be NO external I/O pull-up resistor to 5 V, since this resistor would pull the I/O pad voltage beyond the 3.6 V absolute maximum value and consequently cause damage to the I/O.

When set to 3.3 V LVTTL or 3.3 V LVCMOS mode, Fusion I/Os can directly drive signals into 5 V TTL receivers. In fact, VOL = 0.4 V and VOH = 2.4 V in both 3.3 V LVTTL and 3.3 V LVCMOS modes exceed the VIL = 0.8 V and VIH = 2 V level requirements of 5 V TTL receivers. Therefore, level '1' and level '0' will be recognized correctly by 5 V TTL receivers.

## Simultaneously Switching Outputs and PCB Layout

- Simultaneously switching outputs (SSOs) can produce signal integrity problems on adjacent signals that are not part of the SSO bus. Both inductive and capacitive coupling parasitics of bond wires inside packages and of traces on PCBs will transfer noise from SSO busses onto signals adjacent to those busses. Additionally, SSOs can produce ground bounce noise and VCCI dip noise. These two noise types are caused by rapidly changing currents through GND and VCCI package pin inductances during switching activities:

- Ground bounce noise voltage = L(GND) \* di/dt

- VCCI dip noise voltage = L(VCCI) \* di/dt

Any group of four or more input pins switching on the same clock edge is considered an SSO bus. The shielding should be done both on the board and inside the package unless otherwise described.

In-package shielding can be achieved in several ways; the required shielding will vary depending on whether pins next to SSO bus are LVTTL/LVCMOS inputs, LVTTL/LVCMOS outputs, or GTL/SSTL/HSTL/LVDS/LVPECL inputs and outputs. Board traces in the vicinity of the SSO bus have to be adequately shielded from mutual coupling and inductive noise that can be generated by the SSO bus. Also, noise generated by the SSO bus needs to be reduced inside the package.

PCBs perform an important function in feeding stable supply voltages to the IC and, at the same time, maintaining signal integrity between devices.

Key issues that need to considered are as follows:

- Power and ground plane design and decoupling network design

- · Transmission line reflections and terminations

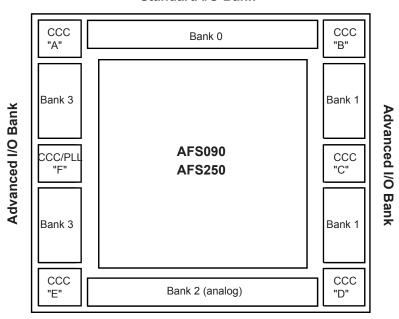

## **User I/O Naming Convention**

Due to the comprehensive and flexible nature of Fusion device user I/Os, a naming scheme is used to show the details of the I/O (Figure 2-113 on page 2-158 and Figure 2-114 on page 2-159). The name identifies to which I/O bank it belongs, as well as the pairing and pin polarity for differential I/Os.

I/O Nomenclature = Gmn/IOuxwByVz

Gmn is only used for I/Os that also have CCC access—i.e., global pins.

- G = Global

- m = Global pin location associated with each CCC on the device: A (northwest corner), B (northeast corner), C (east middle), D (southeast corner), E (southwest corner), and F (west middle).

- n = Global input MUX and pin number of the associated Global location m, either A0, A1, A2, B0, B1, B2, C0, C1, or C2. Figure 2-22 on page 2-25 shows the three input pins per clock source MUX at CCC location m.

- u = I/O pair number in the bank, starting at 00 from the northwest I/O bank and proceeding in a clockwise direction.

- x = P (Positive) or N (Negative) for differential pairs, or R (Regular single-ended) for the I/Os that support single-ended and voltage-referenced I/O standards only. U (Positive-LVDS only) or V (Negative-LVDS only) restrict the I/O differential pair from being selected as an LVPECL pair.

- w = D (Differential Pair), P (Pair), or S (Single-Ended). D (Differential Pair) if both members of the pair are bonded out to adjacent pins or are separated only by one GND or NC pin; P (Pair) if both members of the pair are bonded out but do not meet the adjacency requirement; or S (Single-Ended) if the I/O pair is not bonded out. For Differential (D) pairs, adjacency for ball grid packages means only vertical or horizontal. Diagonal adjacency does not meet the requirements for a true differential pair.

- B = Bank

- y = Bank number (0-3). The Bank number starts at 0 from the northwest I/O bank and proceeds in a clockwise direction.

- V = Reference voltage

- z = Minibank number

#### Standard I/O Bank

**Analog Quads**

Figure 2-113 • Naming Conventions of Fusion Devices with Three Digital I/O Banks

## Table 2-105 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Pro I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOU</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.66              | 7.88            | 0.04             | 1.20            | 1.57             | 0.43             | 8.03            | 6.70            | 2.69            | 2.59            | 10.26            | 8.94             | ns    |

|                   | -1             | 0.56              | 6.71            | 0.04             | 1.02            | 1.33             | 0.36             | 6.83            | 5.70            | 2.29            | 2.20            | 8.73             | 7.60             | ns    |

|                   | -2             | 0.49              | 5.89            | 0.03             | 0.90            | 1.17             | 0.32             | 6.00            | 5.01            | 2.01            | 1.93            | 7.67             | 6.67             | ns    |

| 8 mA              | Std.           | 0.66              | 5.08            | 0.04             | 1.20            | 1.57             | 0.43             | 5.17            | 4.14            | 3.05            | 3.21            | 7.41             | 6.38             | ns    |

|                   | -1             | 0.56              | 4.32            | 0.04             | 1.02            | 1.33             | 0.36             | 4.40            | 3.52            | 2.59            | 2.73            | 6.30             | 5.43             | ns    |

|                   | -2             | 0.49              | 3.79            | 0.03             | 0.90            | 1.17             | 0.32             | 3.86            | 3.09            | 2.28            | 2.40            | 5.53             | 4.76             | ns    |

| 12 mA             | Std.           | 0.66              | 3.67            | 0.04             | 1.20            | 1.57             | 0.43             | 3.74            | 2.87            | 3.28            | 3.61            | 5.97             | 5.11             | ns    |

|                   | -1             | 0.56              | 3.12            | 0.04             | 1.02            | 1.33             | 0.36             | 3.18            | 2.44            | 2.79            | 3.07            | 5.08             | 4.34             | ns    |

|                   | -2             | 0.49              | 2.74            | 0.03             | 0.90            | 1.17             | 0.32             | 2.79            | 2.14            | 2.45            | 2.70            | 4.46             | 3.81             | ns    |

| 16 mA             | Std.           | 0.66              | 3.46            | 0.04             | 1.20            | 1.57             | 0.43             | 3.53            | 2.61            | 3.33            | 3.72            | 5.76             | 4.84             | ns    |

|                   | -1             | 0.56              | 2.95            | 0.04             | 1.02            | 1.33             | 0.36             | 3.00            | 2.22            | 2.83            | 3.17            | 4.90             | 4.12             | ns    |

|                   | -2             | 0.49              | 2.59            | 0.03             | 0.90            | 1.17             | 0.32             | 2.63            | 1.95            | 2.49            | 2.78            | 4.30             | 3.62             | ns    |

| 24 mA             | Std.           | 0.66              | 3.21            | 0.04             | 1.20            | 1.57             | 0.43             | 3.27            | 2.16            | 3.39            | 4.13            | 5.50             | 4.39             | ns    |

|                   | -1             | 0.56              | 2.73            | 0.04             | 1.02            | 1.33             | 0.36             | 2.78            | 1.83            | 2.88            | 3.51            | 4.68             | 3.74             | ns    |

|                   | -2             | 0.49              | 2.39            | 0.03             | 0.90            | 1.17             | 0.32             | 2.44            | 1.61            | 2.53            | 3.08            | 4.11             | 3.28             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

2-177 Revision 6

Table 2-169 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) |

|---------------|----------------|----------------------|-----------------|

| 1.075         | 1.325          | Cross point          | _               |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### **Timing Characteristics**

Table 2-170 • LVDS

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Pro I/Os

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.66              | 2.10            | 0.04             | 1.82            | ns    |

| <b>-1</b>   | 0.56              | 1.79            | 0.04             | 1.55            | ns    |

| -2          | 0.49              | 1.57            | 0.03             | 1.36            | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

#### **BLVDS/M-LVDS**

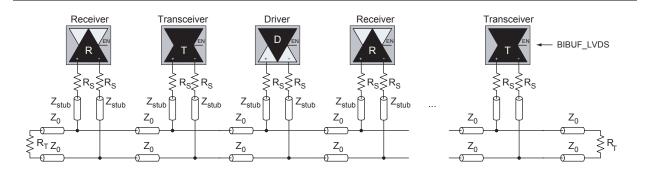

Bus LVDS (BLVDS) and Multipoint LVDS (M-LVDS) specifications extend the existing LVDS standard to high-performance multipoint bus applications. Multidrop and multipoint bus configurations can contain any combination of drivers, receivers, and transceivers. Microsemi LVDS drivers provide the higher drive current required by BLVDS and M-LVDS to accommodate the loading. The driver requires series terminations for better signal quality and to control voltage swing. Termination is also required at both ends of the bus, since the driver can be located anywhere on the bus. These configurations can be implemented using TRIBUF\_LVDS and BIBUF\_LVDS macros along with appropriate terminations. Multipoint designs using Microsemi LVDS macros can achieve up to 200 MHz with a maximum of 20 loads. A sample application is given in Figure 2-135. The input and output buffer delays are available in the LVDS section in Table 2-171.

Example: For a bus consisting of 20 equidistant loads, the following terminations provide the required differential voltage, in worst-case industrial operating conditions at the farthest receiver:  $R_S$  = 60  $\Omega$  and  $R_T$  = 70  $\Omega$ , given  $Z_0$  = 50  $\Omega$  (2") and  $Z_{stub}$  = 50  $\Omega$  (~1.5").

Figure 2-135 • BLVDS/M-LVDS Multipoint Application Using LVDS I/O Buffers

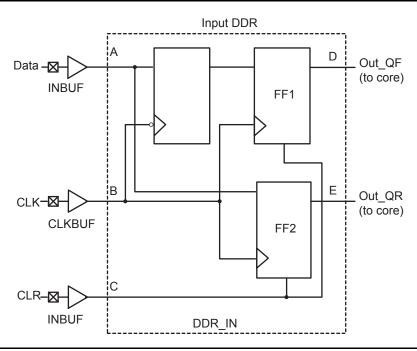

## **DDR Module Specifications**

Input DDR Module

Figure 2-142 • Input DDR Timing Model

### Table 2-179 • Parameter Definitions

| Parameter Name          | Parameter Definition         | Measuring Nodes (from, to) |

|-------------------------|------------------------------|----------------------------|

| t <sub>DDRICLKQ1</sub>  | Clock-to-Out Out_QR          | B, D                       |

| t <sub>DDRICLKQ2</sub>  | Clock-to-Out Out_QF          | B, E                       |

| t <sub>DDRISUD</sub>    | Data Setup Time of DDR Input | A, B                       |

| t <sub>DDRIHD</sub>     | Data Hold Time of DDR Input  | A, B                       |

| t <sub>DDRICLR2Q1</sub> | Clear-to-Out Out_QR          | C, D                       |

| t <sub>DDRICLR2Q2</sub> | Clear-to-Out Out_QF          | C, E                       |

| t <sub>DDRIREMCLR</sub> | Clear Removal                | C, B                       |

| t <sub>DDRIRECCLR</sub> | Clear Recovery               | C, B                       |

2-219 Revision 6

#### IEEE 1532 Characteristics

JTAG timing delays do not include JTAG I/Os. To obtain complete JTAG timing, add I/O buffer delays to the corresponding standard selected; refer to the I/O timing characteristics in the "User I/Os" section on page 2-132 for more details.

### **Timing Characteristics**

Table 2-186 • JTAG 1532

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                 | -2    | -1    | Std.  | Units |

|----------------------|-----------------------------|-------|-------|-------|-------|

| t <sub>DISU</sub>    | Test Data Input Setup Time  | 0.50  | 0.57  | 0.67  | ns    |

| t <sub>DIHD</sub>    | Test Data Input Hold Time   | 1.00  | 1.13  | 1.33  | ns    |

| t <sub>TMSSU</sub>   | Test Mode Select Setup Time | 0.50  | 0.57  | 0.67  | ns    |

| t <sub>TMDHD</sub>   | Test Mode Select Hold Time  | 1.00  | 1.13  | 1.33  | ns    |

| t <sub>TCK2Q</sub>   | Clock to Q (data out)       | 6.00  | 6.80  | 8.00  | ns    |

| t <sub>RSTB2Q</sub>  | Reset to Q (data out)       | 20.00 | 22.67 | 26.67 | ns    |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency       | 25.00 | 22.00 | 19.00 | MHz   |

| t <sub>TRSTREM</sub> | ResetB Removal Time         | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>TRSTREC</sub> | ResetB Recovery Time        | 0.20  | 0.23  | 0.27  | ns    |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse        | TBD   | TBD   | TBD   | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

2-231 Revision 6

Table 3-9 • AFS600 Quiescent Supply Current Characteristics

| Parameter          | Description                   | Conditions                                                                       | Temp.                  | Min | Тур  | Max | Unit |

|--------------------|-------------------------------|----------------------------------------------------------------------------------|------------------------|-----|------|-----|------|

| ICC <sup>1</sup>   | 1.5 V quiescent current       | Operational standby <sup>4</sup> ,                                               | T <sub>J</sub> = 25°C  |     | 13   | 25  | mA   |

|                    |                               | VCC = 1.575 V                                                                    | T <sub>J</sub> = 85°C  |     | 20   | 45  | mA   |

|                    |                               |                                                                                  | T <sub>J</sub> =100°C  |     | 25   | 75  | mA   |

|                    |                               | Standby mode <sup>5</sup> or Sleep mode <sup>6</sup> , VCC = 0 V                 |                        |     | 0    | 0   | μA   |

| ICC33 <sup>2</sup> | 3.3 V analog supplies current | Operational standby <sup>4</sup> ,                                               | T <sub>J</sub> = 25°C  |     | 9.8  | 13  | mA   |

|                    |                               | VCC33 = 3.63 V                                                                   | T <sub>J</sub> = 85°C  |     | 10.7 | 14  | mA   |

|                    |                               |                                                                                  | T <sub>J</sub> = 100°C |     | 10.8 | 15  | mA   |

|                    |                               | Operational standby,<br>only Analog Quad and –3.3 V<br>output ON, VCC33 = 3.63 V | $T_J = 25^{\circ}C$    |     | 0.31 | 2   | mA   |

|                    |                               |                                                                                  | $T_J = 85^{\circ}C$    |     | 0.35 | 2   | mA   |

|                    |                               |                                                                                  | T <sub>J</sub> = 100°C |     | 0.45 | 2   | mA   |

|                    |                               | Standby mode <sup>5</sup> ,                                                      | $T_J = 25^{\circ}C$    |     | 2.8  | 3.6 | mA   |

|                    |                               | VCC33 = 3.63 V                                                                   | T <sub>J</sub> = 85°C  |     | 2.9  | 4   | mA   |

|                    |                               |                                                                                  | T <sub>J</sub> = 100°C |     | 3.5  | 6   | mA   |

|                    |                               | Sleep mode <sup>6</sup> , V <sub>CC33</sub> = 3.63 V                             | $T_J = 25^{\circ}C$    |     | 17   | 19  | μΑ   |

|                    |                               |                                                                                  | T <sub>J</sub> = 85°C  |     | 18   | 20  | μΑ   |

|                    |                               |                                                                                  | T <sub>J</sub> = 100°C |     | 24   | 25  | μΑ   |

| ICCI <sup>3</sup>  | I/O quiescent current         | Operational standby <sup>4</sup> ,<br>VCCIx = 3.63 V                             | T <sub>J</sub> = 25°C  |     | 417  | 648 | μΑ   |

|                    |                               |                                                                                  | T <sub>J</sub> = 85°C  |     | 417  | 648 | μΑ   |

|                    |                               |                                                                                  | T <sub>J</sub> = 100°C |     | 417  | 649 | μΑ   |

| IJTAG              | JTAG I/O quiescent current    | Operational standby <sup>4</sup> ,<br>VJTAG = 3.63 V                             | T <sub>J</sub> = 25°C  |     | 80   | 100 | μΑ   |

|                    |                               |                                                                                  | T <sub>J</sub> = 85°C  |     | 80   | 100 | μΑ   |

|                    |                               |                                                                                  | T <sub>J</sub> = 100°C |     | 80   | 100 | μΑ   |

|                    |                               | Standby mode <sup>5</sup> or Sleep<br>mode <sup>6</sup> , VJTAG = 0 V            |                        |     | 0    | 0   | μA   |

#### Notes:

- 1. ICC is the 1.5 V power supplies, ICC and ICC15A.

- 2. ICC33A includes ICC33A, ICC33PMP, and ICCOSC.

- 3. ICCI includes all ICCI0, ICCI1, ICCI2, and ICCI4.

- 4. Operational standby is when the Fusion device is powered up, all blocks are used, no I/O is toggling, Voltage Regulator is loaded with 200 mA, VCC33PMP is ON, XTAL is ON, and ADC is ON.

- 5. XTAL is configured as high gain, VCC = VJTAG = VPUMP = 0 V.

- 6. Sleep Mode, VCC = VJTAG = VPUMP = 0 V.

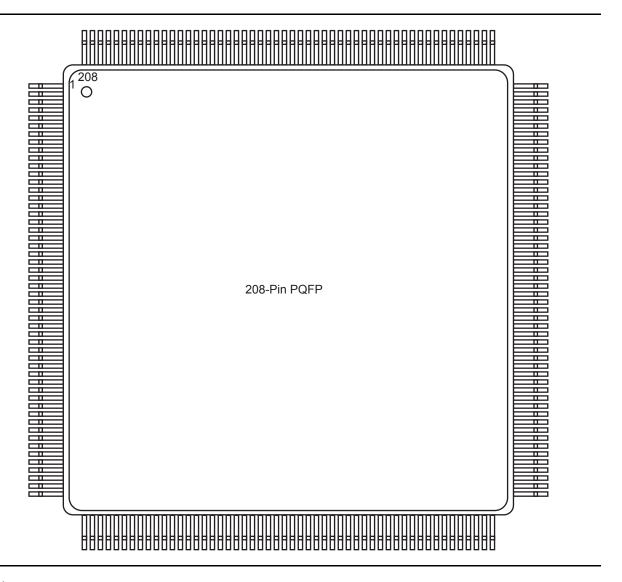

## **PQ208**

## Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/default.aspx.

4-7 Revision 6

|               | PQ208           |                 |  |  |  |

|---------------|-----------------|-----------------|--|--|--|

| Pin<br>Number | AFS250 Function | AFS600 Function |  |  |  |

| 147           | GCC1/IO47PDB1V0 | IO39NDB2V0      |  |  |  |

| 148           | IO42NDB1V0      | GCA2/IO39PDB2V0 |  |  |  |

| 149           | GBC2/IO42PDB1V0 | IO31NDB2V0      |  |  |  |

| 150           | VCCIB1          | GBB2/IO31PDB2V0 |  |  |  |

| 151           | GND             | IO30NDB2V0      |  |  |  |

| 152           | VCC             | GBA2/IO30PDB2V0 |  |  |  |

| 153           | IO41NDB1V0      | VCCIB2          |  |  |  |

| 154           | GBB2/IO41PDB1V0 | GNDQ            |  |  |  |

| 155           | IO40NDB1V0      | VCOMPLB         |  |  |  |

| 156           | GBA2/IO40PDB1V0 | VCCPLB          |  |  |  |

| 157           | GBA1/IO39RSB0V0 | VCCIB1          |  |  |  |

| 158           | GBA0/IO38RSB0V0 | GNDQ            |  |  |  |

| 159           | GBB1/IO37RSB0V0 | GBB1/IO27PPB1V1 |  |  |  |

| 160           | GBB0/IO36RSB0V0 | GBA1/IO28PPB1V1 |  |  |  |

| 161           | GBC1/IO35RSB0V0 | GBB0/IO27NPB1V1 |  |  |  |

| 162           | VCCIB0          | GBA0/IO28NPB1V1 |  |  |  |

| 163           | GND             | VCCIB1          |  |  |  |

| 164           | VCC             | GND             |  |  |  |

| 165           | GBC0/IO34RSB0V0 | VCC             |  |  |  |

| 166           | IO33RSB0V0      | GBC1/IO26PDB1V1 |  |  |  |

| 167           | IO32RSB0V0      | GBC0/IO26NDB1V1 |  |  |  |

| 168           | IO31RSB0V0      | IO24PPB1V1      |  |  |  |

| 169           | IO30RSB0V0      | IO23PPB1V1      |  |  |  |

| 170           | IO29RSB0V0      | IO24NPB1V1      |  |  |  |

| 171           | IO28RSB0V0      | IO23NPB1V1      |  |  |  |

| 172           | IO27RSB0V0      | IO22PPB1V0      |  |  |  |

| 173           | IO26RSB0V0      | IO21PPB1V0      |  |  |  |

| 174           | IO25RSB0V0      | IO22NPB1V0      |  |  |  |

| 175           | VCCIB0          | IO21NPB1V0      |  |  |  |

| 176           | GND             | IO20PSB1V0      |  |  |  |

| 177           | VCC             | IO19PSB1V0      |  |  |  |

| 178           | IO24RSB0V0      | IO14NSB0V1      |  |  |  |

| 179           | IO23RSB0V0      | IO12PDB0V1      |  |  |  |

| 180           | IO22RSB0V0      | IO12NDB0V1      |  |  |  |

| 181           | IO21RSB0V0      | VCCIB0          |  |  |  |

| 182           | IO20RSB0V0      | GND             |  |  |  |

| 183           | IO19RSB0V0      | VCC             |  |  |  |

|               | PQ208           |                 |  |  |

|---------------|-----------------|-----------------|--|--|

| Pin<br>Number | AFS250 Function | AFS600 Function |  |  |

| 184           | IO18RSB0V0      | IO10PPB0V1      |  |  |

| 185           | IO17RSB0V0      | IO09PPB0V1      |  |  |

| 186           | IO16RSB0V0      | IO10NPB0V1      |  |  |

| 187           | IO15RSB0V0      | IO09NPB0V1      |  |  |

| 188           | VCCIB0          | IO08PPB0V1      |  |  |

| 189           | GND             | IO07PPB0V1      |  |  |

| 190           | VCC             | IO08NPB0V1      |  |  |

| 191           | IO14RSB0V0      | IO07NPB0V1      |  |  |

| 192           | IO13RSB0V0      | IO06PPB0V0      |  |  |

| 193           | IO12RSB0V0      | IO05PPB0V0      |  |  |

| 194           | IO11RSB0V0      | IO06NPB0V0      |  |  |

| 195           | IO10RSB0V0      | IO04PPB0V0      |  |  |

| 196           | IO09RSB0V0      | IO05NPB0V0      |  |  |

| 197           | IO08RSB0V0      | IO04NPB0V0      |  |  |

| 198           | IO07RSB0V0      | GAC1/IO03PDB0V0 |  |  |

| 199           | IO06RSB0V0      | GAC0/IO03NDB0V0 |  |  |

| 200           | GAC1/IO05RSB0V0 | VCCIB0          |  |  |

| 201           | VCCIB0          | GND             |  |  |

| 202           | GND             | VCC             |  |  |

| 203           | VCC             | GAB1/IO02PDB0V0 |  |  |

| 204           | GAC0/IO04RSB0V0 | GAB0/IO02NDB0V0 |  |  |

| 205           | GAB1/IO03RSB0V0 | GAA1/IO01PDB0V0 |  |  |

| 206           | GAB0/IO02RSB0V0 | GAA0/IO01NDB0V0 |  |  |

| 207           | GAA1/IO01RSB0V0 | GNDQ            |  |  |

| 208           | GAA0/IO00RSB0V0 | VCCIB0          |  |  |

4-10 Revision 6

Package Pin Assignments

| FG676      |                  |  |  |

|------------|------------------|--|--|

| Pin Number | AFS1500 Function |  |  |

| L17        | VCCIB2           |  |  |

| L18        | GCB2/IO60PDB2V0  |  |  |

| L19        | IO58NDB2V0       |  |  |

| L20        | IO57NDB2V0       |  |  |

| L21        | IO59NDB2V0       |  |  |

| L22        | GCC2/IO61PDB2V0  |  |  |

| L23        | IO55PPB2V0       |  |  |

| L24        | IO56PDB2V0       |  |  |

| L25        | IO55NPB2V0       |  |  |

| L26        | GND              |  |  |

| M1         | NC               |  |  |

| M2         | VCCIB4           |  |  |

| M3         | GFC2/IO108PDB4V0 |  |  |

| M4         | GND              |  |  |

| M5         | IO109NDB4V0      |  |  |

| M6         | IO110NDB4V0      |  |  |

| M7         | GND              |  |  |

| M8         | IO104NDB4V0      |  |  |

| M9         | IO111NDB4V0      |  |  |

| M10        | GND              |  |  |

| M11        | ∨cc              |  |  |

| M12        | GND              |  |  |

| M13        | VCC              |  |  |

| M14        | GND              |  |  |

| M15        | VCC              |  |  |

| M16        | GND              |  |  |

| M17        | GND              |  |  |

| M18        | IO60NDB2V0       |  |  |

| M19        | IO58PDB2V0       |  |  |

| M20        | GND              |  |  |

| M21        | IO68NPB2V0       |  |  |

| M22        | IO61NDB2V0       |  |  |

| M23        | GND              |  |  |

| M24        | IO56NDB2V0       |  |  |

| M25        | VCCIB2           |  |  |

| M26        | IO65PDB2V0       |  |  |

|            |                  |  |  |

| FG676      |                  |  |  |

|------------|------------------|--|--|

| Pin Number | AFS1500 Function |  |  |

| N1         | NC               |  |  |

| N2         | NC               |  |  |

| N3         | IO108NDB4V0      |  |  |

| N4         | vccosc           |  |  |

| N5         | VCCIB4           |  |  |

| N6         | XTAL2            |  |  |

| N7         | GFC1/IO107PDB4V0 |  |  |

| N8         | VCCIB4           |  |  |

| N9         | GFB1/IO106PDB4V0 |  |  |

| N10        | VCCIB4           |  |  |

| N11        | GND              |  |  |

| N12        | VCC              |  |  |

| N13        | GND              |  |  |

| N14        | VCC              |  |  |

| N15        | GND              |  |  |

| N16        | VCC              |  |  |

| N17        | VCCIB2           |  |  |

| N18        | IO70PDB2V0       |  |  |

| N19        | VCCIB2           |  |  |

| N20        | IO69PDB2V0       |  |  |

| N21        | GCA1/IO64PDB2V0  |  |  |

| N22        | VCCIB2           |  |  |

| N23        | GCC0/IO62NDB2V0  |  |  |

| N24        | GCC1/IO62PDB2V0  |  |  |

| N25        | IO66PDB2V0       |  |  |

| N26        | IO65NDB2V0       |  |  |

| P1         | NC               |  |  |

| P2         | NC               |  |  |

| P3         | IO103PDB4V0      |  |  |

| P4         | XTAL1            |  |  |

| P5         | VCCIB4           |  |  |

| P6         | GNDOSC           |  |  |

| P7         | GFC0/IO107NDB4V0 |  |  |

| P8         | VCCIB4           |  |  |

| P9         | GFB0/IO106NDB4V0 |  |  |

| P10        | VCCIB4           |  |  |

|            |                  |  |  |

| FG676 |                  |  |  |

|-------|------------------|--|--|

|       |                  |  |  |

|       | AFS1500 Function |  |  |

| P11   | VCC              |  |  |

| P12   | GND              |  |  |

| P13   | VCC              |  |  |

| P14   | GND              |  |  |

| P15   | VCC              |  |  |

| P16   | GND              |  |  |

| P17   | VCCIB2           |  |  |

| P18   | IO70NDB2V0       |  |  |

| P19   | VCCIB2           |  |  |

| P20   | IO69NDB2V0       |  |  |

| P21   | GCA0/IO64NDB2V0  |  |  |

| P22   | VCCIB2           |  |  |

| P23   | GCB0/IO63NDB2V0  |  |  |

| P24   | GCB1/IO63PDB2V0  |  |  |

| P25   | IO66NDB2V0       |  |  |

| P26   | IO67PDB2V0       |  |  |

| R1    | NC               |  |  |

| R2    | VCCIB4           |  |  |

| R3    | IO103NDB4V0      |  |  |

| R4    | GND              |  |  |

| R5    | IO101PDB4V0      |  |  |

| R6    | IO100NPB4V0      |  |  |

| R7    | GND              |  |  |

| R8    | IO99PDB4V0       |  |  |

| R9    | IO97PDB4V0       |  |  |

| R10   | GND              |  |  |

| R11   | GND              |  |  |

| R12   | VCC              |  |  |

| R13   | GND              |  |  |

| R14   | VCC              |  |  |

| R15   | GND              |  |  |

| R16   | VCC              |  |  |

| R17   | GND              |  |  |

| R18   | GDB2/IO83PDB2V0  |  |  |

| R19   | IO78PDB2V0       |  |  |

| R20   | GND              |  |  |

4-32 Revision 6

# 5 - Datasheet Information

## **List of Changes**

The following table lists critical changes that were made in each revision of the Fusion datasheet.

| Revision                     | Changes                                                                                                                                                                                                                                                                                 | Page            |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Revision 6<br>(March 2014)   | Note added for the discontinuance of QN108 and QN180 packages to the "Package I/Os: Single-/Double-Ended (Analog)" table and the "Temperature Grade Offerings" table (SAR 55113, PDN 1306).                                                                                             |                 |

|                              | Updated details about page programming time in the "Program Operation" section (SAR 49291).                                                                                                                                                                                             | 2-46            |

|                              | ADC_START changed to ADCSTART in the "ADC Operation" section (SAR 44104).                                                                                                                                                                                                               | 2-104           |

| Revision 5<br>(January 2014) | Calibrated offset values (AFS090, AFS250) of the external temperature monitor in Table 2-49 • Analog Channel Specifications have been updated (SAR 51464).                                                                                                                              | 2-117           |

|                              | Specifications for the internal temperature monitor in Table 2-49 • Analog Channel Specifications have been updated (SAR 50870).                                                                                                                                                        | 2-117           |

| Revision 4<br>(January 2013) | The "Product Ordering Codes" section has been updated to mention "Y" as "Blank" mentioning "Device Does Not Include License to Implement IP Based on the Cryptography Research, Inc. (CRI) Patent Portfolio" (SAR 43177).                                                               | III             |

|                              | The note in Table 2-12 • Fusion CCC/PLL Specification referring the reader to SmartGen was revised to refer instead to the online help associated with the core (SAR 42563).                                                                                                            | 2-28            |

|                              | Table 2-49 • Analog Channel Specifications was modified to update the uncalibrated offset values (AFS250) of the external and internal temperature monitors (SAR 43134).                                                                                                                | 2-117           |

|                              | In Table 2-57 • Prescaler Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3), changed the column heading from 'Full-Scale Voltage' to 'Full Scale Voltage in 10-Bit Mode', and added and updated Notes as required (SAR 20812).                                                 | 2-130           |

|                              | The values for the Speed Grade (-1 and Std.) for FDDRIMAX (Table 2-180 • Input DDR Propagation Delays) and values for the Speed Grade (-2 and Std.) for FDDOMAX (Table 2-182 • Output DDR Propagation Delays) had been inadvertently interchanged. This has been rectified (SAR 38514). | 2-220,<br>2-222 |

|                              | Added description about what happens if a user connects VAREF to an external 3.3 V on their board to the "VAREF Analog Reference Voltage" section (SAR 35188).                                                                                                                          | 2-225           |

|                              | Added a note to Table 3-2 • Recommended Operating Conditions1 (SAR 43429): The programming temperature range supported is T <sub>ambient</sub> = 0°C to 85°C.                                                                                                                           | 3-3             |

|                              | Added the Package Thermal details for AFS600-PQ208 and AFS250-PQ208 to Table 3-6 • Package Thermal Resistance (SAR 37816). Deleted the Die Size column from the table (SAR 43503).                                                                                                      | 3-7             |

|                              | Libero Integrated Design Environment (IDE) was changed to Libero System-on-Chip (SoC) throughout the document (SAR 42495).                                                                                                                                                              | NA              |

|                              | Live at Power-Up (LAPU) has been replaced with 'Instant On'.                                                                                                                                                                                                                            |                 |

| Revision 3 (August 2012)     | Microblade U1AFS250 and U1AFS1500 devices were added to the product tables.                                                                                                                                                                                                             | I – IV          |

| (August 2012)                | A sentence pertaining to the analog I/Os was added to the "Specifying I/O States During Programming" section (SAR 34831).                                                                                                                                                               | 1-9             |