Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

E·XFI

| Product Status                 | Active                                                                    |

|--------------------------------|---------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | 110592                                                                    |

| Number of I/O                  | 119                                                                       |

| Number of Gates                | 600000                                                                    |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                           |

| Package / Case                 | 256-LBGA                                                                  |

| Supplier Device Package        | 256-FPBGA (17x17)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1afs600-2fg256 |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

## Fusion Device Family Overview

| Introduction              | 1-1  |

|---------------------------|------|

| General Description       | 1-1  |

| Unprecedented Integration | 1-4  |

| Related Documents         | 1-10 |

## **Device Architecture**

| Fusion Stack Architecture |  |

|---------------------------|--|

| Core Architecture         |  |

| Clocking Resources        |  |

| Real-Time Counter System  |  |

| Embedded Memories         |  |

| Analog Block              |  |

| Analog Configuration MUX  |  |

| User I/Os                 |  |

| Pin Descriptions          |  |

| Security                  |  |

## DC and Power Characteristics

| General Specifications        | 3-1  |

|-------------------------------|------|

| Calculating Power Dissipation | 3-10 |

| Power Consumption             | 3-32 |

## Package Pin Assignments

| QN108 | <br>    | <br> | <br>      | <br> | <br> | <br> | <br>    | <br> | <br> |     | <br> | <br>. 4- | 1 |

|-------|------|------|------|------|------|------|---------|------|-----------|------|------|------|---------|------|------|-----|------|----------|---|

| QN180 |      |      |      |      |      |      |         |      |           |      |      |      |         |      |      |     |      |          |   |

| PQ208 |      |      |      |      |      |      |         |      |           |      |      |      |         |      |      |     |      |          |   |

| FG256 |      |      |      |      |      |      |         |      |           |      |      |      |         |      |      |     |      |          |   |

| FG484 |      |      |      |      |      |      |         |      |           |      |      |      |         |      |      |     |      |          |   |

| FG676 | <br> | <br> | <br> | <br> | <br> | <br> | <br>••• | <br> | <br>• • • | <br> | <br> | <br> | <br>• • | <br> | <br> | ••• | <br> | <br>4-2  | 7 |

## **Datasheet Information**

| List of Changes                                                         |   |

|-------------------------------------------------------------------------|---|

| Datasheet Categories                                                    |   |

| Safety Critical, Life Support, and High-Reliability Applications Policy | / |

## **Clock Aggregation**

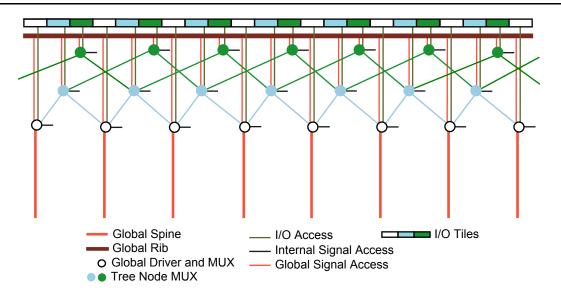

Clock aggregation allows for multi-spine clock domains. A MUX tree provides the necessary flexibility to allow long lines or I/Os to access domains of one, two, or four global spines. Signal access to the clock aggregation system is achieved through long-line resources in the central rib, and also through local resources in the north and south ribs, allowing I/Os to feed directly into the clock system. As Figure 2-14 indicates, this access system is contiguous.

There is no break in the middle of the chip for north and south I/O VersaNet access. This is different from the quadrant clocks, located in these ribs, which only reach the middle of the rib. Refer to the *Using Global Resources in Actel Fusion Devices* application note.

Figure 2-14 • Clock Aggregation Tree Architecture

## **1.5 V Voltage Regulator**

The 1.5 V voltage regulator uses an external pass transistor to generate 1.5 V from a 3.3 V supply. The base of the pass transistor is tied to PTBASE, the collector is tied to 3.3 V, and an emitter is tied to PTBASE and the 1.5 V supplies of the Fusion device. Figure 2-27 on page 2-31 shows the hook-up of the 1.5 V voltage regulator to an external pass transistor.

Microsemi recommends using a PN2222A or 2N2222A transistor. The gain of such a transistor is approximately 25, with a maximum base current of 20 mA. The maximum current that can be supported is 0.5 A. Transistors with different gain can also be used for different current requirements.

## Table 2-18 • Electrical Characteristics

| Symbol  | Parameter         | Condition |                           | Min   | Typical | Max   | Units |

|---------|-------------------|-----------|---------------------------|-------|---------|-------|-------|

| VOUT    | Output Voltage    | Tj = 25°C |                           | 1.425 | 1.5     | 1.575 | V     |

| ICC33A  | Operation Current | Tj = 25⁰C | ILOAD = 1 mA              |       | 11      |       | mA    |

|         |                   |           | ILOAD = 100 mA            |       | 11      |       | mA    |

|         |                   |           | ILOAD = 0.5 A             |       | 30      |       | mA    |

| ∆VOUT   | Load Regulation   | Tj = 25°C | ILOAD = 1 mA to 0.5 A     |       | 90      |       | mV    |

|         | Line Regulation   | Tj = 25°C | VCC33A = 2.97 V to 3.63 V |       |         |       |       |

|         |                   |           | ILOAD = 1 mA              |       | 10.6    |       | mV/V  |

|         |                   |           | VCC33A = 2.97 V to 3.63 V |       |         |       |       |

|         |                   |           | ILOAD = 100 mA            |       | 12.1    |       | mV/V  |

| ∆VOUT   |                   |           | VCC33A = 2.97 V to 3.63 V |       |         |       |       |

|         |                   |           | ILOAD = 500 mA            |       | 10.6    |       | mV/V  |

|         | Dropout Voltage*  | Tj = 25⁰C | ILOAD = 1 mA              |       | 0.63    |       | V     |

|         |                   |           | ILOAD = 100 mA            |       | 0.84    |       | V     |

|         |                   |           | ILOAD = 0.5 A             |       | 1.35    |       | V     |

| IPTBASE | PTBase Current    | Tj = 25°C | ILOAD = 1 mA              |       | 48      |       | μA    |

|         |                   |           | ILOAD = 100 mA            |       | 736     |       | μA    |

|         |                   |           | ILOAD = 0.5 A             |       | 12      | 20    | mA    |

#### VCC33A = 3.3 V

Note: \*Data collected with 2N2222A.

Data operations are performed in widths of 1 to 4 bytes. A write to a location in a page that is not already in the Page Buffer will cause the page to be read from the FB Array and stored in the Page Buffer. The block that was addressed during the write will be put into the Block Buffer, and the data written by WD will overwrite the data in the Block Buffer. After the data is written to the Block Buffer, the Block Buffer is then written to the Page Buffer to keep both buffers in sync. Subsequent writes to the same block will overwrite the Block Buffer and the Page Buffer. A write to another block in the page will cause the addressed block to be loaded from the Page Buffer, and the write will be performed as described previously.

The data width can be selected dynamically via the DATAWIDTH input bus. The truth table for the data width settings is detailed in Table 2-21. The minimum resolvable address is one 8-bit byte. For data widths greater than 8 bits, the corresponding address bits are ignored—when DATAWIDTH = 0 (2 bytes), ADDR[0] is ignored, and when DATAWIDTH = '10' or '11' (4 bytes), ADDR[1:0] are ignored. Data pins are LSB-oriented and unused WD data pins must be grounded.

#### Table 2-21 • Data Width Settings

| DATAWIDTH[1:0] | Data Width     |

|----------------|----------------|

| 00             | 1 byte [7:0]   |

| 01             | 2 byte [15:0]  |

| 10, 11         | 4 bytes [31:0] |

### Flash Memory Block Protection

#### Page Loss Protection

When the PAGELOSSPROTECT pin is set to logic 1, it prevents writes to any page other than the current page in the Page Buffer until the page is either discarded or programmed.

A write to another page while the current page is Page Loss Protected will return a STATUS of '11'.

#### **Overwrite Protection**

Any page that is Overwrite Protected will result in the STATUS being set to '01' when an attempt is made to either write, program, or erase it. To set the Overwrite Protection state for a page, set the OVERWRITEPROTECT pin when a Program operation is undertaken. To clear the Overwrite Protect state for a given page, an Unprotect Page operation must be performed on the page, and then the page must be programmed with the OVERWRITEPROTECT pin cleared to save the new page.

#### LOCKREQUEST

The LOCKREQUEST signal is used to give the user interface control over simultaneous access of the FB from both the User and JTAG interfaces. When LOCKREQUEST is asserted, the JTAG interface will hold off any access attempts until LOCKREQUEST is deasserted.

### Flash Memory Block Operations

#### FB Operation Priority

The FB provides for priority of operations when multiple actions are requested simultaneously. Table 2-22 shows the priority order (priority 0 is the highest).

| Table 2-22 | ٠ | FΒ | <b>Operation Priority</b> |

|------------|---|----|---------------------------|

|------------|---|----|---------------------------|

| Operation             | Priority |

|-----------------------|----------|

| System Initialization | 0        |

| FB Reset              | 1        |

| Read                  | 2        |

| Write                 | 3        |

| Erase Page            | 4        |

| Program               | 5        |

| Unprotect Page        | 6        |

| Discard Page          | 7        |

#### **Program Operation**

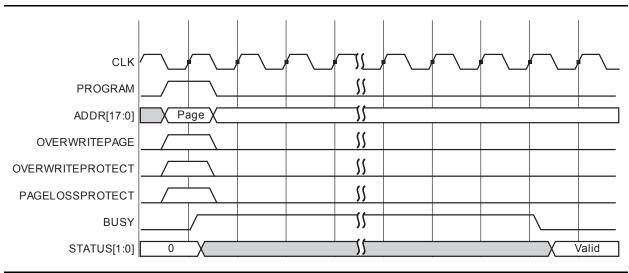

A Program operation is initiated by asserting the PROGRAM signal on the interface. Program operations save the contents of the Page Buffer to the FB Array. Due to the technologies inherent in the FB, the total programming (including erase) time per page of the eNVM is 6.8 ms. While the FB is writing the data to the array, the BUSY signal will be asserted.

During a Program operation, the sector and page addresses on ADDR are compared with the stored address for the page (and sector) in the Page Buffer. If there is a mismatch between the two addresses, the Program operation will be aborted and an error will be reported on the STATUS output.

It is possible to write the Page Buffer to a different page in memory. When asserting the PROGRAM pin, if OVERWRITEPAGE is asserted as well, the FB will write the contents of the Page Buffer to the sector and page designated on the ADDR inputs if the destination page is not Overwrite Protected.

A Program operation can be utilized to either modify the contents of the page in the flash memory block or change the protections for the page. Setting the OVERWRITEPROTECT bit on the interface while asserting the PROGRAM pin will put the page addressed into Overwrite Protect Mode. Overwrite Protect Mode safeguards a page from being inadvertently overwritten during subsequent Program or Erase operations.

Program operations that result in a STATUS value of '01' do not modify the addressed page. For all other values of STATUS, the addressed page is modified. Program errors include the following:

- 1. Attempting to program a page that is Overwrite Protected (STATUS = '01')

- 2. Attempting to program a page that is not in the Page Buffer when the Page Buffer has entered Page Loss Protection Mode (STATUS = '01')

- Attempting to perform a program with OVERWRITEPAGE set when the page addressed has been Overwrite Protected (STATUS = '01')

- 4. The Write Count of the page programmed exceeding the Write Threshold defined in the part specification (STATUS = '11')

- 5. The ECC Logic determining that there is an uncorrectable error within the programmed page (STATUS = '10')

- 6. Attempting to program a page that is **not** in the Page Buffer when OVERWRITEPAGE is not set and the page in the Page Buffer is modified (STATUS = '01')

- 7. Attempting to program the page in the Page Buffer when the Page Buffer is **not** modified

The waveform for a Program operation is shown in Figure 2-36.

#### Figure 2-36 • FB Program Waveform

Note: OVERWRITEPAGE is only sampled when the PROGRAM or ERASEPAGE pins are asserted. OVERWRITEPAGE is ignored in all other operations.

The following error indications are possible for Read operations:

- 1. STATUS = '01' when a single-bit data error was detected and corrected within the block addressed.

- 2. STATUS = '10' when a double-bit error was detected in the block addressed (note that the error is uncorrected).

In addition to data reads, users can read the status of any page in the FB by asserting PAGESTATUS along with REN. The format of the data returned by a page status read is shown in Table 2-23, and the definition of the page status bits is shown in Table 2-24.

Table 2-23 • Page Status Read Data Format

| 31      | 8     | 7    | 4     | 3              | 2              | 1               | 0                   |

|---------|-------|------|-------|----------------|----------------|-----------------|---------------------|

| Write 0 | Count | Rese | erved | Over Threshold | Read Protected | Write Protected | Overwrite Protected |

#### Table 2-24 • Page Status Bit Definition

| Page Status Bit(s) | Definition                                                                                                                                                                                                        |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–8               | The number of times the page addressed has been programmed/erased                                                                                                                                                 |

| 7–4                | Reserved; read as 0                                                                                                                                                                                               |

| 3                  | Over Threshold indicator (see the "Program Operation" section on page 2-46)                                                                                                                                       |

| 2                  | Read Protected; read protect bit for page, which is set via the JTAG interface and only affects JTAG operations. This bit can be overridden by using the correct user key value.                                  |

| 1                  | Write Protected; write protect bit for page, which is set via the JTAG interface and only affects JTAG operations. This bit can be overridden by using the correct user key value.                                |

| 0                  | Overwrite Protected; designates that the user has set the OVERWRITEPROTECT bit on the interface while doing a Program operation. The page cannot be written without first performing an Unprotect Page operation. |

# Table 2-49 • Analog Channel Specifications (continued)Commercial Temperature Range Conditions, TJ = 85°C (unless noted otherwise),Typical: VCC33A = 3.3 V, VCC = 1.5 V

| Parameter                                      | Description                    | Condition                                                     | Min. | Тур. | Max. | Units |

|------------------------------------------------|--------------------------------|---------------------------------------------------------------|------|------|------|-------|

| Temperature Mo                                 | onitor Using Analog Pad        | AT                                                            |      |      |      |       |

| External                                       | Resolution                     | 8-bit ADC                                                     |      | °C   |      |       |

| Temperature<br>Monitor                         |                                | 10-bit ADC                                                    |      |      | 1    | °C    |

| (external diode                                |                                | 12-bit ADC                                                    |      | C    | .25  | °C    |

| 2N3904,<br>T <sub>J</sub> = 25°C) <sup>4</sup> | Systematic Offset <sup>5</sup> | AFS090, AFS250, AFS600,<br>AFS1500, uncalibrated <sup>7</sup> |      |      | 5    | °C    |

|                                                |                                | AFS090, AFS250, AFS600,<br>AFS1500, calibrated <sup>7</sup>   |      |      | ±5   | °C    |

|                                                | Accuracy                       |                                                               |      | ±3   | ±5   | °C    |

|                                                | External Sensor Source         | High level, TMSTBx = 0                                        |      | 10   |      | μA    |

|                                                | Current                        | Low level, TMSTBx = 1                                         |      | 100  |      | μA    |

|                                                | Max Capacitance on AT pad      |                                                               |      |      | 1.3  | nF    |

| Internal                                       | Resolution                     | 8-bit ADC                                                     | 4    |      |      | °C    |

| Temperature<br>Monitor                         |                                | 10-bit ADC                                                    | 1    |      |      | °C    |

| Monitor                                        |                                | 12-bit ADC                                                    | 0.25 |      |      | °C    |

|                                                | Systematic Offset <sup>5</sup> | AFS090 <sup>7</sup>                                           |      | 5    |      |       |

|                                                |                                | AFS250, AFS600, AFS1500 <sup>7</sup>                          |      |      | 11   | °C    |

|                                                | Accuracy                       |                                                               |      | ±3   | ±5   | °C    |

| t <sub>TMSHI</sub>                             | Strobe High time               |                                                               | 10   |      | 105  | μs    |

| t <sub>TMSLO</sub>                             | Strobe Low time                |                                                               | 5    |      |      | μs    |

| t <sub>TMSSET</sub>                            | Settling time                  |                                                               | 5    |      |      | μs    |

Notes:

1. VRSM is the maximum voltage drop across the current sense resistor.

2. Analog inputs used as digital inputs can tolerate the same voltage limits as the corresponding analog pad. There is no reliability concern on digital inputs as long as VIND does not exceed these limits.

3. VIND is limited to VCC33A + 0.2 to allow reaching 10 MHz input frequency.

- 4. An averaging of 1,024 samples (LPF setting in Analog System Builder) is required and the maximum capacitance allowed across the AT pins is 500 pF.

- 5. The temperature offset is a fixed positive value.

- 6. The high current mode has a maximum power limit of 20 mW. Appropriate current limit resistors must be used, based on voltage on the pad.

- 7. When using SmartGen Analog System Builder, CalibIP is required to obtain specified offset. For further details on CalibIP, refer to the "Temperature, Voltage, and Current Calibration in Fusion FPGAs" chapter of the Fusion FPGA Fabric User Guide.

| Calit     | orated Typica               | al Error per                                                                                                                                                                                                                                   | <sup>.</sup> Positive F                                                     | Prescaler S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | etting <sup>1</sup> (%F                                | SR)                                                    | Direct ADC <sup>2,3</sup><br>(%FSR)                                                                                         |

|-----------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 16 V (AT) | 16 V (12 V)<br>(AV/AC)      | 8 V<br>(AV/AC)                                                                                                                                                                                                                                 | 4 V (AT)                                                                    | 4 V<br>(AV/AC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2 V<br>(AV/AC)                                         | 1 V<br>(AV/AC)                                         | VAREF = 2.56 V                                                                                                              |

| 1         |                             |                                                                                                                                                                                                                                                |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                        |                                                        |                                                                                                                             |

| 1         |                             |                                                                                                                                                                                                                                                |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                        |                                                        |                                                                                                                             |

| 1         | 1                           |                                                                                                                                                                                                                                                |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                        |                                                        |                                                                                                                             |

| 2         | 2                           | 1                                                                                                                                                                                                                                              |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                        |                                                        |                                                                                                                             |

| 2         | 2                           | 1                                                                                                                                                                                                                                              | 1                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                        |                                                        |                                                                                                                             |

| 3         | 2                           | 1                                                                                                                                                                                                                                              | 1                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                        |                                                        | 1                                                                                                                           |

| 4         | 4                           | 1                                                                                                                                                                                                                                              | 1                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                      |                                                        | 1                                                                                                                           |

| 5         | 5                           | 2                                                                                                                                                                                                                                              | 2                                                                           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                      |                                                        | 1                                                                                                                           |

| 7         | 6                           | 2                                                                                                                                                                                                                                              | 2                                                                           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                      |                                                        | 1                                                                                                                           |

| 9         | 9                           | 4                                                                                                                                                                                                                                              | 3                                                                           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                      | 1                                                      | 1                                                                                                                           |

|           | 16 V (AT) 1 1 1 2 2 3 4 5 7 | 16 V (AT)         16 V (12 V)<br>(AV/AC)           1         1           1         1           1         1           2         2           2         2           3         2           4         4           5         5           7         6 | 16 V (AT)         16 V (12 V)<br>(AV/AC)         8 V<br>(AV/AC)           1 | 16 V (AT)         16 V (12 V)<br>(AV/AC)         8 V<br>(AV/AC)         4 V (AT)           1         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <td><math display="block">\begin{array}{c c c c c c c c c c c c c c c c c c c </math></td> <td><math display="block">\begin{array}{c c c c c c c c c c c c c c c c c c c </math></td> <td>16 V (AT)(AV/AC)(AV/AC)<math>(AV/AC)</math><math>(AV/AC)</math><math>(AV/AC)</math><math>(AV/AC)</math><math>(AV/AC)</math>1111111111111122111113211111441111155222117622211</td> | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | 16 V (AT)(AV/AC)(AV/AC) $(AV/AC)$ $(AV/AC)$ $(AV/AC)$ $(AV/AC)$ $(AV/AC)$ 1111111111111122111113211111441111155222117622211 |

## Table 2-53 • Analog Channel Accuracy: Monitoring Standard Positive VoltagesTypical Conditions, $T_A = 25^{\circ}C$

Notes:

1. Requires enabling Analog Calibration using SmartGen Analog System Builder. For further details, refer to the "Temperature, Voltage, and Current Calibration in Fusion FPGAs" chapter of the Fusion FPGA Fabric User Guide.

2. Direct ADC mode using an external VAREF of 2.56V±4.6mV, without Analog Calibration macro.

3. For input greater than 2.56 V, the ADC output will saturate. A higher VAREF or prescaler usage is recommended.

#### Examples

#### Calculating Accuracy for an Uncalibrated Analog Channel

#### Formula

For a given prescaler range, EQ 30 gives the output voltage.

Output Voltage = (Channel Output Offset in V) + (Input Voltage x Channel Gain)

EQ 30

#### where

Channel Output offset in V = Channel Input offset in LSBs x Equivalent voltage per LSB Channel Gain Factor = 1 + (% Channel Gain / 100)

#### Example

Input Voltage = 5 V Chosen Prescaler range = 8 V range Refer to Table 2-51 on page 2-122.

Max. Output Voltage = (Max Positive input offset) + (Input Voltage x Max Positive Channel Gain)

Max. Positive input offset = (21 LSB) x (8 mV per LSB in 10-bit mode) Max. Positive input offset = 166 mV Max. Positive Gain Error = +3% Max. Positive Channel Gain = 1 + (+3% / 100) Max. Positive Channel Gain = 1.03 Max. Output Voltage = (166 mV) + (5 V x 1.03) Max. Output Voltage = **5.316 V**

## **Hot-Swap Support**

Hot-swapping (also called hot plugging) is the operation of hot insertion or hot removal of a card in (or from) a powered-up system. The levels of hot-swap support and examples of related applications are described in Table 2-74. The I/Os also need to be configured in hot insertion mode if hot plugging compliance is required.

Table 2-74 • Levels of Hot-Swap Support

| Hot<br>Swapping<br>Level | Description                     | Power<br>Applied<br>to Device | Bus State                                                                                                                   | Card<br>Ground<br>Connection                                                                        | Device<br>Circuitry<br>Connected<br>to Bus Pins | Example of<br>Application with<br>Cards that Contain<br>Fusion Devices                                                                                                                        | Compliance of<br>Fusion Devices                                                                            |

|--------------------------|---------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 1                        | Cold-swap                       | No                            | _                                                                                                                           | _                                                                                                   | _                                               | System and card with<br>Microsemi FPGA chip<br>are powered down,<br>then card gets<br>plugged into system,<br>then power supplies<br>are turned on for<br>system but not for<br>FPGA on card. | Compliant I/Os<br>can but do not<br>have to be set to<br>hot insertion<br>mode.                            |

| 2                        | Hot-swap<br>while reset         | Yes                           | Held in<br>reset state                                                                                                      | Must be made<br>and<br>maintained for<br>1 ms before,<br>during, and<br>after insertion/<br>removal | _                                               | In PCI hot plug<br>specification, reset<br>control circuitry<br>isolates the card<br>busses until the card<br>supplies are at their<br>nominal operating<br>levels and stable.                | Compliant I/Os<br>can but do not<br>have to be set to<br>hot insertion<br>mode.                            |

| 3                        | Hot-swap<br>while bus<br>idle   |                               | Held idle<br>(no ongoing<br>I/O<br>processes<br>during<br>insertion/re<br>moval)                                            | Same as<br>Level 2                                                                                  | glitch-free<br>during<br>power-up or            | no toggling activity on bus. It is critical that                                                                                                                                              | Compliant with<br>cards with two<br>levels of staging.<br>I/Os have to be<br>set to hot<br>insertion mode. |

| 4                        | Hot-swap on<br>an active<br>bus | Yes                           | Bus may<br>have active<br>I/O<br>processes<br>ongoing,<br>but device<br>being<br>inserted or<br>removed<br>must be<br>idle. | Same as<br>Level 2                                                                                  | Same as<br>Level 3                              | is critical that the logic<br>states set on the bus<br>signal do not get                                                                                                                      | Compliant with<br>cards with two<br>levels of staging.<br>I/Os have to be<br>set to hot<br>insertion mode. |

## **5 V Input Tolerance**

I/Os can support 5 V input tolerance when LVTTL 3.3 V, LVCMOS 3.3 V, LVCMOS 2.5 V / 5 V, and LVCMOS 2.5 V configurations are used (see Table 2-77 on page 2-147 for more details). There are four recommended solutions (see Figure 2-103 to Figure 2-106 on page 2-146 for details of board and macro setups) to achieve 5 V receiver tolerance. All the solutions meet a common requirement of limiting the voltage at the input to 3.6 V or less. In fact, the I/O absolute maximum voltage rating is 3.6 V, and any voltage above 3.6 V may cause long-term gate oxide failures.

## Solution 1

The board-level design needs to ensure that the reflected waveform at the pad does not exceed the limits provided in Table 3-4 on page 3-4. This is a long-term reliability requirement.

This scheme will also work for a 3.3 V PCI / PCI-X configuration, but the internal diode should not be used for clamping, and the voltage must be limited by the two external resistors, as explained below. Relying on the diode clamping would create an excessive pad DC voltage of 3.3 V + 0.7 V = 4 V.

The following are some examples of possible resistor values (based on a simplified simulation model with no line effects and 10  $\Omega$  transmitter output resistance, where Rtx\_out\_high = (VCCI – VOH) / IOH, Rtx\_out\_low = VOL / IOL).

Example 1 (high speed, high current):

Rtx\_out\_high = Rtx\_out\_low = 10  $\Omega$

R1 = 36  $\Omega$  (±5%), P(r1)min = 0.069  $\Omega$

R2 = 82  $\Omega$  (±5%), P(r2)min = 0.158  $\Omega$

Imax\_tx = 5.5 V / (82 \* 0.95 + 36 \* 0.95 + 10) = 45.04 mA

t<sub>RISE</sub> = t<sub>FALL</sub> = 0.85 ns at C\_pad\_load = 10 pF (includes up to 25% safety margin)

t<sub>RISE</sub> = t<sub>FALL</sub> = 4 ns at C\_pad\_load = 50 pF (includes up to 25% safety margin)

Example 2 (low-medium speed, medium current):

Rtx\_out\_high = Rtx\_out\_low = 10  $\Omega$

R1 = 220 Ω (±5%), P(r1)min = 0.018 Ω

R2 = 390  $\Omega$  (±5%), P(r2)min = 0.032  $\Omega$

Imax\_tx = 5.5 V / (220 \* 0.95 + 390 \* 0.95 + 10) = 9.17 mA

t<sub>RISE</sub> = t<sub>FALL</sub> = 4 ns at C\_pad\_load = 10 pF (includes up to 25% safety margin)

t<sub>RISE</sub> = t<sub>FALL</sub> = 20 ns at C\_pad\_load = 50 pF (includes up to 25% safety margin)

Other values of resistors are also allowed as long as the resistors are sized appropriately to limit the voltage at the receiving end to 2.5 V < Vin(rx) < 3.6 V when the transmitter sends a logic 1. This range of Vin\_dc(rx) must be assured for any combination of transmitter supply (5 V ± 0.5 V), transmitter output resistance, and board resistor tolerances.

## Summary of I/O Timing Characteristics – Default I/O Software Settings

## Table 2-90 • Summary of AC Measuring Points Applicable to All I/O Bank Types

| Standard                   | Input Reference Voltage<br>(VREF_TYP) | Board Termination Voltage<br>(VTT_REF) | Measuring Trip Point<br>(Vtrip)         |  |  |  |  |  |

|----------------------------|---------------------------------------|----------------------------------------|-----------------------------------------|--|--|--|--|--|

| 3.3 V LVTTL / 3.3 V LVCMOS | -                                     | -                                      | 1.4 V                                   |  |  |  |  |  |

| 2.5 V LVCMOS               | _                                     | -                                      | 1.2 V                                   |  |  |  |  |  |

| 1.8 V LVCMOS               | _                                     | -                                      | 0.90 V                                  |  |  |  |  |  |

| 1.5 V LVCMOS               | _                                     | -                                      | 0.75 V                                  |  |  |  |  |  |

| 3.3 V PCI                  | _                                     | -                                      | 0.285 * VCCI (RR)<br>0.615 * VCCI (FF)) |  |  |  |  |  |

| 3.3 V PCI-X                | _                                     | -                                      | 0.285 * VCCI (RR)<br>0.615 * VCCI (FF)  |  |  |  |  |  |

| 3.3 V GTL                  | 0.8 V                                 | 1.2 V                                  | VREF                                    |  |  |  |  |  |

| 2.5 V GTL                  | 0.8 V                                 | 1.2 V                                  | VREF                                    |  |  |  |  |  |

| 3.3 V GTL+                 | 1.0 V                                 | 1.5 V                                  | VREF                                    |  |  |  |  |  |

| 2.5 V GTL+                 | 1.0 V                                 | 1.5 V                                  | VREF                                    |  |  |  |  |  |

| HSTL (I)                   | 0.75 V                                | 0.75 V                                 | VREF                                    |  |  |  |  |  |

| HSTL (II)                  | 0.75 V                                | 0.75 V                                 | VREF                                    |  |  |  |  |  |

| SSTL2 (I)                  | 1.25 V                                | 1.25 V                                 | VREF                                    |  |  |  |  |  |

| SSTL2 (II)                 | 1.25 V                                | 1.25 V                                 | VREF                                    |  |  |  |  |  |

| SSTL3 (I)                  | 1.5 V                                 | 1.485 V                                | VREF                                    |  |  |  |  |  |

| SSTL3 (II)                 | 1.5 V                                 | 1.485 V                                | VREF                                    |  |  |  |  |  |

| LVDS                       | -                                     | -                                      | Cross point                             |  |  |  |  |  |

| LVPECL                     | _                                     | -                                      | Cross point                             |  |  |  |  |  |

### Table 2-91 • I/O AC Parameter Definitions

| Parameter         | Definition                                                                  |

|-------------------|-----------------------------------------------------------------------------|

| t <sub>DP</sub>   | Data to Pad delay through the Output Buffer                                 |

| t <sub>PY</sub>   | Pad to Data delay through the Input Buffer with Schmitt trigger disabled    |

| t <sub>DOUT</sub> | Data to Output Buffer delay through the I/O interface                       |

| t <sub>EOUT</sub> | Enable to Output Buffer Tristate Control delay through the I/O interface    |

| t <sub>DIN</sub>  | Input Buffer to Data delay through the I/O interface                        |

| t <sub>PYS</sub>  | Pad to Data delay through the Input Buffer with Schmitt trigger enabled     |

| t <sub>HZ</sub>   | Enable to Pad delay through the Output Buffer—High to Z                     |

| t <sub>ZH</sub>   | Enable to Pad delay through the Output Buffer—Z to High                     |

| t <sub>LZ</sub>   | Enable to Pad delay through the Output Buffer—Low to Z                      |

| t <sub>ZL</sub>   | Enable to Pad delay through the Output Buffer—Z to Low                      |

| t <sub>ZHS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to High |

| t <sub>ZLS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to Low  |

#### Table 2-122 • 1.8 V LVCMOS Low Slew

Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V Applicable to Advanced I/Os

| Drive<br>Strength | Speed<br>Grade  | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|-----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.            | 0.66              | 15.53           | 0.04             | 1.31            | 0.43              | 14.11           | 15.53           | 2.78            | 1.60            | 16.35            | 17.77            | ns    |

|                   | -1              | 0.56              | 13.21           | 0.04             | 1.11            | 0.36              | 12.01           | 13.21           | 2.36            | 1.36            | 13.91            | 15.11            | ns    |

|                   | -2 <sup>2</sup> | 0.49              | 11.60           | 0.03             | 0.98            | 0.32              | 10.54           | 11.60           | 2.07            | 1.19            | 12.21            | 13.27            | ns    |

| 4 mA              | Std.            | 0.66              | 10.48           | 0.04             | 1.31            | 0.43              | 10.41           | 10.48           | 3.23            | 2.73            | 12.65            | 12.71            | ns    |

|                   | -1              | 0.56              | 8.91            | 0.04             | 1.11            | 0.36              | 8.86            | 8.91            | 2.75            | 2.33            | 10.76            | 10.81            | ns    |

|                   | -2              | 0.49              | 7.82            | 0.03             | 0.98            | 0.32              | 7.77            | 7.82            | 2.41            | 2.04            | 9.44             | 9.49             | ns    |

| 8 mA              | Std.            | 0.66              | 8.05            | 0.04             | 1.31            | 0.43              | 8.20            | 7.84            | 3.54            | 3.27            | 10.43            | 10.08            | ns    |

|                   | -1              | 0.56              | 6.85            | 0.04             | 1.11            | 0.36              | 6.97            | 6.67            | 3.01            | 2.78            | 8.88             | 8.57             | ns    |

|                   | -2              | 0.49              | 6.01            | 0.03             | 0.98            | 0.32              | 6.12            | 5.86            | 2.64            | 2.44            | 7.79             | 7.53             | ns    |

| 12 mA             | Std.            | 0.66              | 7.50            | 0.04             | 1.31            | 0.43              | 7.64            | 7.30            | 3.61            | 3.41            | 9.88             | 9.53             | ns    |

|                   | -1              | 0.56              | 6.38            | 0.04             | 1.11            | 0.36              | 6.50            | 6.21            | 3.07            | 2.90            | 8.40             | 8.11             | ns    |

|                   | -2              | 0.49              | 5.60            | 0.03             | 0.98            | 0.32              | 5.71            | 5.45            | 2.69            | 2.55            | 7.38             | 7.12             | ns    |

| 16 mA             | Std.            | 0.66              | 7.29            | 0.04             | 1.31            | 0.43              | 7.23            | 7.29            | 3.71            | 3.95            | 9.47             | 9.53             | ns    |

|                   | -1              | 0.56              | 6.20            | 0.04             | 1.11            | 0.36              | 6.15            | 6.20            | 3.15            | 3.36            | 8.06             | 8.11             | ns    |

|                   | -2              | 0.49              | 5.45            | 0.03             | 0.98            | 0.32              | 5.40            | 5.45            | 2.77            | 2.95            | 7.07             | 7.12             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

The 1.76 W power is less than the required 3.00 W. The design therefore requires a heat sink, or the airflow where the device is mounted should be increased. The design's total junction-to-air thermal resistance requirement can be estimated by EQ 7:

$$\theta_{ja(total)} = \frac{T_J - T_A}{P} = \frac{100^{\circ}C - 70^{\circ}C}{3.00 \text{ W}} = 10.00^{\circ}\text{C/W}$$

Determining the heat sink's thermal performance proceeds as follows:

$$\theta_{\mathsf{JA}(\mathsf{TOTAL})} = \theta_{\mathsf{JC}} + \theta_{\mathsf{CS}} + \theta_{\mathsf{SA}}$$

EQ 8

EQ 7

where

- $\theta_{JA} = 0.37^{\circ}C/W$

- Thermal resistance of the interface material between the case and the heat sink, usually provided by the thermal interface manufacturer

$\theta_{SA}$  = Thermal resistance of the heat sink in °C/W

$$\theta_{SA} = \theta_{JA(TOTAL)} - \theta_{JC} - \theta_{CS}$$

EQ 9

$$\theta_{SA} = 13.33^{\circ}C/W - 8.28^{\circ}C/W - 0.37^{\circ}C/W = 5.01^{\circ}C/W$$

A heat sink with a thermal resistance of 5.01°C/W or better should be used. Thermal resistance of heat sinks is a function of airflow. The heat sink performance can be significantly improved with increased airflow.

Carefully estimating thermal resistance is important in the long-term reliability of an Microsemi FPGA. Design engineers should always correlate the power consumption of the device with the maximum allowable power dissipation of the package selected for that device.

Note: The junction-to-air and junction-to-board thermal resistances are based on JEDEC standard (JESD-51) and assumptions made in building the model. It may not be realized in actual application and therefore should be used with a degree of caution. Junction-to-case thermal resistance assumes that all power is dissipated through the case.

### Temperature and Voltage Derating Factors

Table 3-7 • Temperature and Voltage Derating Factors for Timing Delays<br/>(normalized to  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V)

| Array Voltage | Junction Temperature (°C) |      |      |      |      |       |  |  |  |

|---------------|---------------------------|------|------|------|------|-------|--|--|--|

| VCC (V)       | –40°C                     | 0°C  | 25°C | 70°C | 85°C | 100°C |  |  |  |

| 1.425         | 0.88                      | 0.93 | 0.95 | 1.00 | 1.02 | 1.05  |  |  |  |

| 1.500         | 0.83                      | 0.88 | 0.90 | 0.95 | 0.96 | 0.99  |  |  |  |

| 1.575         | 0.80                      | 0.85 | 0.87 | 0.91 | 0.93 | 0.96  |  |  |  |

#### **RC Oscillator Dynamic Contribution**—**P**<sub>RC-OSC</sub>

#### **Operating Mode**

P<sub>RC-OSC</sub> = PAC19

#### Standby Mode and Sleep Mode

$P_{RC-OSC} = 0 W$

#### Analog System Dynamic Contribution—P<sub>AB</sub>

**Operating Mode**

P<sub>AB</sub> = PAC20

#### Standby Mode and Sleep Mode

$P_{AB} = 0 W$

#### Guidelines

#### Toggle Rate Definition

A toggle rate defines the frequency of a net or logic element relative to a clock. It is a percentage. If the toggle rate of a net is 100%, this means that the net switches at half the clock frequency. Below are some examples:

- The average toggle rate of a shift register is 100%, as all flip-flop outputs toggle at half of the clock frequency.

- The average toggle rate of an 8-bit counter is 25%:

- Bit 0 (LSB) = 100%

- Bit 1 = 50%

- Bit 2 = 25%

- ...

- Bit 7 (MSB) = 0.78125%

- Average toggle rate = (100% + 50% + 25% + 12.5% + . . . 0.78125%) / 8.

#### Enable Rate Definition

Output enable rate is the average percentage of time during which tristate outputs are enabled. When non-tristate output buffers are used, the enable rate should be 100%.

#### Table 3-16 • Toggle Rate Guidelines Recommended for Power Calculation

| Component      | Definition                       | Guideline |

|----------------|----------------------------------|-----------|

| $\alpha_1$     | Toggle rate of VersaTile outputs | 10%       |

| α <sub>2</sub> | I/O buffer toggle rate           | 10%       |

#### Table 3-17 • Enable Rate Guidelines Recommended for Power Calculation

| Component      | Definition                           | Guideline |

|----------------|--------------------------------------|-----------|

| β <sub>1</sub> | I/O output buffer enable rate        | 100%      |

| β <sub>2</sub> | RAM enable rate for read operations  | 12.5%     |

| $\beta_3$      | RAM enable rate for write operations | 12.5%     |

| β <sub>4</sub> | NVM enable rate for read operations  | 0%        |

$P_{S-CELL} = 0 W$  $P_{C-CELL} = 0 W$  $P_{NET} = 0 W$  $P_{LOGIC} = 0 W$

#### I/O Input and Output Buffer Contribution—P<sub>I/O</sub>

This example uses LVTTL 3.3 V I/O cells. The output buffers are 12 mA-capable, configured with high output slew and driving a 35 pF output load.

$F_{CLK} = 50 \text{ MHz}$ Number of input pins used: N<sub>INPUTS</sub> = 30 Number of output pins used: N<sub>OUTPUTS</sub> = 40 Estimated I/O buffer toggle rate:  $\alpha_2$  = 0.1 (10%) Estimated IO buffer enable rate:  $\beta_1$  = 1 (100%)

#### **Operating Mode**

$$\begin{split} \mathsf{P}_{\mathsf{INPUTS}} &= \mathsf{N}_{\mathsf{INPUTS}} * (\alpha_2 \,/\, 2) * \mathsf{PAC9} * \mathsf{F}_{\mathsf{CLK}} \\ \mathsf{P}_{\mathsf{INPUTS}} &= 30 * (0.1 \,/\, 2) * 0.01739 * 50 \\ \mathsf{P}_{\mathsf{INPUTS}} &= 1.30 \text{ mW} \end{split}$$

$$\begin{split} \mathsf{P}_{\text{OUTPUTS}} &= \mathsf{N}_{\text{OUTPUTS}} * (\alpha_2 / 2) * \beta_1 * \mathsf{PAC10} * \mathsf{F}_{\text{CLK}} \\ \mathsf{P}_{\text{OUTPUTS}} &= 40 * (0.1 / 2) * 1 * 0.4747 * 50 \\ \mathsf{P}_{\text{OUTPUTS}} &= 47.47 \text{ mW} \end{split}$$

$P_{I/O} = P_{INPUTS} + P_{OUTPUTS}$  $P_{I/O} = 1.30 \text{ mW} + 47.47 \text{ mW}$

P<sub>I/O</sub> = 48.77 mW

#### Standby Mode and Sleep Mode

$P_{INPUTS} = 0 W$

$P_{OUTPUTS} = 0 W$  $P_{I/O} = 0 W$

#### RAM Contribution—P<sub>MEMORY</sub>

Frequency of Read Clock:  $F_{READ-CLOCK} = 10 \text{ MHz}$ Frequency of Write Clock:  $F_{WRITE-CLOCK} = 10 \text{ MHz}$ Number of RAM blocks:  $N_{BLOCKS} = 20$ Estimated RAM Read Enable Rate:  $\beta_2 = 0.125 (12.5\%)$ Estimated RAM Write Enable Rate:  $\beta_3 = 0.125 (12.5\%)$

#### **Operating Mode**

$$\begin{split} \mathsf{P}_{\mathsf{MEMORY}} &= (\mathsf{N}_{\mathsf{BLOCKS}} * \mathsf{PAC11} * \beta_2 * \mathsf{F}_{\mathsf{READ-CLOCK}}) + (\mathsf{N}_{\mathsf{BLOCKS}} * \mathsf{PAC12} * \beta_3 * \mathsf{F}_{\mathsf{WRITE-CLOCK}}) \\ \mathsf{P}_{\mathsf{MEMORY}} &= (20 * 0.025 * 0.125 * 10) + (20 * 0.030 * 0.125 * 10) \\ \mathsf{P}_{\mathsf{MEMORY}} &= 1.38 \text{ mW} \end{split}$$

#### Standby Mode and Sleep Mode

P<sub>MEMORY</sub> = 0 W

Package Pin Assignments

| QN108      |                 |                            | QN108           |            | QN108                   |

|------------|-----------------|----------------------------|-----------------|------------|-------------------------|

| Pin Number | AFS090 Function | Pin Number AFS090 Function |                 | Pin Number | AFS090 Function         |

| A1         | NC              | A39                        | GND             | B21        | AC2                     |

| A2         | GNDQ            | A40                        | GCB1/IO35PDB1V0 | B22        | ATRTN1                  |

| A3         | GAA2/IO52PDB3V0 | A41                        | GCB2/IO33PDB1V0 | B23        | AG3                     |

| A4         | GND             | A42                        | GBA2/IO31PDB1V0 | B24        | AV3                     |

| A5         | GFA1/IO47PDB3V0 | A43                        | NC              | B25        | VCC33A                  |

| A6         | GEB1/IO45PDB3V0 | A44                        | GBA1/IO30RSB0V0 | B26        | VAREF                   |

| A7         | VCCOSC          | A45                        | GBB1/IO28RSB0V0 | B27        | PUB                     |

| A8         | XTAL2           | A46                        | GND             | B28        | VCC33A                  |

| A9         | GEA1/IO44PPB3V0 | A47                        | VCC             | B29        | PTBASE                  |

| A10        | GEA0/IO44NPB3V0 | A48                        | GBC1/IO26RSB0V0 | B30        | VCCNVM                  |

| A11        | GEB2/IO42PDB3V0 | A49                        | IO21RSB0V0      | B31        | VCC                     |

| A12        | VCCNVM          | A50                        | IO19RSB0V0      | B32        | TDI                     |

| A13        | VCC15A          | A51                        | IO09RSB0V0      | B33        | TDO                     |

| A14        | PCAP            | A52                        | GAC0/IO04RSB0V0 | B34        | VJTAG                   |

| A15        | NC              | A53                        | VCCIB0          | B35        | GDC0/IO38NDB1V          |

| A16        | GNDA            | A54                        | GND             |            | 0                       |

| A17        | AV0             | A55                        | GAB0/IO02RSB0V0 | B36        | VCCIB1                  |