Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Detans                         |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Active                                                                     |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | -                                                                          |

| Total RAM Bits                 | 110592                                                                     |

| Number of I/O                  | 119                                                                        |

| Number of Gates                | 600000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 256-LBGA                                                                   |

| Supplier Device Package        | 256-FPBGA (17x17)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/m1afs600-fgg256i |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 – Fusion Device Family Overview

## Introduction

The Fusion mixed signal FPGA satisfies the demand from system architects for a device that simplifies design and unleashes their creativity. As the world's first mixed signal programmable logic family, Fusion integrates mixed signal analog, flash memory, and FPGA fabric in a monolithic device. Fusion devices enable designers to quickly move from concept to completed design and then deliver feature-rich systems to market. This new technology takes advantage of the unique properties of Microsemi flash-based FPGAs, including a high-isolation, triple-well process and the ability to support high-voltage transistors to meet the demanding requirements of mixed signal system design.

Fusion mixed signal FPGAs bring the benefits of programmable logic to many application areas, including power management, smart battery charging, clock generation and management, and motor control. Until now, these applications have only been implemented with costly and space-consuming discrete analog components or mixed signal ASIC solutions. Fusion mixed signal FPGAs present new capabilities for system development by allowing designers to integrate a wide range of functionality into a single device, while at the same time offering the flexibility of upgrades late in the manufacturing process or after the device is in the field. Fusion devices provide an excellent alternative to costly and

time-consuming mixed signal ASIC designs. In addition, when used in conjunction with the ARM Cortex-M1 processor, Fusion technology represents the definitive mixed signal FPGA platform.

Flash-based Fusion devices are Instant On. As soon as system power is applied and within normal operating specifications, Fusion devices are working. Fusion devices have a 128-bit flash-based lock and industry-leading AES decryption, used to secure programmed intellectual property (IP) and configuration data. Fusion devices are the most comprehensive single-chip analog and digital programmable logic solution available today.

To support this new ground-breaking technology, Microsemi has developed a series of major tool innovations to help maximize designer productivity. Implemented as extensions to the popular Microsemi Libero<sup>®</sup> System-on-Chip (SoC) software, these new tools allow designers to easily instantiate and configure peripherals within a design, establish links between peripherals, create or import building blocks or reference designs, and perform hardware verification. This tool suite will also add comprehensive hardware/software debug capability as well as a suite of utilities to simplify development of embedded soft-processor-based solutions.

## **General Description**

The Fusion family, based on the highly successful ProASIC<sup>®</sup>3 and ProASIC3E flash FPGA architecture, has been designed as a high-performance, programmable, mixed signal platform. By combining an advanced flash FPGA core with flash memory blocks and analog peripherals, Fusion devices dramatically simplify system design and, as a result, dramatically reduce overall system cost and board space.

The state-of-the-art flash memory technology offers high-density integrated flash memory blocks, enabling savings in cost, power, and board area relative to external flash solutions, while providing increased flexibility and performance. The flash memory blocks and integrated analog peripherals enable true mixed-mode programmable logic designs. Two examples are using an on-chip soft processor to implement a fully functional flash MCU and using high-speed FPGA logic to offer system and power supervisory capabilities. Instant On, and capable of operating from a single 3.3 V supply, the Fusion family is ideally suited for system management and control applications.

The devices in the Fusion family are categorized by FPGA core density. Each family member contains many peripherals, including flash memory blocks, an analog-to-digital-converter (ADC), high-drive outputs, both RC and crystal oscillators, and a real-time counter (RTC). This provides the user with a high level of flexibility and integration to support a wide variety of mixed signal applications. The flash memory block capacity ranges from 2 Mbits to 8 Mbits. The integrated 12-bit ADC supports up to 30 independently configurable input channels.

# 2 – Device Architecture

# **Fusion Stack Architecture**

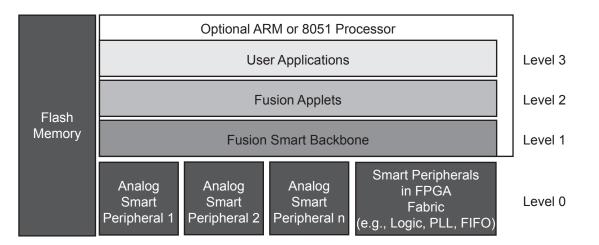

To manage the unprecedented level of integration in Fusion devices, Microsemi developed the Fusion technology stack (Figure 2-1). This layered model offers a flexible design environment, enabling design at very high and very low levels of abstraction. Fusion peripherals include hard analog IP and hard and soft digital IP. Peripherals communicate across the FPGA fabric via a layer of soft gates—the Fusion backbone. Much more than a common bus interface, this Fusion backbone integrates a micro-sequencer within the FPGA fabric and configures the individual peripherals and supports low-level processing of peripheral data. Fusion applets are application building blocks that can control and respond to peripherals and other system signals. Applets can be rapidly combined to create large applications. The technology is scalable across devices, families, design types, and user expertise, and supports a well-defined interface for external IP and tool integration.

At the lowest level, Level 0, are Fusion peripherals. These are configurable functional blocks that can be hardwired structures such as a PLL or analog input channel, or soft (FPGA gate) blocks such as a UART or two-wire serial interface. The Fusion peripherals are configurable and support a standard interface to facilitate communication and implementation.

Connecting and controlling access to the peripherals is the Fusion backbone, Level 1. The backbone is a soft-gate structure, scalable to any number of peripherals. The backbone is a bus and much more; it manages peripheral configuration to ensure proper operation. Leveraging the common peripheral interface and a low-level state machine, the backbone efficiently offloads peripheral management from the system design. The backbone can set and clear flags based upon peripheral behavior and can define performance criteria. The flexibility of the stack enables a designer to configure the silicon, directly bypassing the backbone if that level of control is desired.

One step up from the backbone is the Fusion applet, Level 2. The applet is an application building block that implements a specific function in FPGA gates. It can react to stimuli and board-level events coming through the backbone or from other sources, and responds to these stimuli by accessing and manipulating peripherals via the backbone or initiating some other action. An applet controls or responds to the peripheral(s). Applets can be easily imported or exported from the design environment. The applet structure is open and well-defined, enabling users to import applets from Microsemi, system developers, third parties, and user groups.

Note: Levels 1, 2, and 3 are implemented in FPGA logic gates.

Figure 2-1 • Fusion Architecture Stack

The system application, Level 3, is the larger user application that utilizes one or more applets. Designing at the highest level of abstraction supported by the Fusion technology stack, the application can be easily created in FPGA gates by importing and configuring multiple applets.

In fact, in some cases an entire FPGA system design can be created without any HDL coding.

An optional MCU enables a combination of software and HDL-based design methodologies. The MCU can be on-chip or off-chip as system requirements dictate. System portioning is very flexible, allowing the MCU to reside above the applets or to absorb applets, or applets and backbone, if desired.

The Fusion technology stack enables a very flexible design environment. Users can engage in design across a continuum of abstraction from very low to very high.

## **Core Architecture**

## VersaTile

Based upon successful ProASIC3/E logic architecture, Fusion devices provide granularity comparable to gate arrays. The Fusion device core consists of a sea-of-VersaTiles architecture.

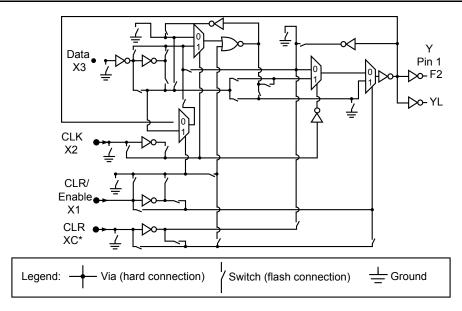

As illustrated in Figure 2-2, there are four inputs in a logic VersaTile cell, and each VersaTile can be configured using the appropriate flash switch connections:

- Any 3-input logic function

- Latch with clear or set

- · D-flip-flop with clear or set

- Enable D-flip-flop with clear or set (on a 4th input)

VersaTiles can flexibly map the logic and sequential gates of a design. The inputs of the VersaTile can be inverted (allowing bubble pushing), and the output of the tile can connect to high-speed, very-long-line routing resources. VersaTiles and larger functions are connected with any of the four levels of routing hierarchy.

When the VersaTile is used as an enable D-flip-flop, the SET/CLR signal is supported by a fourth input, which can only be routed to the core cell over the VersaNet (global) network.

The output of the VersaTile is F2 when the connection is to the ultra-fast local lines, or YL when the connection is to the efficient long-line or very-long-line resources (Figure 2-2).

*Note:* \*This input can only be connected to the global clock distribution network.

Figure 2-2 • Fusion Core VersaTile

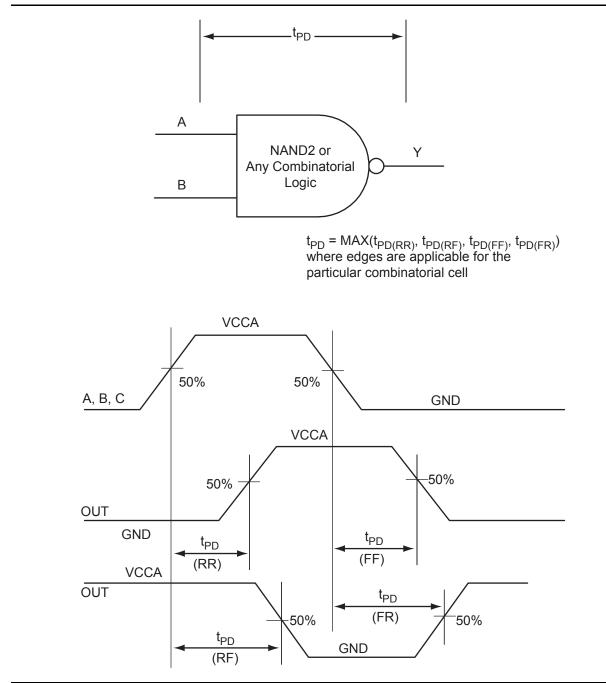

Figure 2-4 • Combinatorial Timing Model and Waveforms

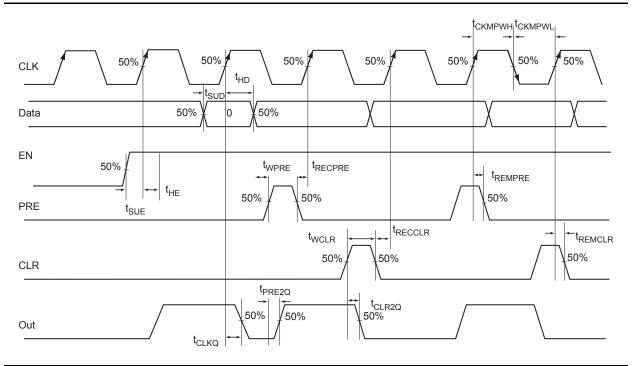

#### Figure 2-6 • Sequential Timing Model and Waveforms

#### Sequential Timing Characteristics

# Table 2-2 • Register Delays<br/>Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter           | Description                                                   | -2   | -1   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 0.55 | 0.63 | 0.74 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 0.43 | 0.49 | 0.57 | ns    |

| t <sub>HD</sub>     | Data Hold Time for the Core Register                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 0.45 | 0.52 | 0.61 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.40 | 0.45 | 0.53 | ns    |

| t <sub>PRE2Q</sub>  | Asynchronous Preset-to-Q of the Core Register                 | 0.40 | 0.45 | 0.53 | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width High for the Core Register          | 0.32 | 0.37 | 0.43 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width Low for the Core Register           | 0.36 | 0.41 | 0.48 | ns    |

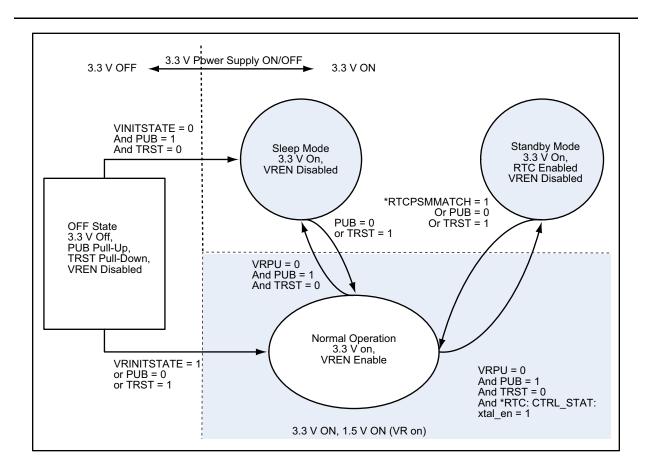

#### Figure 2-31 • State Diagram for All Different Power Modes

When TRST is 1 or PUB is 0, the 1.5 V voltage regulator is always ON, putting the Fusion device in normal operation at all times. Therefore, when the JTAG port is not in reset, the Fusion device cannot enter sleep mode or standby mode.

To enter standby mode, the Fusion device must first power-up into normal operation. The RTC is enabled through the RTC Control/Status Register described in the "Real-Time Counter (part of AB macro)" section on page 2-33. A match value corresponding to the wake-up time is loaded into the Match Register. The 1.5 V voltage regulator is disabled by setting VRPU to 0 to allow the Fusion device to enter standby mode, when the 1.5 V supply is off but the RTC remains on.

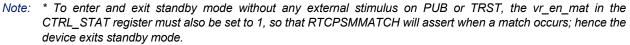

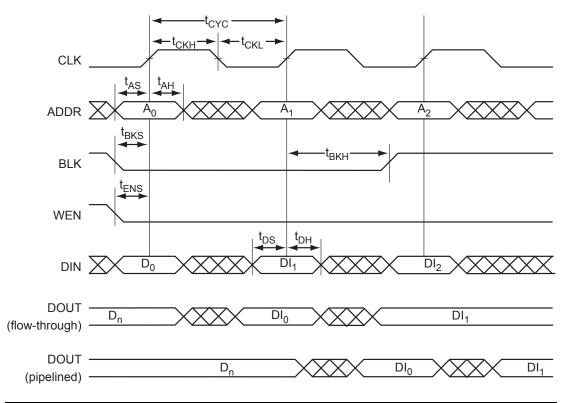

Figure 2-52 • RAM Write, Output Retained. Applicable to both RAM4K9 and RAM512x18.

Figure 2-53 • RAM Write, Output as Write Data (WMODE = 1). Applicable to RAM4K9 Only.

Device Architecture

### Table 2-36 • Analog Block Pin Description (continued)

| Signal Name                                         | Number<br>of Bits | Direction | Function                                                  | Location of<br>Details |

|-----------------------------------------------------|-------------------|-----------|-----------------------------------------------------------|------------------------|

| GDON0 to GDON9                                      | 10                | Input     | Control to power MOS – 1 per quad                         | Analog Quad            |

| TMSTB0 to TMSTB9                                    | 10                | Input     | Temperature monitor strobe – 1 per quad; active high      | Analog Quad            |

| DAVOUT0, DACOUT0, DATOUT0<br>to                     | 30                | Output    | Digital outputs – 3 per quad                              | Analog Quad            |

| DAVOUT9, DACOUT9, DATOUT9                           |                   |           |                                                           |                        |

| DENAV0, DENAC0, DENAT0 to<br>DENAV9, DENAC9, DENAT9 | 30                | Input     | Digital input enables – 3 per quad                        | Analog Quad            |

| AV0                                                 | 1                 | Input     | Analog Quad 0                                             | Analog Quad            |

| AC0                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AG0                                                 | 1                 | Output    |                                                           | Analog Quad            |

| AT0                                                 | 1                 | Input     |                                                           | Analog Quad            |

| ATRETURN01                                          | 1                 | Input     | Temperature monitor return shared by Analog Quads 0 and 1 | Analog Quad            |

| AV1                                                 | 1                 | Input     | Analog Quad 1                                             | Analog Quad            |

| AC1                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AG1                                                 | 1                 | Output    |                                                           | Analog Quad            |

| AT1                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AV2                                                 | 1                 | Input     | Analog Quad 2                                             | Analog Quad            |

| AC2                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AG2                                                 | 1                 | Output    |                                                           | Analog Quad            |

| AT2                                                 | 1                 | Input     |                                                           | Analog Quad            |

| ATRETURN23                                          | 1                 | Input     | Temperature monitor return shared by Analog Quads 2 and 3 | Analog Quad            |

| AV3                                                 | 1                 | Input     | Analog Quad 3                                             | Analog Quad            |

| AC3                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AG3                                                 | 1                 | Output    |                                                           | Analog Quad            |

| AT3                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AV4                                                 | 1                 | Input     | Analog Quad 4                                             | Analog Quad            |

| AC4                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AG4                                                 | 1                 | Output    |                                                           | Analog Quad            |

| AT4                                                 | 1                 | Input     |                                                           | Analog Quad            |

| ATRETURN45                                          | 1                 | Input     | Temperature monitor return shared by Analog Quads 4 and 5 | Analog Quad            |

| AV5                                                 | 1                 | Input     | Analog Quad 5                                             | Analog Quad            |

| AC5                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AG5                                                 | 1                 | Output    |                                                           | Analog Quad            |

| AT5                                                 | 1                 | Input     |                                                           | Analog Quad            |

| AV6                                                 | 1                 | Input     | Analog Quad 6                                             | Analog Quad            |

| AC6                                                 | 1                 | Input     | 1                                                         | Analog Quad            |

| Signal Name     | Number<br>of Bits | Direction | Function                                                  | Location of<br>Details |

|-----------------|-------------------|-----------|-----------------------------------------------------------|------------------------|

| AG6             | 1                 | Output    |                                                           | Analog Quad            |

| AT6             | 1                 | Input     |                                                           | Analog Quad            |

| ATRETURN67      | 1                 | Input     | Temperature monitor return shared by Analog Quads 6 and 7 | Analog Quad            |

| AV7             | 1                 | Input     | Analog Quad 7                                             | Analog Quad            |

| AC7             | 1                 | Input     |                                                           | Analog Quad            |

| AG7             | 1                 | Output    |                                                           | Analog Quad            |

| AT7             | 1                 | Input     |                                                           | Analog Quad            |

| AV8             | 1                 | Input     | Analog Quad 8                                             | Analog Quad            |

| AC8             | 1                 | Input     |                                                           | Analog Quad            |

| AG8             | 1                 | Output    |                                                           | Analog Quad            |

| AT8             | 1                 | Input     |                                                           | Analog Quad            |

| ATRETURN89      | 1                 | Input     | Temperature monitor return shared by Analog Quads 8 and 9 | Analog Quad            |

| AV9             | 1                 | Input     | Analog Quad 9                                             | Analog Quad            |

| AC9             | 1                 | Input     |                                                           | Analog Quad            |

| AG9             | 1                 | Output    |                                                           | Analog Quad            |

| AT9             | 1                 | Input     |                                                           | Analog Quad            |

| RTCMATCH        | 1                 | Output    | МАТСН                                                     | RTC                    |

| RTCPSMMATCH     | 1                 | Output    | MATCH connected to VRPSM                                  | RTC                    |

| RTCXTLMODE[1:0] | 2                 | Output    | Drives XTLOSC RTCMODE[1:0] pins                           | RTC                    |

| RTCXTLSEL       | 1                 | Output    | Drives XTLOSC MODESEL pin                                 | RTC                    |

| RTCCLK          | 1                 | Input     | RTC clock input                                           | RTC                    |

#### Table 2-36 • Analog Block Pin Description (continued)

## **Analog Quad**

With the Fusion family, Microsemi introduces the Analog Quad, shown in Figure 2-65 on page 2-81, as the basic analog I/O structure. The Analog Quad is a four-channel system used to precondition a set of analog signals before sending it to the ADC for conversion into a digital signal. To maximize the usefulness of the Analog Quad, the analog input signals can also be configured as LVTTL digital input signals. The Analog Quad is divided into four sections.

The first section is called the Voltage Monitor Block, and its input pin is named AV. It contains a twochannel analog multiplexer that allows an incoming analog signal to be routed directly to the ADC or allows the signal to be routed to a prescaler circuit before being sent to the ADC. The prescaler can be configured to accept analog signals between -12 V and 0 or between 0 and +12 V. The prescaler circuit scales the voltage applied to the ADC input pad such that it is compatible with the ADC input voltage range. The AV pin can also be used as a digital input pin.

The second section of the Analog Quad is called the Current Monitor Block. Its input pin is named AC. The Current Monitor Block contains all the same functions as the Voltage Monitor Block with one addition, which is a current monitoring function. A small external current sensing resistor (typically less than 1  $\Omega$ ) is connected between the AV and AC pins and is in series with a power source. The Current Monitor Block contains a current monitor circuit that converts the current through the external resistor to a voltage that can then be read using the ADC.

#### Table 2-68 • I/O Bank Support by Device

| I/O Bank     | AFS090 | AFS250 | AFS600 | AFS1500 |

|--------------|--------|--------|--------|---------|

| Standard I/O | Ν      | Ν      | -      | -       |

| Advanced I/O | E, W   | E, W   | E, W   | E, W    |

| Pro I/O      | -      | -      | Ν      | N       |

| Analog Quad  | S      | S      | S      | S       |

*Note: E* = *East side of the device*

W = West side of the device

*N* = *North* side of the device

S = South side of the device

#### Table 2-69 • Fusion VCCI Voltages and Compatible Standards

| VCCI (typical) | Compatible Standards                                                                              |

|----------------|---------------------------------------------------------------------------------------------------|

| 3.3 V          | LVTTL/LVCMOS 3.3, PCI 3.3, SSTL3 (Class I and II),* GTL+ 3.3, GTL 3.3,* LVPECL                    |

| 2.5 V          | LVCMOS 2.5, LVCMOS 2.5/5.0, SSTL2 (Class I and II),* GTL+ 2.5,* GTL 2.5,* LVDS, BLVDS, M-<br>LVDS |

| 1.8 V          | LVCMOS 1.8                                                                                        |

| 1.5 V          | LVCMOS 1.5, HSTL (Class I),* HSTL (Class II)*                                                     |

*Note:* \*I/O standard supported by Pro I/O banks.

#### Table 2-70 • Fusion VREF Voltages and Compatible Standards\*

| VREF (typical) | Compatible Standards            |

|----------------|---------------------------------|

| 1.5 V          | SSTL3 (Class I and II)          |

| 1.25 V         | SSTL2 (Class I and II)          |

| 1.0 V          | GTL+ 2.5, GTL+ 3.3              |

| 0.8 V          | GTL 2.5, GTL 3.3                |

| 0.75 V         | HSTL (Class I), HSTL (Class II) |

*Note:* \*I/O standards supported by Pro I/O banks.

Temporary overshoots are allowed according to Table 3-4 on page 3-4.

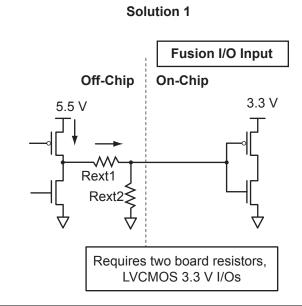

Figure 2-103 • Solution 1

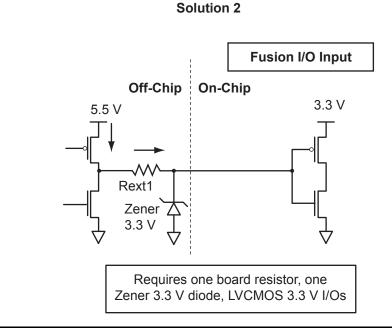

### Solution 2

The board-level design must ensure that the reflected waveform at the pad does not exceed limits provided in Table 3-4 on page 3-4. This is a long-term reliability requirement.

This scheme will also work for a 3.3 V PCI/PCI-X configuration, but the internal diode should not be used for clamping, and the voltage must be limited by the external resistors and Zener, as shown in Figure 2-104. Relying on the diode clamping would create an excessive pad DC voltage of 3.3 V + 0.7 V = 4 V.

Figure 2-104 • Solution 2

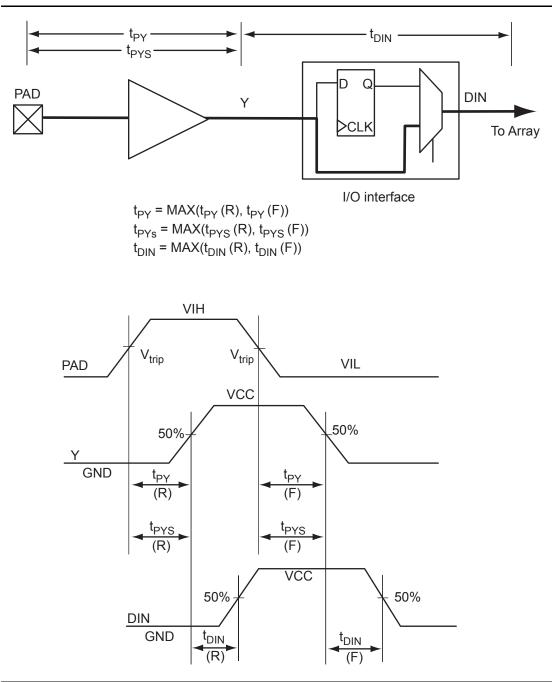

*Figure 2-116* • Input Buffer Timing Model and Delays (example)

#### Table 2-106 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Appl | icable | e to | Advanced | I/Os |

|------|--------|------|----------|------|

|      |        |      |          |      |

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.66              | 10.26           | 0.04             | 1.20            | 0.43              | 10.45           | 8.90            | 2.64            | 2.46            | 12.68            | 11.13            | ns    |

|                   | -1             | 0.56              | 8.72            | 0.04             | 1.02            | 0.36              | 8.89            | 7.57            | 2.25            | 2.09            | 10.79            | 9.47             | ns    |

|                   | -2             | 0.49              | 7.66            | 0.03             | 0.90            | 0.32              | 7.80            | 6.64            | 1.98            | 1.83            | 9.47             | 8.31             | ns    |

| 8 mA              | Std.           | 0.66              | 7.27            | 0.04             | 1.20            | 0.43              | 7.41            | 6.28            | 2.98            | 3.04            | 9.65             | 8.52             | ns    |

|                   | -1             | 0.56              | 6.19            | 0.04             | 1.02            | 0.36              | 6.30            | 5.35            | 2.54            | 2.59            | 8.20             | 7.25             | ns    |

|                   | -2             | 0.49              | 5.43            | 0.03             | 0.90            | 0.32              | 5.53            | 4.69            | 2.23            | 2.27            | 7.20             | 6.36             | ns    |

| 12 mA             | Std.           | 0.66              | 5.58            | 0.04             | 1.20            | 0.43              | 5.68            | 4.87            | 3.21            | 3.42            | 7.92             | 7.11             | ns    |

|                   | -1             | 0.56              | 4.75            | 0.04             | 1.02            | 0.36              | 4.84            | 4.14            | 2.73            | 2.91            | 6.74             | 6.05             | ns    |

|                   | -2             | 0.49              | 4.17            | 0.03             | 0.90            | 0.32              | 4.24            | 3.64            | 2.39            | 2.55            | 5.91             | 5.31             | ns    |

| 16 mA             | Std.           | 0.66              | 5.21            | 0.04             | 1.20            | 0.43              | 5.30            | 4.56            | 3.26            | 3.51            | 7.54             | 6.80             | ns    |

|                   | -1             | 0.56              | 4.43            | 0.04             | 1.02            | 0.36              | 4.51            | 3.88            | 2.77            | 2.99            | 6.41             | 5.79             | ns    |

|                   | -2             | 0.49              | 3.89            | 0.03             | 0.90            | 0.32              | 3.96            | 3.41            | 2.43            | 2.62            | 5.63             | 5.08             | ns    |

| 24 mA             | Std.           | 0.66              | 4.85            | 0.04             | 1.20            | 0.43              | 4.94            | 4.54            | 3.32            | 3.88            | 7.18             | 6.78             | ns    |

|                   | -1             | 0.56              | 4.13            | 0.04             | 1.02            | 0.36              | 4.20            | 3.87            | 2.82            | 3.30            | 6.10             | 5.77             | ns    |

|                   | -2             | 0.49              | 3.62            | 0.03             | 0.90            | 0.32              | 3.69            | 3.39            | 2.48            | 2.90            | 5.36             | 5.06             | ns    |

Device Architecture

#### 3.3 V GTL+

Gunning Transceiver Logic Plus is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 3.3 V.

Table 2-144 • Minimum and Maximum DC Input and Output Levels

| 3.3 V GTL+        | VIL       |            | VIH        |           | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL¹            | IIH <sup>2</sup> |

|-------------------|-----------|------------|------------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-----------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 35 mA             | -0.3      | VREF – 0.1 | VREF + 0.1 | 3.6       | 0.6       | -         | 35  | 35 | 181                     | 268                     | 10              | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

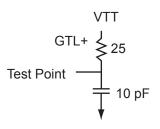

#### Figure 2-126 • AC Loading

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.1    | VREF + 0.1     | 1.0                  | 1.0             | 1.5            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

Table 2-146 • 3.3 V GTL+

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V, VREF = 1.0 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.06            | 0.04             | 1.59            | 0.43              | 2.09            | 2.06            |                 |                 | 4.33             | 4.29             | ns    |

| -1             | 0.56              | 1.75            | 0.04             | 1.35            | 0.36              | 1.78            | 1.75            |                 |                 | 3.68             | 3.65             | ns    |

| -2             | 0.49              | 1.53            | 0.03             | 1.19            | 0.32              | 1.56            | 1.53            |                 |                 | 3.23             | 3.20             | ns    |

#### 2.5 V GTL+

Gunning Transceiver Logic Plus is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 2.5 V.

Table 2-147 • Minimum and Maximum DC Input and Output Levels

| 2.5 V<br>GTL+     |           | VIL        | VIH        |           | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|-----------|------------|------------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 33 mA             | -0.3      | VREF – 0.1 | VREF + 0.1 | 3.6       | 0.6       | -         | 33  | 33 | 124                     | 169                     | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

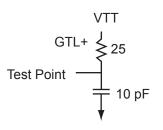

#### Figure 2-127 • AC Loading

#### Table 2-148 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.1    | VREF + 0.1     | 1.0                  | 1.0             | 1.5            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

```

Table 2-149 • 2.5 V GTL+

```

# Commercial Temperature Range Conditions: $T_J$ = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V, VREF = 1.0 V

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.21            | 0.04             | 1.51            | 0.43              | 2.25            | 2.10            |                 |                 | 4.48             | 4.34             | ns    |

| -1             | 0.56              | 1.88            | 0.04             | 1.29            | 0.36              | 1.91            | 1.79            |                 |                 | 3.81             | 3.69             | ns    |

| -2             | 0.49              | 1.65            | 0.03             | 1.13            | 0.32              | 1.68            | 1.57            |                 |                 | 3.35             | 4.34             | ns    |

### RAM Dynamic Contribution—P<sub>MEMORY</sub>

#### **Operating Mode**

$P_{MEMORY} = (N_{BLOCKS} * PAC11 * \beta_2 * F_{READ-CLOCK}) + (N_{BLOCKS} * PAC12 * \beta_3 * F_{WRITE-CLOCK})$  $N_{BLOCKS} \text{ is the number of RAM blocks used in the design.}$

F<sub>READ-CLOCK</sub> is the memory read clock frequency.

$\beta_2$  is the RAM enable rate for read operations—guidelines are provided in Table 3-17 on page 3-27.

$\beta_3$  the RAM enable rate for write operations—guidelines are provided in Table 3-17 on page 3-27.

$\mathsf{F}_{\mathsf{WRITE}\text{-}\mathsf{CLOCK}}$  is the memory write clock frequency.

#### Standby Mode and Sleep Mode

P<sub>MEMORY</sub> = 0 W

#### PLL/CCC Dynamic Contribution—PPLL

#### **Operating Mode**

P<sub>PLL</sub> = PAC13 \* F<sub>CLKOUT</sub>

F<sub>CLKIN</sub> is the input clock frequency.

F<sub>CLKOUT</sub> is the output clock frequency.<sup>1</sup>

#### Standby Mode and Sleep Mode

$P_{PLL} = 0 W$

#### Nonvolatile Memory Dynamic Contribution—P<sub>NVM</sub>

#### **Operating Mode**

The NVM dynamic power consumption is a piecewise linear function of frequency.

$P_{NVM} = N_{NVM-BLOCKS} * \beta_4 * PAC15 * F_{READ-NVM}$  when  $F_{READ-NVM} \le 33$  MHz,

$P_{NVM} = N_{NVM-BLOCKS} * \beta_4 * (PAC16 + PAC17 * F_{READ-NVM} \text{ when } F_{READ-NVM} > 33 \text{ MHz}$

N<sub>NVM-BLOCKS</sub> is the number of NVM blocks used in the design (2 inAFS600).

$\beta_4$  is the NVM enable rate for read operations. Default is 0 (NVM mainly in idle state). F<sub>READ-NVM</sub> is the NVM read clock frequency.

#### Standby Mode and Sleep Mode

P<sub>NVM</sub> = 0 W

#### Crystal Oscillator Dynamic Contribution—P<sub>XTL-OSC</sub>

#### **Operating Mode**

$P_{XTL-OSC} = PAC18$

#### Standby Mode

$P_{XTL-OSC} = PAC18$

#### Sleep Mode

$P_{XTL-OSC} = 0 W$

The PLL dynamic contribution depends on the input clock frequency, the number of output clock signals generated by the PLL, and the frequency of each output clock. If a PLL is used to generate more than one output clock, include each output clock in the formula output clock by adding its corresponding contribution (P<sub>AC14</sub> \* F<sub>CLKOUT</sub> product) to the total PLL contribution.

| FG256      |                 |                 |                 |                  |  |  |

|------------|-----------------|-----------------|-----------------|------------------|--|--|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |  |  |

| E13        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |  |  |

| E14        | GCC2/IO33NDB1V0 | IO42NDB1V0      | IO32NDB2V0      | IO46NDB2V0       |  |  |

| E15        | GCB2/IO33PDB1V0 | GBC2/IO42PDB1V0 | GBC2/IO32PDB2V0 | GBC2/IO46PDB2V0  |  |  |

| E16        | GND             | GND             | GND             | GND              |  |  |

| F1         | NC              | NC              | IO79NDB4V0      | IO111NDB4V0      |  |  |

| F2         | NC              | NC              | IO79PDB4V0      | IO111PDB4V0      |  |  |

| F3         | GFB1/IO48PPB3V0 | IO72NDB3V0      | IO76NDB4V0      | IO112NDB4V0      |  |  |

| F4         | GFC0/IO49NDB3V0 | IO72PDB3V0      | IO76PDB4V0      | IO112PDB4V0      |  |  |

| F5         | NC              | NC              | IO82PSB4V0      | IO120PSB4V0      |  |  |

| F6         | GFC1/IO49PDB3V0 | GAC2/IO74PPB3V0 | GAC2/IO83PPB4V0 | GAC2/IO123PPB4V0 |  |  |

| F7         | NC              | IO09RSB0V0      | IO04PPB0V0      | IO05PPB0V1       |  |  |

| F8         | NC              | IO19RSB0V0      | IO08NDB0V1      | IO11NDB0V1       |  |  |

| F9         | NC              | NC              | IO20PDB1V0      | IO27PDB1V1       |  |  |

| F10        | NC              | IO29RSB0V0      | IO23NDB1V1      | IO37NDB1V2       |  |  |

| F11        | NC              | IO43NDB1V0      | IO36NDB2V0      | IO50NDB2V0       |  |  |

| F12        | NC              | IO43PDB1V0      | IO36PDB2V0      | IO50PDB2V0       |  |  |

| F13        | NC              | IO44NDB1V0      | IO39NDB2V0      | IO59NDB2V0       |  |  |

| F14        | NC              | GCA2/IO44PDB1V0 | GCA2/IO39PDB2V0 | GCA2/IO59PDB2V0  |  |  |

| F15        | GCC1/IO34PDB1V0 | GCB2/IO45PDB1V0 | GCB2/IO40PDB2V0 | GCB2/IO60PDB2V0  |  |  |

| F16        | GCC0/IO34NDB1V0 | IO45NDB1V0      | IO40NDB2V0      | IO60NDB2V0       |  |  |

| G1         | GEC0/IO46NPB3V0 | IO70NPB3V0      | IO74NPB4V0      | IO109NPB4V0      |  |  |

| G2         | VCCIB3          | VCCIB3          | VCCIB4          | VCCIB4           |  |  |

| G3         | GEC1/IO46PPB3V0 | GFB2/IO70PPB3V0 | GFB2/IO74PPB4V0 | GFB2/IO109PPB4V0 |  |  |

| G4         | GFA1/IO47PDB3V0 | GFA2/IO71PDB3V0 | GFA2/IO75PDB4V0 | GFA2/IO110PDB4V0 |  |  |

| G5         | GND             | GND             | GND             | GND              |  |  |

| G6         | GFA0/IO47NDB3V0 | IO71NDB3V0      | IO75NDB4V0      | IO110NDB4V0      |  |  |

| G7         | GND             | GND             | GND             | GND              |  |  |

| G8         | VCC             | VCC             | VCC             | VCC              |  |  |

| G9         | GND             | GND             | GND             | GND              |  |  |

| G10        | VCC             | VCC             | VCC             | VCC              |  |  |

| G11        | GDA1/IO37NDB1V0 | GCC0/IO47NDB1V0 | GCC0/IO43NDB2V0 | GCC0/IO62NDB2V0  |  |  |

| G12        | GND             | GND             | GND             | GND              |  |  |

| G13        | IO37PDB1V0      | GCC1/IO47PDB1V0 | GCC1/IO43PDB2V0 | GCC1/IO62PDB2V0  |  |  |

| G14        | GCB0/IO35NPB1V0 | IO46NPB1V0      | IO41NPB2V0      | IO61NPB2V0       |  |  |

| G15        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |  |  |

| G16        | GCB1/IO35PPB1V0 | GCC2/IO46PPB1V0 | GCC2/IO41PPB2V0 | GCC2/IO61PPB2V0  |  |  |

| H1         | GEB1/IO45PDB3V0 | GFC2/IO69PDB3V0 | GFC2/IO73PDB4V0 | GFC2/IO108PDB4V0 |  |  |

| H2         | GEB0/IO45NDB3V0 | IO69NDB3V0      | IO73NDB4V0      | IO108NDB4V0      |  |  |

Package Pin Assignments

|               | FG484           |                  | FG484         |                 |                  |  |

|---------------|-----------------|------------------|---------------|-----------------|------------------|--|

| Pin<br>Number | AFS600 Function | AFS1500 Function | Pin<br>Number | AFS600 Function | AFS1500 Function |  |

| A1            | GND             | GND              | AA14          | AG7             | AG7              |  |

| A2            | VCC             | NC               | AA15          | AG8             | AG8              |  |

| A3            | GAA1/IO01PDB0V0 | GAA1/IO01PDB0V0  | AA16          | GNDA            | GNDA             |  |

| A4            | GAB0/IO02NDB0V0 | GAB0/IO02NDB0V0  | AA17          | AG9             | AG9              |  |

| A5            | GAB1/IO02PDB0V0 | GAB1/IO02PDB0V0  | AA18          | VAREF           | VAREF            |  |

| A6            | IO07NDB0V1      | IO07NDB0V1       | AA19          | VCCIB2          | VCCIB2           |  |

| A7            | IO07PDB0V1      | IO07PDB0V1       | AA20          | PTEM            | PTEM             |  |

| A8            | IO10PDB0V1      | IO09PDB0V1       | AA21          | GND             | GND              |  |

| A9            | IO14NDB0V1      | IO13NDB0V2       | AA22          | VCC             | NC               |  |

| A10           | IO14PDB0V1      | IO13PDB0V2       | AB1           | GND             | GND              |  |

| A11           | IO17PDB1V0      | IO24PDB1V0       | AB2           | VCC             | NC               |  |

| A12           | IO18PDB1V0      | IO26PDB1V0       | AB3           | NC              | IO94NSB4V0       |  |

| A13           | IO19NDB1V0      | IO27NDB1V1       | AB4           | GND             | GND              |  |

| A14           | IO19PDB1V0      | IO27PDB1V1       | AB5           | VCC33N          | VCC33N           |  |

| A15           | IO24NDB1V1      | IO35NDB1V2       | AB6           | AT0             | AT0              |  |

| A16           | IO24PDB1V1      | IO35PDB1V2       | AB7           | ATRTN0          | ATRTN0           |  |

| A17           | GBC0/IO26NDB1V1 | GBC0/IO40NDB1V2  | AB8           | AT1             | AT1              |  |

| A18           | GBA0/IO28NDB1V1 | GBA0/IO42NDB1V2  | AB9           | AT2             | AT2              |  |

| A19           | IO29NDB1V1      | IO43NDB1V2       | AB10          | ATRTN1          | ATRTN1           |  |

| A20           | IO29PDB1V1      | IO43PDB1V2       | AB11          | AT3             | AT3              |  |

| A21           | VCC             | NC               | AB12          | AT6             | AT6              |  |

| A22           | GND             | GND              | AB13          | ATRTN3          | ATRTN3           |  |

| AA1           | VCC             | NC               | AB14          | AT7             | AT7              |  |

| AA2           | GND             | GND              | AB15          | AT8             | AT8              |  |

| AA3           | VCCIB4          | VCCIB4           | AB16          | ATRTN4          | ATRTN4           |  |

| AA4           | VCCIB4          | VCCIB4           | AB17          | AT9             | AT9              |  |

| AA5           | PCAP            | PCAP             | AB18          | VCC33A          | VCC33A           |  |

| AA6           | AG0             | AG0              | AB19          | GND             | GND              |  |

| AA7           | GNDA            | GNDA             | AB20          | NC              | IO76NPB2V0       |  |

| AA8           | AG1             | AG1              | AB21          | VCC             | NC               |  |

| AA9           | AG2             | AG2              | AB22          | GND             | GND              |  |

| AA10          | GNDA            | GNDA             | B1            | VCC             | NC               |  |

| AA11          | AG3             | AG3              | B2            | GND             | GND              |  |

| AA12          | AG6             | AG6              | B3            | GAA0/IO01NDB0V0 | GAA0/IO01NDB0V0  |  |

| AA13          | GNDA            | GNDA             | B4            | GND             | GND              |  |

|               | FG484           |                  |               | FG484           |                  |

|---------------|-----------------|------------------|---------------|-----------------|------------------|

| Pin<br>Number | AFS600 Function | AFS1500 Function | Pin<br>Number | AFS600 Function | AFS1500 Function |

| H13           | GND             | GND              | K4            | IO75NDB4V0      | IO110NDB4V0      |

| H14           | VCCIB1          | VCCIB1           | K5            | GND             | GND              |

| H15           | GND             | GND              | K6            | NC              | IO104NDB4V0      |

| H16           | GND             | GND              | K7            | NC              | IO111NDB4V0      |

| H17           | NC              | IO53NDB2V0       | K8            | GND             | GND              |

| H18           | IO38PDB2V0      | IO57PDB2V0       | K9            | VCC             | VCC              |

| H19           | GCA2/IO39PDB2V0 | GCA2/IO59PDB2V0  | K10           | GND             | GND              |

| H20           | VCCIB2          | VCCIB2           | K11           | VCC             | VCC              |

| H21           | IO37NDB2V0      | IO54NDB2V0       | K12           | GND             | GND              |

| H22           | IO37PDB2V0      | IO54PDB2V0       | K13           | VCC             | VCC              |

| J1            | NC              | IO112PPB4V0      | K14           | GND             | GND              |

| J2            | IO76NDB4V0      | IO113NDB4V0      | K15           | GND             | GND              |

| J3            | GFB2/IO74PDB4V0 | GFB2/IO109PDB4V0 | K16           | IO40NDB2V0      | IO60NDB2V0       |

| J4            | GFA2/IO75PDB4V0 | GFA2/IO110PDB4V0 | K17           | NC              | IO58PDB2V0       |

| J5            | NC              | IO112NPB4V0      | K18           | GND             | GND              |

| J6            | NC              | IO104PDB4V0      | K19           | NC              | IO68NPB2V0       |

| J7            | NC              | IO111PDB4V0      | K20           | IO41NDB2V0      | IO61NDB2V0       |

| J8            | VCCIB4          | VCCIB4           | K21           | GND             | GND              |

| J9            | GND             | GND              | K22           | IO42NDB2V0      | IO56NDB2V0       |

| J10           | VCC             | VCC              | L1            | IO73NDB4V0      | IO108NDB4V0      |

| J11           | GND             | GND              | L2            | VCCOSC          | VCCOSC           |

| J12           | VCC             | VCC              | L3            | VCCIB4          | VCCIB4           |

| J13           | GND             | GND              | L4            | XTAL2           | XTAL2            |

| J14           | VCC             | VCC              | L5            | GFC1/IO72PDB4V0 | GFC1/IO107PDB4V0 |

| J15           | VCCIB2          | VCCIB2           | L6            | VCCIB4          | VCCIB4           |

| J16           | GCB2/IO40PDB2V0 | GCB2/IO60PDB2V0  | L7            | GFB1/IO71PDB4V0 | GFB1/IO106PDB4V0 |

| J17           | NC              | IO58NDB2V0       | L8            | VCCIB4          | VCCIB4           |

| J18           | IO38NDB2V0      | IO57NDB2V0       | L9            | GND             | GND              |

| J19           | IO39NDB2V0      | IO59NDB2V0       | L10           | VCC             | VCC              |

| J20           | GCC2/IO41PDB2V0 | GCC2/IO61PDB2V0  | L11           | GND             | GND              |

| J21           | NC              | IO55PSB2V0       | L12           | VCC             | VCC              |

| J22           | IO42PDB2V0      | IO56PDB2V0       | L13           | GND             | GND              |

| K1            | GFC2/IO73PDB4V0 | GFC2/IO108PDB4V0 | L14           | VCC             | VCC              |

| K2            | GND             | GND              | L15           | VCCIB2          | VCCIB2           |

| K3            | IO74NDB4V0      | IO109NDB4V0      | L16           | IO48PDB2V0      | IO70PDB2V0       |

Datasheet Information

| Revision                        | Changes                                                                                                                                                                                                                                                                                                                                                                           | Page  |  |  |  |  |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|--|

| v2.0, Revision 1<br>(July 2009) | The MicroBlade and Fusion datasheets have been combined. Pigeon Point<br>information is new.<br>CoreMP7 support was removed since it is no longer offered.<br>–F was removed from the datasheet since it is no longer offered.<br>The operating temperature was changed from ambient to junction to better reflect<br>actual conditions of operations.<br>Commercial: 0°C to 85°C |       |  |  |  |  |  |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                   |       |  |  |  |  |  |

|                                 | -F was removed from the datasheet since it is no longer offered.                                                                                                                                                                                                                                                                                                                  |       |  |  |  |  |  |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                   |       |  |  |  |  |  |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                   |       |  |  |  |  |  |

|                                 | Industrial: -40°C to 100°C                                                                                                                                                                                                                                                                                                                                                        |       |  |  |  |  |  |

|                                 | The version number category was changed from Preliminary to Production, which means the datasheet contains information based on final characterization. The version number changed from Preliminary v1.7 to v2.0.                                                                                                                                                                 |       |  |  |  |  |  |

|                                 | The "Integrated Analog Blocks and Analog I/Os" section was updated to include a reference to the "Analog System Characteristics" section in the <i>Device Architecture</i> chapter of the datasheet, which includes Table 2-46 • Analog Channel Specifications and specific voltage data.                                                                                         | 1-4   |  |  |  |  |  |

|                                 | The phrase "Commercial-Case Conditions" in timing table titles was changed to "Commercial Temperature Range Conditions."                                                                                                                                                                                                                                                          |       |  |  |  |  |  |

|                                 | The "Crystal Oscillator" section was updated significantly. Please review carefully.                                                                                                                                                                                                                                                                                              |       |  |  |  |  |  |

|                                 | The "Real-Time Counter (part of AB macro)" section was updated significantly. Please review carefully.                                                                                                                                                                                                                                                                            |       |  |  |  |  |  |

|                                 | There was a typo in Table 2-19 • Flash Memory Block Pin Names for the ERASEPAGE description; it was the same as DISCARDPAGE. As as a result, the ERASEPAGE description was updated.                                                                                                                                                                                               |       |  |  |  |  |  |

|                                 | The t <sub>FMAXCLKNVM</sub> parameter was updated in Table 2-25 • Flash Memory Block Timing.                                                                                                                                                                                                                                                                                      |       |  |  |  |  |  |

|                                 | Table 2-31 • RAM4K9 and Table 2-32 • RAM512X18 were updated.                                                                                                                                                                                                                                                                                                                      |       |  |  |  |  |  |

|                                 | In Table 2-36 • Analog Block Pin Description, the Function description for PWRDWN was changed from "Comparator power-down if 1" to                                                                                                                                                                                                                                                | 2-78  |  |  |  |  |  |

|                                 | "ADC comparator power-down if 1. When asserted, the ADC will stop functioning,<br>and the digital portion of the analog block will continue operating. This may result in<br>invalid status flags from the analog block. Therefore, Microsemi does not<br>recommend asserting the PWRDWN pin."                                                                                    |       |  |  |  |  |  |

|                                 | Figure 2-75 • Gate Driver Example was updated.                                                                                                                                                                                                                                                                                                                                    | 2-91  |  |  |  |  |  |

|                                 | The "ADC Operation" section was updated. Please review carefully.                                                                                                                                                                                                                                                                                                                 | 2-104 |  |  |  |  |  |

|                                 | Figure 2-92 • Intra-Conversion Timing Diagram and Figure 2-93 • Injected Conversion Timing Diagram are new.                                                                                                                                                                                                                                                                       | 2-113 |  |  |  |  |  |

|                                 | The "Typical Performance Characteristics" section is new.                                                                                                                                                                                                                                                                                                                         | 2-115 |  |  |  |  |  |

|                                 | Table 2-49 • Analog Channel Specifications was significantly updated.                                                                                                                                                                                                                                                                                                             | 2-117 |  |  |  |  |  |

|                                 | Table 2-50 • ADC Characteristics in Direct Input Mode was significantly updated.                                                                                                                                                                                                                                                                                                  | 2-120 |  |  |  |  |  |

|                                 | In Table 2-52 • Calibrated Analog Channel Accuracy 1,2,3, note 2 was updated.                                                                                                                                                                                                                                                                                                     | 2-123 |  |  |  |  |  |

|                                 | In Table 2-53 • Analog Channel Accuracy: Monitoring Standard Positive Voltages,<br>note 1 was updated.                                                                                                                                                                                                                                                                            | 2-124 |  |  |  |  |  |

|                                 | In Table 2-54 • ACM Address Decode Table for Analog Quad, bit 89 was removed.                                                                                                                                                                                                                                                                                                     | 2-126 |  |  |  |  |  |