Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                      |

|--------------------------------|-----------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | -                                                                           |

| Total RAM Bits                 | 276480                                                                      |

| Number of I/O                  | 119                                                                         |

| Number of Gates                | 1500000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                             |

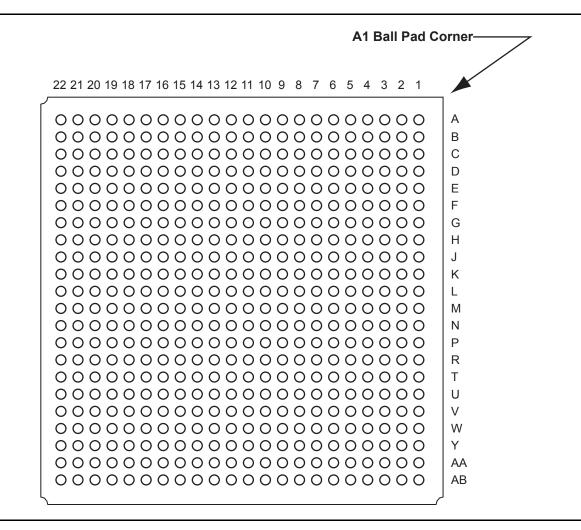

| Package / Case                 | 256-LBGA                                                                    |

| Supplier Device Package        | 256-FPBGA (17x17)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/p1afs1500-2fgg256 |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Global Buffers with No Programmable Delays

The CLKBUF and CLKBUF\_LVPECL/LVDS macros are composite macros that include an I/O macro driving a global buffer, hardwired together (Figure 2-20).

The CLKINT macro provides a global buffer function driven by the FPGA core.

The CLKBUF, CLKBUF\_LVPECL/LVDS, and CLKINT macros are pass-through clock sources and do not use the PLL or provide any programmable delay functionality.

Many specific CLKBUF macros support the wide variety of single-ended and differential I/O standards supported by Fusion devices. The available CLKBUF macros are described in the *IGLOO*, *ProASIC3*, *SmartFusion and Fusion Macro Library Guide*.

| Clock Source                          | Clock Source |      |     |  |  |  |  |  |

|---------------------------------------|--------------|------|-----|--|--|--|--|--|

|                                       |              |      | GLA |  |  |  |  |  |

| CLKBUF_LVDS/LVPECL Macro CLKBUF Macro | CLKINT Macro |      | or  |  |  |  |  |  |

|                                       |              | None | GLB |  |  |  |  |  |

|                                       | A Y          |      | or  |  |  |  |  |  |

|                                       |              |      | GLC |  |  |  |  |  |

Figure 2-20 • Global Buffers with No Programmable Delay

## Global Buffers with Programmable Delay

The CLKDLY macro is a pass-through clock source that does not use the PLL, but provides the ability to delay the clock input using a programmable delay (Figure 2-21 on page 2-25). The CLKDLY macro takes the selected clock input and adds a user-defined delay element. This macro generates an output clock phase shift from the input clock.

The CLKDLY macro can be driven by an INBUF macro to create a composite macro, where the I/O macro drives the global buffer (with programmable delay) using a hardwired connection. In this case, the I/O must be placed in one of the dedicated global I/O locations.

Many specific INBUF macros support the wide variety of single-ended and differential I/O standards supported by the Fusion family. The available INBUF macros are described in the *IGLOO*, *ProASIC3*, *SmartFusion and Fusion Macro Library Guide*.

The CLKDLY macro can be driven directly from the FPGA core.

The CLKDLY macro can also be driven from an I/O that is routed through the FPGA regular routing fabric. In this case, users must instantiate a special macro, PLLINT, to differentiate from the hardwired I/O connection described earlier.

The visual CLKDLY configuration in the SmartGen part of the Libero SoC and Designer tools allows the user to select the desired amount of delay and configures the delay elements appropriately. SmartGen also allows the user to select the input clock source. SmartGen will automatically instantiate the special macro, PLLINT, when needed.

## **Program Operation**

A Program operation is initiated by asserting the PROGRAM signal on the interface. Program operations save the contents of the Page Buffer to the FB Array. Due to the technologies inherent in the FB, the total programming (including erase) time per page of the eNVM is 6.8 ms. While the FB is writing the data to the array, the BUSY signal will be asserted.

During a Program operation, the sector and page addresses on ADDR are compared with the stored address for the page (and sector) in the Page Buffer. If there is a mismatch between the two addresses, the Program operation will be aborted and an error will be reported on the STATUS output.

It is possible to write the Page Buffer to a different page in memory. When asserting the PROGRAM pin, if OVERWRITEPAGE is asserted as well, the FB will write the contents of the Page Buffer to the sector and page designated on the ADDR inputs if the destination page is not Overwrite Protected.

A Program operation can be utilized to either modify the contents of the page in the flash memory block or change the protections for the page. Setting the OVERWRITEPROTECT bit on the interface while asserting the PROGRAM pin will put the page addressed into Overwrite Protect Mode. Overwrite Protect Mode safeguards a page from being inadvertently overwritten during subsequent Program or Erase operations.

Program operations that result in a STATUS value of '01' do not modify the addressed page. For all other values of STATUS, the addressed page is modified. Program errors include the following:

- 1. Attempting to program a page that is Overwrite Protected (STATUS = '01')

- 2. Attempting to program a page that is not in the Page Buffer when the Page Buffer has entered Page Loss Protection Mode (STATUS = '01')

- Attempting to perform a program with OVERWRITEPAGE set when the page addressed has been Overwrite Protected (STATUS = '01')

- 4. The Write Count of the page programmed exceeding the Write Threshold defined in the part specification (STATUS = '11')

- 5. The ECC Logic determining that there is an uncorrectable error within the programmed page (STATUS = '10')

- 6. Attempting to program a page that is **not** in the Page Buffer when OVERWRITEPAGE is not set and the page in the Page Buffer is modified (STATUS = '01')

- 7. Attempting to program the page in the Page Buffer when the Page Buffer is **not** modified

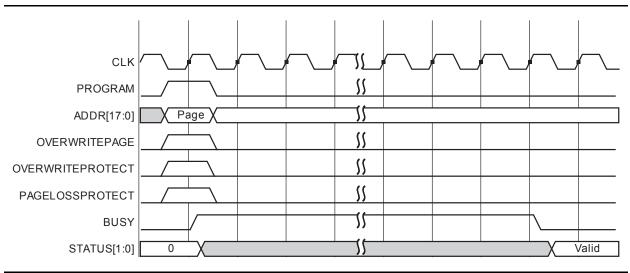

The waveform for a Program operation is shown in Figure 2-36.

### Figure 2-36 • FB Program Waveform

Note: OVERWRITEPAGE is only sampled when the PROGRAM or ERASEPAGE pins are asserted. OVERWRITEPAGE is ignored in all other operations.

The AEMPTY flag is asserted when the difference between the write address and the read address is less than a predefined value. In the example above, a value of 200 for AEVAL means that the AEMPTY flag will be asserted when a read causes the difference between the write address and the read address to drop to 200. It will stay asserted until that difference rises above 200. Note that the FIFO can be configured with different read and write widths; in this case, the AFVAL setting is based on the number of write data entries and the AEVAL setting is based on the number of software and 256×18, only 4,096 bits can be addressed by the 12 bits of AFVAL and AEVAL. The number of words must be multiplied by 8 and 16, instead of 9 and 18. The SmartGen tool automatically uses the proper values. To avoid halfwords being written or read, which could happen if different read and write aspect ratios are specified, the FIFO will assert FULL or EMPTY as soon as at least a minimum of one word cannot be written or read. For example, if a two-bit word is written and a four-bit word is being read, the FIFO will remain in the empty state when the first word is written. This occurs even if the FIFO is not completely empty, because in this case, a complete word cannot be read. The same is applicable in the full state. If a four-bit word is written and a two-bit word is read, the FIFO is full and one word is read. The FULL flag will remain asserted because a complete word cannot be written at this point.

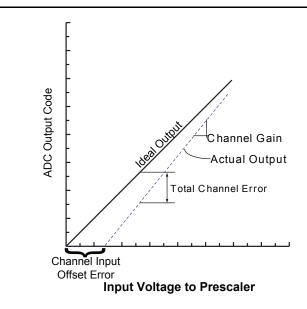

#### Channel Input Offset Error

Channel Offset error is measured as the input voltage that causes the transition from zero to a count of one. An Ideal Prescaler will have offset equal to  $\frac{1}{2}$  of LSB voltage. Offset error is a positive or negative when the first transition point is higher or lower than ideal. Offset error is expressed in LSB or input voltage.

#### **Total Channel Error**

Total Channel Error is defined as the total error measured compared to the ideal value. Total Channel Error is the sum of gain error and offset error combined. Figure 2-68 shows how Total Channel Error is measured.

Total Channel Error is defined as the difference between the actual ADC output and ideal ADC output. In the example shown in Figure 2-68, the Total Channel Error would be a negative number.

Figure 2-68 • Total Channel Error Example

## Terminology

## Resolution

Resolution defines the smallest temperature change Fusion Temperature Monitor can resolve. For ADC configured as 8-bit mode, each LSB represents 4°C, and 1°C per LSB for 10-bit mode. With 12-bit mode, the Temperature Monitor can still only resolve 1°C due to Temperature Monitor design.

## Offset

The Fusion Temperature Monitor has a systematic offset (Table 2-49 on page 2-117), excluding error due to board resistance and ideality factor of the external diode. Microsemi provides an IP block (CalibIP) that is required in order to mitigate the systematic temperature offset. For further details on CalibIP, refer to the "Temperature, Voltage, and Current Calibration in Fusion FPGAs" chapter of the Fusion FPGA Fabric User Guide.

The optimal setting for the system running at 66 MHz with an ADC for 10-bit mode chosen is shown in Table 2-47:

#### Table 2-47 • Optimal Setting at 66 MHz in 10-Bit Mode

| TVC[7:0]  | = 1      | = 0x01 |

|-----------|----------|--------|

| STC[7:0]  | = 3      | = 0x03 |

| MODE[3:0] | = b'0100 | = 0x4* |

*Note:* No power-down after every conversion is chosen in this case; however, if the application is power-sensitive, the MODE[2] can be set to '0', as described above, and it will not affect any performance.

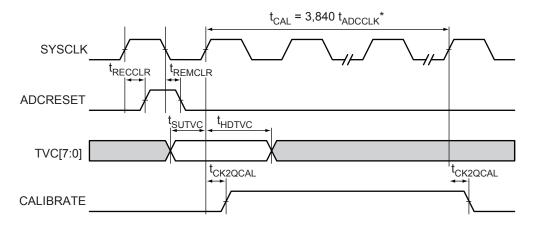

## **Timing Diagrams**

Note: \*Refer to EQ 15 on page 2-107 for the calculation on the period of ADCCLK, t<sub>ADCCLK</sub>.

Figure 2-89 • Power-Up Calibration Status Signal Timing Diagram

## Analog Quad ACM Description

Table 2-56 maps out the ACM space associated with configuration of the Analog Quads within the Analog Block. Table 2-56 shows the byte assignment within each quad and the function of each bit within each byte. Subsequent tables will explain each bit setting and how it corresponds to a particular configuration. After 3.3 V and 1.5 V are applied to Fusion, Analog Quad configuration registers are loaded with default settings until the initialization and configuration state machine changes them to user-defined settings.

| Table 2.56 . | Analog | Quad ACM | <b>Byte</b> | Assignment |

|--------------|--------|----------|-------------|------------|

| Table 2-30 • | Analog |          | Dyte        | Assignment |

| Byte   | Bit | Signal (Bx) | Function                            | Default Setting       |

|--------|-----|-------------|-------------------------------------|-----------------------|

| Byte 0 | 0   | B0[0]       | Scaling factor control – prescaler  | Highest voltage range |

| (AV)   | 1   | B0[1]       |                                     |                       |

|        | 2   | B0[2]       |                                     |                       |

|        | 3   | B0[3]       | Analog MUX select                   | Prescaler             |

|        | 4   | B0[4]       | Current monitor switch              | Off                   |

|        | 5   | B0[5]       | Direct analog input switch          | Off                   |

|        | 6   | B0[6]       | Selects V-pad polarity              | Positive              |

|        | 7   | B0[7]       | Prescaler op amp mode               | Power-down            |

| Byte 1 | 0   | B1[0]       | Scaling factor control – prescaler  | Highest voltage range |

| (AC)   | 1   | B1[1]       |                                     |                       |

|        | 2   | B1[2]       |                                     |                       |

|        | 3   | B1[3]       | Analog MUX select                   | Prescaler             |

|        | 4   | B1[4]       |                                     |                       |

|        | 5   | B1[5]       | Direct analog input switch          | Off                   |

|        | 6   | B1[6]       | Selects C-pad polarity              | Positive              |

|        | 7   | B1[7]       | Prescaler op amp mode               | Power-down            |

| Byte 2 | 0   | B2[0]       | Internal chip temperature monitor * | Off                   |

| (AG)   | 1   | B2[1]       | Spare                               | -                     |

|        | 2   | B2[2]       | Current drive control               | Lowest current        |

|        | 3   | B2[3]       |                                     |                       |

|        | 4   | B2[4]       | Spare                               | -                     |

|        | 5   | B2[5]       | Spare                               | -                     |

|        | 6   | B2[6]       | Selects G-pad polarity              | Positive              |

|        | 7   | B2[7]       | Selects low/high drive              | Low drive             |

| Byte 3 | 0   | B3[0]       | Scaling factor control – prescaler  | Highest voltage range |

| (AT)   | 1   | B3[1]       |                                     |                       |

|        | 2   | B3[2]       | 1                                   |                       |

|        | 3   | B3[3]       | Analog MUX select                   | Prescaler             |

|        | 4   | B3[4]       | 1                                   |                       |

|        | 5   | B3[5]       | Direct analog input switch          | Off                   |

|        | 6   | B3[6]       | -                                   | -                     |

|        | 7   | B3[7]       | Prescaler op amp mode               | Power-down            |

Note: \*For the internal temperature monitor to function, Bit 0 of Byte 2 for all 10 Quads must be set.

## User I/Os

## Introduction

Fusion devices feature a flexible I/O structure, supporting a range of mixed voltages (1.5 V, 1.8 V, 2.5 V, and 3.3 V) through a bank-selectable voltage. Table 2-68, Table 2-69, Table 2-70, and Table 2-71 on page 2-135 show the voltages and the compatible I/O standards. I/Os provide programmable slew rates, drive strengths, weak pull-up, and weak pull-down circuits. 3.3 V PCI and 3.3 V PCI-X are 5 V–tolerant. See the "5 V Input Tolerance" section on page 2-144 for possible implementations of 5 V tolerance.

All I/Os are in a known state during power-up, and any power-up sequence is allowed without current impact. Refer to the "I/O Power-Up and Supply Voltage Thresholds for Power-On Reset (Commercial and Industrial)" section on page 3-5 for more information. In low power standby or sleep mode (VCC is OFF, VCC33A is ON, VCCI is ON) or when the resource is not used, digital inputs are tristated, digital outputs are tristated, and digital bibufs (input/output) are tristated.

I/O Tile

The Fusion I/O tile provides a flexible, programmable structure for implementing a large number of I/O standards. In addition, the registers available in the I/O tile in selected I/O banks can be used to support high-performance register inputs and outputs, with register enable if desired (Figure 2-99 on page 2-133). The registers can also be used to support the JESD-79C DDR standard within the I/O structure (see the "Double Data Rate (DDR) Support" section on page 2-139 for more information).

As depicted in Figure 2-100 on page 2-138, all I/O registers share one CLR port. The output register and output enable register share one CLK port. Refer to the "I/O Registers" section on page 2-138 for more information.

## I/O Banks and I/O Standards Compatibility

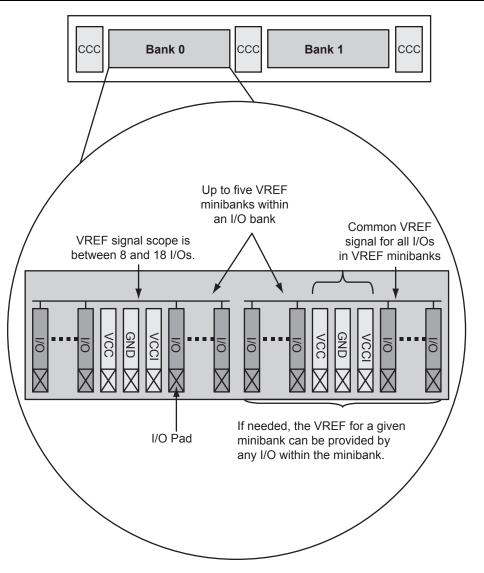

The digital I/Os are grouped into I/O voltage banks. There are three digital I/O banks on the AFS090 and AFS250 devices and four digital I/O banks on the AFS600 and AFS1500 devices. Figure 2-113 on page 2-158 and Figure 2-114 on page 2-159 show the bank configuration by device. The north side of the I/O in the AFS600 and AFS1500 devices comprises two banks of Pro I/Os. The Pro I/Os support a wide number of voltage-referenced I/O standards in addition to the multitude of single-ended and differential I/O standards common throughout all Microsemi digital I/Os. Each I/O voltage bank has dedicated I/O supply and ground voltages (VCCI/GNDQ for input buffers and VCCI/GND for output buffers). Because of these dedicated supplies, only I/Os with compatible standards can be assigned to the same I/O voltage bank. Table 2-69 and Table 2-70 on page 2-134 show the required voltage compatibility values for each of these voltages.

For more information about I/O and global assignments to I/O banks, refer to the specific pin table of the device in the "Package Pin Assignments" on page 4-1 and the "User I/O Naming Convention" section on page 2-158.

Each Pro I/O bank is divided into minibanks. Any user I/O in a VREF minibank (a minibank is the region of scope of a VREF pin) can be configured as a VREF pin (Figure 2-99 on page 2-133). Only one VREF pin is needed to control the entire VREF minibank. The location and scope of the VREF minibanks can be determined by the I/O name. For details, see the "User I/O Naming Convention" section on page 2-158.

Table 2-70 on page 2-134 shows the I/O standards supported by Fusion devices and the corresponding voltage levels.

I/O standards are compatible if the following are true:

- Their VCCI values are identical.

- If both of the standards need a VREF, their VREF values must be identical (Pro I/O only).

Figure 2-99 • Fusion Pro I/O Bank Detail Showing VREF Minibanks (north side of AFS600 and AFS1500)

| I/O Bank     | Single-Ended I/O Standards                                                                        | Differential I/O<br>Standards | Voltage-Referenced                                                                                          | Hot-<br>Swap |

|--------------|---------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------|--------------|

| Standard I/O | LVTTL/LVCMOS 3.3 V, LVCMOS<br>2.5 V / 1.8 V / 1.5 V, LVCMOS<br>2.5/5.0 V                          | _                             | -                                                                                                           | Yes          |

| Advanced I/O | LVTTL/LVCMOS 3.3 V, LVCMOS<br>2.5 V / 1.8 V / 1.5 V, LVCMOS<br>2.5/5.0 V, 3.3 V PCI / 3.3 V PCI-X | LVPECL and<br>LVDS            | -                                                                                                           | -            |

| Pro I/O      | LVTTL/LVCMOS 3.3 V, LVCMOS<br>2.5 V / 1.8 V / 1.5 V, LVCMOS<br>2.5/5.0 V, 3.3 V PCI / 3.3 V PCI-X | LVPECL and<br>LVDS            | GTL+2.5 V / 3.3 V, GTL 2.5 V / 3.3 V,<br>HSTL Class I and II, SSTL2 Class I<br>and II, SSTL3 Class I and II | Yes          |

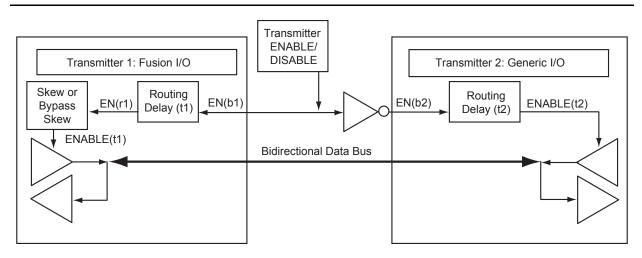

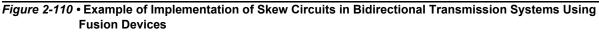

At the system level, the skew circuit can be used in applications where transmission activities on bidirectional data lines need to be coordinated. This circuit, when selected, provides a timing margin that can prevent bus contention and subsequent data loss or transmitter overstress due to transmitter-to-transmitter current shorts. Figure 2-110 presents an example of the skew circuit implementation in a bidirectional communication system. Figure 2-111 shows how bus contention is created, and Figure 2-112 on page 2-151 shows how it can be avoided with the skew circuit.

Figure 2-111 • Timing Diagram (bypasses skew circuit)

# Table 2-93 • Summary of I/O Timing Characteristics – Software Default SettingsCommercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,Worst-Case VCCI = I/O Standard DependentApplicable to Advanced I/Os

|                              |                     |           |                      |                         |        | r    |      |      | 1     |      |      |      |      | r    |      |       |

|------------------------------|---------------------|-----------|----------------------|-------------------------|--------|------|------|------|-------|------|------|------|------|------|------|-------|

| I/O Standard                 | Drive Strength (mA) | Slew Rate | Capacitive Load (pF) | External Resistor (Ohm) | t роит | top  | toin | tev  | teour | tzı  | tzH  | tız  | ZHţ  | tzLS | tzHS | Units |

| 3.3 V LVTTL/<br>3.3 V LVCMOS | 12 mA               | High      | 35 pF                | -                       | 0.49   | 2.64 | 0.03 | 0.90 | 0.32  | 2.69 | 2.11 | 2.40 | 2.68 | 4.36 | 3.78 | ns    |

| 2.5 V LVCMOS                 | 12 mA               | High      | 35 pF                | _                       | 0.49   | 2.66 | 0.03 | 0.98 | 0.32  | 2.71 | 2.56 | 2.47 | 2.57 | 4.38 | 4.23 | ns    |

| 1.8 V LVCMOS                 | 12 mA               | High      | 35 pF                | -                       | 0.49   | 2.64 | 0.03 | 0.91 | 0.32  | 2.69 | 2.27 | 2.76 | 3.05 | 4.36 | 3.94 | ns    |

| 1.5 V LVCMOS                 | 12 mA               | High      | 35 pF                | -                       | 0.49   | 3.05 | 0.03 | 1.07 | 0.32  | 3.10 | 2.67 | 2.95 | 3.14 | 4.77 | 4.34 | ns    |

| 3.3 V PCI                    | Per PCI<br>spec     | High      | 10 pF                | 25 <sup>2</sup>         | 0.49   | 2.00 | 0.03 | 0.65 | 0.32  | 2.04 | 1.46 | 2.40 | 2.68 | 3.71 | 3.13 | ns    |

| 3.3 V PCI-X                  | Per PCI-X<br>spec   | High      | 10 pF                | 25 <sup>2</sup>         | 0.49   | 2.00 | 0.03 | 0.62 | 0.32  | 2.04 | 1.46 | 2.40 | 2.68 | 3.71 | 3.13 | ns    |

| LVDS                         | 24 mA               | High      | -                    | -                       | 0.49   | 1.37 | 0.03 | 1.20 | N/A   | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | ns    |

| LVPECL                       | 24 mA               | High      | -                    | -                       | 0.49   | 1.34 | 0.03 | 1.05 | N/A   | N/A  | N/A  | N/A  | N/A  | N/A  | N/A  | ns    |

Notes:

1. For specific junction temperature and voltage-supply levels, refer to Table 3-6 on page 3-7 for derating values.

2. Resistance is used to measure I/O propagation delays as defined in PCI specifications. See Figure 2-123 on page 2-197 for connectivity. This resistor is not required during normal operation.

# Table 2-94 • Summary of I/O Timing Characteristics – Software Default SettingsCommercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V,Worst-Case VCCI = I/O Standard DependentApplicable to Standard I/Os

| I/O Standard                 | Drive Strength (mA) | Slew Rate | Capacitive Load (pF) | External Resistor (Ohm) | t pour | top  | t <sub>DIN</sub> | t <sub>Þ</sub> v | teour | t <sub>zı</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|------------------------------|---------------------|-----------|----------------------|-------------------------|--------|------|------------------|------------------|-------|-----------------|-----------------|-----------------|-----------------|-------|

| 3.3 V LVTTL/<br>3.3 V LVCMOS | 8 mA                | High      | 35 pF                | -                       | 0.49   | 3.29 | 0.03             | 0.75             | 0.32  | 3.36            | 2.80            | 1.79            | 2.01            | ns    |

| 2.5 V LVCMOS                 | 8 mA                | High      | 35pF                 | -                       | 0.49   | 3.56 | 0.03             | 0.96             | 0.32  | 3.40            | 3.56            | 1.78            | 1.91            | ns    |

| 1.8 V LVCMOS                 | 4 mA                | High      | 35pF                 | -                       | 0.49   | 4.74 | 0.03             | 0.90             | 0.32  | 4.02            | 4.74            | 1.80            | 1.85            | ns    |

| 1.5 V LVCMOS                 | 2 mA                | High      | 35pF                 | Ι                       | 0.49   | 5.71 | 0.03             | 1.06             | 0.32  | 4.71            | 5.71            | 1.83            | 1.83            | ns    |

Note: For specific junction temperature and voltage-supply levels, refer to Table 3-6 on page 3-7 for derating values.

### Table 2-98 • I/O Short Currents IOSH/IOSL (continued)

|                                  | Drive Strength                 | IOSH (mA)* | IOSL (mA)* |

|----------------------------------|--------------------------------|------------|------------|

| 2.5 V LVCMOS                     | 2 mA                           | 16         | 18         |

|                                  | 4 mA                           | 16         | 18         |

|                                  | 6 mA                           | 32         | 37         |

|                                  | 8 mA                           | 32         | 37         |

|                                  | 12 mA                          | 65         | 74         |

|                                  | 16 mA                          | 83         | 87         |

|                                  | 24 mA                          | 169        | 124        |

| 1.8 V LVCMOS                     | 2 mA                           | 9          | 11         |

|                                  | 4 mA                           | 17         | 22         |

|                                  | 6 mA                           | 35         | 44         |

|                                  | 8 mA                           | 45         | 51         |

|                                  | 12 mA                          | 91         | 74         |

|                                  | 16 mA                          | 91         | 74         |

| 1.5 V LVCMOS                     | 2 mA                           | 13         | 16         |

|                                  | 4 mA                           | 25         | 33         |

|                                  | 6 mA                           | 32         | 39         |

|                                  | 8 mA                           | 66         | 55         |

|                                  | 12 mA                          | 66         | 55         |

| 3.3 V PCI/PCI-X                  | Per PCI/PCI-X<br>specification | 103        | 109        |

| Applicable to Standard I/O Banks |                                |            |            |

| 3.3 V LVTTL / 3.3 V LVCMOS       | 2 mA                           | 25         | 27         |

|                                  | 4 mA                           | 25         | 27         |

|                                  | 6 mA                           | 51         | 54         |

|                                  | 8 mA                           | 51         | 54         |

| 2.5 V LVCMOS                     | 2 mA                           | 16         | 18         |

|                                  | 4 mA                           | 16         | 18         |

|                                  | 6 mA                           | 32         | 37         |

|                                  | 8 mA                           | 32         | 37         |

| 1.8 V LVCMOS                     | 2 mA                           | 9          | 11         |

|                                  | 4 mA                           | 17         | 22         |

| 1.5 V LVCMOS                     | 2 mA                           | 13         | 16         |

*Note:*  $^{*}T_{J} = 100^{\circ}C$

The length of time an I/O can withstand IOSH/IOSL events depends on the junction temperature. The reliability data below is based on a 3.3 V, 36 mA I/O setting, which is the worst case for this type of analysis.

For example, at 100°C, the short current condition would have to be sustained for more than six months to cause a reliability concern. The I/O design does not contain any short circuit protection, but such protection would only be needed in extremely prolonged stress conditions.

## Table 2-113 • 2.5 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Pro I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.60              | 8.82            | 0.04             | 1.51            | 1.66             | 0.43              | 8.13            | 8.82            | 2.72            | 2.29            | 10.37            | 11.05            | ns    |

|                   | -1             | 0.51              | 7.50            | 0.04             | 1.29            | 1.41             | 0.36              | 6.92            | 7.50            | 2.31            | 1.95            | 8.82             | 9.40             | ns    |

|                   | -2             | 0.45              | 6.58            | 0.03             | 1.13            | 1.24             | 0.32              | 6.07            | 6.58            | 2.03            | 1.71            | 7.74             | 8.25             | ns    |

| 8 mA              | Std.           | 0.60              | 5.27            | 0.04             | 1.51            | 1.66             | 0.43              | 5.27            | 5.27            | 3.10            | 3.03            | 7.50             | 7.51             | ns    |

|                   | -1             | 0.51              | 4.48            | 0.04             | 1.29            | 1.41             | 0.36              | 4.48            | 4.48            | 2.64            | 2.58            | 6.38             | 6.38             | ns    |

|                   | -2             | 0.45              | 3.94            | 0.03             | 1.13            | 1.24             | 0.32              | 3.93            | 3.94            | 2.32            | 2.26            | 5.60             | 5.61             | ns    |

| 12 mA             | Std.           | 0.66              | 3.74            | 0.04             | 1.51            | 1.66             | 0.43              | 3.81            | 3.49            | 3.37            | 3.49            | 6.05             | 5.73             | ns    |

|                   | -1             | 0.56              | 3.18            | 0.04             | 1.29            | 1.41             | 0.36              | 3.24            | 2.97            | 2.86            | 2.97            | 5.15             | 4.87             | ns    |

|                   | -2             | 0.49              | 2.80            | 0.03             | 1.13            | 1.24             | 0.32              | 2.85            | 2.61            | 2.51            | 2.61            | 4.52             | 4.28             | ns    |

| 16 mA             | Std.           | 0.66              | 3.53            | 0.04             | 1.51            | 1.66             | 0.43              | 3.59            | 3.12            | 3.42            | 3.62            | 5.83             | 5.35             | ns    |

|                   | -1             | 0.56              | 3.00            | 0.04             | 1.29            | 1.41             | 0.36              | 3.06            | 2.65            | 2.91            | 3.08            | 4.96             | 4.55             | ns    |

|                   | -2             | 0.49              | 2.63            | 0.03             | 1.13            | 1.24             | 0.32              | 2.68            | 2.33            | 2.56            | 2.71            | 4.35             | 4.00             | ns    |

| 24 mA             | Std.           | 0.66              | 3.26            | 0.04             | 1.51            | 1.66             | 0.43              | 3.32            | 2.48            | 3.49            | 4.11            | 5.56             | 4.72             | ns    |

|                   | -1             | 0.56              | 2.77            | 0.04             | 1.29            | 1.41             | 0.36              | 2.83            | 2.11            | 2.97            | 3.49            | 4.73             | 4.01             | ns    |

|                   | -2             | 0.49              | 2.44            | 0.03             | 1.13            | 1.24             | 0.32              | 2.48            | 1.85            | 2.61            | 3.07            | 4.15             | 3.52             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

## Table 2-122 • 1.8 V LVCMOS Low Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V Applicable to Advanced I/Os

| Drive<br>Strength | Speed<br>Grade  | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|-----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 2 mA              | Std.            | 0.66              | 15.53           | 0.04             | 1.31            | 0.43              | 14.11           | 15.53           | 2.78            | 1.60            | 16.35            | 17.77            | ns    |

|                   | -1              | 0.56              | 13.21           | 0.04             | 1.11            | 0.36              | 12.01           | 13.21           | 2.36            | 1.36            | 13.91            | 15.11            | ns    |

|                   | -2 <sup>2</sup> | 0.49              | 11.60           | 0.03             | 0.98            | 0.32              | 10.54           | 11.60           | 2.07            | 1.19            | 12.21            | 13.27            | ns    |

| 4 mA              | Std.            | 0.66              | 10.48           | 0.04             | 1.31            | 0.43              | 10.41           | 10.48           | 3.23            | 2.73            | 12.65            | 12.71            | ns    |

|                   | -1              | 0.56              | 8.91            | 0.04             | 1.11            | 0.36              | 8.86            | 8.91            | 2.75            | 2.33            | 10.76            | 10.81            | ns    |

|                   | -2              | 0.49              | 7.82            | 0.03             | 0.98            | 0.32              | 7.77            | 7.82            | 2.41            | 2.04            | 9.44             | 9.49             | ns    |

| 8 mA              | Std.            | 0.66              | 8.05            | 0.04             | 1.31            | 0.43              | 8.20            | 7.84            | 3.54            | 3.27            | 10.43            | 10.08            | ns    |

|                   | -1              | 0.56              | 6.85            | 0.04             | 1.11            | 0.36              | 6.97            | 6.67            | 3.01            | 2.78            | 8.88             | 8.57             | ns    |

|                   | -2              | 0.49              | 6.01            | 0.03             | 0.98            | 0.32              | 6.12            | 5.86            | 2.64            | 2.44            | 7.79             | 7.53             | ns    |

| 12 mA             | Std.            | 0.66              | 7.50            | 0.04             | 1.31            | 0.43              | 7.64            | 7.30            | 3.61            | 3.41            | 9.88             | 9.53             | ns    |

|                   | -1              | 0.56              | 6.38            | 0.04             | 1.11            | 0.36              | 6.50            | 6.21            | 3.07            | 2.90            | 8.40             | 8.11             | ns    |

|                   | -2              | 0.49              | 5.60            | 0.03             | 0.98            | 0.32              | 5.71            | 5.45            | 2.69            | 2.55            | 7.38             | 7.12             | ns    |

| 16 mA             | Std.            | 0.66              | 7.29            | 0.04             | 1.31            | 0.43              | 7.23            | 7.29            | 3.71            | 3.95            | 9.47             | 9.53             | ns    |

|                   | -1              | 0.56              | 6.20            | 0.04             | 1.11            | 0.36              | 6.15            | 6.20            | 3.15            | 3.36            | 8.06             | 8.11             | ns    |

|                   | -2              | 0.49              | 5.45            | 0.03             | 0.98            | 0.32              | 5.40            | 5.45            | 2.77            | 2.95            | 7.07             | 7.12             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

## 1.5 V LVCMOS (JESD8-11)

Low-Voltage CMOS for 1.5 V is an extension of the LVCMOS standard (JESD8-5) used for generalpurpose 1.5 V applications. It uses a 1.5 V input buffer and push-pull output buffer.

| 1.5 V<br>LVCMOS             |                                  | VIL         | VIH         |           | VOL         | VOH         | IOL | юн | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-----------------------------|----------------------------------|-------------|-------------|-----------|-------------|-------------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength           | Min.<br>V                        | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| Applicable                  | Applicable to Pro I/O Banks      |             |             |           |             |             |     |    |                         |                         |                  |                  |

| 2 mA                        | -0.3                             | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 2   | 2  | 16                      | 13                      | 10               | 10               |

| 4 mA                        | -0.3                             | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 4   | 4  | 33                      | 25                      | 10               | 10               |

| 6 mA                        | -0.3                             | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 6   | 6  | 39                      | 32                      | 10               | 10               |

| 8 mA                        | -0.3                             | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 8   | 8  | 55                      | 66                      | 10               | 10               |

| 12 mA                       | -0.3                             | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 12  | 12 | 55                      | 66                      | 10               | 10               |

| Applicable                  | Applicable to Advanced I/O Banks |             |             |           |             |             |     |    |                         |                         |                  |                  |

| 2 mA                        | -0.3                             | 0.35 * VCCI | 0.65 * VCCI | 1.575     | 0.25 * VCCI | 0.75 * VCCI | 2   | 2  | 16                      | 13                      | 10               | 10               |

| 4 mA                        | -0.3                             | 0.35 * VCCI | 0.65 * VCCI | 1.575     | 0.25 * VCCI | 0.75 * VCCI | 4   | 4  | 33                      | 25                      | 10               | 10               |

| 6 mA                        | -0.3                             | 0.35 * VCCI | 0.65 * VCCI | 1.575     | 0.25 * VCCI | 0.75 * VCCI | 6   | 6  | 39                      | 32                      | 10               | 10               |

| 8 mA                        | -0.3                             | 0.35 * VCCI | 0.65 * VCCI | 1.575     | 0.25 * VCCI | 0.75 * VCCI | 8   | 8  | 55                      | 66                      | 10               | 10               |

| 12 mA                       | -0.3                             | 0.35 * VCCI | 0.65 * VCCI | 1.575     | 0.25 * VCCI | 0.75 * VCCI | 12  | 12 | 55                      | 66                      | 10               | 10               |

| Applicable to Pro I/O Banks |                                  |             |             |           |             |             |     |    |                         |                         |                  |                  |

| 2 mA                        | -0.3                             | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 2   | 2  | 16                      | 13                      | 10               | 10               |

| Notes:                      |                                  |             |             |           |             |             |     |    |                         |                         |                  |                  |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

2. I<sub>IH</sub> is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

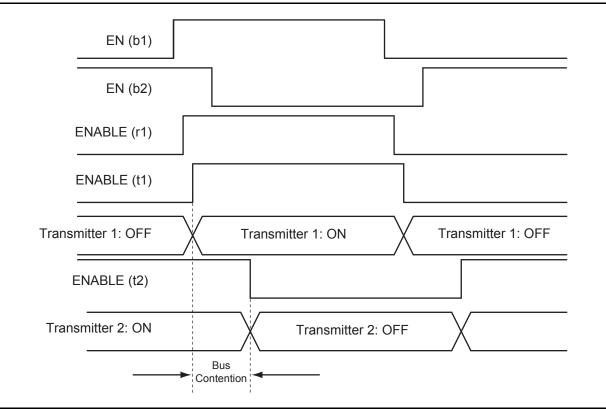

Figure 2-122 • AC Loading

### Table 2-127 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|------------------------|

| 0             | 1.5            | 0.75                 | _               | 35                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

Package Pin Assignments

|                            | QN180             |                 | QN180      |                 |                 |  |  |

|----------------------------|-------------------|-----------------|------------|-----------------|-----------------|--|--|

| Pin Number AFS090 Function |                   | AFS250 Function | Pin Number | AFS090 Function | AFS250 Function |  |  |

| A1                         | GNDQ              | GNDQ            | A37        | VPUMP           | VPUMP           |  |  |

| A2                         | VCCIB3            | VCCIB3          | A38        | TDI             | TDI             |  |  |

| A3                         | GAB2/IO52NDB3V0   | IO74NDB3V0      | A39        | TDO             | TDO             |  |  |

| A4                         | GFA2/IO51NDB3V0   | IO71NDB3V0      | A40        | VJTAG           | VJTAG           |  |  |

| A5                         | GFC2/IO50NDB3V0   | IO69NPB3V0      | A41        | GDB1/IO39PPB1V0 | GDA1/IO54PPB1V0 |  |  |

| A6                         | VCCIB3            | VCCIB3          | A42        | GDC1/IO38PDB1V0 | GDB1/IO53PDB1V0 |  |  |

| A7                         | GFA1/IO47PPB3V0   | GFB1/IO67PPB3V0 | A43        | VCC             | VCC             |  |  |

| A8                         | GEB0/IO45NDB3V0   | NC              | A44        | GCB0/IO35NPB1V0 | GCB0/IO48NPB1V0 |  |  |

| A9                         | XTAL1             | XTAL1           | A45        | GCC1/IO34PDB1V0 | GCC1/IO47PDB1V0 |  |  |

| A10                        | GNDOSC            | GNDOSC          | A46        | VCCIB1          | VCCIB1          |  |  |

| A11                        | GEC2/IO43PPB3V0   | GEA1/IO61PPB3V0 | A47        | GBC2/IO32PPB1V0 | GBB2/IO41PPB1V0 |  |  |

| A12                        | IO43NPB3V0        | GEA0/IO61NPB3V0 | A48        | VCCIB1          | VCCIB1          |  |  |

| A13                        | NC                | VCCIB3          | A49        | NC              | NC              |  |  |

| A14                        | GNDNVM            | GNDNVM          | A50        | GBA0/IO29RSB0V0 | GBB1/IO37RSB0V0 |  |  |

| A15                        | PCAP              | PCAP            | A51        | VCCIB0          | VCCIB0          |  |  |

| A16                        | VCC33PMP          | VCC33PMP        | A52        | GBB0/IO27RSB0V0 | GBC0/IO34RSB0V0 |  |  |

| A17                        | NC                | NC              | A53        | GBC1/IO26RSB0V0 | IO33RSB0V0      |  |  |

| A18                        | AV0               | AV0             | A54        | IO24RSB0V0      | IO29RSB0V0      |  |  |

| A19                        | AG0               | AG0             | A55        | IO21RSB0V0      | IO26RSB0V0      |  |  |

| A20                        | ATRTN0            | ATRTN0          | A56        | VCCIB0          | VCCIB0          |  |  |

| A21                        | AG1               | AG1             | A57        | IO15RSB0V0      | IO21RSB0V0      |  |  |

| A22                        | AC1               | AC1             | A58        | IO10RSB0V0      | IO13RSB0V0      |  |  |

| A23                        | AV2               | AV2             | A59        | IO07RSB0V0      | IO10RSB0V0      |  |  |

| A24                        | AT2               | AT2             | A60        | GAC0/IO04RSB0V0 | IO06RSB0V0      |  |  |

| A25                        | AT3               | AT3             | A61        | GAB1/IO03RSB0V0 | GAC1/IO05RSB0V0 |  |  |

| A26                        | AC3               | AC3             | A62        | VCC             | VCC             |  |  |

| A27                        | AV4               | AV4             | A63        | GAA1/IO01RSB0V0 | GAB0/IO02RSB0V0 |  |  |

| A28                        | AC4               | AC4             | A64        | NC              | NC              |  |  |

| A29                        | AT4               | AT4             | B1         | VCOMPLA         | VCOMPLA         |  |  |

| A30                        | NC                | AG5             | B2         | GAA2/IO52PDB3V0 | GAC2/IO74PDB3V0 |  |  |

| A31                        | NC                | AV5             | B3         | GAC2/IO51PDB3V0 | GFA2/IO71PDB3V0 |  |  |

| A32                        | ADCGNDREF         | ADCGNDREF       | B4         | GFB2/IO50PDB3V0 | GFB2/IO70PSB3V0 |  |  |

| A33                        | VCC33A            | VCC33A          | B5         | VCC             | VCC             |  |  |

| A34                        | GNDA              | GNDA            | B6         | GFC0/IO49NDB3V0 | GFC0/IO68NDB3V0 |  |  |

| A35                        | PTBASE            | PTBASE          | B7         | GEB1/IO45PDB3V0 | NC              |  |  |

| A36                        | A36 VCCNVM VCCNVM |                 | B8         | VCCOSC          | VCCOSC          |  |  |

| FG256      |                 |                 |                 |                  |  |

|------------|-----------------|-----------------|-----------------|------------------|--|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |  |

| R5         | AV0             | AV0             | AV2             | AV2              |  |

| R6         | AT0             | AT0             | AT2             | AT2              |  |

| R7         | AV1             | AV1             | AV3             | AV3              |  |

| R8         | AT3             | AT3             | AT5             | AT5              |  |

| R9         | AV4             | AV4             | AV6             | AV6              |  |

| R10        | NC              | AT5             | AT7             | AT7              |  |

| R11        | NC              | AV5             | AV7             | AV7              |  |

| R12        | NC              | NC              | AT9             | AT9              |  |

| R13        | NC              | NC              | AG9             | AG9              |  |

| R14        | NC              | NC              | AC9             | AC9              |  |

| R15        | PUB             | PUB             | PUB             | PUB              |  |

| R16        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |  |

| T1         | GND             | GND             | GND             | GND              |  |

| T2         | NCAP            | NCAP            | NCAP            | NCAP             |  |

| Т3         | VCC33N          | VCC33N          | VCC33N          | VCC33N           |  |

| T4         | NC              | NC              | ATRTN0          | ATRTN0           |  |

| T5         | AT1             | AT1             | AT3             | AT3              |  |

| Т6         | ATRTN0 ATRTN0   |                 | ATRTN1          | ATRTN1           |  |

| T7         | T7 AT2 AT2      |                 | AT4             | AT4              |  |

| Т8         | ATRTN1          | ATRTN1          | ATRTN2          | ATRTN2           |  |

| Т9         | T9 AT4          |                 | AT6             | AT6              |  |

| T10        | ATRTN2          | ATRTN2          | ATRTN3          | ATRTN3           |  |

| T11        | NC              | NC NC           |                 | AT8              |  |

| T12        | NC              | NC              | ATRTN4          | ATRTN4           |  |

| T13        | GNDA            | GNDA            | GNDA            | GNDA             |  |

| T14        | VCC33A          | A VCC33A VCC33A |                 | VCC33A           |  |

| T15        | VAREF           | VAREF           | VAREF VAREF     |                  |  |

| T16        | GND             | GND             | GND             | GND              |  |

## FG484

## Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/default.aspx.

Fusion Family of Mixed Signal FPGAs

|                             | FG676            |            | FG676            | FG676      |                  |  |

|-----------------------------|------------------|------------|------------------|------------|------------------|--|

| Pin Number AFS1500 Function |                  | Pin Number | AFS1500 Function | Pin Number | AFS1500 Function |  |

| R21                         | IO72NDB2V0       | U5         | VCCIB4           | V15        | AC5              |  |

| R22                         | IO72PDB2V0       | U6         | IO91PDB4V0       | V16        | NC               |  |

| R23                         | GND              | U7         | IO91NDB4V0       | V17        | GNDA             |  |

| R24                         | IO71PDB2V0       | U8         | IO92PDB4V0       | V18        | IO77PPB2V0       |  |

| R25                         | VCCIB2           | U9         | GND              | V19        | IO74PDB2V0       |  |

| R26                         | IO67NDB2V0       | U10        | GND              | V20        | VCCIB2           |  |

| T1                          | GND              | U11        | VCC33A           | V21        | IO82NDB2V0       |  |

| T2                          | NC               | U12        | GNDA             | V22        | GDA2/IO82PDB2V0  |  |

| Т3                          | GFA1/IO105PDB4V0 | U13        | VCC33A           | V23        | GND              |  |

| T4                          | GFA0/IO105NDB4V0 | U14        | GNDA             | V24        | GDC1/IO79PDB2V0  |  |

| Т5                          | IO101NDB4V0      | U15        | VCC33A           | V25        | VCCIB2           |  |

| Т6                          | IO96PDB4V0       | U16        | GNDA             | V26        | NC               |  |

| Τ7                          | IO96NDB4V0       | U17        | VCC              | W1         | GND              |  |

| Т8                          | IO99NDB4V0       | U18        | GND              | W2         | IO94PPB4V0       |  |

| Т9                          | IO97NDB4V0       | U19        | IO74NDB2V0       | W3         | IO98PDB4V0       |  |

| T10                         | VCCIB4           | U20        | GDA0/IO81NDB2V0  | W4         | IO98NDB4V0       |  |

| T11                         | VCC              | U21        | GDB0/IO80NDB2V0  | W5         | GEC1/IO90PDB4V0  |  |

| T12                         | GND              | U22        | VCCIB2           | W6         | GEC0/IO90NDB4V0  |  |

| T13                         | VCC              | U23        | IO75NDB2V0       | W7         | GND              |  |

| T14                         | GND              | U24        | IO75PDB2V0       | W8         | VCCNVM           |  |

| T15                         | VCC              | U25        | NC               | W9         | VCCIB4           |  |

| T16                         | GND              | U26        | NC               | W10        | VCC15A           |  |

| T17                         | VCCIB2           | V1         | NC               | W11        | GNDA             |  |

| T18                         | IO83NDB2V0       | V2         | VCCIB4           | W12        | AC4              |  |

| T19                         | IO78NDB2V0       | V3         | IO100PPB4V0      | W13        | VCC33A           |  |

| T20                         | GDA1/IO81PDB2V0  | V4         | GND              | W14        | GNDA             |  |

| T21                         | GDB1/IO80PDB2V0  | V5         | IO95PDB4V0       | W15        | AG5              |  |

| T22                         | IO73NDB2V0       | V6         | IO95NDB4V0       | W16        | GNDA             |  |

| T23                         | IO73PDB2V0       | V7         | VCCIB4           | W17        | PUB              |  |

| T24                         | IO71NDB2V0       | V8         | IO92NDB4V0       | W18        | VCCIB2           |  |

| T25                         | NC               | V9         | GNDNVM           | W19        | TDI              |  |

| T26                         | GND              | V10        | GNDA             | W20        | GND              |  |

| U1                          | NC               | V11        | NC               | W21        | IO84NDB2V0       |  |

| U2                          | NC               | V12        | AV4              | W22        | GDC2/IO84PDB2V0  |  |

| U3                          | IO102PDB4V0      | V13        | NC               | W23        | IO77NPB2V0       |  |

| U4                          | IO102NDB4V0      | V14        | AV5              | W24        | GDC0/IO79NDB2V0  |  |

Package Pin Assignments

| FG676      |                  |  |  |  |  |

|------------|------------------|--|--|--|--|

| Pin Number | AFS1500 Function |  |  |  |  |

| W25        | NC               |  |  |  |  |

| W26        | GND              |  |  |  |  |

| Y1         | NC               |  |  |  |  |

| Y2         | NC               |  |  |  |  |

| Y3         | GEB1/IO89PDB4V0  |  |  |  |  |

| Y4         | GEB0/IO89NDB4V0  |  |  |  |  |

| Y5         | VCCIB4           |  |  |  |  |

| Y6         | GEA1/IO88PDB4V0  |  |  |  |  |

| Y7         | GEA0/IO88NDB4V0  |  |  |  |  |

| Y8         | GND              |  |  |  |  |

| Y9         | VCC33PMP         |  |  |  |  |

| Y10        | NC               |  |  |  |  |

| Y11        | VCC33A           |  |  |  |  |

| Y12        | AG4              |  |  |  |  |

| Y13        | AT4              |  |  |  |  |

| Y14        | ATRTN2           |  |  |  |  |

| Y15        | AT5              |  |  |  |  |

| Y16        | VCC33A           |  |  |  |  |

| Y17        | NC               |  |  |  |  |

| Y18        | VCC33A           |  |  |  |  |

| Y19        | GND              |  |  |  |  |

| Y20        | TMS              |  |  |  |  |

| Y21        | VJTAG            |  |  |  |  |

| Y22        | VCCIB2           |  |  |  |  |

| Y23        | TRST             |  |  |  |  |

| Y24        | TDO              |  |  |  |  |

| Y25        | NC               |  |  |  |  |

| Y26        | NC               |  |  |  |  |