Welcome to E-XFL.COM

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

## Details

E·XFI

| Product Status                 | Active                                                                     |

|--------------------------------|----------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | -                                                                          |

| Total RAM Bits                 | 110592                                                                     |

| Number of I/O                  | 119                                                                        |

| Number of Gates                | 600000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 256-LBGA                                                                   |

| Supplier Device Package        | 256-FPBGA (17x17)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/p1afs600-2fg256i |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

## Fusion Device Family Overview

| Introduction              | 1-1  |

|---------------------------|------|

| General Description       | 1-1  |

| Unprecedented Integration | 1-4  |

| Related Documents         | 1-10 |

## **Device Architecture**

| Fusion Stack Architecture |  |

|---------------------------|--|

| Core Architecture         |  |

| Clocking Resources        |  |

| Real-Time Counter System  |  |

| Embedded Memories         |  |

| Analog Block              |  |

| Analog Configuration MUX  |  |

| User I/Os                 |  |

| Pin Descriptions          |  |

| Security                  |  |

## DC and Power Characteristics

| General Specifications        | 3-1  |

|-------------------------------|------|

| Calculating Power Dissipation | 3-10 |

| Power Consumption             | 3-32 |

## Package Pin Assignments

| QN108 | <br>    | <br> | <br>      | <br> | <br> | <br>    | <br>    | <br> | <br> |     | <br> | <br>. 4- | 1 |

|-------|------|------|------|------|------|------|---------|------|-----------|------|------|---------|---------|------|------|-----|------|----------|---|

| QN180 |      |      |      |      |      |      |         |      |           |      |      |         |         |      |      |     |      |          |   |

| PQ208 |      |      |      |      |      |      |         |      |           |      |      |         |         |      |      |     |      |          |   |

| FG256 |      |      |      |      |      |      |         |      |           |      |      |         |         |      |      |     |      |          |   |

| FG484 |      |      |      |      |      |      |         |      |           |      |      |         |         |      |      |     |      |          |   |

| FG676 | <br> | <br> | <br> | <br> | <br> | <br> | <br>••• | <br> | <br>• • • | <br> | <br> | <br>• • | <br>• • | <br> | <br> | ••• | <br> | <br>4-2  | 7 |

## **Datasheet Information**

| List of Changes                                                         |   |

|-------------------------------------------------------------------------|---|

| Datasheet Categories                                                    |   |

| Safety Critical, Life Support, and High-Reliability Applications Policy | / |

# 2 – Device Architecture

# **Fusion Stack Architecture**

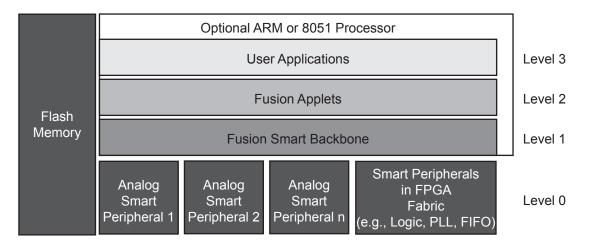

To manage the unprecedented level of integration in Fusion devices, Microsemi developed the Fusion technology stack (Figure 2-1). This layered model offers a flexible design environment, enabling design at very high and very low levels of abstraction. Fusion peripherals include hard analog IP and hard and soft digital IP. Peripherals communicate across the FPGA fabric via a layer of soft gates—the Fusion backbone. Much more than a common bus interface, this Fusion backbone integrates a micro-sequencer within the FPGA fabric and configures the individual peripherals and supports low-level processing of peripheral data. Fusion applets are application building blocks that can control and respond to peripherals and other system signals. Applets can be rapidly combined to create large applications. The technology is scalable across devices, families, design types, and user expertise, and supports a well-defined interface for external IP and tool integration.

At the lowest level, Level 0, are Fusion peripherals. These are configurable functional blocks that can be hardwired structures such as a PLL or analog input channel, or soft (FPGA gate) blocks such as a UART or two-wire serial interface. The Fusion peripherals are configurable and support a standard interface to facilitate communication and implementation.

Connecting and controlling access to the peripherals is the Fusion backbone, Level 1. The backbone is a soft-gate structure, scalable to any number of peripherals. The backbone is a bus and much more; it manages peripheral configuration to ensure proper operation. Leveraging the common peripheral interface and a low-level state machine, the backbone efficiently offloads peripheral management from the system design. The backbone can set and clear flags based upon peripheral behavior and can define performance criteria. The flexibility of the stack enables a designer to configure the silicon, directly bypassing the backbone if that level of control is desired.

One step up from the backbone is the Fusion applet, Level 2. The applet is an application building block that implements a specific function in FPGA gates. It can react to stimuli and board-level events coming through the backbone or from other sources, and responds to these stimuli by accessing and manipulating peripherals via the backbone or initiating some other action. An applet controls or responds to the peripheral(s). Applets can be easily imported or exported from the design environment. The applet structure is open and well-defined, enabling users to import applets from Microsemi, system developers, third parties, and user groups.

Note: Levels 1, 2, and 3 are implemented in FPGA logic gates.

Figure 2-1 • Fusion Architecture Stack

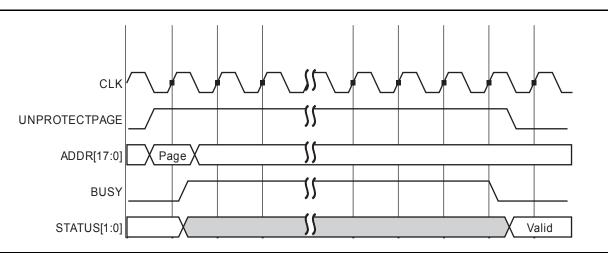

## **Unprotect Page Operation**

An Unprotect Page operation will clear the protection for a page addressed on the ADDR input. It is initiated by setting the UNPROTECTPAGE signal on the interface along with the page address on ADDR.

If the page is not in the Page Buffer, the Unprotect Page operation will copy the page into the Page Buffer. The Copy Page operation occurs only if the current page in the Page Buffer is not Page Loss Protected.

The waveform for an Unprotect Page operation is shown in Figure 2-42.

## Figure 2-42 • FB Unprotected Page Waveform

The Unprotect Page operation can incur the following error conditions:

- 1. If the copy of the page to the Page Buffer determines that the page has a single-bit correctable error in the data, it will report a STATUS = '01'.

- 2. If the address on ADDR does not match the address of the Page Buffer, PAGELOSSPROTECT is asserted, and the Page Buffer has been modified, then STATUS = '11' and the addressed page is not loaded into the Page Buffer.

- 3. If the copy of the page to the Page Buffer determines that at least one block in the page has a double-bit uncorrectable error, STATUS = '10' and the Page Buffer will contain the corrupted data.

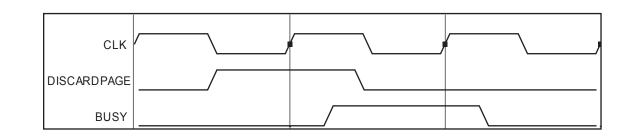

### **Discard Page Operation**

If the contents of the modified Page Buffer have to be discarded, the DISCARDPAGE signal should be asserted. This command results in the Page Buffer being marked as unmodified.

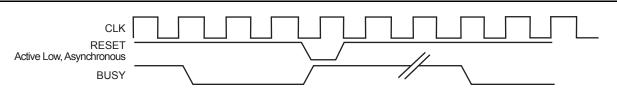

The timing for the operation is shown in Figure 2-43. The BUSY signal will remain asserted until the operation has completed.

Figure 2-43 • FB Discard Page Waveform

# Flash Memory Block Characteristics

## Figure 2-44 • Reset Timing Diagram

# Table 2-25 • Flash Memory Block TimingCommercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter                  | Description                                        | -2    | -1    | Std.  | Units |

|----------------------------|----------------------------------------------------|-------|-------|-------|-------|

| t                          | Clock-to-Q in 5-cycle read mode of the Read Data   | 7.99  | 9.10  | 10.70 | ns    |

| t <sub>CLK2RD</sub>        | Clock-to-Q in 6-cycle read mode of the Read Data   | 5.03  | 5.73  | 6.74  | ns    |

| +                          | Clock-to-Q in 5-cycle read mode of BUSY            | 4.95  | 5.63  | 6.62  | ns    |

| t <sub>CLK2BUSY</sub>      | Clock-to-Q in 6-cycle read mode of BUSY            | 4.45  | 5.07  | 5.96  | ns    |

| +                          | Clock-to-Status in 5-cycle read mode               | 11.24 | 12.81 | 15.06 | ns    |

| t <sub>CLK2STATUS</sub>    | Clock-to-Status in 6-cycle read mode               | 4.48  | 5.10  | 6.00  | ns    |

| t <sub>DSUNVM</sub>        | Data Input Setup time for the Control Logic        | 1.92  | 2.19  | 2.57  | ns    |

| t <sub>DHNVM</sub>         | Data Input Hold time for the Control Logic         | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>ASUNVM</sub>        | Address Input Setup time for the Control Logic     | 2.76  | 3.14  | 3.69  | ns    |

| t <sub>AHNVM</sub>         | Address Input Hold time for the Control Logic      | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUDWNVM</sub>       | Data Width Setup time for the Control Logic        | 1.85  | 2.11  | 2.48  | ns    |

| t <sub>HDDWNVM</sub>       | Data Width Hold time for the Control Logic         | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SURENNVM</sub>      | Read Enable Setup time for the Control Logic       | 3.85  | 4.39  | 5.16  | ns    |

| t <sub>HDRENNVM</sub>      | Read Enable Hold Time for the Control Logic        | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUWENNVM</sub>      | Write Enable Setup time for the Control Logic      | 2.37  | 2.69  | 3.17  | ns    |

| t <sub>HDWENNVM</sub>      | Write Enable Hold Time for the Control Logic       | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUPROGNVM</sub>     | Program Setup time for the Control Logic           | 2.16  | 2.46  | 2.89  | ns    |

| t <sub>HDPROGNVM</sub>     | Program Hold time for the Control Logic            | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUSPAREPAGE</sub>   | SparePage Setup time for the Control Logic         | 3.74  | 4.26  | 5.01  | ns    |

| t <sub>HDSPAREPAGE</sub>   | SparePage Hold time for the Control Logic          | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUAUXBLK</sub>      | Auxiliary Block Setup Time for the Control Logic   | 3.74  | 4.26  | 5.00  | ns    |

| t <sub>hdauxblk</sub>      | Auxiliary Block Hold Time for the Control Logic    | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SURDNEXT</sub>      | ReadNext Setup Time for the Control Logic          | 2.17  | 2.47  | 2.90  | ns    |

| t <sub>HDRDNEXT</sub>      | ReadNext Hold Time for the Control Logic           | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUERASEPG</sub>     | Erase Page Setup Time for the Control Logic        | 3.76  | 4.28  | 5.03  | ns    |

| t <sub>HDERASEPG</sub>     | Erase Page Hold Time for the Control Logic         | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUUNPROTECTPG</sub> | Unprotect Page Setup Time for the Control Logic    | 2.01  | 2.29  | 2.69  | ns    |

| t <sub>HDUNPROTECTPG</sub> | Unprotect Page Hold Time for the Control Logic     | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUDISCARDPG</sub>   | Discard Page Setup Time for the Control Logic      | 1.88  | 2.14  | 2.52  | ns    |

| t <sub>HDDISCARDPG</sub>   | Discard Page Hold Time for the Control Logic       | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUOVERWRPRO</sub>   | Overwrite Protect Setup Time for the Control Logic | 1.64  | 1.86  | 2.19  | ns    |

| t <sub>HDOVERWRPRO</sub>   | Overwrite Protect Hold Time for the Control Logic  | 0.00  | 0.00  | 0.00  | ns    |

Conversely, when writing 4-bit values and reading 9-bit values, the ninth bit of a read operation will be undefined. The RAM blocks employ little-endian byte order for read and write operations.

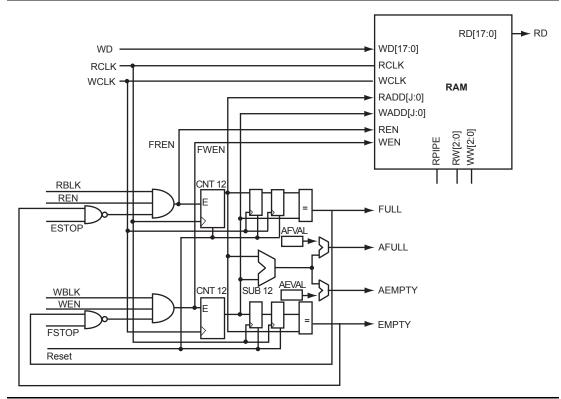

Figure 2-47 • Fusion RAM Block with Embedded FIFO Controller

## DINA and DINB

These are the input data signals, and they are nine bits wide. Not all nine bits are valid in all configurations. When a data width less than nine is specified, unused high-order signals must be grounded (Table 2-29).

## **DOUTA and DOUTB**

These are the nine-bit output data signals. Not all nine bits are valid in all configurations. As with DINA and DINB, high-order bits may not be used (Table 2-29). The output data on unused pins is undefined.

Table 2-29 • Unused/Used Input and Output Data Pins for Various Supported Bus Widths

| D×W   | DINx/[ | DOUTx |

|-------|--------|-------|

| DAW   | Unused | Used  |

| 4k×1  | [8:1]  | [0]   |

| 2k×2  | [8:2]  | [1:0] |

| 1k×4  | [8:4]  | [3:0] |

| 512×9 | None   | [8:0] |

Note: The "x" in DINx and DOUTx implies A or B.

## ADC Input Multiplexer

At the input to the Fusion ADC is a 32:1 multiplexer. Of the 32 input channels, up to 30 are user definable. Two of these channels are hardwired internally. Channel 31 connects to an internal temperature diode so the temperature of the Fusion device itself can be monitored. Channel 0 is wired to the FPGA's 1.5 V VCC supply, enabling the Fusion device to monitor its own power supply. Doing this internally makes it unnecessary to use an analog I/O to support these functions. The balance of the MUX inputs are connected to Analog Quads (see the "Analog Quad" section on page 2-80). Table 2-40 defines which Analog Quad inputs are associated with which specific analog MUX channels. The number of Analog Quads present is device-dependent; refer to the family list in the "Fusion Family" table on page I of this datasheet for the number of quads per device. Regardless of the number of quads populated in a device, the internal connections to both VCC and the internal temperature diode remain on Channels 0 and 31, respectively. To sample the internal temperature monitor, it must be strobed (similar to the AT pads). The TMSTBINT pin on the Analog Block macro is the control for strobing the internal temperature measurement diode.

To determine which channel is selected for conversion, there is a five-pin interface on the Analog Block, CHNUMBER[4:0], defined in Table 2-39.

| Channel Number | CHNUMBER[4:0] |

|----------------|---------------|

| 0              | 00000         |

| 1              | 00001         |

| 2              | 00010         |

| 3              | 00011         |

|                | · ·           |

|                |               |

|                |               |

| 30             | 11110         |

| 31             | 11111         |

### Table 2-39 • Channel Selection

Table 2-40 shows the correlation between the analog MUX input channels and the analog input pins.

## Table 2-40 • Analog MUX Channels

| Analog MUX Channel | Signal     | Analog Quad Number |

|--------------------|------------|--------------------|

| 0                  | Vcc_analog |                    |

| 1                  | AV0        |                    |

| 2                  | AC0        | Analog Quad 0      |

| 3                  | AT0        |                    |

| 4                  | AV1        |                    |

| 5                  | AC1        | Analog Quad 1      |

| 6                  | AT1        |                    |

| 7                  | AV2        |                    |

| 8                  | AC2        | Analog Quad 2      |

| 9                  | AT2        |                    |

| 10                 | AV3        |                    |

| 11                 | AC3        | Analog Quad 3      |

| 12                 | AT3        |                    |

| 13                 | AV4        |                    |

| 14                 | AC4        | Analog Quad 4      |

| 15                 | AT4        | 1                  |

## Table 2-49 • Analog Channel Specifications (continued)

#### Commercial Temperature Range Conditions, $T_J = 85^{\circ}C$ (unless noted otherwise), Typical: VCC33A = 3.3 V, VCC = 1.5 V

| Parameter           | Description              | Condition                                                            | Min. | Тур.     | Max. | Units |

|---------------------|--------------------------|----------------------------------------------------------------------|------|----------|------|-------|

| Digital Input u     | using Analog Pads AV, AC | and AT                                                               |      | <b>.</b> |      |       |

| VIND <sup>2,3</sup> | Input Voltage            | Refer to Table 3-2 on page 3-3                                       |      |          |      |       |

| VHYSDIN             | Hysteresis               |                                                                      |      | 0.3      |      | V     |

| VIHDIN              | Input High               |                                                                      |      | 1.2      |      | V     |

| VILDIN              | Input Low                |                                                                      |      | 0.9      |      | V     |

| VMPWDIN             | Minimum Pulse With       |                                                                      | 50   |          |      | ns    |

| F <sub>DIN</sub>    | Maximum Frequency        |                                                                      |      |          | 10   | MHz   |

| ISTBDIN             | Input Leakage Current    |                                                                      |      | 2        |      | μA    |

| IDYNDIN             | Dynamic Current          |                                                                      |      | 20       |      | μA    |

| t <sub>INDIN</sub>  | Input Delay              |                                                                      |      | 10       |      | ns    |

| Gate Driver O       | utput Using Analog Pad A | G                                                                    |      |          |      |       |

| VG                  | Voltage Range            | Refer to Table 3-2 on page 3-3                                       |      |          |      |       |

| IG                  | Output Current Drive     | High Current Mode <sup>6</sup> at 1.0 V                              |      |          | ±20  | mA    |

|                     |                          | Low Current Mode: ±1 µA                                              | 0.8  | 1.0      | 1.3  | μA    |

|                     |                          | Low Current Mode: ±3 µA                                              | 2.0  | 2.7      | 3.3  | μA    |

|                     |                          | Low Current Mode: ± 10 µA                                            | 7.4  | 9.0      | 11.5 | μA    |

|                     |                          | Low Current Mode: ± 30 µA                                            | 21.0 | 27.0     | 32.0 | μA    |

| IOFFG               | Maximum Off Current      |                                                                      |      |          | 100  | nA    |

| F <sub>G</sub>      | Maximum switching rate   | High Current Mode <sup>6</sup> at 1.0 V, 1 k $\Omega$ resistive load |      | 1.3      |      | MHz   |

|                     |                          | Low Current Mode:<br>±1 μA, 3 MΩ resistive load                      |      | 3        |      | KHz   |

|                     |                          | Low Current Mode:<br>±3 μA, 1 MΩ resistive load                      |      | 7        |      | KHz   |

|                     |                          | Low Current Mode: $\pm 10 \ \mu$ A, 300 k $\Omega$ resistive load    |      | 25       |      | KHz   |

|                     |                          | Low Current Mode: $\pm 30 \ \mu$ A, 105 k $\Omega$ resistive load    |      | 78       |      | KHz   |

Notes:

1. VRSM is the maximum voltage drop across the current sense resistor.

2. Analog inputs used as digital inputs can tolerate the same voltage limits as the corresponding analog pad. There is no reliability concern on digital inputs as long as VIND does not exceed these limits.

3. VIND is limited to VCC33A + 0.2 to allow reaching 10 MHz input frequency.

4. An averaging of 1,024 samples (LPF setting in Analog System Builder) is required and the maximum capacitance allowed across the AT pins is 500 pF.

5. The temperature offset is a fixed positive value.

6. The high current mode has a maximum power limit of 20 mW. Appropriate current limit resistors must be used, based on voltage on the pad.

7. When using SmartGen Analog System Builder, CalibIP is required to obtain specified offset. For further details on CalibIP, refer to the "Temperature, Voltage, and Current Calibration in Fusion FPGAs" chapter of the Fusion FPGA Fabric User Guide.

## Table 2-50 • ADC Characteristics in Direct Input Mode (continued)

Commercial Temperature Range Conditions,  $T_J = 85^{\circ}C$  (unless noted otherwise), Typical: VCC33A = 3.3 V, VCC = 1.5 V

| Parameter  | Description                  | Condition   | Min. | Тур.  | Max.  | Units |

|------------|------------------------------|-------------|------|-------|-------|-------|

| Dynamic Pe | erformance                   |             |      |       |       |       |

| SNR        | Signal-to-Noise Ratio        | 8-bit mode  | 48.0 | 49.5  |       | dB    |

|            |                              | 10-bit mode | 58.0 | 60.0  |       | dB    |

|            |                              | 12-bit mode | 62.9 | 64.5  |       | dB    |

| SINAD      | Signal-to-Noise Distortion   | 8-bit mode  | 47.6 | 49.5  |       | dB    |

|            |                              | 10-bit mode | 57.4 | 59.8  |       | dB    |

|            |                              | 12-bit mode | 62.0 | 64.2  |       | dB    |

| THD        | Total Harmonic<br>Distortion | 8-bit mode  |      | -74.4 | -63.0 | dBc   |

|            |                              | 10-bit mode |      | -78.3 | -63.0 | dBc   |

|            |                              | 12-bit mode |      | -77.9 | -64.4 | dBc   |

| ENOB       | Effective Number of Bits     | 8-bit mode  | 7.6  | 7.9   |       | bits  |

|            |                              | 10-bit mode | 9.5  | 9.6   |       | bits  |

|            |                              | 12-bit mode | 10.0 | 10.4  |       | bits  |

| Conversion | Rate                         |             |      |       |       |       |

|            | Conversion Time              | 8-bit mode  | 1.7  |       |       | μs    |

|            |                              | 10-bit mode | 1.8  |       |       | μs    |

|            |                              | 12-bit mode | 2    |       |       | μs    |

|            | Sample Rate                  | 8-bit mode  |      |       | 600   | Ksps  |

|            |                              | 10-bit mode |      |       | 550   | Ksps  |

|            |                              | 12-bit mode |      |       | 500   | Ksps  |

Notes:

1. Accuracy of the external reference is  $2.56 V \pm 4.6 mV$ .

2. Data is based on characterization.

3. The sample rate is time-shared among active analog inputs.

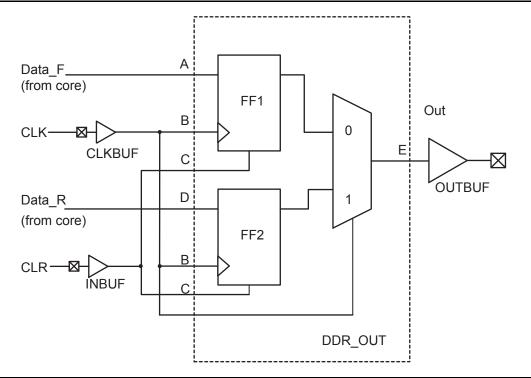

Figure 2-102 • DDR Output Support in Fusion Devices

## Table 2-96 • I/O Output Buffer Maximum Resistances <sup>1</sup> (continued)

| Standard                         | Drive Strength | R <sub>PULL-DOWN</sub><br>(ohms) <sup>2</sup> | R <sub>PULL-UP</sub><br>(ohms) <sup>3</sup> |

|----------------------------------|----------------|-----------------------------------------------|---------------------------------------------|

| Applicable to Standard I/O Banks |                |                                               |                                             |

| 3.3 V LVTTL / 3.3 V LVCMOS       | 2 mA           | 100                                           | 300                                         |

|                                  | 4 mA           | 100                                           | 300                                         |

|                                  | 6 mA           | 50                                            | 150                                         |

|                                  | 8 mA           | 50                                            | 150                                         |

| 2.5 V LVCMOS                     | 2 mA           | 100                                           | 200                                         |

|                                  | 4 mA           | 100                                           | 200                                         |

|                                  | 6 mA           | 50                                            | 100                                         |

|                                  | 8 mA           | 50                                            | 100                                         |

| 1.8 V LVCMOS                     | 2 mA           | 200                                           | 225                                         |

|                                  | 4 mA           | 100                                           | 112                                         |

| 1.5 V LVCMOS                     | 2 mA           | 200                                           | 224                                         |

Notes:

1. These maximum values are provided for informational reasons only. Minimum output buffer resistance values depend on VCC, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the Microsemi SoC Products Group website: http://www.microsemi.com/soc/techdocs/models/ibis.html.

2. R<sub>(PULL-DOWN-MAX)</sub> = VOLspec / I<sub>OLspec</sub>

3. R<sub>(PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / IOHspec

#### Table 2-97 • I/O Weak Pull-Up/Pull-Down Resistances Minimum and Maximum Weak Pull-Up/Pull-Down Resistance Values

|       | R <sub>(WEAK F</sub><br>(oh | PULL-UP)<br>ms) | R <sub>(WEAK PULL-DOWN)</sub> 2<br>(ohms) |       |  |

|-------|-----------------------------|-----------------|-------------------------------------------|-------|--|

| VCCI  | Min.                        | Max.            | Min.                                      | Max.  |  |

| 3.3 V | 10 k                        | 45 k            | 10 k                                      | 45 k  |  |

| 2.5 V | 11 k                        | 55 k            | 12 k                                      | 74 k  |  |

| 1.8 V | 18 k                        | 70 k            | 17 k                                      | 110 k |  |

| 1.5 V | 19 k                        | 90 k            | 19 k                                      | 140 k |  |

Notes:

R<sub>(WEAK PULL-UP-MAX)</sub> = (VCCImax – VOHspec) / I<sub>WEAK PULL-UP-MIN</sub>

R<sub>(WEAK PULL-DOWN-MAX)</sub> = VOLspec / I<sub>WEAK PULL-DOWN-MIN</sub>

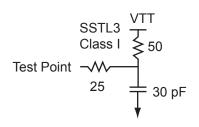

## SSTL3 Class I

Stub-Speed Terminated Logic for 3.3 V memory bus standard (JESD8-8). Fusion devices support Class I. This provides a differential amplifier input buffer and a push-pull output buffer.

Table 2-162 • Minimum and Maximum DC Input and Output Levels

| SSTL3 Class I     |           | VIL        | VIH        |           | VOL       | VOH        | IOL | IOH | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|-----------|------------|------------|-----------|-----------|------------|-----|-----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V  | Min.<br>V  | Max.<br>V | Max.<br>V | Min.<br>V  | mA  | mA  | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 14 mA             | -0.3      | VREF – 0.2 | VREF + 0.2 | 3.6       | 0.7       | VCCI – 1.1 | 14  | 14  | 54                      | 51                      | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

## Figure 2-132 • AC Loading

### Table 2-163 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.2    | VREF + 0.2     | 1.5                  | 1.5             | 1.485          | 30                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

### Timing Characteristics

Table 2-164 • SSTL3 Class I

```

Commercial Temperature Range Conditions: T_J = 70^{\circ}C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V, VREF = 1.5 V

```

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.31            | 0.04             | 1.25            | 0.43              | 2.35            | 1.84            |                 |                 | 4.59             | 4.07             | ns    |

| -1             | 0.56              | 1.96            | 0.04             | 1.06            | 0.36              | 2.00            | 1.56            |                 |                 | 3.90             | 3.46             | ns    |

| -2             | 0.49              | 1.72            | 0.03             | 0.93            | 0.32              | 1.75            | 1.37            |                 |                 | 3.42             | 3.04             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

## Input Register

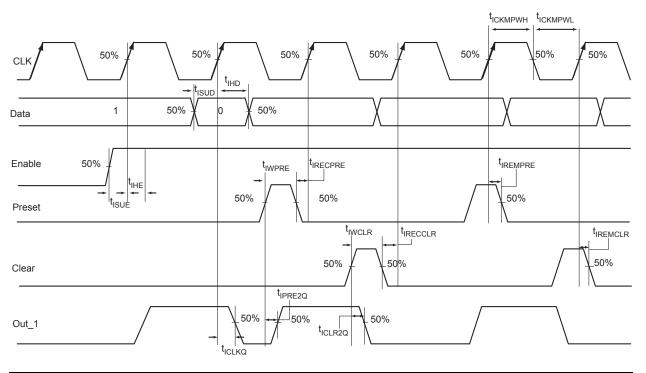

## Figure 2-139 • Input Register Timing Diagram

#### Timing Characteristics

# Table 2-176 • Input Data Register Propagation DelaysCommercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                         | -2   | -1   | Std. | Units |

|----------------------|---------------------------------------------------------------------|------|------|------|-------|

| t <sub>ICLKQ</sub>   | Clock-to-Q of the Input Data Register                               | 0.24 | 0.27 | 0.32 | ns    |

| t <sub>ISUD</sub>    | Data Setup Time for the Input Data Register                         | 0.26 | 0.30 | 0.35 | ns    |

| t <sub>IHD</sub>     | Data Hold Time for the Input Data Register                          | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ISUE</sub>    | Enable Setup Time for the Input Data Register                       | 0.37 | 0.42 | 0.50 | ns    |

| t <sub>IHE</sub>     | Enable Hold Time for the Input Data Register                        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ICLR2Q</sub>  | Asynchronous Clear-to-Q of the Input Data Register                  | 0.45 | 0.52 | 0.61 | ns    |

| t <sub>IPRE2Q</sub>  | Asynchronous Preset-to-Q of the Input Data Register                 | 0.45 | 0.52 | 0.61 | ns    |

| t <sub>IREMCLR</sub> | Asynchronous Clear Removal Time for the Input Data Register         | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>IRECCLR</sub> | Asynchronous Clear Recovery Time for the Input Data Register        | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>IREMPRE</sub> | Asynchronous Preset Removal Time for the Input Data Register        | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>IRECPRE</sub> | Asynchronous Preset Recovery Time for the Input Data Register       | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>IWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Input Data Register  | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>IWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Input Data Register | 0.22 | 0.25 | 0.30 | ns    |

| t <sub>ICKMPWH</sub> | Clock Minimum Pulse Width High for the Input Data Register          | 0.36 | 0.41 | 0.48 | ns    |

| t <sub>ICKMPWL</sub> | Clock Minimum Pulse Width Low for the Input Data Register           | 0.32 | 0.37 | 0.43 | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

## Methodology

## Total Power Consumption—PTOTAL

## Operating Mode, Standby Mode, and Sleep Mode

$P_{TOTAL} = P_{STAT} + P_{DYN}$

P<sub>STAT</sub> is the total static power consumption.

P<sub>DYN</sub> is the total dynamic power consumption.

## Total Static Power Consumption—P<sub>STAT</sub>

## **Operating Mode**

$\label{eq:pstat} \begin{array}{l} \mathsf{P}_{\mathsf{STAT}} = \mathsf{PDC1} + (\mathsf{N}_{\mathsf{NVM-BLOCKS}} * \mathsf{PDC4}) + \mathsf{PDC5} + (\mathsf{N}_{\mathsf{QUADS}} * \mathsf{PDC6}) + (\mathsf{N}_{\mathsf{INPUTS}} * \mathsf{PDC7}) + (\mathsf{N}_{\mathsf{OUTPUTS}} * \mathsf{PDC8}) + (\mathsf{N}_{\mathsf{PLLS}} * \mathsf{PDC9}) \end{array}$

$N_{\ensuremath{\mathsf{NVM}}\xspace-BLOCKS}$  is the number of NVM blocks available in the device.

N<sub>QUADS</sub> is the number of Analog Quads used in the design.

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

N<sub>OUTPUTS</sub> is the number of I/O output buffers used in the design.

N<sub>PLLS</sub> is the number of PLLs available in the device.

## Standby Mode

P<sub>STAT</sub> = PDC2

## Sleep Mode

$P_{STAT} = PDC3$

## Total Dynamic Power Consumption—P<sub>DYN</sub>

### **Operating Mode**

P<sub>DYN</sub> = P<sub>CLOCK</sub> + P<sub>S-CELL</sub> + P<sub>C-CELL</sub> + P<sub>NET</sub> + P<sub>INPUTS</sub> + P<sub>OUTPUTS</sub> + P<sub>MEMORY</sub> + P<sub>PLL</sub> + P<sub>NVM</sub>+ P<sub>XTL-OSC</sub> + P<sub>RC-OSC</sub> + P<sub>AB</sub>

## Standby Mode

$P_{DYN} = P_{XTL-OSC}$

Sleep Mode

$P_{DYN} = 0 W$

## Global Clock Dynamic Contribution—P<sub>CLOCK</sub>

## **Operating Mode**

$P_{CLOCK} = (PAC1 + N_{SPINE} * PAC2 + N_{ROW} * PAC3 + N_{S-CELL} * PAC4) * F_{CLK}$

N<sub>SPINE</sub> is the number of global spines used in the user design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *Fusion and Extended Temperature Fusion FPGA Fabric User's Guide*.

N<sub>ROW</sub> is the number of VersaTile rows used in the design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *Fusion and Extended Temperature Fusion FPGA Fabric User's Guide*.

$\mathsf{F}_{\mathsf{CLK}}$  is the global clock signal frequency.

N<sub>S-CELL</sub> is the number of VersaTiles used as sequential modules in the design.

### Standby Mode and Sleep Mode

$P_{CLOCK} = 0 W$

## Sequential Cells Dynamic Contribution—P<sub>S-CELL</sub>

## **Operating Mode**

## Total Static Power Consumption—PSTAT

Number of Quads used:  $N_{QUADS} = 4$ Number of NVM blocks available (AFS600):  $N_{NVM-BLOCKS} = 2$ Number of input pins used:  $N_{INPUTS} = 30$ Number of output pins used:  $N_{OUTPUTS} = 40$

## **Operating Mode**

$\mathsf{P}_{\mathsf{STAT}} = \mathsf{PDC1} + (\mathsf{N}_{\mathsf{NVM-BLOCKS}} * \mathsf{PDC4}) + \mathsf{PDC5} + (\mathsf{N}_{\mathsf{QUADS}} * \mathsf{PDC6}) + (\mathsf{N}_{\mathsf{INPUTS}} * \mathsf{PDC7}) + (\mathsf{N}_{\mathsf{OUTPUTS}} * \mathsf{PDC8})$

P<sub>STAT</sub> = 7.50 mW + (2 \* 1.19 mW) + 8.25 mW + (4 \* 3.30 mW) + (30 \* 0.00) + (40 \* 0.00)

P<sub>STAT</sub> = 31.33 mW

### Standby Mode

P<sub>STAT</sub> = PDC2

$P_{STAT} = 0.03 \text{ mW}$

### Sleep Mode

$P_{STAT} = PDC3$

$P_{STAT} = 0.03 \text{ mW}$

## Total Power Consumption—PTOTAL

In operating mode, the total power consumption of the device is 174.39 mW:

$P_{TOTAL} = P_{STAT} + P_{DYN}$

P<sub>TOTAL</sub> = 143.06 mW + 31.33 mW

P<sub>TOTAL</sub> = 174.39 mW

In standby mode, the total power consumption of the device is limited to 0.66 mW:

$P_{TOTAL} = P_{STAT} + P_{DYN}$

$P_{TOTAL} = 0.03 \text{ mW} + 0.63 \text{ mW}$

$P_{TOTAL} = 0.66 \text{ mW}$

In sleep mode, the total power consumption of the device drops as low as 0.03 mW:

$P_{TOTAL} = P_{STAT} + P_{DYN}$  $P_{TOTAL} = 0.03 \text{ mW}$

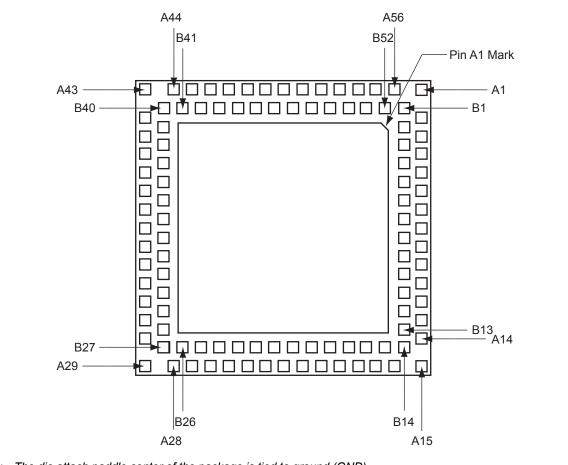

# 4 – Package Pin Assignments

# **QN108**

Note: The die attach paddle center of the package is tied to ground (GND).

## Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/default.aspx.

Package Pin Assignments

|            | QN180           |                 |

|------------|-----------------|-----------------|

| Pin Number | AFS090 Function | AFS250 Function |

| C21        | AG2             | AG2             |

| C22        | NC              | NC              |

| C23        | NC              | NC              |

| C24        | NC              | NC              |

| C25        | NC              | AT5             |

| C26        | GNDAQ           | GNDAQ           |

| C27        | NC              | NC              |

| C28        | NC              | NC              |

| C29        | NC              | NC              |

| C30        | NC              | NC              |

| C31        | GND             | GND             |

| C32        | NC              | NC              |

| C33        | NC              | NC              |

| C34        | NC              | NC              |

| C35        | GND             | GND             |

| C36        | GDB0/IO39NPB1V0 | GDA0/IO54NPB1V0 |

| C37        | GDA1/IO37NSB1V0 | GDC0/IO52NSB1V0 |

| C38        | GCA0/IO36NDB1V0 | GCA0/IO49NDB1V0 |

| C39        | GCB1/IO35PPB1V0 | GCB1/IO48PPB1V0 |

| C40        | GND             | GND             |

| C41        | GCA2/IO32NPB1V0 | IO41NPB1V0      |

| C42        | GBB2/IO31NDB1V0 | IO40NDB1V0      |

| C43        | NC              | NC              |

| C44        | NC              | GBA1/IO39RSB0V0 |

| C45        | NC              | GBB0/IO36RSB0V0 |

| C46        | GND             | GND             |

| C47        | NC              | IO30RSB0V0      |

| C48        | IO22RSB0V0      | IO27RSB0V0      |

| C49        | GND             | GND             |

| C50        | IO13RSB0V0      | IO16RSB0V0      |

| C51        | IO09RSB0V0      | IO12RSB0V0      |

| C52        | IO06RSB0V0      | IO09RSB0V0      |

| C53        | GND             | GND             |

| C54        | NC              | GAB1/IO03RSB0V0 |

| C55        | NC              | GAA0/IO00RSB0V0 |

| C56        | NC              | NC              |

|            | QN180           |                 |

|------------|-----------------|-----------------|

| Pin Number | AFS090 Function | AFS250 Function |

| D1         | NC              | NC              |

| D2         | NC              | NC              |

| D3         | NC              | NC              |

| D4         | NC              | NC              |

|            |                 | FG256           |                 |                  |

|------------|-----------------|-----------------|-----------------|------------------|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |

| K9         | VCC             | VCC             | VCC             | VCC              |

| K10        | GND             | GND             | GND             | GND              |

| K11        | NC              | GDC2/IO57PPB1V0 | GDC2/IO57PPB2V0 | GDC2/IO84PPB2V0  |

| K12        | GND             | GND             | GND             | GND              |

| K13        | NC              | GDA0/IO54NDB1V0 | GDA0/IO54NDB2V0 | GDA0/IO81NDB2V0  |

| K14        | NC              | GDA2/IO55PPB1V0 | GDA2/IO55PPB2V0 | GDA2/IO82PPB2V0  |

| K15        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |

| K16        | NC              | GDB1/IO53PPB1V0 | GDB1/IO53PPB2V0 | GDB1/IO80PPB2V0  |

| L1         | NC              | GEC1/IO63PDB3V0 | GEC1/IO63PDB4V0 | GEC1/IO90PDB4V0  |

| L2         | NC              | GEC0/IO63NDB3V0 | GEC0/IO63NDB4V0 | GEC0/IO90NDB4V0  |

| L3         | NC              | GEB1/IO62PDB3V0 | GEB1/IO62PDB4V0 | GEB1/IO89PDB4V0  |

| L4         | NC              | GEB0/IO62NDB3V0 | GEB0/IO62NDB4V0 | GEB0/IO89NDB4V0  |

| L5         | NC              | IO60NDB3V0      | IO60NDB4V0      | IO87NDB4V0       |

| L6         | NC              | GEC2/IO60PDB3V0 | GEC2/IO60PDB4V0 | GEC2/IO87PDB4V0  |

| L7         | GNDA            | GNDA            | GNDA            | GNDA             |

| L8         | AC0             | AC0             | AC2             | AC2              |

| L9         | AV2             | AV2             | AV4             | AV4              |

| L10        | AC3             | AC3             | AC5             | AC5              |

| L11        | PTEM            | PTEM            | PTEM            | PTEM             |

| L12        | TDO             | TDO             | TDO             | TDO              |

| L13        | VJTAG           | VJTAG           | VJTAG           | VJTAG            |

| L14        | NC              | IO57NPB1V0      | IO57NPB2V0      | IO84NPB2V0       |

| L15        | GDB2/IO41PPB1V0 | GDB2/IO56PPB1V0 | GDB2/IO56PPB2V0 | GDB2/IO83PPB2V0  |

| L16        | NC              | IO55NPB1V0      | IO55NPB2V0      | IO82NPB2V0       |

| M1         | GND             | GND             | GND             | GND              |

| M2         | NC              | GEA1/IO61PDB3V0 | GEA1/IO61PDB4V0 | GEA1/IO88PDB4V0  |

| M3         | NC              | GEA0/IO61NDB3V0 | GEA0/IO61NDB4V0 | GEA0/IO88NDB4V0  |

| M4         | VCCIB3          | VCCIB3          | VCCIB4          | VCCIB4           |

| M5         | NC              | IO58NPB3V0      | IO58NPB4V0      | IO85NPB4V0       |

| M6         | NC              | NC              | AV0             | AV0              |

| M7         | NC              | NC              | AC1             | AC1              |

| M8         | AG1             | AG1             | AG3             | AG3              |

| M9         | AC2             | AC2             | AC4             | AC4              |

| M10        | AC4             | AC4             | AC6             | AC6              |

| M11        | NC              | AG5             | AG7             | AG7              |

| M12        | VPUMP           | VPUMP           | VPUMP           | VPUMP            |

| M13        | VCCIB1          | VCCIB1          | VCCIB2          | VCCIB2           |

| M14        | TMS             | TMS             | TMS             | TMS              |

| Revision                       | Changes                                                                                                                                                                                                                                           | Page  |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Advance v1.0<br>(January 2008) | All Timing Characteristics tables were updated. For the Differential I/O Standards, the Standard I/O support tables are new.                                                                                                                      | N/A   |

|                                | Table 2-3 • Array Coordinates was updated to change the max x and y values                                                                                                                                                                        | 2-9   |

|                                | Table 2-12 • Fusion CCC/PLL Specification was updated.                                                                                                                                                                                            | 2-31  |

|                                | A note was added to Table 2-16 · RTC ACM Memory Map.                                                                                                                                                                                              | 2-37  |

|                                | A reference to the Peripheral's User's Guide was added to the "Voltage Regulator<br>Power Supply Monitor (VRPSM)" section.                                                                                                                        | 2-42  |

|                                | In Table 2-25 • Flash Memory Block Timing, the commercial conditions were updated.                                                                                                                                                                | 2-55  |

|                                | In Table 2-26 • FlashROM Access Time, the commercial conditions were missing and have been added below the title of the table.                                                                                                                    | 2-58  |

|                                | In Table 2-36 • Analog Block Pin Description, the function description was updated for the ADCRESET.                                                                                                                                              | 2-82  |

|                                | In the "Voltage Monitor" section, the following sentence originally had $\pm$ 10% and it was changed to +10%.                                                                                                                                     | 2-86  |

|                                | The Analog Quad inputs are tolerant up to 12 V + 10%.                                                                                                                                                                                             |       |

|                                | In addition, this statement was deleted from the datasheet:                                                                                                                                                                                       |       |

|                                | Each I/O will draw power when connected to power (3 mA at 3 V).                                                                                                                                                                                   |       |

|                                | The "Terminology" section is new.                                                                                                                                                                                                                 | 2-88  |

|                                | The "Current Monitor" section was significantly updated. Figure 2-72 • Timing Diagram for Current Monitor Strobe to Figure 2-74 • Negative Current Monitor and Table 2-37 • Recommended Resistor for Different Current Range Measurement are new. | 2-90  |

|                                | The "ADC Description" section was updated to add the "Terminology" section.                                                                                                                                                                       | 2-93  |

|                                | In the "Gate Driver" section, 25 mA was changed to 20 mA and 1.5 MHz was changed to 1.3 MHz. In addition, the following sentence was deleted:<br>The maximum AG pad switching frequency is 1.25 MHz.                                              | 2-94  |

|                                | The "Temperature Monitor" section was updated to rewrite most of the text and add Figure 2-78, Figure 2-79, and Table 2-38 • Temperature Data Format.                                                                                             | 2-96  |

|                                | In Table 2-38 • Temperature Data Format, the temperature K column was changed for 85°C from 538 to 358.                                                                                                                                           | 2-98  |

|                                | In Table 2-45 • ADC Interface Timing, "Typical-Case" was changed to "Worst-Case."                                                                                                                                                                 | 2-110 |

|                                | The "ADC Interface Timing" section is new.                                                                                                                                                                                                        | 2-110 |

|                                | Table 2-46 • Analog Channel Specifications was updated.                                                                                                                                                                                           | 2-118 |

|                                | The "V <sub>CC15A</sub> Analog Power Supply (1.5 V)" section was updated.                                                                                                                                                                         | 2-224 |

|                                | The "V <sub>CCPLA/B</sub> PLL Supply Voltage" section is new.                                                                                                                                                                                     | 2-225 |

|                                | In " $V_{CCNVM}$ Flash Memory Block Power Supply (1.5 V)" section, supply was changed to supply input.                                                                                                                                            | 2-224 |

|                                | The "V <sub>CCPLA/B</sub> PLL Supply Voltage" pin description was updated to include the following statement:                                                                                                                                     | 2-225 |

|                                | Actel recommends tying VCCPLX to VCC and using proper filtering circuits to decouple $\rm V_{CC}$ noise from PLL.                                                                                                                                 |       |

|                                | The "V <sub>COMPLA/B</sub> Ground for West and East PLL" section was updated.                                                                                                                                                                     | 2-225 |

| Revision                    | Changes                                                                                                                                                                                  | Page  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Advance v0.6<br>(continued) | The "Analog-to-Digital Converter Block" section was updated with the following statement:<br>"All results are MSB justified in the ADC."                                                 | 2-99  |

|                             | The information about the ADCSTART signal was updated in the "ADC Description" section.                                                                                                  | 2-102 |

|                             | Table 2-46 · Analog Channel Specifications was updated.                                                                                                                                  | 2-118 |

|                             | Table 2-47 · ADC Characteristics in Direct Input Mode was updated.                                                                                                                       | 2-121 |

|                             | Table 2-51 • ACM Address Decode Table for Analog Quad was updated.                                                                                                                       | 2-127 |

|                             | In Table 2-53 • Analog Quad ACM Byte Assignment, the Function and Default Setting for Bit 6 in Byte 3 was updated.                                                                       | 2-130 |

|                             | The "Introduction" section was updated to include information about digital inputs, outputs, and bibufs.                                                                                 | 2-133 |

|                             | In Table 2-69 • Fusion Pro I/O Features, the programmable delay descriptions were updated for the following features:<br>Single-ended receiver                                           | 2-137 |

|                             | Voltage-referenced differential receiver                                                                                                                                                 |       |

|                             | LVDS/LVPECL differential receiver features                                                                                                                                               |       |

|                             | The "User I/O Naming Convention" section was updated to include "V" and "z" descriptions                                                                                                 | 2-159 |

|                             | The "VCC33PMP Analog Power Supply (3.3 V)" section was updated to include information about avoiding high current draw.                                                                  | 2-224 |

|                             | The "VCCNVM Flash Memory Block Power Supply (1.5 V)" section was updated to include information about avoiding high current draw.                                                        | 2-224 |

|                             | The "VMVx I/O Supply Voltage (quiet)" section was updated to include this statement: VMV and VCCI must be connected to the same power supply and $V_{CCI}$ pins within a given I/O bank. | 2-185 |

|                             | The "PUB Push Button" section was updated to include information about leaving the pin floating if it is not used.                                                                       | 2-228 |

|                             | The "PTBASE Pass Transistor Base" section was updated to include information about leaving the pin floating if it is not used.                                                           | 2-228 |

|                             | The "PTEM Pass Transistor Emitter" section was updated to include information about leaving the pin floating if it is not used.                                                          | 2-228 |

|                             | The heading was incorrect in the "208-Pin PQFP" table. It should be AFS250 and not AFS090.                                                                                               | 3-8   |