Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                    |

|--------------------------------|---------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | 110592                                                                    |

| Number of I/O                  | 172                                                                       |

| Number of Gates                | 600000                                                                    |

| Voltage - Supply               | 1.425V ~ 1.575V                                                           |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                                           |

| Package / Case                 | 484-BGA                                                                   |

| Supplier Device Package        | 484-FPBGA (23x23)                                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/p1afs600-2fg484 |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Temperature Grade Offerings**

| Fusion Devices        | AFS090 | AFS250                | AFS600                | AFS1500                |

|-----------------------|--------|-----------------------|-----------------------|------------------------|

| ARM Cortex-M1 Devices |        | M1AFS250              |                       | M1AFS1500              |

| Pigeon Point Devices  |        |                       | P1AFS600 <sup>3</sup> | P1AFS1500 3            |

| MicroBlade Devices    |        | U1AFS250 <sup>4</sup> | U1AFS600 <sup>4</sup> | U1AFS1500 <sup>4</sup> |

| QN108 <sup>5</sup>    | C, I   | -                     | -                     | -                      |

| QN180 <sup>5</sup>    | C, I   | C, I                  | -                     | -                      |

| PQ208                 | -      | C, I                  | C, I                  | -                      |

| FG256                 | C, I   | C, I                  | C, I                  | C, I                   |

| FG484                 | -      | -                     | C, I                  | C, I                   |

| FG676                 | -      | _                     | -                     | C, I                   |

|                       |        |                       |                       |                        |

Notes:

1. C = Commercial Temperature Range: 0°C to 85°C Junction

2. I = Industrial Temperature Range: -40°C to 100°C Junction

3. Pigeon Point devices are only offered in FG484 and FG256.

4. MicroBlade devices are only offered in FG256.

5. Package not available.

# **Speed Grade and Temperature Grade Matrix**

|                | Std. <sup>1</sup> | -1           | -2 <sup>2</sup> |

|----------------|-------------------|--------------|-----------------|

| C <sup>3</sup> | $\checkmark$      | $\checkmark$ | $\checkmark$    |

| l <sup>4</sup> | $\checkmark$      | $\checkmark$ | $\checkmark$    |

Notes:

1. MicroBlade devices are only offered in standard speed grade.

2. Pigeon Point devices are only offered in –2 speed grade.

3. C = Commercial Temperature Range: 0°C to 85°C Junction

4. I = Industrial Temperature Range: -40°C to 100°C Junction

Contact your local Microsemi SoC Products Group representative for device availability:

http://www.microsemi.com/index.php?option=com\_content&id=137&lang=en&view=article.

# **Cortex-M1, Pigeon Point, and MicroBlade Fusion Device** Information

This datasheet provides information for all Fusion (AFS), Cortex-M1 (M1), Pigeon Point (P1), and MicroBlade (U1) devices. The remainder of the document will only list the Fusion (AFS) devices. Please apply relevant information to M1, P1, and U1 devices when appropriate. Please note the following:

- Cortex-M1 devices are offered in the same speed grades and packages as basic Fusion devices.

- Pigeon Point devices are only offered in –2 speed grade and FG484 and FG256 packages.

- MicroBlade devices are only offered in standard speed grade and the FG256 package.

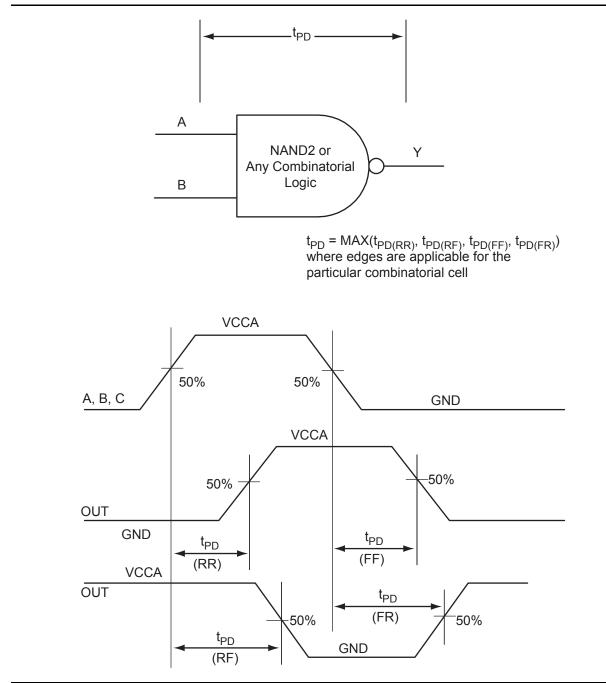

Figure 2-4 • Combinatorial Timing Model and Waveforms

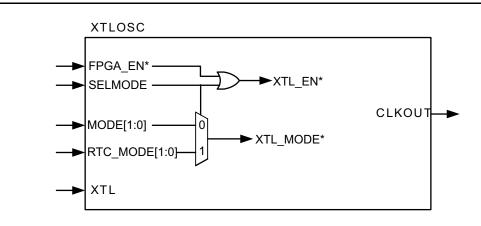

# **Crystal Oscillator**

The Crystal Oscillator (XTLOSC) is source that generates the clock from an external crystal. The output of XTLOSC CLKOUT signal can be selected as an input to the PLL. Refer to the "Clock Conditioning Circuits" section for more details. The XTLOSC can operate in normal operations and Standby mode (RTC is running and 1.5 V is not present).

In normal operation, the internal FPGA\_EN signal is '1' as long as 1.5 V is present for VCC. As such, the internal enable signal, XTL\_EN, for Crystal Oscillator is enabled since FPGA\_EN is asserted. The XTL\_MODE has the option of using MODE or RTC\_MODE, depending on SELMODE.

During Standby, 1.5 V is not available, as such, and FPGA\_EN is '0'. SELMODE must be asserted in order for XTL\_EN to be enabled; hence XTL\_MODE relies on RTC\_MODE. SELMODE and RTC\_MODE must be connected to RTCXTLSEL and RTCXTLMODE from the AB respectively for correct operation during Standby (refer to the "Real-Time Counter System" section on page 2-31 for a detailed description).

The Crystal Oscillator can be configured in one of four modes:

- RC network, 32 KHz to 4 MHz

- Low gain, 32 to 200 KHz

- Medium gain, 0.20 to 2.0 MHz

- High gain, 2.0 to 20.0 MHz

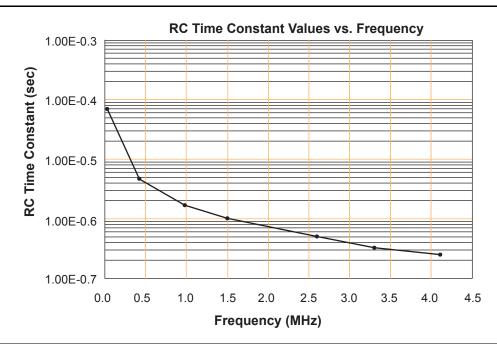

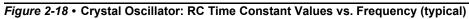

In RC network mode, the XTAL1 pin is connected to an RC circuit, as shown in Figure 2-16 on page 2-18. The XTAL2 pin should be left floating. The RC value can be chosen based on Figure 2-18 for any desired frequency between 32 KHz and 4 MHz. The RC network mode can also accommodate an external clock source on XTAL1 instead of an RC circuit.

In Low gain, Medium gain, and High gain, an external crystal component or ceramic resonator can be added onto XTAL1 and XTAL2, as shown in Figure 2-16 on page 2-18. In the case where the Crystal Oscillator block is not used, the XTAL1 pin should be connected to GND and the XTAL2 pin should be left floating.

Note: \*Internal signal—does not exist in macro.

Figure 2-17 • XTLOSC Macro

| Signal Name   | Width | Direction | Function                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                         |  |  |

|---------------|-------|-----------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|

| XTL_EN*       | 1     |           | Enables the                                                         | Enables the crystal. Active high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                         |  |  |

| XTL_MODE*     | 2     |           | Settings for                                                        | the crystal clock for different from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | equency.                                                |  |  |

|               |       |           | Value                                                               | Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Frequency Range                                         |  |  |

|               |       |           | b'00                                                                | RC network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32 KHz to 4 MHz                                         |  |  |

|               |       |           | b'01                                                                | Low gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32 to 200 KHz                                           |  |  |

|               |       |           | b'10                                                                | Medium gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0.20 to 2.0 MHz                                         |  |  |

|               |       |           | b'11                                                                | High gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.0 to 20.0 MHz                                         |  |  |

| SELMODE       | 1     | IN        |                                                                     | source of XTL_MODE and a TLSEL from AB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Iso enables the XTL_EN. Connect                         |  |  |

|               |       |           | 0                                                                   | For normal operation or sl<br>FPGA_EN, XTL_MODE depe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | eep mode, XTL_EN depends on nds on MODE                 |  |  |

|               |       |           | 1                                                                   | For Standby mode, XTL_EN i<br>RTC_MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | s enabled, XTL_MODE depends on                          |  |  |

| RTC_MODE[1:0] | 2     | IN        |                                                                     | the crystal clock for different find the second sec | requency ranges. XTL_MODE uses                          |  |  |

| MODE[1:0]     | 2     | IN        |                                                                     | the crystal clock for different find sELMODE is '0'. In Standby,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | requency ranges. XTL_MODE uses MODE inputs will be 0's. |  |  |

| FPGA_EN*      | 1     | IN        | 0 when 1.5 V is not present for VCC 1 when 1.5 V is present for VCC |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                         |  |  |

| XTL           | 1     | IN        | Crystal Clock source                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                         |  |  |

| CLKOUT        | 1     | OUT       | Crystal Cloo                                                        | ck output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                         |  |  |

Table 2-10 • XTLOSC Signals Descriptions

*Note:* \*Internal signal—does not exist in macro.

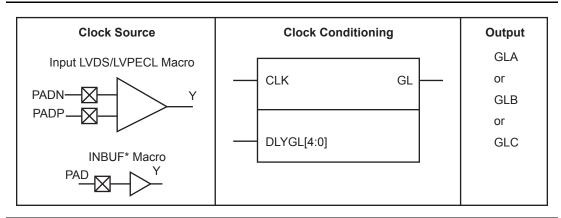

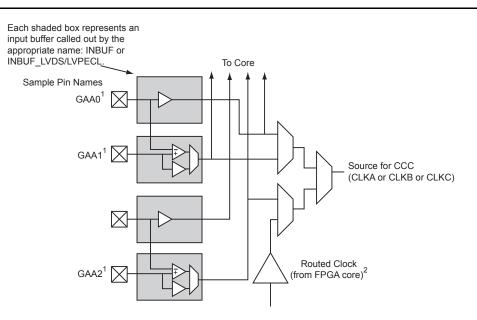

Figure 2-21 • Fusion CCC Options: Global Buffers with Programmable Delay

## **Global Input Selections**

Each global buffer, as well as the PLL reference clock, can be driven from one of the following (Figure 2-22):

- 3 dedicated single-ended I/Os using a hardwired connection

- 2 dedicated differential I/Os using a hardwired connection

- The FPGA core

GAA[0:2]: GA represents global in the northwest corner of the device. A[0:2]: designates specific A clock source.

#### Notes:

- 1. Represents the global input pins. Globals have direct access to the clock conditioning block and are not routed via the FPGA fabric. Refer to the "User I/O Naming Convention" section on page 2-158 for more information.

- 2. Instantiate the routed clock source input as follows:

- a) Connect the output of a logic element to the clock input of the PLL, CLKDLY, or CLKINT macro. b) Do not place a clock source I/O (INBUF or INBUF\_LVPECL/LVDS) in a relevant global pin location.

- 3. LVDS-based clock sources are available in the east and west banks on all Fusion devices.

#### Figure 2-22 • Clock Input Sources Including CLKBUF, CLKBUF\_LVDS/LVPECL, and CLKINT

#### **Timing Characteristics**

#### Table 2-31 • RAM4K9

#### Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                                                                         | -2   | -1   | Std. | Units |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                  | 0.25 | 0.28 | 0.33 | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                   | 0.00 | 0.00 | 0.00 | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                 | 0.14 | 0.16 | 0.19 | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                  | 0.10 | 0.11 | 0.13 | ns    |

| t <sub>BKS</sub>      | BLK setup time                                                                                                      | 0.23 | 0.27 | 0.31 | ns    |

| t <sub>BKH</sub>      | BL hold time                                                                                                        | 0.02 | 0.02 | 0.02 | ns    |

| t <sub>DS</sub>       | Input data (DIN) setup time                                                                                         | 0.18 | 0.21 | 0.25 | ns    |

| t <sub>DH</sub>       | Input data (DIN) hold time                                                                                          | 0.00 | 0.00 | 0.00 | ns    |

| +                     | Clock High to new data valid on DOUT (output retained, WMODE = 0)                                                   | 1.79 | 2.03 | 2.39 | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on DOUT (flow-through, WMODE = 1)                                                      | 2.36 | 2.68 | 3.15 | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on DOUT (pipelined)                                                                    | 0.89 | 1.02 | 1.20 | ns    |

| t <sub>C2CWWH</sub> 1 | Address collision clk-to-clk delay for reliable write after write on same address—Applicable to Rising Edge         | 0.30 | 0.26 | 0.23 | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address—Applicable to Opening Edge  | 0.45 | 0.38 | 0.34 | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address— Applicable to Opening Edge | 0.49 | 0.42 | 0.37 | ns    |

| 1                     | RESET Low to data out Low on DOUT (flow-through)                                                                    | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to Data Out Low on DOUT (pipelined)                                                                       | 0.92 | 1.05 | 1.23 | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                       | 0.29 | 0.33 | 0.38 | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                      | 1.50 | 1.71 | 2.01 | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                           | 0.21 | 0.24 | 0.29 | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                    | 3.23 | 3.68 | 4.32 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                   | 310  | 272  | 231  | MHz   |

Notes:

1. For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

2. For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

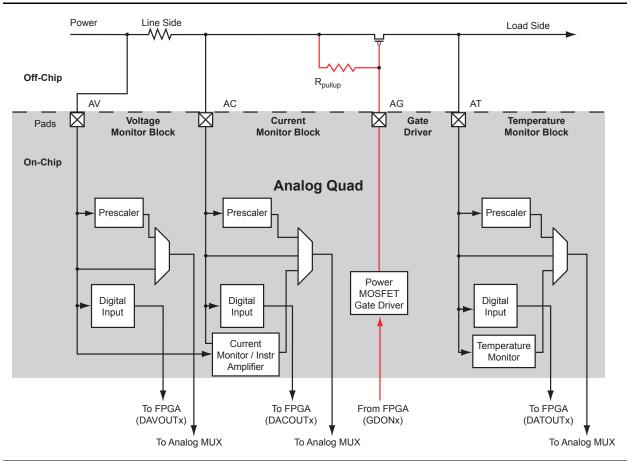

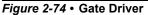

## Gate Driver

The Fusion Analog Quad includes a Gate Driver connected to the Quad's AG pin (Figure 2-74). Designed to work with external p- or n-channel MOSFETs, the Gate driver is a configurable current sink or source and requires an external pull-up or pull-down resistor. The AG supports 4 selectable gate drive levels: 1  $\mu$ A, 3  $\mu$ A, 10  $\mu$ A, and 30  $\mu$ A (Figure 2-75 on page 2-91). The AG also supports a High Current Drive mode in which it can sink 20 mA; in this mode the switching rate is approximately 1.3 MHz with 100 ns turn-on time and 600 ns turn-off time. Modeled on an open-drain-style output, it does not output a voltage level without an appropriate pull-up or pull-down resistor. If 1 V is forced on the drain, the current sinking/sourcing will exceed the ability of the transistor, and the device could be damaged.

The AG pad is turned on via the corresponding GDONx pin in the Analog Block macro, where x is the number of the corresponding Analog Quad for the AG pad to be enabled (GDON0 to GDON9).

The gate-to-source voltage ( $V_{gs}$ ) of the external MOSFET is limited to the programmable drive current times the external pull-up or pull-down resistor value (EQ 5).

$$V_{gs} \le I_g \times (R_{pullup} \text{ or } R_{pulldown})$$

EQ 5

## ADC Terminology

#### **Conversion Time**

Conversion time is the interval between the release of the hold state (imposed by the input circuitry of a track-and-hold) and the instant at which the voltage on the sampling capacitor settles to within one LSB of a new input value.

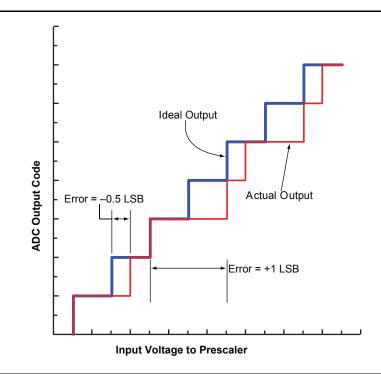

#### DNL – Differential Non-Linearity

For an ideal ADC, the analog-input levels that trigger any two successive output codes should differ by one LSB (DNL = 0). Any deviation from one LSB in defined as DNL (Figure 2-83).

Figure 2-83 • Differential Non-Linearity (DNL)

#### **ENOB – Effective Number of Bits**

ENOB specifies the dynamic performance of an ADC at a specific input frequency and sampling rate. An ideal ADC's error consists only of quantization of noise. As the input frequency increases, the overall noise (particularly in the distortion components) also increases, thereby reducing the ENOB and SINAD (also see "Signal-to-Noise and Distortion Ratio (SINAD)".) ENOB for a full-scale, sinusoidal input waveform is computed using EQ 12.

$$ENOB = \frac{SINAD - 1.76}{6.02}$$

EQ 12

#### FS Error – Full-Scale Error

Full-scale error is the difference between the actual value that triggers that transition to full-scale and the ideal analog full-scale transition value. Full-scale error equals offset error plus gain error.

#### INL – Integral Non-Linearity

INL is the deviation of an actual transfer function from a straight line. After nullifying offset and gain errors, the straight line is either a best-fit straight line or a line drawn between the end points of the transfer function (Figure 2-85).

Figure 2-85 • Integral Non-Linearity (INL)

#### LSB – Least Significant Bit

In a binary number, the LSB is the least weighted bit in the group. Typically, the LSB is the furthest right bit. For an ADC, the weight of an LSB equals the full-scale voltage range of the converter divided by  $2^N$ , where N is the converter's resolution.

EQ 13 shows the calculation for a 10-bit ADC with a unipolar full-scale voltage of 2.56 V:

EQ 13

#### **No Missing Codes**

An ADC has no missing codes if it produces all possible digital codes in response to a ramp signal applied to the analog input.

# Table 2-50 • ADC Characteristics in Direct Input ModeCommercial Temperature Range Conditions, TJ = 85°C (unless noted otherwise),Typical: VCC33A = 3.3 V, VCC = 1.5 V

| Parameter   | Description                                     | Condition                         | Min.  | Тур.   | Max.          | Units    |

|-------------|-------------------------------------------------|-----------------------------------|-------|--------|---------------|----------|

| Direct Inpu | t using Analog Pad AV, AC, A                    | T                                 |       |        |               |          |

| VINADC      | Input Voltage (Direct Input)                    | Refer to Table 3-2 on page 3-3    |       |        |               |          |

| CINADC      | Input Capacitance                               | Channel not selected              |       | 7      |               | pF       |

|             |                                                 | Channel selected but not sampling |       | 8      |               | pF       |

|             |                                                 | Channel selected and sampling     |       | 18     |               | pF       |

| ZINADC      | Input Impedance                                 | 8-bit mode                        |       | 2      |               | kΩ       |

|             |                                                 | 10-bit mode                       |       | 2      |               | kΩ       |

|             |                                                 | 12-bit mode                       |       | 2      |               | kΩ       |

| Analog Ref  | erence Voltage VAREF                            |                                   |       |        |               |          |

| VAREF       | Accuracy                                        | T <sub>J</sub> = 25°C             | 2.537 | 2.56   | 2.583         | V        |

|             | Temperature Drift of<br>Internal Reference      |                                   |       | 65     |               | ppm / °C |

|             | External Reference                              |                                   | 2.527 |        | VCC33A + 0.05 | V        |

| ADC Accur   | acy (using external reference                   | ) <sup>1,2</sup>                  | 1     |        | I             |          |

| DC Accura   |                                                 |                                   |       |        |               |          |

| TUE         | Total Unadjusted Error                          | 8-bit mode                        |       | 0.3    | 29            | LSB      |

|             |                                                 | 10-bit mode                       |       | 0.     | 72            | LSB      |

|             |                                                 | 12-bit mode                       |       | 1.     | .8            | LSB      |

| INL         | Integral Non-Linearity                          | 8-bit mode                        |       | 0.20   | 0.25          | LSB      |

|             |                                                 | 10-bit mode                       |       | 0.32   | 0.43          | LSB      |

|             |                                                 | 12-bit mode                       |       | 1.71   | 1.80          | LSB      |

| DNL         | Differential Non-Linearity<br>(no missing code) | 8-bit mode                        |       | 0.20   | 0.24          | LSB      |

|             |                                                 | 10-bit mode                       |       | 0.60   | 0.65          | LSB      |

|             |                                                 | 12-bit mode                       |       | 2.40   | 2.48          | LSB      |

|             | Offset Error                                    | 8-bit mode                        |       | 0.01   | 0.17          | LSB      |

|             | ]                                               | 10-bit mode                       |       | 0.05   | 0.20          | LSB      |

|             | ]                                               | 12-bit mode                       |       | 0.20   | 0.40          | LSB      |

|             | Gain Error                                      | 8-bit mode                        |       | 0.0004 | 0.003         | LSB      |

|             | ]                                               | 10-bit mode                       |       | 0.002  | 0.011         | LSB      |

|             | ]                                               | 12-bit mode                       |       | 0.007  | 0.044         | LSB      |

|             | Gain Error (with internal reference)            | All modes                         |       | 2      |               | % FSR    |

#### Notes:

1. Accuracy of the external reference is 2.56 V  $\pm$  4.6 mV.

2. Data is based on characterization.

3. The sample rate is time-shared among active analog inputs.

## **Timing Characteristics**

# Table 2-55 • Analog Configuration Multiplexer (ACM) TimingCommercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter               | Description                                        | -2    | -1    | Std.  | Units |

|-------------------------|----------------------------------------------------|-------|-------|-------|-------|

| t <sub>CLKQACM</sub>    | Clock-to-Q of the ACM                              | 19.73 | 22.48 | 26.42 | ns    |

| t <sub>SUDACM</sub>     | Data Setup time for the ACM                        | 4.39  | 5.00  | 5.88  | ns    |

| t <sub>HDACM</sub>      | Data Hold time for the ACM                         | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUAACM</sub>     | Address Setup time for the ACM                     | 4.73  | 5.38  | 6.33  | ns    |

| t <sub>HAACM</sub>      | Address Hold time for the ACM                      | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>SUEACM</sub>     | Enable Setup time for the ACM                      | 3.93  | 4.48  | 5.27  | ns    |

| t <sub>HEACM</sub>      | Enable Hold time for the ACM                       | 0.00  | 0.00  | 0.00  | ns    |

| t <sub>MPWARACM</sub>   | Asynchronous Reset Minimum Pulse Width for the ACM | 10.00 | 10.00 | 10.00 | ns    |

| t <sub>REMARACM</sub>   | Asynchronous Reset Removal time for the ACM        | 12.98 | 14.79 | 17.38 | ns    |

| t <sub>RECARACM</sub>   | Asynchronous Reset Recovery time for the ACM       | 12.98 | 14.79 | 17.38 | ns    |

| t <sub>MPWCLKACM</sub>  | Clock Minimum Pulse Width for the ACM              | 45.00 | 45.00 | 45.00 | ns    |

| t <sub>FMAXCLKACM</sub> | lock Maximum Frequency for the ACM                 | 10.00 | 10.00 | 10.00 | MHz   |

# Features Supported on Pro I/Os

Table 2-72 lists all features supported by transmitter/receiver for single-ended and differential I/Os.

#### Table 2-72 • Fusion Pro I/O Features

| Feature                                             | Description                                                                                                                                                                                           |     |  |  |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| Single-ended and voltage-<br>referenced transmitter | Hot insertion in every mode except PCI or 5 V input tolerant (these modes u clamp diodes and do not allow hot insertion)                                                                              | ise |  |  |

| features                                            | Activation of hot insertion (disabling the clamp diode) is selectable by I/Os.                                                                                                                        |     |  |  |

|                                                     | Weak pull-up and pull-down                                                                                                                                                                            |     |  |  |

|                                                     | Two slew rates                                                                                                                                                                                        |     |  |  |

|                                                     | Skew between output buffer enable/disable time: 2 ns delay (rising edge) a 0 ns delay (falling edge); see "Selectable Skew between Output Buf Enable/Disable Time" on page 2-149 for more information |     |  |  |

|                                                     | Five drive strengths                                                                                                                                                                                  |     |  |  |

|                                                     | 5 V-tolerant receiver ("5 V Input Tolerance" section on page 2-144)                                                                                                                                   |     |  |  |

|                                                     | LVTTL/LVCMOS 3.3 V outputs compatible with 5 V TTL inputs ("5 V Outputs Tolerance" section on page 2-148)                                                                                             | out |  |  |

|                                                     | igh performance (Table 2-76 on page 2-143)                                                                                                                                                            |     |  |  |

| Single-ended receiver features                      | Schmitt trigger option                                                                                                                                                                                |     |  |  |

|                                                     | ESD protection                                                                                                                                                                                        |     |  |  |

|                                                     | Programmable delay: 0 ns if bypassed, 0.625 ns with '000' setting, 6.575 with '111' setting, 0.85-ns intermediate delay increments (at $25^{\circ}$ C, 1.5 V)                                         | ns  |  |  |

|                                                     | High performance (Table 2-76 on page 2-143)                                                                                                                                                           |     |  |  |

|                                                     | Separate ground planes, GND/GNDQ, for input buffers only to avoid outp induced noise in the input circuitry                                                                                           | ut- |  |  |

| Voltage-referenced differential receiver features   | Programmable Delay: 0 ns if bypassed, 0.625 ns with '000' setting, 6.575 with '111' setting, 0.85-ns intermediate delay increments (at $25^{\circ}$ C, 1.5 V)                                         | ns  |  |  |

|                                                     | High performance (Table 2-76 on page 2-143)                                                                                                                                                           |     |  |  |

|                                                     | Separate ground planes, GND/GNDQ, for input buffers only to avoid outp induced noise in the input circuitry                                                                                           | ut- |  |  |

| CMOS-style LVDS, BLVDS,<br>M-LVDS, or LVPECL        | Two I/Os and external resistors are used to provide a CMOS-style LVE BLVDS, M-LVDS, or LVPECL transmitter solution.                                                                                   | )S, |  |  |

| transmitter                                         | Activation of hot insertion (disabling the clamp diode) is selectable by I/Os.                                                                                                                        |     |  |  |

|                                                     | Weak pull-up and pull-down                                                                                                                                                                            |     |  |  |

|                                                     | Fast slew rate                                                                                                                                                                                        |     |  |  |

| LVDS/LVPECL differential                            | ESD protection                                                                                                                                                                                        |     |  |  |

| receiver features                                   | High performance (Table 2-76 on page 2-143)                                                                                                                                                           |     |  |  |

|                                                     | Programmable delay: 0.625 ns with '000' setting, 6.575 ns with '111' settin<br>0.85-ns intermediate delay increments (at 25°C, 1.5 V)                                                                 | ng, |  |  |

|                                                     | Separate input buffer ground and power planes to avoid output-induced no in the input circuitry                                                                                                       | ise |  |  |

Device Architecture

#### Table 2-77 • Comparison Table for 5 V–Compliant Receiver Scheme

| Scheme | Board Components                                                                                                                                                           | Speed                    | Current Limitations                                                                                                                                                                                                                                                                                                                          |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | Two resistors                                                                                                                                                              | Low to high <sup>1</sup> | Limited by transmitter's drive strength                                                                                                                                                                                                                                                                                                      |

| 2      | Resistor and Zener 3.3 V                                                                                                                                                   | Medium                   | Limited by transmitter's drive strength                                                                                                                                                                                                                                                                                                      |

| 3      | Bus switch                                                                                                                                                                 | High                     | N/A                                                                                                                                                                                                                                                                                                                                          |

| 4      | Minimum resistor value <sup>2</sup><br>R = 47 $\Omega$ at T <sub>J</sub> = 70°C<br>R = 150 $\Omega$ at T <sub>J</sub> = 85°C<br>R = 420 $\Omega$ at T <sub>J</sub> = 100°C | Medium                   | Maximum diode current at 100% duty cycle, signal constantly at<br>'1'<br>52.7 mA at $T_J = 70^{\circ}C / 10$ -year lifetime<br>16.5 mA at $T_J = 85^{\circ}C / 10$ -year lifetime<br>5.9 mA at $T_J = 100^{\circ}C / 10$ -year lifetime<br>For duty cycles other than 100%, the currents can be increased<br>by a factor = 1 / (duty cycle). |

|        |                                                                                                                                                                            |                          | Example: 20% duty cycle at 70°C<br>Maximum current = (1 / 0.2) * 52.7 mA = 5 * 52.7 mA = 263.5 mA                                                                                                                                                                                                                                            |

Notes:

1. Speed and current consumption increase as the board resistance values decrease.

2. Resistor values ensure I/O diode long-term reliability.

Device Architecture

#### Table 2-81 • Fusion Pro I/O Default Attributes

| I/O Standards           | SLEW<br>(output only)                                     | OUT_DRIVE<br>(output only)                          | SKEW (tribuf and bibuf only) | RES_PULL | OUT_LOAD (output only) | COMBINE_REGISTER | IN_DELAY (input only) | IN_DELAY_VAL (input only) | SCHMITT_TRIGGER (input only) |

|-------------------------|-----------------------------------------------------------|-----------------------------------------------------|------------------------------|----------|------------------------|------------------|-----------------------|---------------------------|------------------------------|

| LVTTL/LVCMO<br>S 3.3 V  | Refer to the following<br>tables for more<br>information: | Refer to the following tables for more information: | Off                          | None     | 35 pF                  | -                | Off                   | 0                         | Off                          |

| LVCMOS 2.5 V            | Table 2-78 on page 2-152                                  | Table 2-78 on page 2-152                            | Off                          | None     | 35 pF                  | —                | Off                   | 0                         | Off                          |

| LVCMOS<br>2.5/5.0 V     | Table 2-79 on page 2-152   Table 2-80 on page 2-152       | Table 2-79 on page 2-152   Table 2-80 on page 2-152 | Off                          | None     | 35 pF                  | -                | Off                   | 0                         | Off                          |

| LVCMOS 1.8 V            | Table 2-00 off page 2-102                                 |                                                     | Off                          | None     | 35 pF                  | -                | Off                   | 0                         | Off                          |

| LVCMOS 1.5 V            |                                                           |                                                     | Off                          | None     | 35 pF                  | _                | Off                   | 0                         | Off                          |

| PCI (3.3 V)             |                                                           |                                                     | Off                          | None     | 10 pF                  | -                | Off                   | 0                         | Off                          |

| PCI-X (3.3 V)           |                                                           |                                                     | Off                          | None     | 10 pF                  | -                | Off                   | 0                         | Off                          |

| GTL+ (3.3 V)            |                                                           |                                                     | Off                          | None     | 10 pF                  | -                | Off                   | 0                         | Off                          |

| GTL+ (2.5 V)            |                                                           |                                                     | Off                          | None     | 10 pF                  | -                | Off                   | 0                         | Off                          |

| GTL (3.3 V)             |                                                           |                                                     | Off                          | None     | 10 pF                  | -                | Off                   | 0                         | Off                          |

| GTL (2.5 V)             |                                                           |                                                     | Off                          | None     | 10 pF                  | -                | Off                   | 0                         | Off                          |

| HSTL Class I            |                                                           |                                                     | Off                          | None     | 20 pF                  | -                | Off                   | 0                         | Off                          |

| HSTL Class II           |                                                           |                                                     | Off                          | None     | 20 pF                  | -                | Off                   | 0                         | Off                          |

| SSTL2<br>Class I and II |                                                           |                                                     | Off                          | None     | 30 pF                  | -                | Off                   | 0                         | Off                          |

| SSTL3<br>Class I and II |                                                           |                                                     | Off                          | None     | 30 pF                  | -                | Off                   | 0                         | Off                          |

| LVDS, BLVDS,<br>M-LVDS  |                                                           |                                                     | Off                          | None     | 0 pF                   | -                | Off                   | 0                         | Off                          |

| LVPECL                  |                                                           |                                                     | Off                          | None     | 0 pF                   | -                | Off                   | 0                         | Off                          |

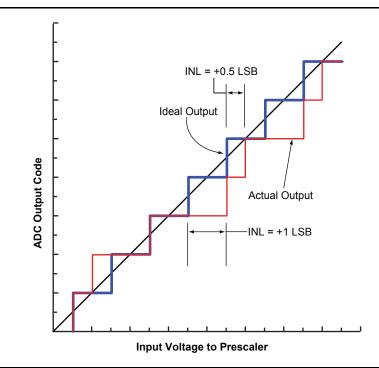

*Figure 2-118* • Tristate Output Buffer Timing Model and Delays (example)

Device Architecture

## **Output DDR**

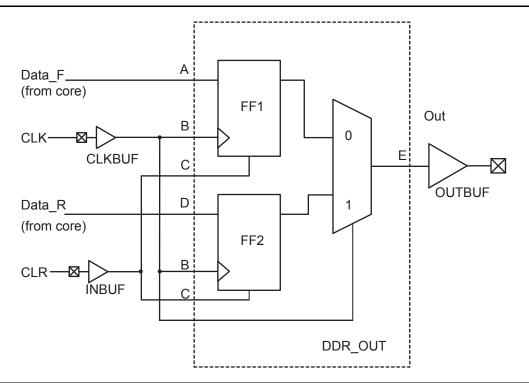

## Figure 2-144 • Output DDR Timing Model

### Table 2-181 • Parameter Definitions

| Parameter Name          | Parameter Definition      | Measuring Nodes (From, To) |

|-------------------------|---------------------------|----------------------------|

| t <sub>DDROCLKQ</sub>   | Clock-to-Out              | B, E                       |

| t <sub>DDROCLR2Q</sub>  | Asynchronous Clear-to-Out | C, E                       |

| t <sub>DDROREMCLR</sub> | Clear Removal             | С, В                       |

| t <sub>DDRORECCLR</sub> | Clear Recovery            | С, В                       |

| t <sub>DDROSUD1</sub>   | Data Setup Data_F         | A, B                       |

| t <sub>DDROSUD2</sub>   | Data Setup Data_R         | D, B                       |

| t <sub>DDROHD1</sub>    | Data Hold Data_F          | A, B                       |

| t <sub>DDROHD2</sub>    | Data Hold Data_R          | D, B                       |

|            | QN180           |                 |            | QN180           |                 |

|------------|-----------------|-----------------|------------|-----------------|-----------------|

| Pin Number | AFS090 Function | AFS250 Function | Pin Number | AFS090 Function | AFS250 Function |

| B9         | XTAL2           | XTAL2           | B45        | GBA2/IO31PDB1V0 | GBA2/IO40PDB1V0 |

| B10        | GEA0/IO44NDB3V0 | GFA0/IO66NDB3V0 | B46        | GNDQ            | GNDQ            |

| B11        | GEB2/IO42PDB3V0 | IO60NDB3V0      | B47        | GBA1/IO30RSB0V0 | GBA0/IO38RSB0V0 |

| B12        | VCC             | VCC             | B48        | GBB1/IO28RSB0V0 | GBC1/IO35RSB0V0 |