Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                     |

|--------------------------------|----------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | -                                                                          |

| Total RAM Bits                 | 110592                                                                     |

| Number of I/O                  | 172                                                                        |

| Number of Gates                | 600000                                                                     |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 484-BGA                                                                    |

| Supplier Device Package        | 484-FPBGA (23x23)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/p1afs600-2fg484i |

|                                |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The system application, Level 3, is the larger user application that utilizes one or more applets. Designing at the highest level of abstraction supported by the Fusion technology stack, the application can be easily created in FPGA gates by importing and configuring multiple applets.

In fact, in some cases an entire FPGA system design can be created without any HDL coding.

An optional MCU enables a combination of software and HDL-based design methodologies. The MCU can be on-chip or off-chip as system requirements dictate. System portioning is very flexible, allowing the MCU to reside above the applets or to absorb applets, or applets and backbone, if desired.

The Fusion technology stack enables a very flexible design environment. Users can engage in design across a continuum of abstraction from very low to very high.

## **Core Architecture**

### VersaTile

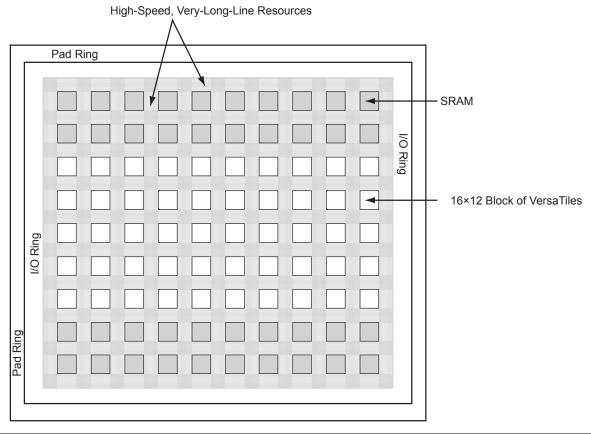

Based upon successful ProASIC3/E logic architecture, Fusion devices provide granularity comparable to gate arrays. The Fusion device core consists of a sea-of-VersaTiles architecture.

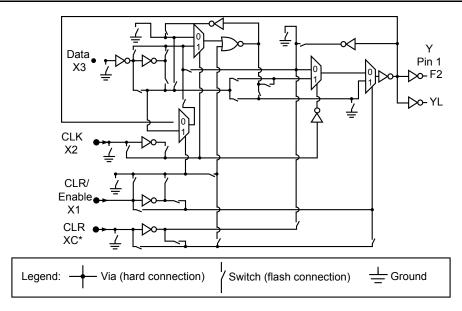

As illustrated in Figure 2-2, there are four inputs in a logic VersaTile cell, and each VersaTile can be configured using the appropriate flash switch connections:

- Any 3-input logic function

- Latch with clear or set

- · D-flip-flop with clear or set

- Enable D-flip-flop with clear or set (on a 4th input)

VersaTiles can flexibly map the logic and sequential gates of a design. The inputs of the VersaTile can be inverted (allowing bubble pushing), and the output of the tile can connect to high-speed, very-long-line routing resources. VersaTiles and larger functions are connected with any of the four levels of routing hierarchy.

When the VersaTile is used as an enable D-flip-flop, the SET/CLR signal is supported by a fourth input, which can only be routed to the core cell over the VersaNet (global) network.

The output of the VersaTile is F2 when the connection is to the ultra-fast local lines, or YL when the connection is to the efficient long-line or very-long-line resources (Figure 2-2).

*Note:* \*This input can only be connected to the global clock distribution network.

Figure 2-2 • Fusion Core VersaTile

Figure 2-10 • Very-Long-Line Resources

#### Notes:

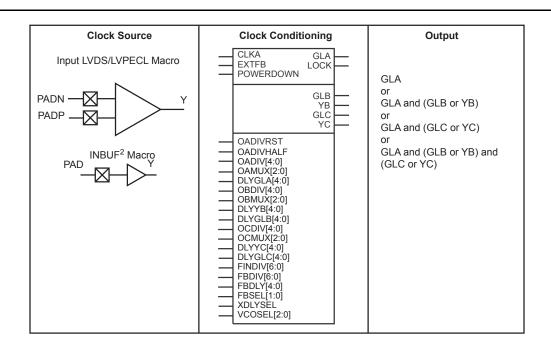

- 1. Visit the Microsemi SoC Products Group website for application notes concerning dynamic PLL reconfiguration. Refer to the "PLL Macro" section on page 2-27 for signal descriptions.

- 2. Many specific INBUF macros support the wide variety of single-ended and differential I/O standards for the Fusion family.

- 3. Refer to the IGLOO, ProASIC3, SmartFusion and Fusion Macro Library Guide for more information.

### Figure 2-19 • Fusion CCC Options: Global Buffers with the PLL Macro

### Table 2-11 • Available Selections of I/O Standards within CLKBUF and CLKBUF\_LVDS/LVPECL Macros

| CLKBUF Macros                |

|------------------------------|

| CLKBUF_LVCMOS5               |

| CLKBUF_LVCMOS33 <sup>1</sup> |

| CLKBUF_LVCMOS18              |

| CLKBUF_LVCMOS15              |

| CLKBUF_PCI                   |

| CLKBUF_LVDS <sup>2</sup>     |

| CLKBUF_LVPECL                |

Notes:

1. This is the default macro. For more details, refer to the IGLOO, ProASIC3, SmartFusion and Fusion Macro Library Guide.

2. The B-LVDS and M-LVDS standards are supported with CLKBUF\_LVDS.

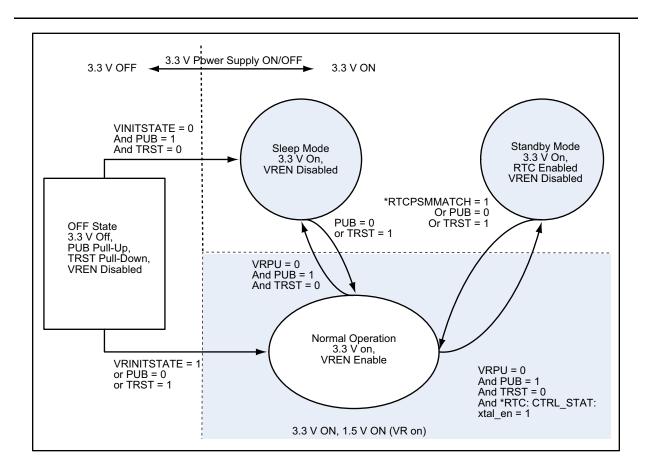

#### Figure 2-31 • State Diagram for All Different Power Modes

When TRST is 1 or PUB is 0, the 1.5 V voltage regulator is always ON, putting the Fusion device in normal operation at all times. Therefore, when the JTAG port is not in reset, the Fusion device cannot enter sleep mode or standby mode.

To enter standby mode, the Fusion device must first power-up into normal operation. The RTC is enabled through the RTC Control/Status Register described in the "Real-Time Counter (part of AB macro)" section on page 2-33. A match value corresponding to the wake-up time is loaded into the Match Register. The 1.5 V voltage regulator is disabled by setting VRPU to 0 to allow the Fusion device to enter standby mode, when the 1.5 V supply is off but the RTC remains on.

### 1.5 V Voltage Regulator

The 1.5 V voltage regulator uses an external pass transistor to generate 1.5 V from a 3.3 V supply. The base of the pass transistor is tied to PTBASE, the collector is tied to 3.3 V, and an emitter is tied to PTBASE and the 1.5 V supplies of the Fusion device. Figure 2-27 on page 2-31 shows the hook-up of the 1.5 V voltage regulator to an external pass transistor.

Microsemi recommends using a PN2222A or 2N2222A transistor. The gain of such a transistor is approximately 25, with a maximum base current of 20 mA. The maximum current that can be supported is 0.5 A. Transistors with different gain can also be used for different current requirements.

### Table 2-18 • Electrical Characteristics

| Symbol  | Parameter         | Condition |                           | Min   | Typical | Max   | Units |

|---------|-------------------|-----------|---------------------------|-------|---------|-------|-------|

| VOUT    | Output Voltage    | Tj = 25°C |                           | 1.425 | 1.5     | 1.575 | V     |

| ICC33A  | Operation Current | Tj = 25⁰C | ILOAD = 1 mA              |       | 11      |       | mA    |

|         |                   |           | ILOAD = 100 mA            |       | 11      |       | mA    |

|         |                   |           | ILOAD = 0.5 A             |       | 30      |       | mA    |

| ∆VOUT   | Load Regulation   | Tj = 25°C | ILOAD = 1 mA to 0.5 A     |       | 90      |       | mV    |

|         | Line Regulation   | Tj = 25°C | VCC33A = 2.97 V to 3.63 V |       |         |       |       |

|         |                   |           | ILOAD = 1 mA              |       | 10.6    |       | mV/V  |

|         |                   |           | VCC33A = 2.97 V to 3.63 V |       |         |       |       |

|         |                   |           | ILOAD = 100 mA            |       | 12.1    |       | mV/V  |

| ∆VOUT   |                   |           | VCC33A = 2.97 V to 3.63 V |       |         |       |       |

|         |                   |           | ILOAD = 500 mA            |       | 10.6    |       | mV/V  |

|         | Dropout Voltage*  | Tj = 25⁰C | ILOAD = 1 mA              |       | 0.63    |       | V     |

|         |                   |           | ILOAD = 100 mA            |       | 0.84    |       | V     |

|         |                   |           | ILOAD = 0.5 A             |       | 1.35    |       | V     |

| IPTBASE | PTBase Current    | Tj = 25°C | ILOAD = 1 mA              |       | 48      |       | μA    |

|         |                   |           | ILOAD = 100 mA            |       | 736     |       | μA    |

|         |                   |           | ILOAD = 0.5 A             |       | 12      | 20    | mA    |

### VCC33A = 3.3 V

Note: \*Data collected with 2N2222A.

### **Program Operation**

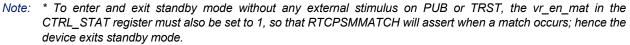

A Program operation is initiated by asserting the PROGRAM signal on the interface. Program operations save the contents of the Page Buffer to the FB Array. Due to the technologies inherent in the FB, the total programming (including erase) time per page of the eNVM is 6.8 ms. While the FB is writing the data to the array, the BUSY signal will be asserted.

During a Program operation, the sector and page addresses on ADDR are compared with the stored address for the page (and sector) in the Page Buffer. If there is a mismatch between the two addresses, the Program operation will be aborted and an error will be reported on the STATUS output.

It is possible to write the Page Buffer to a different page in memory. When asserting the PROGRAM pin, if OVERWRITEPAGE is asserted as well, the FB will write the contents of the Page Buffer to the sector and page designated on the ADDR inputs if the destination page is not Overwrite Protected.

A Program operation can be utilized to either modify the contents of the page in the flash memory block or change the protections for the page. Setting the OVERWRITEPROTECT bit on the interface while asserting the PROGRAM pin will put the page addressed into Overwrite Protect Mode. Overwrite Protect Mode safeguards a page from being inadvertently overwritten during subsequent Program or Erase operations.

Program operations that result in a STATUS value of '01' do not modify the addressed page. For all other values of STATUS, the addressed page is modified. Program errors include the following:

- 1. Attempting to program a page that is Overwrite Protected (STATUS = '01')

- 2. Attempting to program a page that is not in the Page Buffer when the Page Buffer has entered Page Loss Protection Mode (STATUS = '01')

- Attempting to perform a program with OVERWRITEPAGE set when the page addressed has been Overwrite Protected (STATUS = '01')

- 4. The Write Count of the page programmed exceeding the Write Threshold defined in the part specification (STATUS = '11')

- 5. The ECC Logic determining that there is an uncorrectable error within the programmed page (STATUS = '10')

- 6. Attempting to program a page that is **not** in the Page Buffer when OVERWRITEPAGE is not set and the page in the Page Buffer is modified (STATUS = '01')

- 7. Attempting to program the page in the Page Buffer when the Page Buffer is **not** modified

The waveform for a Program operation is shown in Figure 2-36.

### Figure 2-36 • FB Program Waveform

Note: OVERWRITEPAGE is only sampled when the PROGRAM or ERASEPAGE pins are asserted. OVERWRITEPAGE is ignored in all other operations.

# Table 2-25 • Flash Memory Block Timing (continued)Commercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter                  | Description                                                            | -2     | -1    | Std.  | Units |

|----------------------------|------------------------------------------------------------------------|--------|-------|-------|-------|

| t <sub>SUPGLOSSPRO</sub>   | Page Loss Protect Setup Time for the Control Logic                     | 1.69   | 1.93  | 2.27  | ns    |

| t <sub>HDPGLOSSPRO</sub>   | Page Loss Protect Hold Time for the Control Logic                      | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>SUPGSTAT</sub>      | Page Status Setup Time for the Control Logic                           | 2.49   | 2.83  | 3.33  | ns    |

| t <sub>HDPGSTAT</sub>      | Page Status Hold Time for the Control Logic                            | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>SUOVERWRPG</sub>    | Over Write Page Setup Time for the Control Logic                       | 1.88   | 2.14  | 2.52  | ns    |

| t <sub>HDOVERWRPG</sub>    | Over Write Page Hold Time for the Control Logic                        | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>SULOCKREQUEST</sub> | Lock Request Setup Time for the Control Logic                          | 0.87   | 0.99  | 1.16  | ns    |

| t <sub>HDLOCKREQUEST</sub> | Lock Request Hold Time for the Control Logic                           | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>RECARNVM</sub>      | Reset Recovery Time                                                    | 0.94   | 1.07  | 1.25  | ns    |

| t <sub>REMARNVM</sub>      | Reset Removal Time                                                     | 0.00   | 0.00  | 0.00  | ns    |

| t <sub>MPWARNVM</sub>      | Asynchronous Reset Minimum Pulse Width for the Control Logic           | 10.00  | 12.50 | 12.50 | ns    |

| t <sub>MPWCLKNVM</sub>     | Clock Minimum Pulse Width for the Control Logic                        | 4.00   | 5.00  | 5.00  | ns    |

|                            | Maximum Frequency for Clock for the Control Logic – for AFS1500/AFS600 | 80.00  | 80.00 | 80.00 | MHz   |

| <sup>I</sup> FMAXCLKNVM    | Maximum Frequency for Clock for the Control Logic – for AFS250/AFS090  | 100.00 | 80.00 | 80.00 | MHz   |

### FlashROM

Fusion devices have 1 kbit of on-chip nonvolatile flash memory that can be read from the FPGA core fabric. The FlashROM is arranged in eight banks of 128 bits during programming. The 128 bits in each bank are addressable as 16 bytes during the read-back of the FlashROM from the FPGA core (Figure 2-45).

The FlashROM can only be programmed via the IEEE 1532 JTAG port. It cannot be programmed directly from the FPGA core. When programming, each of the eight 128-bit banks can be selectively reprogrammed. The FlashROM can only be reprogrammed on a bank boundary. Programming involves an automatic, on-chip bank erase prior to reprogramming the bank. The FlashROM supports a synchronous read and can be read on byte boundaries. The upper three bits of the FlashROM address from the FPGA core define the bank that is being accessed. The lower four bits of the FlashROM address from the FPGA core define which of the 16 bytes in the bank is being accessed.

The maximum FlashROM access clock is given in Table 2-26 on page 2-54. Figure 2-46 shows the timing behavior of the FlashROM access cycle—the address has to be set up on the rising edge of the clock for DOUT to be valid on the next falling edge of the clock.

If the address is unchanged for two cycles:

- D0 becomes invalid t<sub>CK2Q</sub> ns after the second rising edge of the clock.

- D0 becomes valid again t<sub>CK2Q</sub> ns after the second falling edge.

If the address unchanged for three cycles:

- D0 becomes invalid t<sub>CK2Q</sub> ns after the second rising edge of the clock.

- D0 becomes valid again t<sub>CK2Q</sub> ns after the second falling edge.

- D0 becomes invalid t<sub>CK2Q</sub> ns after the third rising edge of the clock.

- D0 becomes valid again  $t_{CK2Q}$  ns after the third falling edge.

### ESTOP, FSTOP

ESTOP is used to stop the FIFO read counter from further counting once the FIFO is empty (i.e., the EMPTY flag goes High). A High on this signal inhibits the counting.

FSTOP is used to stop the FIFO write counter from further counting once the FIFO is full (i.e., the FULL flag goes High). A High on this signal inhibits the counting.

For more information on these signals, refer to the "ESTOP and FSTOP Usage" section on page 2-70.

### FULL, EMPTY

When the FIFO is full and no more data can be written, the FULL flag asserts High. The FULL flag is synchronous to WCLK to inhibit writing immediately upon detection of a full condition and to prevent overflows. Since the write address is compared to a resynchronized (and thus time-delayed) version of the read address, the FULL flag will remain asserted until two WCLK active edges after a read operation eliminates the full condition.

When the FIFO is empty and no more data can be read, the EMPTY flag asserts High. The EMPTY flag is synchronous to RCLK to inhibit reading immediately upon detection of an empty condition and to prevent underflows. Since the read address is compared to a resynchronized (and thus time-delayed) version of the write address, the EMPTY flag will remain asserted until two RCLK active edges after a write operation removes the empty condition.

For more information on these signals, refer to the "FIFO Flag Usage Considerations" section on page 2-70.

### AFULL, AEMPTY

These are programmable flags and will be asserted on the threshold specified by AFVAL and AEVAL, respectively.

When the number of words stored in the FIFO reaches the amount specified by AEVAL while reading, the AEMPTY output will go High. Likewise, when the number of words stored in the FIFO reaches the amount specified by AFVAL while writing, the AFULL output will go High.

### AFVAL, AEVAL

The AEVAL and AFVAL pins are used to specify the almost-empty and almost-full threshold values, respectively. They are 12-bit signals. For more information on these signals, refer to "FIFO Flag Usage Considerations" section.

### ESTOP and FSTOP Usage

The ESTOP pin is used to stop the read counter from counting any further once the FIFO is empty (i.e., the EMPTY flag goes High). Likewise, the FSTOP pin is used to stop the write counter from counting any further once the FIFO is full (i.e., the FULL flag goes High).

The FIFO counters in the Fusion device start the count at 0, reach the maximum depth for the configuration (e.g., 511 for a 512×9 configuration), and then restart at 0. An example application for the ESTOP, where the read counter keeps counting, would be writing to the FIFO once and reading the same content over and over without doing another write.

### FIFO Flag Usage Considerations

The AEVAL and AFVAL pins are used to specify the 12-bit AEMPTY and AFULL threshold values, respectively. The FIFO contains separate 12-bit write address (WADDR) and read address (RADDR) counters. WADDR is incremented every time a write operation is performed, and RADDR is incremented every time a read operation is performed. Whenever the difference between WADDR and RADDR is greater than or equal to AFVAL, the AFULL output is asserted. Likewise, whenever the difference between WADDR and RADDR is less than or equal to AEVAL, the AEMPTY output is asserted. To handle different read and write aspect ratios, AFVAL and AEVAL are expressed in terms of total data bits instead of total data words. When users specify AFVAL and AEVAL in terms of read or write words, the SmartGen tool translates them into bit addresses and configures these signals automatically. SmartGen configures the AFULL flag to assert when the write address exceeds the read address by at least a predefined value. In a 2k×8 FIFO, for example, a value of 1,500 for AFVAL means that the AFULL flag will be asserted after a write when the difference between the write address and the read address reaches 1,500 (there have been at least 1500 more writes than reads). It will stay asserted until the difference between the write and read addresses drops below 1,500.

Table 2-36 describes each pin in the Analog Block. Each function within the Analog Block will be explained in detail in the following sections.

Table 2-36 • Analog Block Pin Description

| Signal Name      | Number<br>of Bits | Direction    | Function                                                                                                                                                      | Location of<br>Details |

|------------------|-------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| VAREF            | 1                 | Input/Output | Voltage reference for ADC                                                                                                                                     | ADC                    |

| ADCGNDREF        | 1                 | Input        | External ground reference                                                                                                                                     | ADC                    |

| MODE[3:0]        | 4                 | Input        | ADC operating mode                                                                                                                                            | ADC                    |

| SYSCLK           | 1                 | Input        | External system clock                                                                                                                                         |                        |

| TVC[7:0]         | 8                 | Input        | Clock divide control                                                                                                                                          | ADC                    |

| STC[7:0]         | 8                 | Input        | Sample time control                                                                                                                                           | ADC                    |

| ADCSTART         | 1                 | Input        | Start of conversion                                                                                                                                           | ADC                    |

| PWRDWN           |                   |              |                                                                                                                                                               |                        |

| ADCRESET         | 1                 | Input        | ADC resets and disables Analog Quad – active high                                                                                                             | ADC                    |

| BUSY             | 1                 | Output       | 1 – Running conversion                                                                                                                                        | ADC                    |

| CALIBRATE        | 1                 | Output       | 1 – Power-up calibration                                                                                                                                      | ADC                    |

| DATAVALID        | 1                 | Output       | 1 – Valid conversion result                                                                                                                                   | ADC                    |

| RESULT[11:0]     | 12                | Output       | Conversion result                                                                                                                                             | ADC                    |

| TMSTBINT         | 1                 | Input        | Internal temp. monitor strobe                                                                                                                                 | ADC                    |

| SAMPLE           | 1                 | Output       | <ul> <li>1 – An analog signal is actively being sampled (stays high during signal acquisition only)</li> <li>0 – No analog signal is being sampled</li> </ul> | ADC                    |

| VAREFSEL         | 1                 | Input        | 0 = Output internal voltage reference<br>(2.56 V) to VAREF                                                                                                    | ADC                    |

|                  |                   |              | 1 = Input external voltage reference<br>from VAREF and ADCGNDREF                                                                                              |                        |

| CHNUMBER[4:0]    | 5                 | Input        | Analog input channel select                                                                                                                                   | Input<br>multiplexer   |

| ACMCLK           | 1                 | Input        | ACM clock                                                                                                                                                     | ACM                    |

| ACMWEN           | 1                 | Input        | ACM write enable – active high                                                                                                                                | ACM                    |

| ACMRESET         | 1                 | Input        | ACM reset – active low                                                                                                                                        | ACM                    |

| ACMWDATA[7:0]    | 8                 | Input        | ACM write data                                                                                                                                                | ACM                    |

| ACMRDATA[7:0]    | 8                 | Output       | ACM read data                                                                                                                                                 | ACM                    |

| ACMADDR[7:0]     | 8                 | Input        | ACM address                                                                                                                                                   | ACM                    |

| CMSTB0 to CMSTB9 | 10                | Input        | Current monitor strobe – 1 per quad, active high                                                                                                              | Analog Quad            |

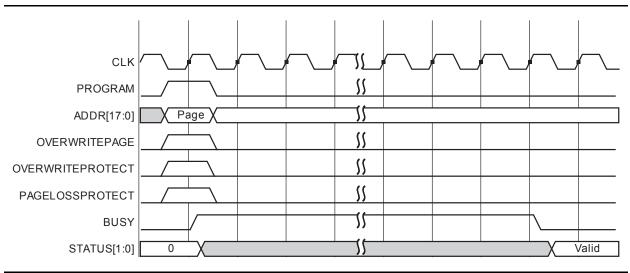

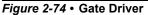

### Gate Driver

The Fusion Analog Quad includes a Gate Driver connected to the Quad's AG pin (Figure 2-74). Designed to work with external p- or n-channel MOSFETs, the Gate driver is a configurable current sink or source and requires an external pull-up or pull-down resistor. The AG supports 4 selectable gate drive levels: 1  $\mu$ A, 3  $\mu$ A, 10  $\mu$ A, and 30  $\mu$ A (Figure 2-75 on page 2-91). The AG also supports a High Current Drive mode in which it can sink 20 mA; in this mode the switching rate is approximately 1.3 MHz with 100 ns turn-on time and 600 ns turn-off time. Modeled on an open-drain-style output, it does not output a voltage level without an appropriate pull-up or pull-down resistor. If 1 V is forced on the drain, the current sinking/sourcing will exceed the ability of the transistor, and the device could be damaged.

The AG pad is turned on via the corresponding GDONx pin in the Analog Block macro, where x is the number of the corresponding Analog Quad for the AG pad to be enabled (GDON0 to GDON9).

The gate-to-source voltage ( $V_{gs}$ ) of the external MOSFET is limited to the programmable drive current times the external pull-up or pull-down resistor value (EQ 5).

$$V_{gs} \le I_g \times (R_{pullup} \text{ or } R_{pulldown})$$

EQ 5

### **Hot-Swap Support**

Hot-swapping (also called hot plugging) is the operation of hot insertion or hot removal of a card in (or from) a powered-up system. The levels of hot-swap support and examples of related applications are described in Table 2-74. The I/Os also need to be configured in hot insertion mode if hot plugging compliance is required.

Table 2-74 • Levels of Hot-Swap Support

| Hot<br>Swapping<br>Level | Description                     | Power<br>Applied<br>to Device | Bus State                                                                                                                   | Card<br>Ground<br>Connection                                                                        | Device<br>Circuitry<br>Connected<br>to Bus Pins | Example of<br>Application with<br>Cards that Contain<br>Fusion Devices                                                                                                         | Compliance of<br>Fusion Devices                                                                            |

|--------------------------|---------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| 1                        | Cold-swap                       | No                            | _                                                                                                                           | _                                                                                                   | _                                               |                                                                                                                                                                                | Compliant I/Os<br>can but do not<br>have to be set to<br>hot insertion<br>mode.                            |

| 2                        | Hot-swap<br>while reset         | Yes                           | reset state                                                                                                                 | Must be made<br>and<br>maintained for<br>1 ms before,<br>during, and<br>after insertion/<br>removal | _                                               | In PCI hot plug<br>specification, reset<br>control circuitry<br>isolates the card<br>busses until the card<br>supplies are at their<br>nominal operating<br>levels and stable. | Compliant I/Os<br>can but do not<br>have to be set to<br>hot insertion<br>mode.                            |

| 3                        | Hot-swap<br>while bus<br>idle   |                               | Held idle<br>(no ongoing<br>I/O<br>processes<br>during<br>insertion/re<br>moval)                                            | Same as<br>Level 2                                                                                  | glitch-free<br>during<br>power-up or            | no toggling activity on bus. It is critical that                                                                                                                               | Compliant with<br>cards with two<br>levels of staging.<br>I/Os have to be<br>set to hot<br>insertion mode. |

| 4                        | Hot-swap on<br>an active<br>bus | Yes                           | Bus may<br>have active<br>I/O<br>processes<br>ongoing,<br>but device<br>being<br>inserted or<br>removed<br>must be<br>idle. | Same as<br>Level 2                                                                                  | Same as<br>Level 3                              | is critical that the logic<br>states set on the bus<br>signal do not get                                                                                                       | Compliant with<br>cards with two<br>levels of staging.<br>I/Os have to be<br>set to hot<br>insertion mode. |

Fusion Family of Mixed Signal FPGAs

Figure 2-117 • Output Buffer Model and Delays (example)

Fusion Family of Mixed Signal FPGAs

### Table 2-98 • I/O Short Currents IOSH/IOSL

|                                  | Drive Strength | IOSH (mA)* | IOSL (mA)* |

|----------------------------------|----------------|------------|------------|

| Applicable to Pro I/O Banks      |                |            |            |

| 3.3 V LVTTL / 3.3 V LVCMOS       | 4 mA           | 25         | 27         |

|                                  | 8 mA           | 51         | 54         |

|                                  | 12 mA          | 103        | 109        |

|                                  | 16 mA          | 132        | 127        |

|                                  | 24 mA          | 268        | 181        |

| 2.5 V LVCMOS                     | 4 mA           | 16         | 18         |

|                                  | 8 mA           | 32         | 37         |

|                                  | 12 mA          | 65         | 74         |

|                                  | 16 mA          | 83         | 87         |

|                                  | 24 mA          | 169        | 124        |

| 1.8 V LVCMOS                     | 2 mA           | 9          | 11         |

|                                  | 4 mA           | 17         | 22         |

|                                  | 6 mA           | 35         | 44         |

|                                  | 8 mA           | 45         | 51         |

|                                  | 12 mA          | 91         | 74         |

|                                  | 16 mA          | 91         | 74         |

| 1.5 V LVCMOS                     | 2 mA           | 13         | 16         |

|                                  | 4 mA           | 25         | 33         |

|                                  | 6 mA           | 32         | 39         |

|                                  | 8 mA           | 66         | 55         |

|                                  | 12 mA          | 66         | 55         |

| Applicable to Advanced I/O Banks | ;<br>;         |            | 1          |

| 3.3 V LVTTL / 3.3 V LVCMOS       | 2 mA           | 25         | 27         |

|                                  | 4 mA           | 25         | 27         |

|                                  | 6 mA           | 51         | 54         |

|                                  | 8 mA           | 51         | 54         |

|                                  | 12 mA          | 103        | 109        |

|                                  | 16 mA          | 132        | 127        |

|                                  | 24 mA          | 268        | 181        |

| 3.3 V LVCMOS                     | 2 mA           | 25         | 27         |

|                                  | 4 mA           | 25         | 27         |

|                                  | 6 mA           | 51         | 54         |

|                                  | 8 mA           | 51         | 54         |

|                                  | 12 mA          | 103        | 109        |

|                                  | 16 mA          | 132        | 127        |

|                                  | 24 mA          | 268        | 181        |

*Note:*  $^{*}T_{J} = 100^{\circ}C$

### Table 2-106 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Appl | icable | e to | Advanced | I/Os |

|------|--------|------|----------|------|

|      |        |      |          |      |

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.66              | 10.26           | 0.04             | 1.20            | 0.43              | 10.45           | 8.90            | 2.64            | 2.46            | 12.68            | 11.13            | ns    |

|                   | -1             | 0.56              | 8.72            | 0.04             | 1.02            | 0.36              | 8.89            | 7.57            | 2.25            | 2.09            | 10.79            | 9.47             | ns    |

|                   | -2             | 0.49              | 7.66            | 0.03             | 0.90            | 0.32              | 7.80            | 6.64            | 1.98            | 1.83            | 9.47             | 8.31             | ns    |

| 8 mA              | Std.           | 0.66              | 7.27            | 0.04             | 1.20            | 0.43              | 7.41            | 6.28            | 2.98            | 3.04            | 9.65             | 8.52             | ns    |

|                   | -1             | 0.56              | 6.19            | 0.04             | 1.02            | 0.36              | 6.30            | 5.35            | 2.54            | 2.59            | 8.20             | 7.25             | ns    |

|                   | -2             | 0.49              | 5.43            | 0.03             | 0.90            | 0.32              | 5.53            | 4.69            | 2.23            | 2.27            | 7.20             | 6.36             | ns    |

| 12 mA             | Std.           | 0.66              | 5.58            | 0.04             | 1.20            | 0.43              | 5.68            | 4.87            | 3.21            | 3.42            | 7.92             | 7.11             | ns    |

|                   | -1             | 0.56              | 4.75            | 0.04             | 1.02            | 0.36              | 4.84            | 4.14            | 2.73            | 2.91            | 6.74             | 6.05             | ns    |

|                   | -2             | 0.49              | 4.17            | 0.03             | 0.90            | 0.32              | 4.24            | 3.64            | 2.39            | 2.55            | 5.91             | 5.31             | ns    |

| 16 mA             | Std.           | 0.66              | 5.21            | 0.04             | 1.20            | 0.43              | 5.30            | 4.56            | 3.26            | 3.51            | 7.54             | 6.80             | ns    |

|                   | -1             | 0.56              | 4.43            | 0.04             | 1.02            | 0.36              | 4.51            | 3.88            | 2.77            | 2.99            | 6.41             | 5.79             | ns    |

|                   | -2             | 0.49              | 3.89            | 0.03             | 0.90            | 0.32              | 3.96            | 3.41            | 2.43            | 2.62            | 5.63             | 5.08             | ns    |

| 24 mA             | Std.           | 0.66              | 4.85            | 0.04             | 1.20            | 0.43              | 4.94            | 4.54            | 3.32            | 3.88            | 7.18             | 6.78             | ns    |

|                   | -1             | 0.56              | 4.13            | 0.04             | 1.02            | 0.36              | 4.20            | 3.87            | 2.82            | 3.30            | 6.10             | 5.77             | ns    |

|                   | -2             | 0.49              | 3.62            | 0.03             | 0.90            | 0.32              | 3.69            | 3.39            | 2.48            | 2.90            | 5.36             | 5.06             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

### Table 2-107 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Advanced I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.66              | 7.66            | 0.04             | 1.20            | 0.43              | 7.80            | 6.59            | 2.65            | 2.61            | 10.03            | 8.82             | ns    |

|                   | -1             | 0.56              | 6.51            | 0.04             | 1.02            | 0.36              | 6.63            | 5.60            | 2.25            | 2.22            | 8.54             | 7.51             | ns    |

|                   | -2             | 0.49              | 5.72            | 0.03             | 0.90            | 0.32              | 5.82            | 4.92            | 1.98            | 1.95            | 7.49             | 6.59             | ns    |

| 8 mA              | Std.           | 0.66              | 4.91            | 0.04             | 1.20            | 0.43              | 5.00            | 4.07            | 2.99            | 3.20            | 7.23             | 6.31             | ns    |

|                   | -1             | 0.56              | 4.17            | 0.04             | 1.02            | 0.36              | 4.25            | 3.46            | 2.54            | 2.73            | 6.15             | 5.36             | ns    |

|                   | -2             | 0.49              | 3.66            | 0.03             | 0.90            | 0.32              | 3.73            | 3.04            | 2.23            | 2.39            | 5.40             | 4.71             | ns    |

| 12 mA             | Std.           | 0.66              | 3.53            | 0.04             | 1.20            | 0.43              | 3.60            | 2.82            | 3.21            | 3.58            | 5.83             | 5.06             | ns    |

|                   | -1             | 0.56              | 3.00            | 0.04             | 1.02            | 0.36              | 3.06            | 2.40            | 2.73            | 3.05            | 4.96             | 4.30             | ns    |

|                   | -2             | 0.49              | 2.64            | 0.03             | 0.90            | 0.32              | 2.69            | 2.11            | 2.40            | 2.68            | 4.36             | 3.78             | ns    |

| 16 mA             | Std.           | 0.66              | 3.33            | 0.04             | 1.20            | 0.43              | 3.39            | 2.56            | 3.26            | 3.68            | 5.63             | 4.80             | ns    |

|                   | -1             | 0.56              | 2.83            | 0.04             | 1.02            | 0.36              | 2.89            | 2.18            | 2.77            | 3.13            | 4.79             | 4.08             | ns    |

|                   | -2             | 0.49              | 2.49            | 0.03             | 0.90            | 0.32              | 2.53            | 1.91            | 2.44            | 2.75            | 4.20             | 3.58             | ns    |

| 24 mA             | Std.           | 0.66              | 3.08            | 0.04             | 1.20            | 0.43              | 3.13            | 2.12            | 3.32            | 4.06            | 5.37             | 4.35             | ns    |

|                   | -1             | 0.56              | 2.62            | 0.04             | 1.02            | 0.36              | 2.66            | 1.80            | 2.83            | 3.45            | 4.57             | 3.70             | ns    |

|                   | -2             | 0.49              | 2.30            | 0.03             | 0.90            | 0.32              | 2.34            | 1.58            | 2.48            | 3.03            | 4.01             | 3.25             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

### Table 2-108 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 9.46            | 0.04             | 1.00            | 0.43              | 9.64            | 8.54            | 2.07            | 2.04            | ns    |

|                   | -1             | 0.56              | 8.05            | 0.04             | 0.85            | 0.36              | 8.20            | 7.27            | 1.76            | 1.73            | ns    |

|                   | -2             | 0.49              | 7.07            | 0.03             | 0.75            | 0.32              | 7.20            | 6.38            | 1.55            | 1.52            | ns    |

| 4 mA              | Std.           | 0.66              | 9.46            | 0.04             | 1.00            | 0.43              | 9.64            | 8.54            | 2.07            | 2.04            | ns    |

|                   | -1             | 0.56              | 8.05            | 0.04             | 0.85            | 0.36              | 8.20            | 7.27            | 1.76            | 1.73            | ns    |

|                   | -2             | 0.49              | 7.07            | 0.03             | 0.75            | 0.32              | 7.20            | 6.38            | 1.55            | 1.52            | ns    |

| 6 mA              | Std.           | 0.66              | 6.57            | 0.04             | 1.00            | 0.43              | 6.69            | 5.98            | 2.40            | 2.57            | ns    |

|                   | -1             | 0.56              | 5.59            | 0.04             | 0.85            | 0.36              | 5.69            | 5.09            | 2.04            | 2.19            | ns    |

|                   | -2             | 0.49              | 4.91            | 0.03             | 0.75            | 0.32              | 5.00            | 4.47            | 1.79            | 1.92            | ns    |

| 8 mA              | Std.           | 0.66              | 6.57            | 0.04             | 1.00            | 0.43              | 6.69            | 5.98            | 2.40            | 2.57            | ns    |

|                   | -1             | 0.56              | 5.59            | 0.04             | 0.85            | 0.36              | 5.69            | 5.09            | 2.04            | 2.19            | ns    |

|                   | -2             | 0.49              | 4.91            | 0.03             | 0.75            | 0.32              | 5.00            | 4.47            | 1.79            | 1.92            | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

### Table 2-169 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) |

|---------------|----------------|----------------------|-----------------|

| 1.075         | 1.325          | Cross point          | -               |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

#### Table 2-170 • LVDS

### Commercial Temperature Range Conditions: $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Pro I/Os

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.66              | 2.10            | 0.04             | 1.82            | ns    |

| -1          | 0.56              | 1.79            | 0.04             | 1.55            | ns    |

| -2          | 0.49              | 1.57            | 0.03             | 1.36            | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

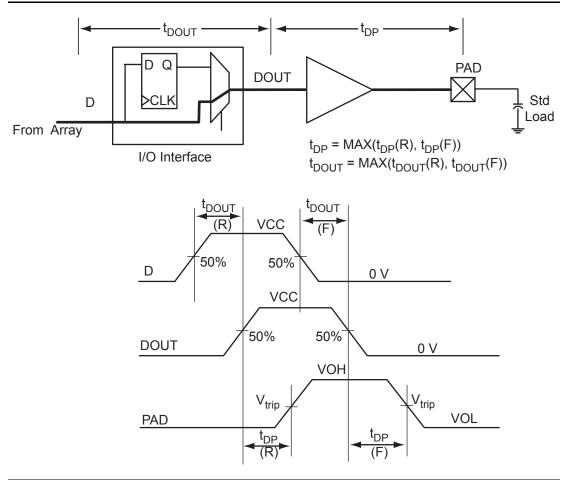

### BLVDS/M-LVDS

Bus LVDS (BLVDS) and Multipoint LVDS (M-LVDS) specifications extend the existing LVDS standard to high-performance multipoint bus applications. Multidrop and multipoint bus configurations can contain any combination of drivers, receivers, and transceivers. Microsemi LVDS drivers provide the higher drive current required by BLVDS and M-LVDS to accommodate the loading. The driver requires series terminations for better signal quality and to control voltage swing. Termination is also required at both ends of the bus, since the driver can be located anywhere on the bus. These configurations can be implemented using TRIBUF\_LVDS and BIBUF\_LVDS macros along with appropriate terminations. Multipoint designs using Microsemi LVDS macros can achieve up to 200 MHz with a maximum of 20 loads. A sample application is given in Figure 2-135. The input and output buffer delays are available in the LVDS section in Table 2-171.

Example: For a bus consisting of 20 equidistant loads, the following terminations provide the required differential voltage, in worst-case industrial operating conditions at the farthest receiver:  $R_S = 60 \Omega$  and  $R_T = 70 \Omega$ , given  $Z_0 = 50 \Omega$  (2") and  $Z_{stub} = 50 \Omega$  (~1.5").

Figure 2-135 • BLVDS/M-LVDS Multipoint Application Using LVDS I/O Buffers

### Table 2-175 • Parameter Definitions and Measuring Nodes

| Parameter Name        | Parameter Definition                                            | Measuring Nodes<br>(from, to)* |

|-----------------------|-----------------------------------------------------------------|--------------------------------|

| t <sub>oclkq</sub>    | Clock-to-Q of the Output Data Register                          | HH, DOUT                       |

| tosup                 | Data Setup Time for the Output Data Register                    | FF, HH                         |

| t <sub>OHD</sub>      | Data Hold Time for the Output Data Register                     | FF, HH                         |

| t <sub>OSUE</sub>     | Enable Setup Time for the Output Data Register                  | GG, HH                         |

| t <sub>OHE</sub>      | Enable Hold Time for the Output Data Register                   | GG, HH                         |

| t <sub>OCLR2Q</sub>   | Asynchronous Clear-to-Q of the Output Data Register             | LL, DOUT                       |

| t <sub>OREMCLR</sub>  | Asynchronous Clear Removal Time for the Output Data Register    | LL, HH                         |

| tORECCLR              | Asynchronous Clear Recovery Time for the Output Data Register   | LL, HH                         |

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                        | HH, EOUT                       |

| tOESUD                | Data Setup Time for the Output Enable Register                  | JJ, HH                         |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                   | JJ, HH                         |

| t <sub>OESUE</sub>    | Enable Setup Time for the Output Enable Register                | KK, HH                         |

| t <sub>OEHE</sub>     | Enable Hold Time for the Output Enable Register                 | KK, HH                         |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register           | II, EOUT                       |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register  | II, HH                         |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register | II, HH                         |

| t <sub>ICLKQ</sub>    | Clock-to-Q of the Input Data Register                           | AA, EE                         |

| t <sub>ISUD</sub>     | Data Setup Time for the Input Data Register                     | CC, AA                         |

| t <sub>IHD</sub>      | Data Hold Time for the Input Data Register                      | CC, AA                         |

| t <sub>ISUE</sub>     | Enable Setup Time for the Input Data Register                   | BB, AA                         |

| t <sub>IHE</sub>      | Enable Hold Time for the Input Data Register                    | BB, AA                         |

| t <sub>ICLR2Q</sub>   | Asynchronous Clear-to-Q of the Input Data Register              | DD, EE                         |

| t <sub>IREMCLR</sub>  | Asynchronous Clear Removal Time for the Input Data Register     | DD, AA                         |

| t <sub>IRECCLR</sub>  | Asynchronous Clear Recovery Time for the Input Data Register    | DD, AA                         |

*Note:* \*See Figure 2-138 on page 2-214 for more information.

# 3 – DC and Power Characteristics

## **General Specifications**

### **Operating Conditions**

Stresses beyond those listed in Table 3-1 may cause permanent damage to the device.

Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Devices should not be operated outside the recommended operating ranges specified in Table 3-2 on page 3-3.

| Symbol   | Parameter                                  | Commercial                                                                                                                                                                                  | Industrial                | Units |

|----------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------|

| VCC      | DC core supply voltage                     | -0.3 to 1.65                                                                                                                                                                                | -0.3 to 1.65              | V     |

| VJTAG    | JTAG DC voltage                            | -0.3 to 3.75                                                                                                                                                                                | -0.3 to 3.75              | V     |

| VPUMP    | Programming voltage                        | -0.3 to 3.75                                                                                                                                                                                | -0.3 to 3.75              | V     |

| VCCPLL   | Analog power supply (PLL)                  | -0.3 to 1.65                                                                                                                                                                                | -0.3 to 1.65              | V     |

| VCCI     | DC I/O output buffer supply voltage        | -0.3 to 3.75                                                                                                                                                                                | -0.3 to 3.75              | V     |

| VI       | I/O input voltage <sup>1</sup>             | <ul> <li>-0.3 V to 3.6 V (when I/O hot insertion mode is enabled)</li> <li>-0.3 V to (VCCI + 1 V) or 3.6 V, whichever voltage is lower (when I/O hot-insertion mode is disabled)</li> </ul> |                           |       |

| VCC33A   | +3.3 V power supply                        | -0.3 to 3.75 <sup>2</sup>                                                                                                                                                                   | -0.3 to 3.75 <sup>2</sup> | V     |

| VCC33PMP | +3.3 V power supply                        | -0.3 to 3.75 <sup>2</sup>                                                                                                                                                                   | -0.3 to 3.75 <sup>2</sup> | V     |

| VAREF    | Voltage reference for ADC                  | -0.3 to 3.75                                                                                                                                                                                | -0.3 to 3.75              | V     |

| VCC15A   | Digital power supply for the analog system | -0.3 to 1.65                                                                                                                                                                                | -0.3 to 1.65              | V     |

| VCCNVM   | Embedded flash power supply                | -0.3 to 1.65                                                                                                                                                                                | -0.3 to 1.65              | V     |

| VCCOSC   | Oscillator power supply                    | -0.3 to 3.75                                                                                                                                                                                | -0.3 to 3.75              | V     |

### Table 3-1 • Absolute Maximum Ratings

Notes:

1. The device should be operated within the limits specified by the datasheet. During transitions, the input signal may undershoot or overshoot according to the limits shown in Table 3-4 on page 3-4.

2. Analog data not valid beyond 3.65 V.

3. The high current mode has a maximum power limit of 20 mW. Appropriate current limit resistors must be used, based on voltage on the pad.

4. For flash programming and retention maximum limits, refer to Table 3-5 on page 3-5. For recommended operating limits refer to Table 3-2 on page 3-3.

| Pads   | Pad Configuration                  | Prescaler Range  | Input Resistance to Ground |

|--------|------------------------------------|------------------|----------------------------|

| AV, AC | Analog Input (direct input to ADC) | -                | 2 kΩ (typical)             |

|        |                                    | -                | > 10 MΩ                    |

|        | Analog Input (positive prescaler)  | +16 V to +2 V    | 1 MΩ (typical)             |

|        |                                    | +1 V to +0.125 V | > 10 MΩ                    |

|        | Analog Input (negative prescaler)  | –16 V to –2 V    | 1 MΩ (typical)             |

|        | Ī                                  | -1 V to -0.125 V | > 10 MΩ                    |

|        | Digital input                      | +16 V to +2 V    | 1 MΩ (typical)             |

|        | Current monitor                    | +16 V to +2 V    | 1 MΩ (typical)             |

|        | Ī                                  | –16 V to –2 V    | 1 MΩ (typical)             |

| AT     | Analog Input (direct input to ADC) | -                | 1 MΩ (typical)             |

|        | Analog Input (positive prescaler)  | +16 V, +4 V      | 1 MΩ (typical)             |

|        | Digital input                      | +16 V, +4 V      | 1 MΩ (typical)             |

|        | Temperature monitor                | +16 V, +4 V      | > 10 MΩ                    |

### Table 3-3 • Input Resistance of Analog Pads

### Table 3-4 • Overshoot and Undershoot Limits <sup>1</sup>

| VCCI          | Average VCCI–GND Overshoot or Undershoot<br>Duration as a Percentage of Clock Cycle <sup>2</sup> | Maximum Overshoot/<br>Undershoot <sup>2</sup> |

|---------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 2.7 V or less | 10%                                                                                              | 1.4 V                                         |

|               | 5%                                                                                               | 1.49 V                                        |

| 3.0 V         | 10%                                                                                              | 1.1 V                                         |

|               | 5%                                                                                               | 1.19 V                                        |

| 3.3 V         | 10%                                                                                              | 0.79 V                                        |

|               | 5%                                                                                               | 0.88 V                                        |

| 3.6 V         | 10%                                                                                              | 0.45 V                                        |

|               | 5%                                                                                               | 0.54 V                                        |

Notes:

1. Based on reliability requirements at a junction temperature of 85°C.

2. The duration is allowed at one cycle out of six clock cycle. If the overshoot/undershoot occurs at one out of two cycles, the maximum overshoot/undershoot has to be reduced by 0.15 V.

# **5 – Datasheet Information**

## **List of Changes**

The following table lists critical changes that were made in each revision of the Fusion datasheet.

| Revision                     | Changes                                                                                                                                                                                                                                                                                 | Page            |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Revision 6<br>(March 2014)   | Note added for the discontinuance of QN108 and QN180 packages to the "Package I/Os: Single-/Double-Ended (Analog)" table and the "Temperature Grade Offerings" table (SAR 55113, PDN 1306).                                                                                             |                 |

|                              | Updated details about page programming time in the "Program Operation" section (SAR 49291).                                                                                                                                                                                             | 2-46            |

|                              | ADC_START changed to ADCSTART in the "ADC Operation" section (SAR 44104).                                                                                                                                                                                                               | 2-104           |

| Revision 5<br>(January 2014) | Calibrated offset values (AFS090, AFS250) of the external temperature monitor in Table 2-49 • Analog Channel Specifications have been updated (SAR 51464).                                                                                                                              |                 |

|                              | Specifications for the internal temperature monitor in<br>Table 2-49 • Analog Channel Specifications have been updated (SAR 50870).                                                                                                                                                     | 2-117           |

| Revision 4<br>(January 2013) | The "Product Ordering Codes" section has been updated to mention "Y" as "Blank" mentioning "Device Does Not Include License to Implement IP Based on the Cryptography Research, Inc. (CRI) Patent Portfolio" (SAR 43177).                                                               |                 |

|                              | The note in Table 2-12 • Fusion CCC/PLL Specification referring the reader to SmartGen was revised to refer instead to the online help associated with the core (SAR 42563).                                                                                                            |                 |

|                              | Table 2-49 • Analog Channel Specifications was modified to update the uncalibrated offset values (AFS250) of the external and internal temperature monitors (SAR 43134).                                                                                                                | 2-117           |

|                              | In Table 2-57 • Prescaler Control Truth Table—AV ( $x = 0$ ), AC ( $x = 1$ ), and AT ( $x = 3$ ), changed the column heading from 'Full-Scale Voltage' to 'Full Scale Voltage in 10-Bit Mode', and added and updated Notes as required (SAR 20812).                                     | 2-130           |

|                              | The values for the Speed Grade (-1 and Std.) for FDDRIMAX (Table 2-180 • Input DDR Propagation Delays) and values for the Speed Grade (-2 and Std.) for FDDOMAX (Table 2-182 • Output DDR Propagation Delays) had been inadvertently interchanged. This has been rectified (SAR 38514). | 2-220,<br>2-222 |

|                              | Added description about what happens if a user connects VAREF to an external 3.3 V on their board to the "VAREF Analog Reference Voltage" section (SAR 35188).                                                                                                                          | 2-225           |

|                              | Added a note to Table 3-2 • Recommended Operating Conditions1 (SAR 43429):<br>The programming temperature range supported is $T_{ambient} = 0^{\circ}C$ to 85°C.                                                                                                                        | 3-3             |

|                              | Added the Package Thermal details for AFS600-PQ208 and AFS250-PQ208 to Table 3-6 • Package Thermal Resistance (SAR 37816). Deleted the Die Size column from the table (SAR 43503).                                                                                                      | 3-7             |

|                              | Libero Integrated Design Environment (IDE) was changed to Libero System-on-Chip (SoC) throughout the document (SAR 42495).                                                                                                                                                              | NA              |

|                              | Live at Power-Up (LAPU) has been replaced with 'Instant On'.                                                                                                                                                                                                                            |                 |

| Revision 3                   | Microblade U1AFS250 and U1AFS1500 devices were added to the product tables.                                                                                                                                                                                                             | I – IV          |

| (nuguəi 2012)                | A sentence pertaining to the analog I/Os was added to the "Specifying I/O States During Programming" section (SAR 34831).                                                                                                                                                               | 1-9             |

| (August 2012)                | A sentence pertaining to the analog I/Os was added to the "Specifying I/O State                                                                                                                                                                                                         |                 |