Welcome to E-XFL.COM

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                      |

|--------------------------------|-----------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | ·                                                                           |

| Total RAM Bits                 | 110592                                                                      |

| Number of I/O                  | 119                                                                         |

| Number of Gates                | 600000                                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 256-LBGA                                                                    |

| Supplier Device Package        | 256-FPBGA (17x17)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/p1afs600-2fgg256i |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Temperature Grade Offerings**

| Fusion Devices        | AFS090 | AFS250                | AFS600                | AFS1500                |

|-----------------------|--------|-----------------------|-----------------------|------------------------|

| ARM Cortex-M1 Devices |        | M1AFS250              | M1AFS600              | M1AFS1500              |

| Pigeon Point Devices  |        |                       | P1AFS600 <sup>3</sup> | P1AFS1500 3            |

| MicroBlade Devices    |        | U1AFS250 <sup>4</sup> | U1AFS600 <sup>4</sup> | U1AFS1500 <sup>4</sup> |

| QN108 <sup>5</sup>    | C, I   | -                     | -                     | -                      |

| QN180 <sup>5</sup>    | C, I   | C, I                  | -                     | -                      |

| PQ208                 | -      | C, I                  | C, I                  | -                      |

| FG256                 | C, I   | C, I                  | C, I                  | C, I                   |

| FG484                 | -      | -                     | C, I                  | C, I                   |

| FG676                 | -      | _                     | -                     | C, I                   |

|                       |        |                       |                       |                        |

Notes:

1. C = Commercial Temperature Range: 0°C to 85°C Junction

2. I = Industrial Temperature Range: -40°C to 100°C Junction

3. Pigeon Point devices are only offered in FG484 and FG256.

4. MicroBlade devices are only offered in FG256.

5. Package not available.

# **Speed Grade and Temperature Grade Matrix**

|                | Std. <sup>1</sup> | -1           | -2 <sup>2</sup> |

|----------------|-------------------|--------------|-----------------|

| C <sup>3</sup> | $\checkmark$      | $\checkmark$ | $\checkmark$    |

| l <sup>4</sup> | $\checkmark$      | $\checkmark$ | $\checkmark$    |

Notes:

1. MicroBlade devices are only offered in standard speed grade.

2. Pigeon Point devices are only offered in –2 speed grade.

3. C = Commercial Temperature Range: 0°C to 85°C Junction

4. I = Industrial Temperature Range: -40°C to 100°C Junction

Contact your local Microsemi SoC Products Group representative for device availability:

http://www.microsemi.com/index.php?option=com\_content&id=137&lang=en&view=article.

# **Cortex-M1, Pigeon Point, and MicroBlade Fusion Device** Information

This datasheet provides information for all Fusion (AFS), Cortex-M1 (M1), Pigeon Point (P1), and MicroBlade (U1) devices. The remainder of the document will only list the Fusion (AFS) devices. Please apply relevant information to M1, P1, and U1 devices when appropriate. Please note the following:

- Cortex-M1 devices are offered in the same speed grades and packages as basic Fusion devices.

- Pigeon Point devices are only offered in –2 speed grade and FG484 and FG256 packages.

- MicroBlade devices are only offered in standard speed grade and the FG256 package.

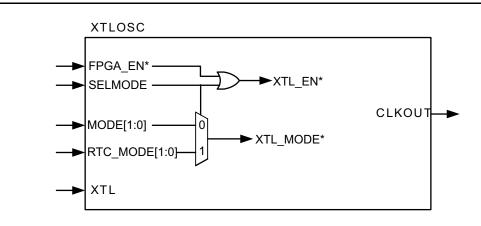

### **Crystal Oscillator**

The Crystal Oscillator (XTLOSC) is source that generates the clock from an external crystal. The output of XTLOSC CLKOUT signal can be selected as an input to the PLL. Refer to the "Clock Conditioning Circuits" section for more details. The XTLOSC can operate in normal operations and Standby mode (RTC is running and 1.5 V is not present).

In normal operation, the internal FPGA\_EN signal is '1' as long as 1.5 V is present for VCC. As such, the internal enable signal, XTL\_EN, for Crystal Oscillator is enabled since FPGA\_EN is asserted. The XTL\_MODE has the option of using MODE or RTC\_MODE, depending on SELMODE.

During Standby, 1.5 V is not available, as such, and FPGA\_EN is '0'. SELMODE must be asserted in order for XTL\_EN to be enabled; hence XTL\_MODE relies on RTC\_MODE. SELMODE and RTC\_MODE must be connected to RTCXTLSEL and RTCXTLMODE from the AB respectively for correct operation during Standby (refer to the "Real-Time Counter System" section on page 2-31 for a detailed description).

The Crystal Oscillator can be configured in one of four modes:

- RC network, 32 KHz to 4 MHz

- Low gain, 32 to 200 KHz

- Medium gain, 0.20 to 2.0 MHz

- High gain, 2.0 to 20.0 MHz

In RC network mode, the XTAL1 pin is connected to an RC circuit, as shown in Figure 2-16 on page 2-18. The XTAL2 pin should be left floating. The RC value can be chosen based on Figure 2-18 for any desired frequency between 32 KHz and 4 MHz. The RC network mode can also accommodate an external clock source on XTAL1 instead of an RC circuit.

In Low gain, Medium gain, and High gain, an external crystal component or ceramic resonator can be added onto XTAL1 and XTAL2, as shown in Figure 2-16 on page 2-18. In the case where the Crystal Oscillator block is not used, the XTAL1 pin should be connected to GND and the XTAL2 pin should be left floating.

Note: \*Internal signal—does not exist in macro.

Figure 2-17 • XTLOSC Macro

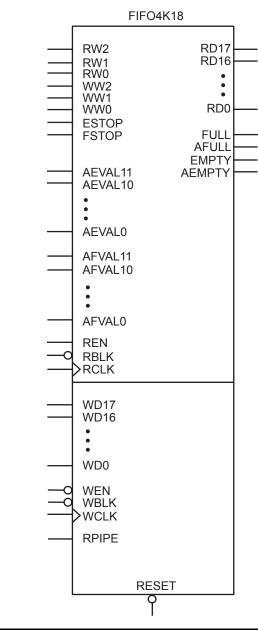

### FIFO4K18 Description

Figure 2-56 • FIFO4KX18

### ESTOP, FSTOP

ESTOP is used to stop the FIFO read counter from further counting once the FIFO is empty (i.e., the EMPTY flag goes High). A High on this signal inhibits the counting.

FSTOP is used to stop the FIFO write counter from further counting once the FIFO is full (i.e., the FULL flag goes High). A High on this signal inhibits the counting.

For more information on these signals, refer to the "ESTOP and FSTOP Usage" section on page 2-70.

### FULL, EMPTY

When the FIFO is full and no more data can be written, the FULL flag asserts High. The FULL flag is synchronous to WCLK to inhibit writing immediately upon detection of a full condition and to prevent overflows. Since the write address is compared to a resynchronized (and thus time-delayed) version of the read address, the FULL flag will remain asserted until two WCLK active edges after a read operation eliminates the full condition.

When the FIFO is empty and no more data can be read, the EMPTY flag asserts High. The EMPTY flag is synchronous to RCLK to inhibit reading immediately upon detection of an empty condition and to prevent underflows. Since the read address is compared to a resynchronized (and thus time-delayed) version of the write address, the EMPTY flag will remain asserted until two RCLK active edges after a write operation removes the empty condition.

For more information on these signals, refer to the "FIFO Flag Usage Considerations" section on page 2-70.

### AFULL, AEMPTY

These are programmable flags and will be asserted on the threshold specified by AFVAL and AEVAL, respectively.

When the number of words stored in the FIFO reaches the amount specified by AEVAL while reading, the AEMPTY output will go High. Likewise, when the number of words stored in the FIFO reaches the amount specified by AFVAL while writing, the AFULL output will go High.

### AFVAL, AEVAL

The AEVAL and AFVAL pins are used to specify the almost-empty and almost-full threshold values, respectively. They are 12-bit signals. For more information on these signals, refer to "FIFO Flag Usage Considerations" section.

### ESTOP and FSTOP Usage

The ESTOP pin is used to stop the read counter from counting any further once the FIFO is empty (i.e., the EMPTY flag goes High). Likewise, the FSTOP pin is used to stop the write counter from counting any further once the FIFO is full (i.e., the FULL flag goes High).

The FIFO counters in the Fusion device start the count at 0, reach the maximum depth for the configuration (e.g., 511 for a 512×9 configuration), and then restart at 0. An example application for the ESTOP, where the read counter keeps counting, would be writing to the FIFO once and reading the same content over and over without doing another write.

### FIFO Flag Usage Considerations

The AEVAL and AFVAL pins are used to specify the 12-bit AEMPTY and AFULL threshold values, respectively. The FIFO contains separate 12-bit write address (WADDR) and read address (RADDR) counters. WADDR is incremented every time a write operation is performed, and RADDR is incremented every time a read operation is performed. Whenever the difference between WADDR and RADDR is greater than or equal to AFVAL, the AFULL output is asserted. Likewise, whenever the difference between WADDR and RADDR is less than or equal to AEVAL, the AEMPTY output is asserted. To handle different read and write aspect ratios, AFVAL and AEVAL are expressed in terms of total data bits instead of total data words. When users specify AFVAL and AEVAL in terms of read or write words, the SmartGen tool translates them into bit addresses and configures these signals automatically. SmartGen configures the AFULL flag to assert when the write address exceeds the read address by at least a predefined value. In a 2k×8 FIFO, for example, a value of 1,500 for AFVAL means that the AFULL flag will be asserted after a write when the difference between the write address and the read address reaches 1,500 (there have been at least 1500 more writes than reads). It will stay asserted until the difference between the write and read addresses drops below 1,500.

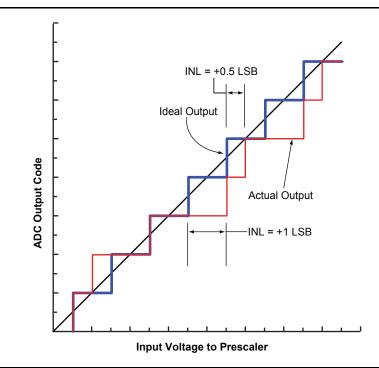

### INL – Integral Non-Linearity

INL is the deviation of an actual transfer function from a straight line. After nullifying offset and gain errors, the straight line is either a best-fit straight line or a line drawn between the end points of the transfer function (Figure 2-85).

Figure 2-85 • Integral Non-Linearity (INL)

### LSB – Least Significant Bit

In a binary number, the LSB is the least weighted bit in the group. Typically, the LSB is the furthest right bit. For an ADC, the weight of an LSB equals the full-scale voltage range of the converter divided by  $2^N$ , where N is the converter's resolution.

EQ 13 shows the calculation for a 10-bit ADC with a unipolar full-scale voltage of 2.56 V:

EQ 13

### **No Missing Codes**

An ADC has no missing codes if it produces all possible digital codes in response to a ramp signal applied to the analog input.

Table 2-57 details the settings available to control the prescaler values of the AV, AC, and AT pins. Note that the AT pin has a reduced number of available prescaler values.

| Control Lines<br>Bx[2:0] | Scaling<br>Factor, Pad to<br>ADC Input | LSB for an<br>8-Bit<br>Conversion <sup>1</sup><br>(mV) | LSB for a<br>10-Bit<br>Conversion <sup>1</sup><br>(mV) | LSB for a<br>12-Bit<br>Conversion <sup>1</sup><br>(mV) | Full-Scale<br>Voltage in<br>10-Bit<br>Mode <sup>2</sup> | Range Name |

|--------------------------|----------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|------------|

| 000 <sup>3</sup>         | 0.15625                                | 64                                                     | 16                                                     | 4                                                      | 16.368 V                                                | 16 V       |

| 001                      | 0.3125                                 | 32                                                     | 8                                                      | 2                                                      | 8.184 V                                                 | 8 V        |

| 010 <sup>3</sup>         | 0.625                                  | 16                                                     | 4                                                      | 1                                                      | 4.092 V                                                 | 4 V        |

| 011                      | 1.25                                   | 8                                                      | 2                                                      | 0.5                                                    | 2.046 V                                                 | 2 V        |

| 100                      | 2.5                                    | 4                                                      | 1                                                      | 0.25                                                   | 1.023 V                                                 | 1 V        |

| 101                      | 5.0                                    | 2                                                      | 0.5                                                    | 0.125                                                  | 0.5115 V                                                | 0.5 V      |

| 110                      | 10.0                                   | 1                                                      | 0.25                                                   | 0.0625                                                 | 0.25575 V                                               | 0.25 V     |

| 111                      | 20.0                                   | 0.5                                                    | 0.125                                                  | 0.03125                                                | 0.127875 V                                              | 0.125 V    |

Table 2-57 • Prescaler Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)

Notes:

1. LSB voltage equivalences assume VAREF = 2.56 V.

2. Full Scale voltage for n-bit mode: ((2<sup>n</sup>) - 1) x (LSB for a n-bit Conversion)

3. These are the only valid ranges for the Temperature Monitor Block Prescaler.

Table 2-58 details the settings available to control the MUX within each of the AV, AC, and AT circuits. This MUX determines whether the signal routed to the ADC is the direct analog input, prescaled signal, or output of either the Current Monitor Block or the Temperature Monitor Block.

Table 2-58 • Analog Multiplexer Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)

| Control Lines Bx[4] | Control Lines Bx[3] | ADC Connected To                      |

|---------------------|---------------------|---------------------------------------|

| 0                   | 0                   | Prescaler                             |

| 0                   | 1                   | Direct input                          |

| 1                   | 0                   | Current amplifier temperature monitor |

| 1                   | 1                   | Not valid                             |

Table 2-59 details the settings available to control the Direct Analog Input switch for the AV, AC, and AT pins.

### *Table 2-59* • Direct Analog Input Switch Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)

| Control Lines Bx[5] | Direct Input Switch |

|---------------------|---------------------|

| 0                   | Off                 |

| 1                   | On                  |

Table 2-60 details the settings available to control the polarity of the signals coming to the AV, AC, and AT pins. Note that the only valid setting for the AT pin is logic 0 to support positive voltages.

### Table 2-60 • Voltage Polarity Control Truth Table—AV (x = 0), AC (x = 1), and AT (x = 3)\*

| Control Lines Bx[6] | Input Signal Polarity |

|---------------------|-----------------------|

| 0                   | Positive              |

| 1                   | Negative              |

Note: \*The B3[6] signal for the AT pad should be kept at logic 0 to accept only positive voltages.

### I/O Software Support

In the Fusion development software, default settings have been defined for the various I/O standards supported. Changes can be made to the default settings via the use of attributes; however, not all I/O attributes are applicable for all I/O standards. Table 2-84 and Table 2-85 list the valid I/O attributes that can be manipulated by the user for each I/O standard.

Single-ended I/O standards in Fusion support up to five different drive strengths.

Table 2-84 • Fusion Standard and Advanced I/O Attributes vs. I/O Standard Applications

| I/O Standards       | SLEW<br>(output<br>only) | OUT_DRIVE<br>(output only) | SKEW<br>(all macros<br>with OE)* | RES_PULL | OUT_LOAD<br>(output only) | COMBINE_REGISTER |

|---------------------|--------------------------|----------------------------|----------------------------------|----------|---------------------------|------------------|

| LVTTL/LVCMOS 3.3 V  | 3                        | 3                          | 3                                | 3        | 3                         | 3                |

| LVCMOS 2.5 V        | 3                        | 3                          | 3                                | 3        | 3                         | 3                |

| LVCMOS 2.5/5.0 V    | 3                        | 3                          | 3                                | 3        | 3                         | 3                |

| LVCMOS 1.8 V        | 3                        | 3                          | 3                                | 3        | 3                         | 3                |

| LVCMOS 1.5 V        | 3                        | 3                          | 3                                | 3        | 3                         | 3                |

| PCI (3.3 V)         |                          |                            | 3                                |          | 3                         | 3                |

| PCI-X (3.3 V)       | 3                        |                            | 3                                |          | 3                         | 3                |

| LVDS, BLVDS, M-LVDS |                          |                            | 3                                |          |                           | 3                |

| LVPECL              |                          |                            |                                  |          |                           | 3                |

Note: \* This feature does not apply to the standard I/O banks, which are the north I/O banks of AFS090 and AFS250 devices

Device Architecture

### Table 2-115 • 2.5 V LVCMOS High Slew

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Advanced I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>zL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| 4 mA              | Std.           | 0.66              | 8.66            | 0.04             | 1.31            | 0.43              | 7.83            | 8.66            | 2.68            | 2.30            | 10.07            | 10.90            | ns    |

|                   | -1             | 0.56              | 7.37            | 0.04             | 1.11            | 0.36              | 6.66            | 7.37            | 2.28            | 1.96            | 8.56             | 9.27             | ns    |

|                   | -2             | 0.49              | 6.47            | 0.03             | 0.98            | 0.32              | 5.85            | 6.47            | 2.00            | 1.72            | 7.52             | 8.14             | ns    |

| 8 mA              | Std.           | 0.66              | 5.17            | 0.04             | 1.31            | 0.43              | 5.04            | 5.17            | 3.05            | 3.00            | 7.27             | 7.40             | ns    |

|                   | -1             | 0.56              | 4.39            | 0.04             | 1.11            | 0.36              | 4.28            | 4.39            | 2.59            | 2.55            | 6.19             | 6.30             | ns    |

|                   | -2             | 0.49              | 3.86            | 0.03             | 0.98            | 0.32              | 3.76            | 3.86            | 2.28            | 2.24            | 5.43             | 5.53             | ns    |

| 12 mA             | Std.           | 0.66              | 3.56            | 0.04             | 1.31            | 0.43              | 3.63            | 3.43            | 3.30            | 3.44            | 5.86             | 5.67             | ns    |

|                   | -1             | 0.56              | 3.03            | 0.04             | 1.11            | 0.36              | 3.08            | 2.92            | 2.81            | 2.92            | 4.99             | 4.82             | ns    |

|                   | -2             | 0.49              | 2.66            | 0.03             | 0.98            | 0.32              | 2.71            | 2.56            | 2.47            | 2.57            | 4.38             | 4.23             | ns    |

| 16 mA             | Std.           | 0.66              | 3.35            | 0.04             | 1.31            | 0.43              | 3.41            | 3.06            | 3.36            | 3.55            | 5.65             | 5.30             | ns    |

|                   | -1             | 0.56              | 2.85            | 0.04             | 1.11            | 0.36              | 2.90            | 2.60            | 2.86            | 3.02            | 4.81             | 4.51             | ns    |

|                   | -2             | 0.49              | 2.50            | 0.03             | 0.98            | 0.32              | 2.55            | 2.29            | 2.51            | 2.65            | 4.22             | 3.96             | ns    |

| 24 mA             | Std.           | 0.66              | 3.56            | 0.04             | 1.31            | 0.43              | 3.63            | 3.43            | 3.30            | 3.44            | 5.86             | 5.67             | ns    |

|                   | -1             | 0.56              | 3.03            | 0.04             | 1.11            | 0.36              | 3.08            | 2.92            | 2.81            | 2.92            | 4.99             | 4.82             | ns    |

|                   | -2             | 0.49              | 2.66            | 0.03             | 0.98            | 0.32              | 2.71            | 2.56            | 2.47            | 2.57            | 4.38             | 4.23             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

### Table 2-116 • 2.5 V LVCMOS Low Slew

Commercial Temperature Range Conditions:  $T_J$  = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 2.3 V Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 11.00           | 0.04             | 1.29            | 0.43              | 10.37           | 11.00           | 2.03            | 1.83            | ns    |

|                   | -1             | 0.56              | 9.35            | 0.04             | 1.10            | 0.36              | 8.83            | 9.35            | 1.73            | 1.56            | ns    |

|                   | -2             | 0.49              | 8.21            | 0.03             | 0.96            | 0.32              | 7.75            | 8.21            | 1.52            | 1.37            | ns    |

| 4 mA              | Std.           | 0.66              | 11.00           | 0.04             | 1.29            | 0.43              | 10.37           | 11.00           | 2.03            | 1.83            | ns    |

|                   | -1             | 0.56              | 9.35            | 0.04             | 1.10            | 0.36              | 8.83            | 9.35            | 1.73            | 1.56            | ns    |

|                   | -2             | 0.49              | 8.21            | 0.03             | 0.96            | 0.32              | 7.75            | 8.21            | 1.52            | 1.37            | ns    |

| 6 mA              | Std.           | 0.66              | 7.50            | 0.04             | 1.29            | 0.43              | 7.36            | 7.50            | 2.39            | 2.46            | ns    |

|                   | -1             | 0.56              | 6.38            | 0.04             | 1.10            | 0.36              | 6.26            | 6.38            | 2.03            | 2.10            | ns    |

|                   | -2             | 0.49              | 5.60            | 0.03             | 0.96            | 0.32              | 5.49            | 5.60            | 1.78            | 1.84            | ns    |

| 8 mA              | Std.           | 0.66              | 7.50            | 0.04             | 1.29            | 0.43              | 7.36            | 7.50            | 2.39            | 2.46            | ns    |

|                   | -1             | 0.56              | 6.38            | 0.04             | 1.10            | 0.36              | 6.26            | 6.38            | 2.03            | 2.10            | ns    |

|                   | -2             | 0.49              | 5.60            | 0.03             | 0.96            | 0.32              | 5.49            | 5.60            | 1.78            | 1.84            | ns    |

# Table 2-117 • 2.5 V LVCMOS High Slew<br/>Commercial Temperature Range Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V,<br/>Worst-Case VCCI = 2.3 V<br/>Applicable to Standard I/Os

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA              | Std.           | 0.66              | 8.20            | 0.04             | 1.29            | 0.43              | 7.24            | 8.20            | 2.03            | 1.91            | ns    |

|                   | -1             | 0.56              | 6.98            | 0.04             | 1.10            | 0.36              | 6.16            | 6.98            | 1.73            | 1.62            | ns    |

|                   | -2             | 0.49              | 6.13            | 0.03             | 0.96            | 0.32              | 5.41            | 6.13            | 1.52            | 1.43            | ns    |

| 4 mA              | Std.           | 0.66              | 8.20            | 0.04             | 1.29            | 0.43              | 7.24            | 8.20            | 2.03            | 1.91            | ns    |

|                   | -1             | 0.56              | 6.98            | 0.04             | 1.10            | 0.36              | 6.16            | 6.98            | 1.73            | 1.62            | ns    |

|                   | -2             | 0.49              | 6.13            | 0.03             | 0.96            | 0.32              | 5.41            | 6.13            | 1.52            | 1.43            | ns    |

| 6 mA              | Std.           | 0.66              | 4.77            | 0.04             | 1.29            | 0.43              | 4.55            | 4.77            | 2.38            | 2.55            | ns    |

|                   | -1             | 0.56              | 4.05            | 0.04             | 1.10            | 0.36              | 3.87            | 4.05            | 2.03            | 2.17            | ns    |

|                   | -2             | 0.49              | 3.56            | 0.03             | 0.96            | 0.32              | 3.40            | 3.56            | 1.78            | 1.91            | ns    |

| 8 mA              | Std.           | 0.66              | 4.77            | 0.04             | 1.29            | 0.43              | 4.55            | 4.77            | 2.38            | 2.55            | ns    |

|                   | -1             | 0.56              | 4.05            | 0.04             | 1.10            | 0.36              | 3.87            | 4.05            | 2.03            | 2.17            | ns    |

|                   | -2             | 0.49              | 3.56            | 0.03             | 0.96            | 0.32              | 3.40            | 3.56            | 1.78            | 1.91            | ns    |

### Timing Characteristics

### Table 2-136 • 3.3 V PCI/PCI-X

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Pro I/Os

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.81            | 0.04             | 1.05            | 1.67             | 0.43              | 2.86            | 2.00            | 3.28            | 3.61            | 5.09             | 4.23             | ns    |

| -1             | 0.56              | 2.39            | 0.04             | 0.89            | 1.42             | 0.36              | 2.43            | 1.70            | 2.79            | 3.07            | 4.33             | 3.60             | ns    |

| -2             | 0.49              | 2.09            | 0.03             | 0.78            | 1.25             | 0.32              | 2.13            | 1.49            | 2.45            | 2.70            | 3.80             | 3.16             | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 3-7 on page 3-9.

### Table 2-137 • 3.3 V PCI/PCI-X

Commercial Temperature Range Conditions:  $T_J = 70^{\circ}$ C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V Applicable to Advanced I/Os

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>ZLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.68            | 0.04             | 0.86            | 0.43             | 2.73              | 1.95            | 3.21            | 3.58            | 4.97            | 4.19             | 0.66             | ns    |

| -1             | 0.56              | 2.28            | 0.04             | 0.73            | 0.36             | 2.32              | 1.66            | 2.73            | 3.05            | 4.22            | 3.56             | 0.56             | ns    |

| -2             | 0.49              | 2.00            | 0.03             | 0.65            | 0.32             | 2.04              | 1.46            | 2.40            | 2.68            | 3.71            | 3.13             | 0.49             | ns    |

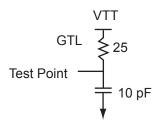

### 2.5 V GTL

Gunning Transceiver Logic is a high-speed bus standard (JESD8-3). It provides a differential amplifier input buffer and an open-drain output buffer. The VCCI pin should be connected to 2.5 V.

Table 2-141 • Minimum and Maximum DC Input and Output Levels

| 2.5 GTL            | VIL       |             | VIL VIH     |           | VOL       | VOH       | IOL | IOH | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|--------------------|-----------|-------------|-------------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength  | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA  | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 20 mA <sup>3</sup> | -0.3      | VREF – 0.05 | VREF + 0.05 | 3.6       | 0.4       | -         | 20  | 20  | 124                     | 169                     | 10               | 10               |

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

### Figure 2-125 • AC Loading

### Table 2-142 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | VREF (typ.) (V) | VTT (typ.) (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|-----------------|----------------|------------------------|

| VREF – 0.05   | VREF + 0.05    | 0.8                  | 0.8             | 1.2            | 10                     |

Note: \*Measuring point = Vtrip. See Table 2-90 on page 2-166 for a complete table of trip points.

#### Timing Characteristics

Table 2-143 • 2.5 V GTL

```

Commercial Temperature Range Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V, VREF = 0.8 V

```

| Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | t <sub>zLS</sub> | t <sub>zHS</sub> | Units |

|----------------|-------------------|-----------------|------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|-------|

| Std.           | 0.66              | 2.13            | 0.04             | 2.46            | 0.43              | 2.16            | 2.13            |                 |                 | 4.40             | 4.36             | ns    |

| -1             | 0.56              | 1.81            | 0.04             | 2.09            | 0.36              | 1.84            | 1.81            |                 |                 | 3.74             | 3.71             | ns    |

| -2             | 0.49              | 1.59            | 0.03             | 1.83            | 0.32              | 1.61            | 1.59            |                 |                 | 3.28             | 3.26             | ns    |

# **Pin Descriptions**

### **Supply Pins**

GND Ground

Ground supply voltage to the core, I/O outputs, and I/O logic.

### GNDQ Ground (quiet)

Quiet ground supply voltage to input buffers of I/O banks. Within the package, the GNDQ plane is decoupled from the simultaneous switching noise originated from the output buffer ground domain. This minimizes the noise transfer within the package and improves input signal integrity. GNDQ needs to always be connected on the board to GND. Note: In FG256, FG484, and FG676 packages, GNDQ and GND pins are connected within the package and are labeled as GND pins in the respective package pin assignment tables.

### ADCGNDREF Analog Reference Ground

Analog ground reference used by the ADC. This pad should be connected to a quiet analog ground.

### GNDA Ground (analog)

Quiet ground supply voltage to the Analog Block of Fusion devices. The use of a separate analog ground helps isolate the analog functionality of the Fusion device from any digital switching noise. A 0.2 V maximum differential voltage between GND and GNDA/GNDQ should apply to system implementation.

### GNDAQ Ground (analog quiet)

Quiet ground supply voltage to the analog I/O of Fusion devices. The use of a separate analog ground helps isolate the analog functionality of the Fusion device from any digital switching noise. A 0.2 V maximum differential voltage between GND and GNDA/GNDQ should apply to system implementation. Note: In FG256, FG484, and FG676 packages, GNDAQ and GNDA pins are connected within the package and are labeled as GNDA pins in the respective package pin assignment tables.

### GNDNVM Flash Memory Ground

Ground supply used by the Fusion device's flash memory block module(s).

#### GNDOSC Oscillator Ground

Ground supply for both integrated RC oscillator and crystal oscillator circuit.

#### VCC15A Analog Power Supply (1.5 V)

1.5 V clean analog power supply input for use by the 1.5 V portion of the analog circuitry.

#### VCC33A Analog Power Supply (3.3 V)

3.3 V clean analog power supply input for use by the 3.3 V portion of the analog circuitry.

### VCC33N Negative 3.3 V Output

This is the -3.3 V output from the voltage converter. A 2.2  $\mu$ F capacitor must be connected from this pin to ground.

#### VCC33PMP Analog Power Supply (3.3 V)

3.3 V clean analog power supply input for use by the analog charge pump. To avoid high current draw, VCC33PMP should be powered up simultaneously with or after VCC33A.

### VCCNVM Flash Memory Block Power Supply (1.5 V)

1.5 V power supply input used by the Fusion device's flash memory block module(s). To avoid high current draw, VCC should be powered up before or simultaneously with VCCNVM.

#### VCCOSC Oscillator Power Supply (3.3 V)

Power supply for both integrated RC oscillator and crystal oscillator circuit. The internal 100 MHz oscillator, powered by the VCCOSC pin, is needed for device programming, operation of the VDDN33 pump, and eNVM operation. VCCOSC is off only when VCCA is off. VCCOSC must be powered whenever the Fusion device needs to function.

### Power per I/O Pin

### Table 3-12 • Summary of I/O Input Buffer Power (per pin)—Default I/O Software Settings

|                                           | VCCI (V)                              | Static Power<br>PDC7 (mW) <sup>1</sup> | Dynamic Power<br>PAC9 (µW/MHz) <sup>2</sup> |

|-------------------------------------------|---------------------------------------|----------------------------------------|---------------------------------------------|

| Applicable to Pro I/O Banks               |                                       |                                        |                                             |

| Single-Ended                              |                                       |                                        |                                             |

| 3.3 V LVTTL/LVCMOS                        | 3.3                                   | -                                      | 17.39                                       |

| 3.3 V LVTTL/LVCMOS – Schmitt trigger      | 3.3                                   | _                                      | 25.51                                       |

| 2.5 V LVCMOS                              | 2.5                                   | _                                      | 5.76                                        |

| 2.5 V LVCMOS – Schmitt trigger            | 2.5                                   | _                                      | 7.16                                        |

| 1.8 V LVCMOS                              | 1.8                                   | _                                      | 2.72                                        |

| 1.8 V LVCMOS – Schmitt trigger            | 1.8                                   | _                                      | 2.80                                        |

| 1.5 V LVCMOS (JESD8-11)                   | 1.5                                   | _                                      | 2.08                                        |

| 1.5 V LVCMOS (JESD8-11) – Schmitt trigger | 1.5                                   | _                                      | 2.00                                        |

| 3.3 V PCI                                 | 3.3                                   | _                                      | 18.82                                       |

| 3.3 V PCI – Schmitt trigger               | 3.3                                   | _                                      | 20.12                                       |

| 3.3 V PCI-X                               | 3.3                                   | _                                      | 18.82                                       |

| 3.3 V PCI-X – Schmitt trigger             | 3.3                                   | _                                      | 20.12                                       |

| Voltage-Referenced                        |                                       |                                        |                                             |

| 3.3 V GTL                                 | 3.3                                   | 2.90                                   | 8.23                                        |

| 2.5 V GTL                                 | 2.5                                   | 2.13                                   | 4.78                                        |

| 3.3 V GTL+                                | 3.3                                   | 2.81                                   | 4.14                                        |

| 2.5 V GTL+                                | 2.5                                   | 2.57                                   | 3.71                                        |

| HSTL (I)                                  | 1.5                                   | 0.17                                   | 2.03                                        |

| HSTL (II)                                 | 1.5                                   | 0.17                                   | 2.03                                        |

| SSTL2 (I)                                 | 2.5                                   | 1.38                                   | 4.48                                        |

| SSTL2 (II)                                | 2.5                                   | 1.38                                   | 4.48                                        |

| SSTL3 (I)                                 | 3.3                                   | 3.21                                   | 9.26                                        |

| SSTL3 (II)                                | 3.3                                   | 3.21                                   | 9.26                                        |

| Differential                              | · · · · · · · · · · · · · · · · · · · |                                        | -                                           |

| LVDS                                      | 2.5                                   | 2.26                                   | 1.50                                        |

| LVPECL                                    | 3.3                                   | 5.71                                   | 2.17                                        |

Notes:

1. PDC7 is the static power (where applicable) measured on VCCI.

2. PAC9 is the total dynamic power measured on VCC and VCCI.

### Total Static Power Consumption—PSTAT

Number of Quads used:  $N_{QUADS} = 4$ Number of NVM blocks available (AFS600):  $N_{NVM-BLOCKS} = 2$ Number of input pins used:  $N_{INPUTS} = 30$ Number of output pins used:  $N_{OUTPUTS} = 40$

### **Operating Mode**

$\mathsf{P}_{\mathsf{STAT}} = \mathsf{PDC1} + (\mathsf{N}_{\mathsf{NVM-BLOCKS}} * \mathsf{PDC4}) + \mathsf{PDC5} + (\mathsf{N}_{\mathsf{QUADS}} * \mathsf{PDC6}) + (\mathsf{N}_{\mathsf{INPUTS}} * \mathsf{PDC7}) + (\mathsf{N}_{\mathsf{OUTPUTS}} * \mathsf{PDC8})$

P<sub>STAT</sub> = 7.50 mW + (2 \* 1.19 mW) + 8.25 mW + (4 \* 3.30 mW) + (30 \* 0.00) + (40 \* 0.00)

P<sub>STAT</sub> = 31.33 mW

### Standby Mode

P<sub>STAT</sub> = PDC2

$P_{STAT} = 0.03 \text{ mW}$

### Sleep Mode

$P_{STAT} = PDC3$

$P_{STAT} = 0.03 \text{ mW}$

### Total Power Consumption—PTOTAL

In operating mode, the total power consumption of the device is 174.39 mW:

$P_{TOTAL} = P_{STAT} + P_{DYN}$

P<sub>TOTAL</sub> = 143.06 mW + 31.33 mW

P<sub>TOTAL</sub> = 174.39 mW

In standby mode, the total power consumption of the device is limited to 0.66 mW:

$P_{TOTAL} = P_{STAT} + P_{DYN}$

$P_{TOTAL} = 0.03 \text{ mW} + 0.63 \text{ mW}$

$P_{TOTAL} = 0.66 \text{ mW}$

In sleep mode, the total power consumption of the device drops as low as 0.03 mW:

$P_{TOTAL} = P_{STAT} + P_{DYN}$  $P_{TOTAL} = 0.03 \text{ mW}$

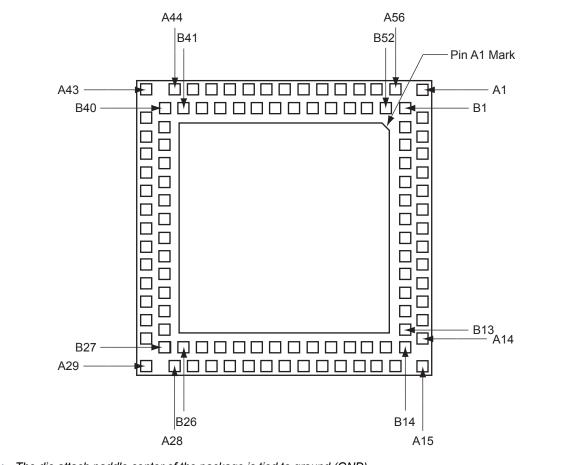

# 4 – Package Pin Assignments

# QN108

Note: The die attach paddle center of the package is tied to ground (GND).

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/default.aspx.

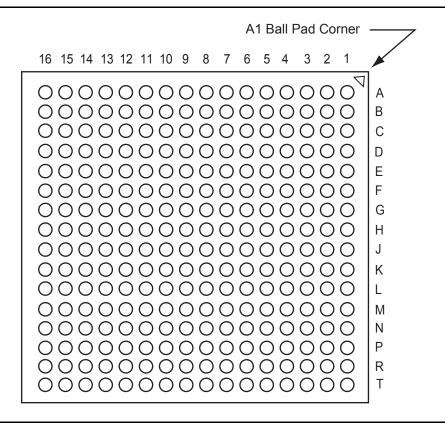

### FG256

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/default.aspx.

|            |                 | FG256           |                 |                  |

|------------|-----------------|-----------------|-----------------|------------------|

| Pin Number | AFS090 Function | AFS250 Function | AFS600 Function | AFS1500 Function |

| M15        | TRST            | TRST            | TRST            | TRST             |

| M16        | GND             | GND             | GND             | GND              |

| N1         | GEB2/IO42PDB3V0 | GEB2/IO59PDB3V0 | GEB2/IO59PDB4V0 | GEB2/IO86PDB4V0  |

| N2         | GEA2/IO42NDB3V0 | IO59NDB3V0      | IO59NDB4V0      | IO86NDB4V0       |

| N3         | NC              | GEA2/IO58PPB3V0 | GEA2/IO58PPB4V0 | GEA2/IO85PPB4V0  |

| N4         | VCC33PMP        | VCC33PMP        | VCC33PMP        | VCC33PMP         |

| N5         | VCC15A          | VCC15A          | VCC15A          | VCC15A           |

| N6         | NC              | NC              | AG0             | AG0              |

| N7         | AC1             | AC1             | AC3             | AC3              |

| N8         | AG3             | AG3             | AG5             | AG5              |

| N9         | AV3             | AV3             | AV5             | AV5              |

| N10        | AG4             | AG4             | AG6             | AG6              |

| N11        | NC              | NC              | AC8             | AC8              |

| N12        | GNDA            | GNDA            | GNDA            | GNDA             |

| N13        | VCC33A          | VCC33A          | VCC33A          | VCC33A           |

| N14        | VCCNVM          | VCCNVM          | VCCNVM          | VCCNVM           |

| N15        | ТСК             | ТСК             | ТСК             | ТСК              |

| N16        | TDI             | TDI             | TDI             | TDI              |

| P1         | VCCNVM          | VCCNVM          | VCCNVM          | VCCNVM           |

| P2         | GNDNVM          | GNDNVM          | GNDNVM          | GNDNVM           |

| P3         | GNDA            | GNDA            | GNDA            | GNDA             |

| P4         | NC              | NC              | AC0             | AC0              |

| P5         | NC              | NC              | AG1             | AG1              |

| P6         | NC              | NC              | AV1             | AV1              |

| P7         | AG0             | AG0             | AG2             | AG2              |

| P8         | AG2             | AG2             | AG4             | AG4              |

| P9         | GNDA            | GNDA            | GNDA            | GNDA             |

| P10        | NC              | AC5             | AC7             | AC7              |

| P11        | NC              | NC              | AV8             | AV8              |

| P12        | NC              | NC              | AG8             | AG8              |

| P13        | NC              | NC              | AV9             | AV9              |

| P14        | ADCGNDREF       | ADCGNDREF       | ADCGNDREF       | ADCGNDREF        |

| P15        | PTBASE          | PTBASE          | PTBASE          | PTBASE           |

| P16        | GNDNVM          | GNDNVM          | GNDNVM          | GNDNVM           |

| R1         | VCCIB3          | VCCIB3          | VCCIB4          | VCCIB4           |

| R2         | PCAP            | PCAP            | PCAP            | PCAP             |

| R3         | NC              | NC              | AT1             | AT1              |

| R4         | NC              | NC              | AT0             | AT0              |

|               | FG484           |                  |               | FG484           |                  |

|---------------|-----------------|------------------|---------------|-----------------|------------------|

| Pin<br>Number | AFS600 Function | AFS1500 Function | Pin<br>Number | AFS600 Function | AFS1500 Function |

| B5            | IO05NDB0V0      | IO04NDB0V0       | C18           | VCCIB1          | VCCIB1           |

| B6            | IO05PDB0V0      | IO04PDB0V0       | C19           | VCOMPLB         | VCOMPLB          |

| B7            | GND             | GND              | C20           | GBA2/IO30PDB2V0 | GBA2/IO44PDB2V0  |

| B8            | IO10NDB0V1      | IO09NDB0V1       | C21           | NC              | IO48PSB2V0       |

| B9            | IO13PDB0V1      | IO11PDB0V1       | C22           | GBB2/IO31PDB2V0 | GBB2/IO45PDB2V0  |

| B10           | GND             | GND              | D1            | IO82NDB4V0      | IO121NDB4V0      |

| B11           | IO17NDB1V0      | IO24NDB1V0       | D2            | GND             | GND              |

| B12           | IO18NDB1V0      | IO26NDB1V0       | D3            | IO83NDB4V0      | IO123NDB4V0      |

| B13           | GND             | GND              | D4            | GAC2/IO83PDB4V0 | GAC2/IO123PDB4V0 |

| B14           | IO21NDB1V0      | IO31NDB1V1       | D5            | GAA2/IO85PDB4V0 | GAA2/IO125PDB4V0 |

| B15           | IO21PDB1V0      | IO31PDB1V1       | D6            | GAC0/IO03NDB0V0 | GAC0/IO03NDB0V0  |

| B16           | GND             | GND              | D7            | GAC1/IO03PDB0V0 | GAC1/IO03PDB0V0  |

| B17           | GBC1/IO26PDB1V1 | GBC1/IO40PDB1V2  | D8            | IO09NDB0V1      | IO10NDB0V1       |

| B18           | GBA1/IO28PDB1V1 | GBA1/IO42PDB1V2  | D9            | IO09PDB0V1      | IO10PDB0V1       |

| B19           | GND             | GND              | D10           | IO11NDB0V1      | IO14NDB0V2       |

| B20           | VCCPLB          | VCCPLB           | D11           | IO16NDB1V0      | IO23NDB1V0       |

| B21           | GND             | GND              | D12           | IO16PDB1V0      | IO23PDB1V0       |

| B22           | VCC             | NC               | D13           | NC              | IO32NPB1V1       |

| C1            | IO82PDB4V0      | IO121PDB4V0      | D14           | IO23NDB1V1      | IO34NDB1V1       |

| C2            | NC              | IO122PSB4V0      | D15           | IO23PDB1V1      | IO34PDB1V1       |

| C3            | IO00NDB0V0      | IO00NDB0V0       | D16           | IO25PDB1V1      | IO37PDB1V2       |

| C4            | IO00PDB0V0      | IO00PDB0V0       | D17           | GBB1/IO27PDB1V1 | GBB1/IO41PDB1V2  |

| C5            | VCCIB0          | VCCIB0           | D18           | VCCIB2          | VCCIB2           |

| C6            | IO06NDB0V0      | IO05NDB0V1       | D19           | NC              | IO47PPB2V0       |

| C7            | IO06PDB0V0      | IO05PDB0V1       | D20           | IO30NDB2V0      | IO44NDB2V0       |

| C8            | VCCIB0          | VCCIB0           | D21           | GND             | GND              |

| C9            | IO13NDB0V1      | IO11NDB0V1       | D22           | IO31NDB2V0      | IO45NDB2V0       |

| C10           | IO11PDB0V1      | IO14PDB0V2       | E1            | IO81NDB4V0      | IO120NDB4V0      |

| C11           | VCCIB0          | VCCIB0           | E2            | IO81PDB4V0      | IO120PDB4V0      |

| C12           | VCCIB1          | VCCIB1           | E3            | VCCIB4          | VCCIB4           |

| C13           | IO20NDB1V0      | IO29NDB1V1       | E4            | GAB2/IO84PDB4V0 | GAB2/IO124PDB4V0 |

| C14           | IO20PDB1V0      | IO29PDB1V1       | E5            | IO85NDB4V0      | IO125NDB4V0      |

| C15           | VCCIB1          | VCCIB1           | E6            | GND             | GND              |

| C16           | IO25NDB1V1      | IO37NDB1V2       | E7            | VCCIB0          | VCCIB0           |

| C17           | GBB0/IO27NDB1V1 | GBB0/IO41NDB1V2  | E8            | NC              | IO08NDB0V1       |

| Revision                  | Changes                                                                                                                                                                                                                                                                                | Page            |  |  |  |  |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| Revision 2<br>(continued) | The prescalar range for the 'Analog Input (direct input to ADC)" configurations was removed as inapplicable for direct inputs. The input resistance for direct inputs is covered in Table 2-50 • ADC Characteristics in Direct Input Mode (SAR 31201).                                 | 2-120           |  |  |  |  |  |

|                           | The "Examples" for calibrating accuracy for ADC channels were revised and corrected to make them consistent with terminology in the associated tables (SARs 36791, 36773).                                                                                                             |                 |  |  |  |  |  |

|                           | A note was added to Table 2-56 • Analog Quad ACM Byte Assignment and the introductory text for Table 2-66 • Internal Temperature Monitor Control Truth Table, stating that for the internal temperature monitor to function, Bit 0 of Byte 2 for all 10 Quads must be set (SAR 34418). | 2-129,<br>2-131 |  |  |  |  |  |

|                           | t <sub>DOUT</sub> was corrected to t <sub>DIN</sub> in Figure 2-116 • Input Buffer Timing Model and Delays (example) (SAR 37115).                                                                                                                                                      | 2-161           |  |  |  |  |  |

|                           | The formulas in the table notes for Table 2-97 • I/O Weak Pull-Up/Pull-Down Resistances were corrected (SAR 34751).                                                                                                                                                                    | 2-171           |  |  |  |  |  |

|                           | The AC Loading figures in the "Single-Ended I/O Characteristics" section were updated to match tables in the "Summary of I/O Timing Characteristics – Default I/O Software Settings" section (SAR 34877).                                                                              |                 |  |  |  |  |  |

|                           | The following notes were removed from Table 2-168 • Minimum and Maximum DC<br>Input and Output Levels (SAR 34808):<br>±5%<br>Differential input voltage = ±350 mV                                                                                                                      | 2-209           |  |  |  |  |  |

|                           | An incomplete, duplicate sentence was removed from the end of the "GNDAQ Ground (analog quiet)" pin description (SAR 30185).                                                                                                                                                           | 2-223           |  |  |  |  |  |

|                           | Information about configuration of unused I/Os was added to the "User Pins" section (SAR 32642).                                                                                                                                                                                       | 2-225           |  |  |  |  |  |

|                           | The following information was added to the pin description for "XTAL1 Crystal Oscillator Circuit Input" and "XTAL2 Crystal Oscillator Circuit Input" (SAR 24119).                                                                                                                      | 2-227           |  |  |  |  |  |

|                           | The input resistance to ground value in Table 3-3 • Input Resistance of Analog Pads for Analog Input (direct input to ADC), was corrected from 1 M $\Omega$ (typical) to 2 k $\Omega$ (typical) (SAR 34371).                                                                           | 3-4             |  |  |  |  |  |

|                           | The Storage Temperature column in Table 3-5 • FPGA Programming, Storage, and Operating Limits stated Min. $T_J$ twice for commercial and industrial product grades and has been corrected to Min. $T_J$ and Max. $T_J$ (SAR 29416).                                                    | 3-5             |  |  |  |  |  |

|                           | The reference to guidelines for global spines and VersaTile rows, given in the "Global Clock Dynamic Contribution—PCLOCK" section, was corrected to the "Spine Architecture" section of the Global Resources chapter in the <i>Fusion FPGA Fabric User's Guide</i> (SAR 34741).        | 3-24            |  |  |  |  |  |

|                           | Package names used in the "Package Pin Assignments" section were revised to match standards given in <i>Package Mechanical Drawings</i> (SAR 36612).                                                                                                                                   | 4-1             |  |  |  |  |  |

| July 2010                 | The versioning system for datasheets has been changed. Datasheets are assigned<br>a revision number that increments each time the datasheet is revised. The "Fusion<br>Device Status" table indicates the status for each device in the device family.                                 | N/A             |  |  |  |  |  |

Fusion Family of Mixed Signal FPGAs

| Revision     | Changes                                                                                                                                                                                                                                                                 | Page  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|

| Advance v0.3 | The "Temperature Monitor" section was updated.                                                                                                                                                                                                                          | 2-96  |  |  |

| (continued)  | EQ 2 is new.                                                                                                                                                                                                                                                            | 2-103 |  |  |

|              | The "ADC Description" section was updated.                                                                                                                                                                                                                              |       |  |  |

|              | Figure 2-16 • Fusion Clocking Options was updated.                                                                                                                                                                                                                      |       |  |  |

|              | Table 2-46 · Analog Channel Specifications was updated.                                                                                                                                                                                                                 | 2-118 |  |  |

|              | The notes in Table 2-72 • Fusion Standard and Advanced I/O – Hot-Swap and 5 V Input Tolerance Capabilities were updated.                                                                                                                                                |       |  |  |

|              | The "Simultaneously Switching Outputs and PCB Layout" section is new.                                                                                                                                                                                                   | 2-149 |  |  |

|              | LVPECL and LVDS were updated in Table 2-81 • Fusion Standard and Advanced I/O Attributes vs. I/O Standard Applications.                                                                                                                                                 |       |  |  |

|              | LVPECL and LVDS were updated in Table 2-82 • Fusion Pro I/O Attributes vs. I/O Standard Applications.                                                                                                                                                                   |       |  |  |

|              | The "Timing Model" was updated.                                                                                                                                                                                                                                         |       |  |  |

|              | All voltage-referenced Minimum and Maximum DC Input and Output Level tables were updated.                                                                                                                                                                               |       |  |  |

|              | All Timing Characteristic tables were updated                                                                                                                                                                                                                           | N/A   |  |  |

|              | <ul> <li>Table 2-83 • Summary of Maximum and Minimum DC Input and Output Levels<br/>Applicable to Commercial and Industrial Conditions was updated.</li> <li>Table 2-79 • Summary of I/O Timing Characteristics – Software Default Settings<br/>was updated.</li> </ul> |       |  |  |

|              |                                                                                                                                                                                                                                                                         |       |  |  |

|              | Table 2-93 • I/O Output Buffer Maximum Resistances <sup>1</sup> was updated.                                                                                                                                                                                            |       |  |  |

|              | The "BLVDS/M-LVDS" section is new. BLVDS and M-LVDS are two new I/O standards included in the datasheet.<br>The "CoreMP7 and Cortex-M1 Software Tools" section is new.                                                                                                  |       |  |  |

|              |                                                                                                                                                                                                                                                                         |       |  |  |

|              | Table 2-83 • Summary of Maximum and Minimum DC Input and Output Levels           Applicable to Commercial and Industrial Conditions was updated.                                                                                                                        | 2-165 |  |  |

|              | Table 2-79 • Summary of I/O Timing Characteristics – Software Default Settings was updated.                                                                                                                                                                             | 2-134 |  |  |

|              | Table 2-93 • I/O Output Buffer Maximum Resistances <sup>1</sup> was updated.                                                                                                                                                                                            | 2-171 |  |  |

|              | The "BLVDS/M-LVDS" section is new. BLVDS and M-LVDS are two new I/O standards included in the datasheet.                                                                                                                                                                | 2-211 |  |  |

|              | The "108-Pin QFN" table for the AFS090 device is new.                                                                                                                                                                                                                   |       |  |  |

|              | The "180-Pin QFN" table for the AFS090 device is new.                                                                                                                                                                                                                   | 3-4   |  |  |

|              | The "208-Pin PQFP" table for the AFS090 device is new.                                                                                                                                                                                                                  | 3-8   |  |  |

|              | The "256-Pin FBGA" table for the AFS090 device is new.                                                                                                                                                                                                                  | 3-12  |  |  |

|              | The "256-Pin FBGA" table for the AFS250 device is new.                                                                                                                                                                                                                  | 3-12  |  |  |