#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                                  |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | ARM® Cortex®-A9                                                         |

| Number of Cores/Bus Width       | 4 Core, 32-Bit                                                          |

| Speed                           | 1.0GHz                                                                  |

| Co-Processors/DSP               | Multimedia; NEON™ SIMD                                                  |

| RAM Controllers                 | LPDDR2, DDR3L, DDR3                                                     |

| Graphics Acceleration           | Yes                                                                     |

| Display & Interface Controllers | HDMI, Keypad, LCD, LVDS, MIPI/DSI, Parallel                             |

| Ethernet                        | 10/100/1000Mbps (1)                                                     |

| SATA                            | SATA 3Gbps (1)                                                          |

| USB                             | USB 2.0 + PHY (3), USB 2.0 OTG + PHY (1)                                |

| Voltage - I/O                   | 1.8V, 2.5V, 2.8V, 3.3V                                                  |

| Operating Temperature           | -20°C ~ 105°C (TJ)                                                      |

| Security Features               | ARM TZ, A-HAB, CAAM, CSU, SJC, SNVS                                     |

| Package / Case                  | 624-LFBGA, FCBGA                                                        |

| Supplier Device Package         | 624-FCPBGA (21x21)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6qp5eym1ab |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.1.2 Thermal Resistance

### NOTE

Per JEDEC JESD51-2, the intent of thermal resistance measurements is solely for a thermal performance comparison of one package to another in a standardized environment. This methodology is not meant to and will not predict the performance of a package in an application-specific environment.

## 4.1.2.1 FCPBGA Package Thermal Resistance

Table 5 provides the FCPBGA package thermal resistance data for the *non-lidded* package type.

| Thermal Parameter                     | Test Conditions                                           | Symbol                 | Value | Unit |

|---------------------------------------|-----------------------------------------------------------|------------------------|-------|------|

| Junction to Ambient <sup>1</sup>      | Single-layer board (1s); natural convection <sup>2</sup>  | R <sub>θJA</sub>       | 31    | °C/W |

|                                       | Four-layer board (2s2p); natural convection <sup>2</sup>  | $R_{	extsf{	heta}JA}$  | 22    | °C/W |

| Junction to Ambient <sup>1</sup>      | Single-layer board (1s); air flow 200 ft/min <sup>3</sup> | $R_{	extsf{	heta}JMA}$ | 24    | °C/W |

|                                       | Four-layer board (2s2p); air flow 200 ft/min <sup>3</sup> | $R_{\thetaJMA}$        | 18    | °C/W |

| Junction to Board <sup>1,4</sup>      | _                                                         | R <sub>θJB</sub>       | 12    | °C/W |

| Junction to Case (top) <sup>1,5</sup> | _                                                         | R <sub>0JCtop</sub>    | <0.1  | °C/W |

Table 5. FCPBGA Package Thermal Resistance Data (Non-Lidded)

<sup>1</sup> Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

<sup>2</sup> Per JEDEC JESD51-3 with the single layer board horizontal. Thermal test board meets JEDEC specification for the specified package.

<sup>3</sup> Per JEDEC JESD51-6 with the board horizontal.

<sup>4</sup> Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

<sup>5</sup> Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1). The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

# 4.1.3 Operating Ranges

Table 6 provides the operating ranges of the i.MX 6DualPlus/6QuadPlus processors.

| Parameter<br>Description                          | Symbol                                  | Min                  | Тур  | Max <sup>1</sup> | Unit | Comment <sup>2</sup>                                                                                                                                                                           |

|---------------------------------------------------|-----------------------------------------|----------------------|------|------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Run mode:<br>LDO enabled                          | VDD_ARM_IN<br>VDD_ARM23_IN <sup>3</sup> | 1.4 <sup>4</sup>     |      | 1.5              | V    | LDO Output Set Point (VDD_ARM_CAP <sup>5</sup> ) of 1.275 V minimum for operation up to 1200 MHz. <b>Only supported in LDO enabled mode.</b>                                                   |

|                                                   |                                         | 1.35 <sup>4</sup>    | _    | 1.5              | V    | LDO Output Set Point (VDD_ARM_CAP <sup>5</sup> ) of 1.225 V minimum for operation up to 996 MHz.                                                                                               |

|                                                   |                                         | 1.275 <sup>4</sup>   | —    | 1.5              | V    | LDO Output Set Point (VDD_ARM_CAP <sup>5</sup> ) of 1.150 V minimum for operation up to 792 MHz.                                                                                               |

|                                                   |                                         | 1.05 <sup>4</sup>    | _    | 1.5              | V    | LDO Output Set Point (VDD_ARM_CAP <sup>5</sup> ) of 0.925 V minimum for operation up to 396 MHz.                                                                                               |

|                                                   | VDD_SOC_IN <sup>6</sup>                 | 1.35 <sup>4</sup>    | —    | 1.5              | V    | 264 MHz < VPU $\leq$ 352 MHz; VDDSOC and VDDPU LDO outputs (VDD_SOC_CAP and VDD_PU_CAP) require 1.275 V minimum.                                                                               |

|                                                   |                                         | 1.275 <sup>4,7</sup> | —    | 1.5              | V    | $VPU \le 264$ MHz; VDDSOC and VDDPU LDO outputs (VDD_SOC_CAP and VDD_PU_CAP) require 1.15 V minimum.                                                                                           |

| Run mode:                                         | VDD_ARM_IN                              | 1.225                | _    | 1.3              | V    | LDO bypassed for operation up to 996 MHz.                                                                                                                                                      |

| LDO bypassed <sup>8</sup>                         | VDD_ARM23_IN <sup>3</sup>               | 1.150                | —    | 1.3              | V    | LDO bypassed for operation up to 792 MHz.                                                                                                                                                      |

|                                                   |                                         | 0.925                | —    | 1.3              | V    | LDO bypassed for operation up to 396 MHz.                                                                                                                                                      |

|                                                   | VDD_SOC_IN <sup>6</sup>                 | 1.225                | —    | 1.3              | V    | 264 MHz < VPU ≤ 352 MHz                                                                                                                                                                        |

|                                                   |                                         | 1.15                 | —    | 1.3              | V    | VPU ≤ 264 MHz                                                                                                                                                                                  |

| Standby/DSM mode                                  | VDD_ARM_IN<br>VDD_ARM23_IN <sup>3</sup> | 0.9                  | _    | 1.3              | V    | See Table 9, "Stop Mode Current and Power Consumption," on page 28.                                                                                                                            |

|                                                   | VDD_SOC_IN                              | 1.05                 | _    | 1.3              | V    |                                                                                                                                                                                                |

| VDD_HIGH internal<br>regulator                    | VDD_HIGH_IN <sup>9</sup>                | 2.7                  | _    | 3.6              | V    | Must match the range of voltages that the rechargeable backup battery supports.                                                                                                                |

| Backup battery supply range                       | VDD_SNVS_IN <sup>9</sup>                | 2.8                  | —    | 3.6              | V    | Should be supplied from the same supply as VDD_HIGH_IN, if the system does not require keeping real time and other data on OFF state.                                                          |

| USB supply voltages                               | USB_OTG_VBUS                            | 4.4                  | —    | 5.25             | V    | —                                                                                                                                                                                              |

|                                                   | USB_H1_VBUS                             | 4.4                  | —    | 5.25             | V    | —                                                                                                                                                                                              |

| DDR I/O supply                                    | NVCC_DRAM                               | 1.14                 | 1.2  | 1.3              | V    | LPDDR2                                                                                                                                                                                         |

|                                                   |                                         | 1.425                | 1.5  | 1.575            | V    | DDR3                                                                                                                                                                                           |

|                                                   |                                         | 1.283                | 1.35 | 1.45             | V    | DDR3L                                                                                                                                                                                          |

| Supply for RGMII I/O<br>power group <sup>10</sup> | NVCC_RGMII                              | 1.15                 | —    | 2.625            | V    | <ul> <li>1.15 V – 1.30 V in HSIC 1.2 V mode</li> <li>1.43 V – 1.58 V in RGMII 1.5 V mode</li> <li>1.70 V – 1.90 V in RGMII 1.8 V mode</li> <li>2.25 V – 2.625 V in RGMII 2.5 V mode</li> </ul> |

### Table 6. Operating Ranges

| Parameter<br>Description    | Symbol                                                                                                                                                                      | Min   | Тур                 | Max <sup>1</sup> | Unit | Comment <sup>2</sup>                                                                                                                                                                                                              |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------|------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO supplies <sup>10</sup> | NVCC_CSI,<br>NVCC_EIM0,<br>NVCC_EIM1,<br>NVCC_EIM2,<br>NVCC_ENET,<br>NVCC_GPI0,<br>NVCC_GPI0,<br>NVCC_LCD,<br>NVCC_LCD,<br>NVCC_SD1,<br>NVCC_SD2,<br>NVCC_SD3,<br>NVCC_JTAG | 1.65  | 1.8,<br>2.8,<br>3.3 | 3.6              | V    | Isolation between the NVCC_EIMx and<br>NVCC_SDx different supplies allow them to<br>operate at different voltages within the specified<br>range.<br>Example: NVCC_EIM1 can operate at 1.8 V<br>while NVCC_EIM2 operates at 3.3 V. |

|                             | NVCC_LVDS_2P5 <sup>11</sup><br>NVCC_MIPI                                                                                                                                    | 2.25  | 2.5                 | 2.75             | V    | _                                                                                                                                                                                                                                 |

| HDMI supply voltages        | HDMI_VP                                                                                                                                                                     | 0.99  | 1.1                 | 1.3              | V    | —                                                                                                                                                                                                                                 |

|                             | HDMI_VPH                                                                                                                                                                    | 2.25  | 2.5                 | 2.75             | V    | —                                                                                                                                                                                                                                 |

| PCIe supply voltages        | PCIE_VP                                                                                                                                                                     | 1.023 | 1.1                 | 1.3              | V    | —                                                                                                                                                                                                                                 |

|                             | PCIE_VPH                                                                                                                                                                    | 2.325 | 2.5                 | 2.75             | V    | —                                                                                                                                                                                                                                 |

|                             | PCIE_VPTX                                                                                                                                                                   | 1.023 | 1.1                 | 1.3              | V    | _                                                                                                                                                                                                                                 |

| SATA Supply voltages        | SATA_VP                                                                                                                                                                     | 0.99  | 1.1                 | 1.3              | V    | —                                                                                                                                                                                                                                 |

|                             | SATA_VPH                                                                                                                                                                    | 2.25  | 2.5                 | 2.75             | V    | —                                                                                                                                                                                                                                 |

| Junction temperature        | Т                                                                                                                                                                           | -20   | 95                  | 105              | °C   | See <i>i.MX</i> 6Dual/6Quad Product Lifetime Usage<br>Estimates Application Note, AN4724, for<br>information on product lifetime (power-on<br>years) for this processor.                                                          |

### Table 6. Operating Ranges (continued)

Applying the maximum voltage results in maximum power consumption and heat generation. NXP recommends a voltage set point = (Vmin + the supply tolerance). This results in an optimized power/speed ratio.

<sup>2</sup> See the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG) for bypass capacitors requirements for each of the \*\_CAP supply outputs.

- <sup>3</sup> For Quad core system, connect to VDD\_ARM\_IN. For Dual core system, may be shorted to GND together with VDD\_ARM23\_CAP to reduce leakage.

- <sup>4</sup> VDD\_ARM\_IN and VDD\_SOC\_IN must be at least 125 mV higher than the LDO Output Set Point for correct voltage regulation.

<sup>5</sup> VDD\_ARM\_CAP must not exceed VDD\_CACHE\_CAP by more than +50 mV. VDD\_CACHE\_CAP must not exceed VDD\_ARM\_CAP by more than 200 mV.

- <sup>6</sup> VDD\_SOC\_CAP and VDD\_PU\_CAP must be equal.

- <sup>7</sup> In LDO enabled mode, the internal LDO output set points must be configured such that the:

VDD\_ARM LDO output set point does not exceed the VDD\_SOC LDO output set point by more than 100 mV.

VDD\_SOC LDO output set point is equal to the VDD\_PU LDO output set point.

The VDD\_ARM LDO output set point can be lower than the VDD\_SOC LDO output set point, however, the minimum output set points shown in this table must be maintained.

- <sup>8</sup> In LDO bypassed mode, the external power supply must ensure that VDD\_ARM\_IN does not exceed VDD\_SOC\_IN by more than 100 mV. The VDD\_ARM\_IN supply voltage can be lower than the VDD\_SOC\_IN supply voltage. The minimum voltages shown in this table must be maintained.

- <sup>9</sup> To set VDD\_SNVS\_IN voltage with respect to Charging Currents and RTC, see the *Hardware Development Guide for i.MX* 6Dual, 6Quad, 6Solo, 6DualLite Families of Applications Processors (IMX6DQ6SDLHDG).

### i.MX 6DualPlus/6QuadPlus Applications Processors Consumer Products, Rev. 2, 09/2017

1

<sup>10</sup> All digital I/O supplies (NVCC\_xxxx) must be powered under normal conditions whether the associated I/O pins are in use or not, and associated I/O pins need to have a pull-up or pull-down resistor applied to limit any floating gate current.

<sup>11</sup> This supply also powers the pre-drivers of the DDR I/O pins; therefore, it must always be provided, even when LVDS is not used.

# 4.1.4 External Clock Sources

Each i.MX 6DualPlus/6QuadPlus processor has two external input system clocks: a low frequency (RTC\_XTALI) and a high frequency (XTALI).

The RTC\_XTALI is used for low-frequency functions. It supplies the clock for wake-up circuit, power-down real time clock operation, and slow system and watchdog counters. The clock input can be connected to either an external oscillator or a crystal using the internal oscillator amplifier. Additionally, there is an internal ring oscillator, that can be used instead of RTC\_XTALI when accuracy is not important.

The system clock input XTALI is used to generate the main system clock. It supplies the PLLs and other peripherals. The system clock input can be connected to either an external oscillator or a crystal using the internal oscillator amplifier.

### NOTE

The internal RTC oscillator does not provide an accurate frequency and is affected by process, voltage and temperature variations. NXP strongly recommends using an external crystal as the RTC\_XTALI reference. If the internal oscillator is used instead, careful consideration should be given to the timing implications on all of the SoC modules dependent on this clock.

Table 7 shows the interface frequency requirements.

| Table 7. | External | Input | Clock | Frequency |

|----------|----------|-------|-------|-----------|

|----------|----------|-------|-------|-----------|

| Parameter Description               | Symbol            | Min | Тур                       | Мах | Unit |

|-------------------------------------|-------------------|-----|---------------------------|-----|------|

| RTC_XTALI Oscillator <sup>1,2</sup> | f <sub>ckil</sub> | _   | 32.768 <sup>3</sup> /32.0 | _   | kHz  |

| XTALI Oscillator <sup>4,2</sup>     | f <sub>xtal</sub> | _   | 24                        | _   | MHz  |

<sup>1</sup> External oscillator or a crystal with internal oscillator amplifier.

<sup>2</sup> The required frequency stability of this clock source is application dependent. For recommendations, see the Hardware Development Guide for i.MX 6Dual, 6Quad, 6Solo, 6DualLite Families of Applications Processors (IMX6DQ6SDLHDG).

<sup>3</sup> Recommended nominal frequency 32.768 kHz.

<sup>4</sup> External oscillator or a fundamental frequency crystal with internal oscillator amplifier.

The typical values shown in Table 7 are required for use with NXP BSPs to ensure precise time keeping and USB operation. For RTC\_XTALI operation, two clock sources are available:

- On-chip 40 kHz ring oscillator: This clock source has the following characteristics:

- Approximately 25 µA more Idd than crystal oscillator

- Approximately  $\pm 50\%$  tolerance

- No external component required

- Starts up quicker than 32 kHz crystal oscillator

- External crystal oscillator with on-chip support circuit

# 4.4.5 MLB PLL

The MediaLB PLL is necessary in the MediaLB 6-Pin implementation to phase align the internal and external clock edges, effectively tuning out the delay of the differential clock receiver and is also responsible for generating the higher speed internal clock, when the internal-to-external clock ratio is not 1:1.

| Table 18. | MLB PLL | Electrical | Parameters |

|-----------|---------|------------|------------|

|-----------|---------|------------|------------|

| Parameter | Value   |

|-----------|---------|

| Lock time | <1.5 ms |

# 4.4.6 ARM PLL

| Parameter          | Value                  |

|--------------------|------------------------|

| Clock output range | 650 MHz~1.3 GHz        |

| Reference clock    | 24 MHz                 |

| Lock time          | <2250 reference cycles |

# 4.5 **On-Chip Oscillators**

# 4.5.1 OSC24M

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implements an oscillator. The oscillator is powered from NVCC\_PLL\_OUT.

The system crystal oscillator consists of a Pierce-type structure running off the digital supply. A straight forward biased-inverter implementation is used.

# 4.5.2 OSC32K

This block implements an amplifier that when combined with a suitable quartz crystal and external load capacitors implements a low power oscillator. It also implements a power mux such that it can be powered from either a ~3 V backup battery (VDD\_SNVS\_IN) or VDD\_HIGH\_IN such as the oscillator consumes power from VDD\_HIGH\_IN when that supply is available and transitions to the back up battery when VDD\_HIGH\_IN is lost.

In addition, if the clock monitor determines that the OSC32K is not present, then the source of the 32 kHz clock will automatically switch to the internal ring oscillator.

# 4.7.1 General Purpose I/O AC Parameters

The I/O AC parameters for GPIO in slow and fast modes are presented in the Table 28 and Table 29, respectively. Note that the fast or slow I/O behavior is determined by the appropriate control bits in the IOMUXC control registers.

| Parameter                                                         | Symbol | Test Condition                                             | Min | Тур | Мах                    | Unit |

|-------------------------------------------------------------------|--------|------------------------------------------------------------|-----|-----|------------------------|------|

| Output Pad Transition Times, rise/fall<br>(Max Drive, DSE=111)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 2.72/2.79<br>1.51/1.54 |      |

| Output Pad Transition Times, rise/fall<br>(High Drive, DSE=101)   | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 3.20/3.36<br>1.96/2.07 | ns   |

| Output Pad Transition Times, rise/fall<br>(Medium Drive, DSE=100) | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 3.64/3.88<br>2.27/2.53 | 115  |

| Output Pad Transition Times, rise/fall<br>(Low Drive. DSE=011)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 4.32/4.50<br>3.16/3.17 |      |

| Input Transition Times <sup>1</sup>                               | trm    | _                                                          |     | _   | 25                     | ns   |

Table 28. General Purpose I/O AC Parameters 1.8 V Mode

<sup>1</sup> Hysteresis mode is recommended for inputs with transition times greater than 25 ns.

## Table 29. General Purpose I/O AC Parameters 3.3 V Mode

| Parameter                                                         | Symbol | Test Condition                                             | Min | Тур | Мах                    | Unit |

|-------------------------------------------------------------------|--------|------------------------------------------------------------|-----|-----|------------------------|------|

| Output Pad Transition Times, rise/fall<br>(Max Drive, DSE=101)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 1.70/1.79<br>1.06/1.15 |      |

| Output Pad Transition Times, rise/fall<br>(High Drive, DSE=011)   | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 2.35/2.43<br>1.74/1.77 | ns   |

| Output Pad Transition Times, rise/fall<br>(Medium Drive, DSE=010) | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 3.13/3.29<br>2.46/2.60 |      |

| Output Pad Transition Times, rise/fall<br>(Low Drive. DSE=001)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 5.14/5.57<br>4.77/5.15 |      |

| Input Transition Times <sup>1</sup>                               | trm    | _                                                          | —   | —   | 25                     | ns   |

<sup>1</sup> Hysteresis mode is recommended for inputs with transition times greater than 25 ns.

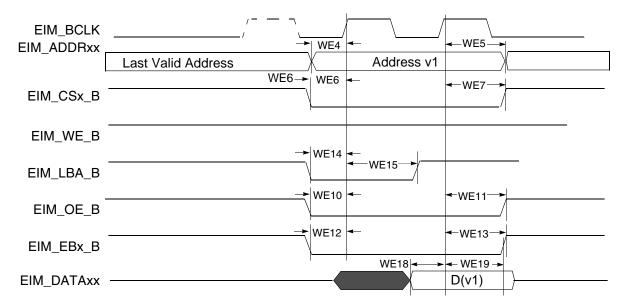

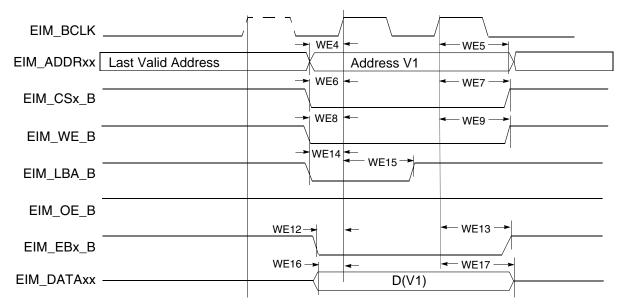

Figure 14 to Figure 17 provide few examples of basic EIM accesses to external memory devices with the timing parameters mentioned previously for specific control parameters settings.

Figure 14. Synchronous Memory Read Access, WSC=1

Figure 15. Synchronous Memory, Write Access, WSC=1, WBEA=0 and WADVN=0

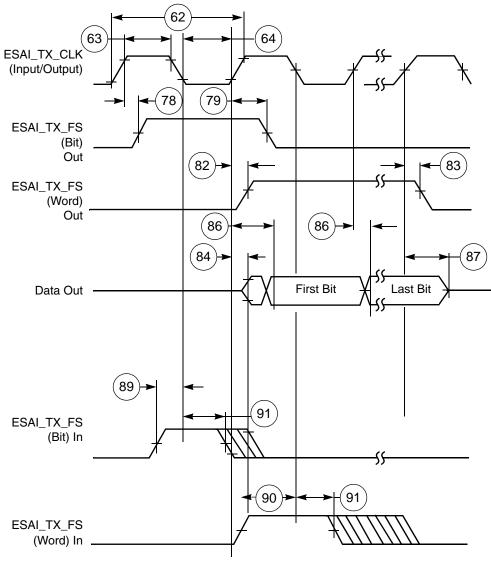

# 4.12.3 Enhanced Serial Audio Interface (ESAI) Timing Parameters

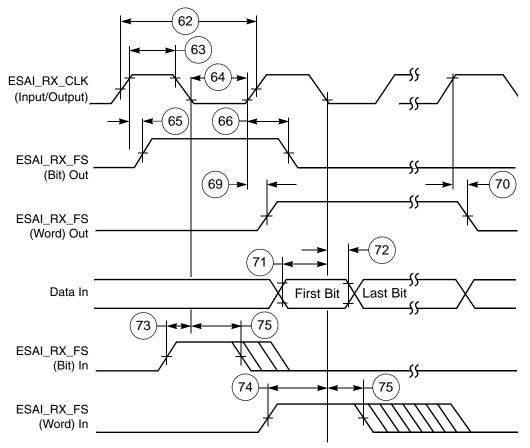

The ESAI consists of independent transmitter and receiver sections, each section with its own clock generator. Table 49 shows the interface timing values. The number field in the table refers to timing signals found in Figure 37 and Figure 38.

| ID | Parameter <sup>1,2</sup>                                                              | Symbol             | Expression <sup>2</sup>                                         | Min          | Max          | Condition <sup>3</sup> | Unit |

|----|---------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------|--------------|--------------|------------------------|------|

| 62 | Clock cycle <sup>4</sup>                                                              | t <sub>SSICC</sub> | $\begin{array}{c} 4 \times T_{C} \\ 4 \times T_{C} \end{array}$ | 30.0<br>30.0 | _            | i ck<br>i ck           | ns   |

| 63 | Clock high period:<br>• For internal clock<br>• For external clock                    | _                  | $2 \times T_{c} - 9.0$ $2 \times T_{c}$                         | 6<br>15      | _            | _                      | ns   |

| 64 | Clock low period:<br>• For internal clock<br>• For external clock                     |                    | $2 \times T_{c} - 9.0$ $2 \times T_{c}$                         | 6<br>15      | _            |                        | ns   |

| 65 | ESAI_RX_CLK rising edge to ESAI_RX_FS out (bl) high                                   | —                  |                                                                 |              | 19.0<br>7.0  | x ck<br>i ck a         | ns   |

| 66 | ESAI_RX_CLK rising edge to ESAI_RX_FS out (bl) low                                    |                    | —                                                               |              | 19.0<br>7.0  | x ck<br>i ck a         | ns   |

| 67 | ESAI_RX_CLK rising edge to ESAI_RX_FS out (wr)<br>high <sup>5</sup>                   |                    |                                                                 |              | 19.0<br>9.0  | x ck<br>i ck a         | ns   |

| 68 | ESAI_RX_CLK rising edge to ESAI_RX_FS out (wr) low <sup>5</sup>                       |                    |                                                                 |              | 19.0<br>9.0  | x ck<br>i ck a         | ns   |

| 69 | ESAI_RX_CLK rising edge to ESAI_RX_FS out (wI) high                                   |                    | —                                                               |              | 19.0<br>6.0  | x ck<br>i ck a         | ns   |

| 70 | ESAI_RX_CLK rising edge to ESAI_RX_FSout (wl) low                                     | —                  | —                                                               |              | 17.0<br>7.0  | x ck<br>i ck a         | ns   |

| 71 | Data in setup time before ESAI_RX_CLK (serial clock in synchronous mode) falling edge |                    | —                                                               | 12.0<br>19.0 | _            | x ck<br>i ck           | ns   |

| 72 | Data in hold time after ESAI_RX_CLK falling edge                                      |                    | —                                                               | 3.5<br>9.0   | _            | x ck<br>i ck           | ns   |

| 73 | ESAI_RX_FS input (bl, wr) high before ESAI_RX_CLK falling edge <sup>5</sup>           | —                  | —                                                               | 2.0<br>19.0  | —            | x ck<br>i ck a         | ns   |

| 74 | ESAI_RX_FS input (wl) high before ESAI_RX_CLK falling edge                            | —                  | —                                                               | 2.0<br>19.0  | —            | x ck<br>i ck a         | ns   |

| 75 | ESAI_RX_FS input hold time after ESAI_RX_CLK falling edge                             |                    | —                                                               | 2.5<br>8.5   | _            | x ck<br>i ck a         | ns   |

| 78 | ESAI_TX_CLK rising edge to ESAI_TX_FS out (bl) high                                   | —                  | —<br>—                                                          | _            | 19.0<br>8.0  | x ck<br>i ck           | ns   |

| 79 | ESAI_TX_CLK rising edge to ESAI_TX_FS out (bl) low                                    | —                  | —<br>—                                                          |              | 20.0<br>10.0 | x ck<br>i ck           | ns   |

| 80 | ESAI_TX_CLK rising edge to ESAI_TX_FS out (wr) high <sup>5</sup>                      | —                  | —<br>—                                                          |              | 20.0<br>10.0 | x ck<br>i ck           | ns   |

### Table 49. Enhanced Serial Audio Interface (ESAI) Timing

Figure 37. ESAI Transmitter Timing

Figure 38. ESAI Receiver Timing

| Table 55. MII Asynchronous | Inputs | Signal 7 | Гiming |

|----------------------------|--------|----------|--------|

|----------------------------|--------|----------|--------|

| ID              | Characteristic                           | Min | Max | Unit               |

|-----------------|------------------------------------------|-----|-----|--------------------|

| M9 <sup>1</sup> | ENET_CRS to ENET_COL minimum pulse width | 1.5 |     | ENET_TX_CLK period |

<sup>1</sup> ENET\_COL has the same timing in 10-Mbit 7-wire interface mode.

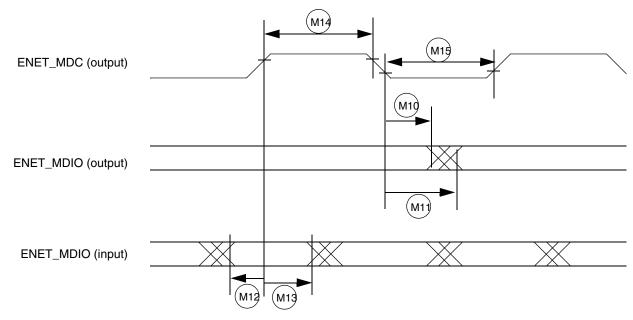

## 4.12.5.1.4 MII Serial Management Channel Timing (ENET\_MDIO and ENET\_MDC)

The MDC frequency is designed to be equal to or less than 2.5 MHz to be compatible with the IEEE 802.3 MII specification. However the ENET can function correctly with a maximum MDC frequency of 15 MHz.

Figure 45 shows MII asynchronous input timings. Table 56 describes the timing parameters (M10–M15) shown in the figure.

Figure 45. MII Serial Management Channel Timing Diagram

| Table 56. MII Serial Management Cha | nnel Timing |

|-------------------------------------|-------------|

|-------------------------------------|-------------|

| ID  | Characteristic                                                                | Min | Max | Unit            |

|-----|-------------------------------------------------------------------------------|-----|-----|-----------------|

| M10 | ENET_MDC falling edge to ENET_MDIO output invalid (minimum propagation delay) | 0   | —   | ns              |

| M11 | ENET_MDC falling edge to ENET_MDIO output valid (maximum propagation delay)   | _   | 5   | ns              |

| M12 | ENET_MDIO (input) to ENET_MDC rising edge setup                               | 18  | —   | ns              |

| M13 | ENET_MDIO (input) to ENET_MDC rising edge hold                                | 0   | —   | ns              |

| M14 | ENET_MDC pulse width high                                                     | 40% | 60% | ENET_MDC period |

| M15 | ENET_MDC pulse width low                                                      | 40% | 60% | ENET_MDC period |

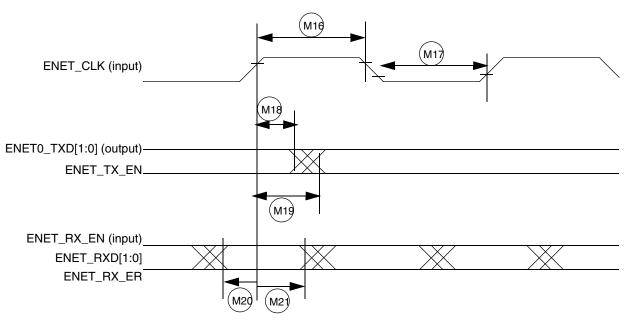

# 4.12.5.2 RMII Mode Timing

In RMII mode, ENET\_CLK is used as the REF\_CLK, which is a 50 MHz  $\pm$  50 ppm continuous reference clock. ENET\_RX\_EN is used as the ENET\_RX\_EN in RMII. Other signals under RMII mode include ENET\_TX\_EN, ENET0\_TXD[1:0], ENET\_RXD[1:0] and ENET\_RX\_ER.

Figure 46 shows RMII mode timings. Table 57 describes the timing parameters (M16–M21) shown in the figure.

Figure 46. RMII Mode Signal Timing Diagram

| Table | 67  |        | Cianal | Timina |

|-------|-----|--------|--------|--------|

| lable | 57. | RIVIII | Signai | Timing |

| ID  | Characteristic                                                      | Min | Max  | Unit            |

|-----|---------------------------------------------------------------------|-----|------|-----------------|

| M16 | ENET_CLK pulse width high                                           | 35% | 65%  | ENET_CLK period |

| M17 | ENET_CLK pulse width low                                            | 35% | 65%  | ENET_CLK period |

| M18 | ENET_CLK to ENET0_TXD[1:0], ENET_TX_EN invalid                      | 4   | —    | ns              |

| M19 | ENET_CLK to ENET0_TXD[1:0], ENET_TX_EN valid                        | —   | 13.5 | ns              |

| M20 | ENET_RXD[1:0], ENET_RX_EN(ENET_RX_EN), ENET_RX_ER to ENET_CLK setup | 4   | _    | ns              |

| M21 | ENET_CLK to ENET_RXD[1:0], ENET_RX_EN, ENET_RX_ER hold              | 2   | —    | ns              |

Power-up time for the HDMI 3D Tx PHY while operating with the fastest input reference clock supported (340 MHz) is 133  $\mu$ s.

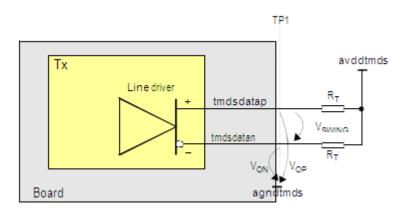

## 4.12.7.2 Electrical Characteristics

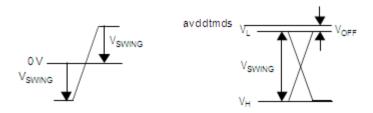

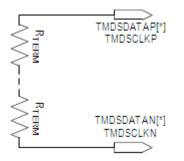

The table below provides electrical characteristics for the HDMI 3D Tx PHY. The following three figures illustrate various definitions and measurement conditions specified in the table below.

Figure 50. Driver Measuring Conditions

Figure 51. Driver Definitions

Figure 52. Source Termination

**Table 59. Electrical Characteristics**

| Symbol                        | Parameter                             | Condition | Min | Тур | Max  | Unit |

|-------------------------------|---------------------------------------|-----------|-----|-----|------|------|

| Operating conditions for HDMI |                                       |           |     |     |      |      |

| avddtmds                      | avddtmds Termination supply voltage — |           |     |     | 3.45 | V    |

| Symbol             | Parameter                                                                                                                                                                                                                                                                                                                                                              | Condition                                                                                                                                                                           | Min                  | Тур   | Max                  | Unit |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|----------------------|------|

| R <sub>T</sub>     | Termination resistance                                                                                                                                                                                                                                                                                                                                                 | —                                                                                                                                                                                   | 45                   | 50    | 55                   | Ω    |

|                    | T                                                                                                                                                                                                                                                                                                                                                                      | MDS drivers DC specifications                                                                                                                                                       |                      |       |                      |      |

| V <sub>OFF</sub>   | Single-ended standby voltage                                                                                                                                                                                                                                                                                                                                           | RT = 50 Ω                                                                                                                                                                           | avddt                | mds ± | 10 mV                | mV   |

| V <sub>SWING</sub> | Single-ended output swing voltage                                                                                                                                                                                                                                                                                                                                      | For measurement conditions and<br>definitions, see the first two figures<br>above.<br>Compliance point TP1 as defined in<br>the HDMI specification, version 1.3a,<br>section 4.2.4. | 400                  | _     | 600                  | mV   |

| V <sub>H</sub>     | Single-ended output high voltage<br>For definition, see the second                                                                                                                                                                                                                                                                                                     | If attached sink supports TMDSCLK < or = 165 MHz                                                                                                                                    | avddti               | mds ± | 10 mV                | mV   |

| figure above.      | figure above.                                                                                                                                                                                                                                                                                                                                                          | If attached sink supports TMDSCLK > 165 MHz                                                                                                                                         | avddtmds<br>– 200 mV | —     | avddtmds<br>+ 10 mV  | mV   |

| VL                 | V <sub>L</sub> Single-ended output low voltage<br>For definition, see the second<br>figure above.                                                                                                                                                                                                                                                                      | If attached sink supports TMDSCLK < or = 165 MHz                                                                                                                                    | avddtmds<br>– 600 mV | —     | avddtmds<br>- 400mV  | mV   |

|                    |                                                                                                                                                                                                                                                                                                                                                                        | If attached sink supports TMDSCLK > 165 MHz                                                                                                                                         | avddtmds<br>– 700 mV | —     | avddtmds<br>- 400 mV | mV   |

| R <sub>TERM</sub>  | Differential source termination load<br>(inside HDMI 3D Tx PHY)<br>Although the HDMI 3D Tx PHY<br>includes differential source<br>termination, the user-defined value<br>is set for each single line (for<br>illustration, see the third figure<br>above).<br><b>Note:</b> R <sub>TERM</sub> can also be<br>configured to be open and not<br>present on TMDS channels. |                                                                                                                                                                                     | 50                   |       | 200                  | Ω    |

|                    |                                                                                                                                                                                                                                                                                                                                                                        | Hot plug detect specifications                                                                                                                                                      |                      |       |                      |      |

| HPD <sup>VH</sup>  | Hot plug detect high range                                                                                                                                                                                                                                                                                                                                             | _                                                                                                                                                                                   | 2.0                  |       | 5.3                  | V    |

|                    | Hot plug detect low range                                                                                                                                                                                                                                                                                                                                              | _                                                                                                                                                                                   | 0                    | —     | 0.8                  | V    |

| HPD                | Hot plug detect input impedance                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                     | 10                   | _     |                      | kΩ   |

| HPD<br>t           | Hot plug detect time delay                                                                                                                                                                                                                                                                                                                                             | —                                                                                                                                                                                   | _                    | —     | 100                  | μs   |

### Table 59. Electrical Characteristics (continued)

# 4.12.8 Switching Characteristics

Table 60 describes switching characteristics for the HDMI 3D Tx PHY. Figure 53 to Figure 57 illustrate various parameters specified in table.

### NOTE

All dynamic parameters related to the TMDS line drivers' performance imply the use of assembly guidelines.

### Table 65 shows timing characteristics of signals presented in Figure 63 and Figure 64.

| ID   | Parameter                      | Symbol | Value                                 | Description                                                                                                                                                                                                                                                                                                               | Unit |

|------|--------------------------------|--------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| IP5  | Display interface clock period | Tdicp  | (see <sup>1</sup> )                   | Display interface clock IPP_DISP_CLK                                                                                                                                                                                                                                                                                      | ns   |

| IP6  | Display pixel clock period     | Tdpcp  | DISP_CLK_PER_PIXEL<br>X Tdicp         | Time of translation of one pixel to display,<br>DISP_CLK_PER_PIXEL—number of pixel<br>components in one pixel (1. <i>n</i> ).<br>The DISP_CLK_PER_PIXEL is virtual<br>parameter to define display pixel clock<br>period.<br>The DISP_CLK_PER_PIXEL is received by<br>DC/DI one access division to <i>n</i><br>components. | ns   |

| IP7  | Screen width time              | Tsw    | (SCREEN_WIDTH)<br>× Tdicp             | SCREEN_WIDTH—screen width in,<br>interface clocks. horizontal blanking<br>included.<br>The SCREEN_WIDTH should be built by<br>suitable DI's counter <sup>2</sup> .                                                                                                                                                        | ns   |

| IP8  | HSYNC width time               | Thsw   | (HSYNC_WIDTH)                         | HSYNC_WIDTH—Hsync width in DI_CLK<br>with 0.5 DI_CLK resolution. Defined by DI's<br>counter.                                                                                                                                                                                                                              | ns   |

| IP9  | Horizontal blank interval 1    | Thbi1  | BGXP × Tdicp                          | BGXP—width of a horizontal blanking<br>before a first active data in a line (in<br>interface clocks). The BGXP should be built<br>by suitable DI's counter.                                                                                                                                                               | ns   |

| IP10 | Horizontal blank interval 2    | Thbi2  | (SCREEN_WIDTH –<br>BGXP – FW) × Tdicp | Width a horizontal blanking after a last<br>active data in a line (in interface clocks)<br>FW—with of active line in interface clocks.<br>The FW should be built by suitable DI's<br>counter.                                                                                                                             | ns   |

| IP12 | Screen height                  | Tsh    | (SCREEN_HEIGHT)<br>× Tsw              | SCREEN_HEIGHT— screen height in lines<br>with blanking.<br>The SCREEN_HEIGHT is a distance<br>between 2 VSYNCs.<br>The SCREEN_HEIGHT should be built by<br>suitable DI's counter.                                                                                                                                         | ns   |

| IP13 | VSYNC width                    | Tvsw   | VSYNC_WIDTH                           | VSYNC_WIDTH—Vsync width in DI_CLK with 0.5 DI_CLK resolution. Defined by DI's counter.                                                                                                                                                                                                                                    | ns   |

| IP14 | Vertical blank interval 1      | Tvbi1  | BGYP × Tsw                            | BGYP—width of first Vertical<br>blanking interval in line. The BGYP should<br>be built by suitable DI's counter.                                                                                                                                                                                                          | ns   |

| IP15 | Vertical blank interval 2      | Tvbi2  | (SCREEN_HEIGHT –<br>BGYP – FH) X Tsw  | Width of second vertical blanking interval in line. The FH should be built by suitable DI's counter.                                                                                                                                                                                                                      | ns   |

### Table 65. Synchronous Display Interface Timing Characteristics (Pixel Level)

# 4.12.15.1 PCIE\_REXT Reference Resistor Connection

The impedance calibration process requires connection of reference resistor 200  $\Omega$ . 1% precision resistor on PCIE\_REXT pads to ground. It is used for termination impedance calibration.

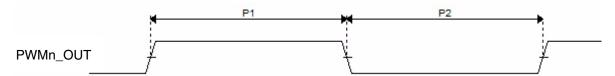

# 4.12.16 Pulse Width Modulator (PWM) Timing Parameters

This section describes the electrical information of the PWM. The PWM can be programmed to select one of three clock signals as its source frequency. The selected clock signal is passed through a prescaler before being input to the counter. The output is available at the pulse-width modulator output (PWMO) external pin.

Figure 83 depicts the timing of the PWM, and Table 76 lists the PWM timing parameters.

Figure 83. PWM Timing

### Table 76. PWM Output Timing Parameters

| ID | Parameter                   | Min | Мах     | Unit |

|----|-----------------------------|-----|---------|------|

| _  | PWM Module Clock Frequency  | 0   | ipg_clk | MHz  |

| P1 | PWM output pulse width high | 15  | —       | ns   |

| P2 | PWM output pulse width low  | 15  | —       | ns   |

# 4.12.17 SATA PHY Parameters

This section describes SATA PHY electrical specifications.

## 4.12.17.1 Transmitter and Receiver Characteristics

The SATA PHY meets or exceeds the electrical compliance requirements defined in the SATA specifications.

### NOTE

The tables in the following sections indicate any exceptions to the SATA specification or aspects of the SATA PHY that exceed the standard, as well as provide information about parameters not defined in the standard.

The following subsections provide values obtained from a combination of simulations and silicon characterization.

| ID   | Parameter                                      | Min  | Мах  | Unit |

|------|------------------------------------------------|------|------|------|

|      | External Clock Operation                       | on   |      |      |

| SS22 | AUDx_TXC/AUDx_RXC clock period                 | 81.4 | _    | ns   |

| SS23 | AUDx_TXC/AUDx_RXC clock high period            | 36   | —    | ns   |

| SS24 | AUDx_TXC/AUDx_RXC clock rise time              | _    | 6.0  | ns   |

| SS25 | AUDx_TXC/AUDx_RXC clock low period             | 36   | —    | ns   |

| SS26 | AUDx_TXC/AUDx_RXC clock fall time              |      | 6.0  | ns   |

| SS28 | AUDx_RXC high to AUDx_TXFS (bl) high           | -10  | 15.0 | ns   |

| SS30 | AUDx_RXC high to AUDx_TXFS (bl) low            | 10   | —    | ns   |

| SS32 | AUDx_RXC high to AUDx_TXFS (wl) high           | -10  | 15.0 | ns   |

| SS34 | AUDx_RXC high to AUDx_TXFS (wl) low            | 10   | _    | ns   |

| SS35 | AUDx_TXC/AUDx_RXC External AUDx_TXFS rise time | _    | 6.0  | ns   |

| SS36 | AUDx_TXC/AUDx_RXC External AUDx_TXFS fall time | _    | 6.0  | ns   |

| SS40 | AUDx_RXD setup time before AUDx_RXC low        | 10   | —    | ns   |

| SS41 | AUDx_RXD hold time after AUDx_RXC low          | 2    | —    | ns   |

### Table 85. SSI Receiver Timing with External Clock

### NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal AUDx\_TXC/AUDx\_RXC and/or the frame sync AUDx\_TXFS/AUDx\_RXFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- AUDx\_TXC and AUDx\_RXC refer to the Transmit and Receive sections of the SSI.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the frame sync timing is same as that of transmit data (for example, during AC97 mode of operation).

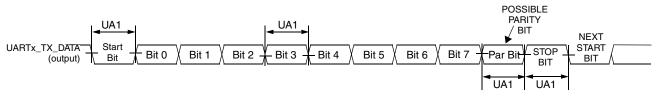

# 4.12.21.2 UART RS-232 Serial Mode Timing

The following sections describe the electrical information of the UART module in the RS-232 mode.

### 4.12.21.2.1 UART Transmitter

Figure 94 depicts the transmit timing of UART in the RS-232 serial mode, with 8 data bit/1 stop bit format. Table 87 lists the UART RS-232 serial mode transmit timing characteristics.

Figure 94. UART RS-232 Serial Mode Transmit Timing Diagram

### Table 87. RS-232 Serial Mode Transmit Timing Parameters

| ID  | Parameter         | Symbol            | Min                                 | Мах                                             | Unit |

|-----|-------------------|-------------------|-------------------------------------|-------------------------------------------------|------|

| UA1 | Transmit Bit Time | t <sub>Tbit</sub> | $1/F_{baud_rate}^1 - T_{ref_clk}^2$ | 1/F <sub>baud_rate</sub> + T <sub>ref_clk</sub> | _    |

<sup>1</sup> F<sub>baud rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

<sup>2</sup> T<sub>ref\_clk</sub>: The period of UART reference clock *ref\_clk* (*ipg\_perclk* after RFDIV divider).

### 4.12.21.2.2 UART Receiver

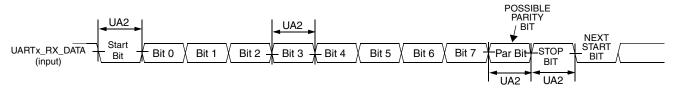

Figure 95 depicts the RS-232 serial mode receive timing with 8 data bit/1 stop bit format. Table 88 lists serial mode receive timing characteristics.

Figure 95. UART RS-232 Serial Mode Receive Timing Diagram

Table 88. RS-232 Serial Mode Receive Timing Parameters

| ID  | Parameter                     | Symbol            | Min                                                                         | Мах                                                            | Unit |

|-----|-------------------------------|-------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------|------|

| UA2 | Receive Bit Time <sup>1</sup> | t <sub>Rbit</sub> | 1/F <sub>baud_rate</sub> <sup>2</sup> −<br>1/(16 × F <sub>baud_rate</sub> ) | 1/F <sub>baud_rate</sub> +<br>1/(16 × F <sub>baud_rate</sub> ) | —    |

The UART receiver can tolerate  $1/(16 \times F_{baud\_rate})$  tolerance in each bit. But accumulation tolerance in one frame must not exceed  $3/(16 \times F_{baud\_rate})$ .

<sup>2</sup> F<sub>baud rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

**Package Information and Contact Assignments**

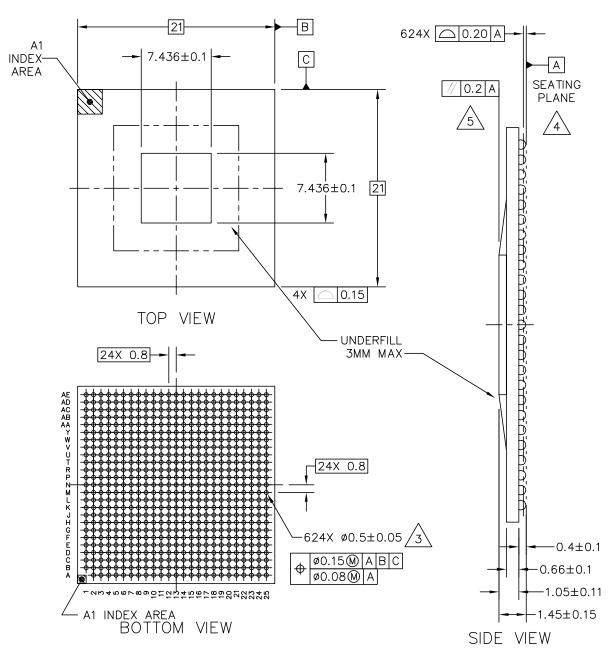

## 6.2.1.2 21 x 21 mm Non-Lidded (Bare Die) Package

Figure 103 and Figure 103 show the top, bottom, and side views of the  $21 \times 21$  mm bare die package.

| NXP SEMICONDUCTORS N.V.<br>ALL RIGHTS RESERVED | MECHANICAL OUTLINE     |         | PRINT VERSION NOT TO SCALE |             |  |

|------------------------------------------------|------------------------|---------|----------------------------|-------------|--|

| TITLE: 624 I/O FC PBGA,                        |                        |         | NT NO: 98ASA00329D         | REV: B      |  |

| 21 X 21 PKG, 0.8 MM                            | STANDARD: JEDEC MS-034 |         |                            |             |  |

| NO LID                                         |                        | SOT1642 | -1                         | 07 JAN 2016 |  |

Figure 102. 21 x 21 mm Bare Die Package Top, Bottom, and Side Views (Sheet 1 of 2)

#### Package Information and Contact Assignments

| Supply Rail Name | Ball(s) Position(s)                              | Remark                                                                                                                              |  |  |

|------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|

| VDDHIGH_CAP      | H10, J10                                         | Secondary supply for the 2.5 V domain<br>(internal regulator output—requires<br>capacitor if internal regulator is used)            |  |  |

| VDDHIGH_IN       | H9, J9                                           | Primary supply for the 2.5 V regulator                                                                                              |  |  |

| VDDPU_CAP        | H17, J17, K17, L17, M17, N17, P17                | Secondary supply for the VPU and<br>GPU (internal regulator output—<br>requires capacitor if internal regulator<br>is used)         |  |  |

| VDDSOC_CAP       | R10, T10, T13, T14, U10, U13, U14                | Secondary supply for the SoC and PU<br>(internal regulator output—requires<br>capacitor if internal regulator is used)              |  |  |

| VDDSOC_IN        | H16, J16, K16, L16, M16, N16, P16, R16, T16, U16 | Primary supply for the SoC and PU regulators                                                                                        |  |  |

| VDDUSB_CAP       | F9                                               | Secondary supply for the 3 V domain<br>(internal regulator output—requires<br>capacitor if internal regulator is used)              |  |  |

| ZQPAD            | AE17                                             | Connect ZQPAD to an external $240\Omega$ 1% resistor to GND. This is a reference used during DRAM output buffer driver calibration. |  |  |

### Table 95. 21 x 21 mm Supplies Contact Assignment (continued)

## 6.2.3 21 x 21 mm Functional Contact Assignments

Table 96 displays an alpha-sorted list of the signal assignments including power rails. The table also includes out of reset pad state.

|            |      |              |           | Out of Reset Condition <sup>1</sup> |                                   |              |                    |

|------------|------|--------------|-----------|-------------------------------------|-----------------------------------|--------------|--------------------|

| Ball Name  | Ball | Power Group  | Ball Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function<br>(Signal Name) | Input/Output | Value <sup>2</sup> |

| BOOT_MODE0 | C12  | VDD_SNVS_IN  | GPIO      | ALT0                                | SRC_BOOT_MODE0                    | Input        | PD (100K)          |

| BOOT_MODE1 | F12  | VDD_SNVS_IN  | GPIO      | ALT0                                | SRC_BOOT_MODE1                    | Input        | PD (100K)          |

| CLK1_N     | C7   | VDD_HIGH_CAP | —         | —                                   | CLK1_N                            | —            | —                  |

| CLK1_P     | D7   | VDD_HIGH_CAP | —         | —                                   | CLK1_P                            | —            | —                  |

| CLK2_N     | C5   | VDD_HIGH_CAP | —         | —                                   | CLK2_N                            | —            | —                  |

| CLK2_P     | D5   | VDD_HIGH_CAP | —         | —                                   | CLK2_P                            | —            | —                  |

| CSI_CLK0M  | F4   | NVCC_MIPI    | —         | —                                   | CSI_CLK_N                         | —            | —                  |

| CSI_CLK0P  | F3   | NVCC_MIPI    | —         | —                                   | CSI_CLK_P                         | —            | —                  |

| CSI_D0M    | E4   | NVCC_MIPI    | —         | —                                   | CSI_DATA0_N                       | —            | —                  |

| CSI_D0P    | E3   | NVCC_MIPI    | —         | —                                   | CSI_DATA0_P                       | —            | —                  |

| CSI_D1M    | D1   | NVCC_MIPI    | _         |                                     | CSI_DATA1_N                       | _            | —                  |

Table 96. 21 x 21 mm Functional Contact Assignments