Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | AVR                                                                       |

| Core Size                  | 8/16-Bit                                                                  |

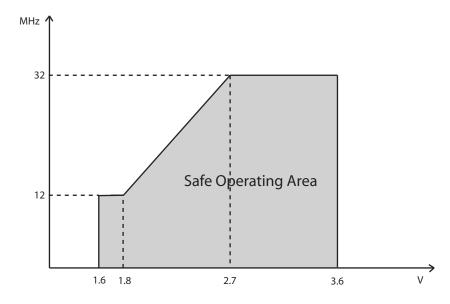

| Speed                      | 32MHz                                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 78                                                                        |

| Program Memory Size        | 64KB (32K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 4K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 4x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 100-TQFP                                                                  |

| Supplier Device Package    | 100-TQFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega64a1-aur |

#### 8.3.4 Production Signature Row

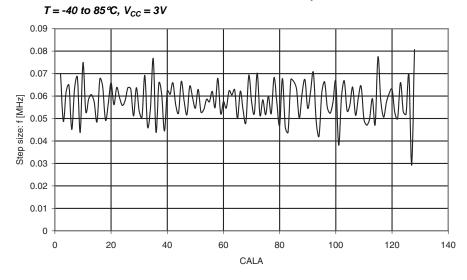

The production signature row is a separate memory section for factory programmed data. It contains calibration data for functions such as oscillators and analog modules. Some of the calibration values will be automatically loaded to the corresponding module or peripheral unit during reset. Other values must be loaded from the signature row and written to the corresponding peripheral registers from software. For details on calibration conditions, refer to "Electrical Characteristics" on page 76.

The production signature row also contains an ID that identifies each microcontroller device type and a serial number for each manufactured device. The serial number consists of the production lot number, wafer number, and wafer coordinates for the device. The device ID for the available devices is shown in Table 8-1.

The production signature row cannot be written or erased, but it can be read from application software and external programmers.

Table 8-1. Device ID bytes.

| Device       | Device ID bytes |        |        |  |  |  |  |

|--------------|-----------------|--------|--------|--|--|--|--|

|              | Byte 2          | Byte 1 | Byte 0 |  |  |  |  |

| ATxmega64A1  | 4E              | 96     | 1E     |  |  |  |  |

| ATxmega128A1 | 4C              | 97     | 1E     |  |  |  |  |

#### 8.3.5 User Signature Row

The user signature row is a separate memory section that is fully accessible (read and write) from application software and external programmers. It is one flash page in size, and is meant for static user parameter storage, such as calibration data, custom serial number, identification numbers, random number seeds, etc. This section is not erased by chip erase commands that erase the flash, and requires a dedicated erase command. This ensures parameter storage during multiple program/erase operations and on-chip debug sessions.

## 8.4 Fuses and Lock bits

The fuses are used to configure important system functions, and can only be written from an external programmer. The application software can read the fuses. The fuses are used to configure reset sources such as brownout detector and watchdog, startup configuration, JTAG enable, and JTAG user ID.

The lock bits are used to set protection levels for the different flash sections (that is, if read and/or write access should be blocked). Lock bits can be written by external programmers and application software, but only to stricter protection levels. Chip erase is the only way to erase the lock bits. To ensure that flash contents are protected even during chip erase, the lock bits are erased after the rest of the flash memory has been erased.

An unprogrammed fuse or lock bit will have the value one, while a programmed fuse or lock bit will have the value zero. Both fuses and lock bits are reprogrammable like the flash program memory.

## 8.5 Data Memory

The data memory contains the I/O memory, internal SRAM, optionally memory mapped EEPROM, and external memory if available. The data memory is organized as one continuous memory section, see Figure 8-2 on page 15. To simplify development, I/O Memory, EEPROM and SRAM will always have the same start addresses for all Atmel AVR XMEGA devices. The address space for External Memory will always start at the end of Internal SRAM and end at address 0xFFFFFF.

Table 8-3. Number of Bytes and Pages in the EEPROM.

| Device       | EEPROM | Page Size | E2BYTE    | E2PAGE     | No of pages |

|--------------|--------|-----------|-----------|------------|-------------|

|              | Size   | bytes     |           |            |             |

| ATxmega64A1  | 2 KB   | 32        | ADDR[4:0] | ADDR[10:5] | 64          |

| ATxmega128A1 | 2 KB   | 32        | ADDR[4:0  | ADDR[10:5] | 64          |

## 8.14.1 I/O Memory

All peripherals and modules are addressable through I/O memory locations in the data memory space. All I/O memory locations can be accessed by the Load (LD/LDS/LDD) and Store (ST/STS/STD) instructions, transferring data between the 32 general purpose registers in the CPU and the I/O Memory.

The IN and OUT instructions can address I/O memory locations in the range 0x00 - 0x3F directly.

I/O registers within the address range 0x00 - 0x1F are directly bit-accessible using the SBI and CBI instructions. The value of single bits can be checked by using the SBIS and SBIC instructions on these registers.

The I/O memory address for all peripherals and modules in XMEGA A1 is shown in the "Peripheral Module Address Map" on page 62.

# 14. Interrupts and Programmable Multilevel Interrupt Controller

## 14.1 Features

- Short and predictable interrupt response time

- Separate interrupt configuration and vector address for each interrupt

- Programmable multilevel interrupt controller

- Interrupt prioritizing according to level and vector address

- Three selectable interrupt levels for all interrupts: low, medium and high

- Selectable, round-robin priority scheme within low-level interrupts

- Non-maskable interrupts for critical functions

- Interrupt vectors optionally placed in the application section or the boot loader section

## 14.2 Overview

Interrupts signal a change of state in peripherals, and this can be used to alter program execution. Peripherals can have one or more interrupts, and all are individually enabled and configured. When an interrupt is enabled and configured, it will generate an interrupt request when the interrupt condition is present. The programmable multilevel interrupt controller (PMIC) controls the handling and prioritizing of interrupt requests. When an interrupt request is acknowledged by the PMIC, the program counter is set to point to the interrupt vector, and the interrupt handler can be executed.

All peripherals can select between three different priority levels for their interrupts: low, medium, and high. Interrupts are prioritized according to their level and their interrupt vector address. Medium-level interrupts will interrupt low-level interrupt handlers. High-level interrupts will interrupt both medium- and low-level interrupt handlers. Within each level, the interrupt priority is decided from the interrupt vector address, where the lowest interrupt vector address has the highest interrupt priority. Low-level interrupts have an optional round-robin scheduling scheme to ensure that all interrupts are serviced within a certain amount of time.

Non-maskable interrupts (NMI) are also supported, and can be used for system critical functions.

## 14.3 Interrupt vectors

The interrupt vector is the sum of the peripheral's base interrupt address and the offset address for specific interrupts in each peripheral. The base addresses for the Atmel AVR XMEGA A1U devices are shown in Table 14-1. Offset addresses for each interrupt available in the peripheral are described for each peripheral in the XMEGA AU manual. For peripherals or modules that have only one interrupt, the interrupt vector is shown in Table 14-1. The program address is the word address.

Table 14-1. Reset and Interrupt vectors

| Program Address<br>(Base Address) | Source         | Interrupt Description                             |

|-----------------------------------|----------------|---------------------------------------------------|

| 0x000                             | RESET          |                                                   |

| 0x002                             | OSCF_INT_vect  | Crystal Oscillator Failure Interrupt vector (NMI) |

| 0x004                             | PORTC_INT_base | Port C Interrupt base                             |

| 0x008                             | PORTR_INT_base | Port R Interrupt base                             |

| 0x00C                             | DMA_INT_base   | DMA Controller Interrupt base                     |

| 0x014                             | RTC_INT_base   | Real Time Counter Interrupt base                  |

| 0x018                             | TWIC_INT_base  | Two-Wire Interface on Port C Interrupt base       |

| Program Address<br>(Base Address) | Source           | Interrupt Description                    |

|-----------------------------------|------------------|------------------------------------------|

| 0x0D8                             | TCF0_INT_base    | Timer/Counter 0 on port F Interrupt base |

| 0x0E4                             | TCF1_INT_base    | Timer/Counter 1 on port F Interrupt base |

| 0x0EC                             | SPIF_INT_vector  | SPI ion port F Interrupt base            |

| 0x0EE                             | USARTF0_INT_base | USART 0 on port F Interrupt base         |

| 0x0F4                             | USARTF1_INT_base | USART 1 on port F Interrupt base         |

The high-resolution (hi-res) extension can be used to increase the waveform output resolution by four or eight times by using an internal clock source running up to four times faster than the peripheral clock. See "Hi-Res - High Resolution Extension" on page 39 for more details.

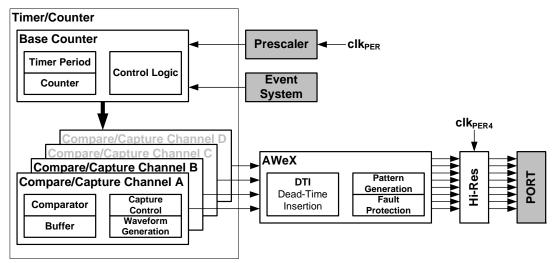

Figure 16-1. Overview of a Timer/Counter and closely related peripherals

PORTC, PORTD, PORTE and PORTF each has one Timer/Counter 0 and one Timer/Counter1. Notation of these Timer/Counters are TCC0 (Time/Counter C0), TCC1, TCD0, TCD1, TCE0, TCE1, TCF0, and TCF1, respectively.

## 22. USART

## 22.1 Features

- Eight identical USART peripherals

- Full-duplex operation

- Asynchronous or synchronous operation

- Synchronous clock rates up to 1/2 of the device clock frequency

- Asynchronous clock rates up to 1/8 of the device clock frequency

- Supports serial frames with 5, 6, 7, 8, or 9 data bits and 1 or 2 stop bits

- Fractional baud rate generator

- Can generate desired baud rate from any system clock frequency

- No need for external oscillator with certain frequencies

- Built-in error detection and correction schemes

- Odd or even parity generation and parity check

- Data overrun and framing error detection

- · Noise filtering includes false start bit detection and digital low-pass filter

- Separate interrupts for

- Transmit complete

- Transmit data register empty

- Receive complete

- Multiprocessor communication mode

- Addressing scheme to address a specific devices on a multidevice bus

- Enable unaddressed devices to automatically ignore all frames

- Master SPI mode

- Double buffered operation

- Operation up to 1/2 of the peripheral clock frequency

- IRCOM module for IrDA compliant pulse modulation/demodulation

#### 22.2 Overview

The universal synchronous and asynchronous serial receiver and transmitter (USART) is a fast and flexible serial communication module. The USART supports full-duplex communication and asynchronous and synchronous operation. The USART can be configured to operate in SPI master mode and used for SPI communication.

Communication is frame based, and the frame format can be customized to support a wide range of standards. The USART is buffered in both directions, enabling continued data transmission without any delay between frames. Separate interrupts for receive and transmit complete enable fully interrupt driven communication. Frame error and buffer overflow are detected in hardware and indicated with separate status flags. Even or odd parity generation and parity check can also be enabled.

The clock generator includes a fractional baud rate generator that is able to generate a wide range of USART baud rates from any system clock frequencies. This removes the need to use an external crystal oscillator with a specific frequency to achieve a required baud rate. It also supports external clock input in synchronous slave operation.

When the USART is set in master SPI mode, all USART-specific logic is disabled, leaving the transmit and receive buffers, shift registers, and baud rate generator enabled. Pin control and interrupt generation are identical in both modes. The registers are used in both modes, but their functionality differs for some control settings.

An IRCOM module can be enabled for one USART to support IrDA 1.4 physical compliant pulse modulation and demodulation for baud rates up to 115.2Kbps.

PORTC, PORTD, PORTE, and PORTF each has two USARTs. Notation of these peripherals are USARTC0, USARTC1, USARTD0, USARTD1, USARTE0, USARTE1, USARTF0 and USARTF1.

# 23. IRCOM - IR Communication Module

## 23.1 Features

- Pulse modulation/demodulation for infrared communication

- IrDA compatible for baud rates up to 115.2Kbps

- Selectable pulse modulation scheme

- 3/16 of the baud rate period

- Fixed pulse period, 8-bit programmable

- Pulse modulation disabled

- Built-in filtering

- Can be connected to and used by any USART

## 23.2 Overview

Atmel AVR XMEGA devices contain an infrared communication module (IRCOM) that is IrDA compatible for baud rates up to 115.2Kbps. It can be connected to any USART to enable infrared pulse encoding/decoding for that USART.

## 25. EBI – External Bus Interface

## 25.1 Features

- Supports SRAM up to:

- 512KB using 3-port EBI configuration

- 16MB using 3-port EBI configuration

- Supports SDRAM up to:

- 128Mb using 3-port EBI configuration

- Four software configurable chip selects

- Software configurable wait state insertion

- Can run from the 2x peripheral clock frequency for fast access

#### 25.2 Overview

The External Bus Interface (EBI) is used to connect external peripherals and memory for access through the data memory space. When the EBI is enabled, data address space outside the internal SRAM becomes available using dedicated EBI pins.

The EBI can interface external SRAM, SDRAM, and peripherals, such as LCD displays and other memory mapped devices.

The address space for the external memory is selectable from 256 bytes (8-bit) up to 16MB (24-bit). Various multiplexing modes for address and data lines can be selected for optimal use of pins when more or fewer pins are available for the EBI. The complete memory will be mapped into one linear data address space continuing from the end of the internal SRAM.

The EBI has four chip selects, each with separate configuration. Each can be configured for SRAM, SRAM low pin count (LPC), or SDRAM.

The EBI is clocked from the fast, 2x peripheral clock, running up to two times faster than the CPU.

Four-bit and eight-bit SDRAM are supported, and SDRAM configurations, such as CAS latency and refresh rate, are configurable in software.

# 27. DAC - 12-bit Digital to Analog Converter

## 27.1 Features

- 12-bit resolution

- Two independent, continuous-drive output channels

- Up to one million samples per second conversion rate

- Built-in calibration that removes:

- Offset error

- Gain error

- Multiple conversion trigger sources

- On new available data

- Events from the event system

- · High drive capabilities and support for

- Resistive loads

- Capacitive loads

- Combined resistive and capacitive loads

- Internal and external reference options

- DAC output available as input to analog comparator and ADC

- Low-power mode, with reduced drive strength

- Optional DMA transfer of data

#### 27.2 Overview

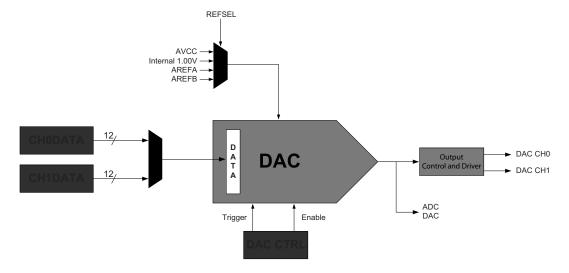

The XMEGA A1 devices features two 12-bit, 1 Msps DACs with built-in offset and gain calibration, see Figure 27-1 on page 50.

A DAC converts a digital value into an analog signal. The DAC may use an internal 1.0 voltage as the upper limit for conversion, but it is also possible to use the supply voltage or any applied voltage in-between. The external reference input is shared with the ADC reference input.

Figure 27-1. DAC overview

## 30.2 Alternate Pin Functions

The tables below show the primary/default function for each pin on a port in the first column, the pin number in the second column, and then all alternate pin functions in the remaining columns. The head row shows what peripheral that enable and use the alternate pin functions.

Table 30-1. Port A - Alternate functions.

| PORT A | PIN# | INTERRUPT  | ADCA<br>POS | ADCA<br>NEG | ADCA<br>GAINPOS | ADCA<br>GAINNEG | ACA<br>POS | ACA<br>NEG | ACA<br>OUT | DACA | REFA |

|--------|------|------------|-------------|-------------|-----------------|-----------------|------------|------------|------------|------|------|

| GND    | 93   |            |             |             |                 |                 |            |            |            |      |      |

| AVCC   | 94   |            |             |             |                 |                 |            |            |            |      |      |

| PA0    | 95   | SYNC       | ADC0        | ADC0        | ADC0            |                 | AC0        | AC0        |            |      | AREF |

| PA1    | 96   | SYNC       | ADC1        | ADC1        | ADC1            |                 | AC1        | AC1        |            |      |      |

| PA2    | 97   | SYNC/ASYNC | ADC2        | ADC2        | ADC2            |                 | AC2        |            |            | DAC0 |      |

| PA3    | 98   | SYNC       | ADC3        | ADC3        | ADC3            |                 | AC3        | AC3        |            | DAC1 |      |

| PA4    | 99   | SYNC       | ADC4        |             | ADC4            | ADC4            | AC4        |            |            |      |      |

| PA5    | 100  | SYNC       | ADC5        |             | ADC5            | ADC5            | AC5        | AC5        |            |      |      |

| PA6    | 1    | SYNC       | ADC6        |             | ADC6            | ADC6            | AC6        |            |            |      |      |

| PA7    | 2    | SYNC       | ADC7        |             | ADC7            | ADC7            |            | AC7        | AC0OUT     |      |      |

Table 30-2. Port B - Alternate functions.

| PORT B | PIN# | INTERRUPT  | ADCB<br>POS | ADCB<br>NEG | ADCB<br>GAINPOS | ADCB<br>GAINNEG | ACB<br>POS | ACB<br>NEG | ACB<br>OUT | DACB | REFB | JTAG |

|--------|------|------------|-------------|-------------|-----------------|-----------------|------------|------------|------------|------|------|------|

| GND    | 3    |            |             |             |                 |                 |            |            |            |      |      |      |

| AVCC   | 4    |            |             |             |                 |                 |            |            |            |      |      |      |

| РВ0    | 5    | SYNC       | ADC0        | ADC0        | ADC0            |                 | AC0        | AC0        |            |      | AREF |      |

| PB1    | 6    | SYNC       | ADC1        | ADC1        | ADC1            |                 | AC1        | AC1        |            |      |      |      |

| PB2    | 7    | SYNC/ASYNC | ADC2        | ADC2        | ADC2            |                 | AC2        |            |            | DAC0 |      |      |

| РВ3    | 8    | SYNC       | ADC3        | ADC3        | ADC3            |                 | AC3        | AC3        |            | DAC1 |      |      |

| PB4    | 9    | SYNC       | ADC4        |             | ADC4            | ADC4            | AC4        |            |            |      |      | TMS  |

| PB5    | 10   | SYNC       | ADC5        |             | ADC5            | ADC5            | AC5        | AC5        |            |      |      | TDI  |

| РВ6    | 11   | SYNC       | ADC6        |             | ADC6            | ADC6            | AC6        |            |            |      |      | TCK  |

| РВ7    | 12   | SYNC       | ADC7        |             | ADC7            | ADC7            |            | AC7        | AC0OUT     |      |      | TDO  |

Table 30-3. Port C - Alternate functions.

| PORT C | PIN# | INTERRUPT  | TCC0 | AWEXC  | TCC1 | USARTC0 | USARTC1 | SPIC | TWIC | сьоскоит | EVENTOUT |

|--------|------|------------|------|--------|------|---------|---------|------|------|----------|----------|

| GND    | 13   |            |      |        |      |         |         |      |      |          |          |

| vcc    | 14   |            |      |        |      |         |         |      |      |          |          |

| PC0    | 15   | SYNC       | OC0A | OC0ALS |      |         |         |      | SDA  |          |          |

| PC1    | 16   | SYNC       | OC0B | OC0AHS |      | XCK0    |         |      | SCL  |          |          |

| PC2    | 17   | SYNC/ASYNC | OC0C | OC0BLS |      | RXD0    |         |      |      |          |          |

| RCALL         k         Reactive Call Subroutine         PC         c         PC + k+1         None         2.7°°°           ICALL         Indirect Call to (2)         PCC15150         c.         2         None         2.7°°°           ECALL         Indirect Call to (2)         PCC15150         c.         2 EID         None         2.3°°           CALL         k         call Subroutine Featur         PC         c.         EID         None         2.4°°           RET         Local Subroutine Featur         PC         c.         STACK         None         4.4°°           RET         Local Subroutine Featur         PC         c.         STACK         None         4.4°°           RET         Local Subroutine Featur         PC         c.         STACK         None         4.4°°           RET         Local Subroutine Featur         PC         c.         STACK         None         4.4°°           RET         BCR         RAR         Compare with Carry         RET         C.         PC 2 or 3         None         1.7°°           CPC         RAR         Compare with Carry         RET         RET (TC)         S.         PC 2 or 3         None         1.2°°                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Mnemonics | Operands | Description                         | Operation                |          |             | Flags       | #Clocks              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|-------------------------------------|--------------------------|----------|-------------|-------------|----------------------|

| EICALL   R.   Catanada Indirect Calle Io(Z)   PC(21-16)   L.   C.   C.   C.   None   C.   C.   C.   C.   None   C.   C.   C.   C.   None   C.   C.   C.   C.   C.   C.   C.   C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RCALL     | k        | Relative Call Subroutine            | PC                       | <b>←</b> | PC + k + 1  | None        | 2 / 3 <sup>(1)</sup> |

| CALL   K   CALL   CAL | ICALL     |          | Indirect Call to (Z)                | PC(15:0)<br>PC(21:16)    |          |             | None        | 2 / 3 <sup>(1)</sup> |

| RET         Subroutine Return         PC         ←         STACK         None         4 / 9 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1 / 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | EICALL    |          | Extended Indirect Call to (Z)       |                          |          |             | None        | 3 <sup>(1)</sup>     |

| Part    | CALL      | k        | call Subroutine                     | PC                       | <b>←</b> | k           | None        | 3 / 4 <sup>(1)</sup> |

| CPSE         Rd.Rr         Compare         if (Rd = Rr) PC         ←         PC + 2 or 3         None         11/2/3           CP         Rd.Rr         Compare         Rd - Rr         C         PC + 2 or 3         None         11/2/3           CPC         Rd.Rr         Compare with Carry         Rd - Rr - C         U         C.C.NVS.H         1           CPI         Rd.K         Compare with Immediate         Rd - K         U         C.C.NVS.H         1           SBRC         Rr, b         Skip if Bit in Pagister Cleared         if (Rr(b) = 0) PC         C         PC + 2 or 3         None         1/2/3           SBIS         R, b         Skip if Bit in VO Register Cleared         If (D(O(Ab) = 0) PC         C         PC + 2 or 3         None         1/2/3           SBIS         A, b         Skip if Bit in VO Register Cleared         If (RR(b) = 1) PC         C         PC + 2 or 3         None         1/2/3           SBIS         A, b         Skip if Bit in VO Register Cleared         If (RREG(a) = 1) then PC         C         PC + k + 1         None         1/2           BRBC         s, k         Branch if Status Plag Cleared         If (SEEG(a) = 0) then PC         C         PC + k + 1         None         1/2 <t< td=""><td>RET</td><td></td><td>Subroutine Return</td><td>PC</td><td><b>←</b></td><td>STACK</td><td>None</td><td>4 / 5<sup>(1)</sup></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RET       |          | Subroutine Return                   | PC                       | <b>←</b> | STACK       | None        | 4 / 5 <sup>(1)</sup> |

| CP         Rd.Rr         Compare with Carry         Rd + Rr + C         C.C.N.V.S.H         1           CPC         Rd.Rr         Compare with Carry         Rd + Rr + C         C.C.N.V.S.H         1           CPI         Rd.K         Compare with Carry         Rd + Rr + C         C.C.N.V.S.H         1           SBRC         Rr, b         Skip if Bit in Register Cleared         if (Rr(b) = 0) PC         PC + 2 or 3         None         1/2/3           SBRS         Rr, b         Skip if Bit in I/O Register Cleared         if (Rr(b) = 1) PC         ← PC + 2 or 3         None         1/2/3           SBIC         A. b         Skip if Bit in I/O Register Steared         if (IC(A,b) = 0) PC         ← PC + 2 or 3         None         2/3/4           SBIS         A. b         Skip if Bit in I/O Register Steared         if (IC(A,b) = 1) PC         ← PC + 2 or 3         None         2/3/4           BRBS         s, k         Branch if Satus Flag Set         if (IC(A,b) = 1) PC         ← PC + k + 1         None         1/2           BRBC         s, k         Branch if Satus Flag Set         if (SEEG(s) = 1) then PC         ← PC + k + 1         None         1/2           BRC         k         Branch if Carry Set         if (C = 1) then PC         ← PC + k + 1         None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RETI      |          | Interrupt Return                    | PC                       | <b>←</b> | STACK       | 1           | 4 / 5 <sup>(1)</sup> |

| CPC         Rd.Rr         Compare with Carry         RdRr - C         L         2.C.N.V.S.H         1           CPI         Rd.K         Compare with Immediate         Rd - K         L         Z.C.N.V.S.H         1           SBRC         Rr, b         Skip if Bit in Register Cleared         if (Rr(b) = 0) PC         +         PC + 2 or 3         None         1 /2 /3           SBRS         Rr, b         Skip if Bit in VO Register Cleared         if (Rr(b) = 1) PC         +         PC + 2 or 3         None         1 /2 /3           SBIS         A, b         Skip if Bit in VO Register Set         if (Rr(b) = 1) PC         +         PC + 2 or 3         None         2 /3 /4           SBIS         A, b         Skip if Bit in VO Register Set         if (RRG(s) = 1) PC         +         PC + 2 or 3         None         2 /3 /4           BRBS         s, k         Branch if Status Flag Set         if (RRG(s) = 1) PC         +         PC + k + 1         None         1 /2           BRBC         s, k         Branch if Status Flag Set         if (SEG(s) = 0) then PC         +         PC + k + 1         None         1 /2           BRC         k         Branch if Status Flag Set         if (SEG(s) = 0) then PC         +         PC + k + 1         None <td< td=""><td>CPSE</td><td>Rd,Rr</td><td>Compare, Skip if Equal</td><td>if (Rd = Rr) PC</td><td><b>←</b></td><td>PC + 2 or 3</td><td>None</td><td>1/2/3</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CPSE      | Rd,Rr    | Compare, Skip if Equal              | if (Rd = Rr) PC          | <b>←</b> | PC + 2 or 3 | None        | 1/2/3                |

| CPI         RAJK         Compare with immediate         Rd + K         PC + 2 or 3         None         1/2/3           SBRC         Rr, b         Skip if Bit in Register Cleared         if (Rr(b) = 0) PC ← PC + 2 or 3         None         1/2/3           SBRS         Rr, b         Skip if Bit in NO Register Cleared         if (NO(A,b) = 0) PC ← PC + 2 or 3         None         1/2/3           SBIS         A, b         Skip if Bit in NO Register Cleared         if (NO(A,b) = 0) PC ← PC + 2 or 3         None         2/3/4           BRSS         s, k         Branch if Satus Flag Set         if (NO(A,b) = 1) PC ← PC + k + 1         None         2/3/4           BRBS         s, k         Branch if Satus Flag Cleared         if (SREG(s) = 1) then PC ← PC + k + 1         None         1/2           BRBC         s, k         Branch if Satus Flag Cleared         if (SEG(s) = 1) then PC ← PC + k + 1         None         1/2           BRBC         s, k         Branch if Not Equal         if (Z = 1) then PC ← PC + k + 1         None         1/2           BRCS         k         Branch if Carry Cleared         if (C = 1) then PC ← PC + k + 1         None         1/2           BRCS         k         Branch if Carry Cleared         if (C = 0) then PC ← PC + k + 1         None         1/2           B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | СР        | Rd,Rr    | Compare                             | Rd - Rr                  |          |             | Z,C,N,V,S,H | 1                    |

| SBRC         Rt, b         Skip if Bit in Register Cleared         if (R(t)) = 0) PC         ← PC + 2 or 3         None         1 / 2 / 3           SBRS         Rt, b         Skip if Bit in Register Set         if (R(t)) = 1) PC         ← PC + 2 or 3         None         1 / 2 / 3           SBIC         A, b         Skip if Bit in I/O Register Set         if (WO(A,b) = 0) PC         ← PC + 2 or 3         None         2 / 3 / 4           SBIS         A, b         Skip if Bit in I/O Register Set         if (WO(A,b) = 1) PC         ← PC + 2 or 3         None         2 / 3 / 4           SBIS         A, b         Skip if Bit in I/O Register Set         if (WO(A,b) = 1) PC         ← PC + k + 1         None         2 / 3 / 4           BRS         s, k         Branch if Status Flag Set         if (SEEG(s) = 1) then PC         ← PC + k + 1         None         1 / 2           BREQ         k         Branch if Equal         if (Z = 1) then PC         ← PC + k + 1         None         1 / 2           BRNE         k         Branch if Lower         if (C = 1) then PC         ← PC + k + 1         None         1 / 2           BRC         k         Branch if Same or Higher         if (C = 0) then PC         ← PC + k + 1         None         1 / 2           BRC         k         Br                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CPC       | Rd,Rr    | Compare with Carry                  | Rd - Rr - C              |          |             | Z,C,N,V,S,H | 1                    |

| SBRS         Rt, b         Skip if Bit in Register Set         if (R(t)) = 1) PC         ←         PC + 2 or 3         None         1 / 2 / 3           SBIC         A, b         Skip if Bit in I/O Register Cleared         if (I/O(A,b) = 0) PC         ←         PC + 2 or 3         None         2 / 3 / 4           SBIS         A, b         Skip if Bit in I/O Register Set         if (I/O(A,b) = 1) PC         ←         PC + 2 or 3         None         2 / 3 / 4           BRBS         s, k         Branch if Status Flag Set         if (SREG(s) = 1) then PC         ←         PC + k + 1         None         1 / 2           BRBC         s, k         Branch if Status Flag Cleared         if (SEG(s) = 0) then PC         ←         PC + k + 1         None         1 / 2           BRBC         s, k         Branch if Status Flag Cleared         if (SEG(s) = 0) then PC         ←         PC + k + 1         None         1 / 2           BRD         k         Branch if Note Equal         if (SEG(s) = 0) then PC         ←         PC + k + 1         None         1 / 2           BRC         k         Branch if Carry Set         if (C = 0) then PC         ←         PC + k + 1         None         1 / 2           BRC         k         Branch if Same or Higher         if (C = 0) then PC <td>CPI</td> <td>Rd,K</td> <td>Compare with Immediate</td> <td>Rd - K</td> <td></td> <td></td> <td>Z,C,N,V,S,H</td> <td>1</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CPI       | Rd,K     | Compare with Immediate              | Rd - K                   |          |             | Z,C,N,V,S,H | 1                    |

| SBIC         A, b         Skip if Bit in I/O Register Cleared         if (I/O(Ab) = 0) PC         ← PC + 2 or 3         None         2/3/4           SBIS         A, b         Skip if Bit in I/O Register Set         If (I/O(Ab) = 1) PC         ← PC + 2 or 3         None         2/3/4           BRBS         s, k         Branch if Status Flag Set         if (SREG(s) = 1) then PC         ← PC + k+1         None         1/2           BRBC         s, k         Branch if Status Flag Cleared         if (SREG(s) = 0) then PC         ← PC + k+1         None         1/2           BRCQ         k         Branch if Status Flag Cleared         if (Z= 1) then PC         ← PC + k+1         None         1/2           BRNE         k         Branch if Not Equal         if (Z= 0) then PC         ← PC + k+1         None         1/2           BRCS         k         Branch if Carry Set         if (C= 1) then PC         ← PC + k+1         None         1/2           BRCS         k         Branch if Carry Set         if (C= 0) then PC         ← PC + k+1         None         1/2           BRCS         k         Branch if Lower         if (C= 0) then PC         ← PC + k+1         None         1/2           BRSH         k         Branch if Minus         if (N = 1) then PC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SBRC      | Rr, b    | Skip if Bit in Register Cleared     | if (Rr(b) = 0) PC        | <b>←</b> | PC + 2 or 3 | None        | 1/2/3                |

| SBIS         A, b         Skip if Bit in I/O Register Set         If (I/O(A,b) = 1) PC         ←         PC+2 or 3         None         2/3/4           BRBS         s, k         Branch if Status Flag Set         if (SREG(s) = 1) then PC         ←         PC+k+1         None         1/2           BRBC         s, k         Branch if Status Flag Cleared         if (SREG(s) = 0) then PC         ←         PC+k+1         None         1/2           BREQ         k         Branch if Not Equal         if (Z = 1) then PC         ←         PC+k+1         None         1/2           BRNE         k         Branch if Not Equal         if (Z = 0) then PC         ←         PC+k+1         None         1/2           BRCS         k         Branch if Carry Set         if (C = 0) then PC         ←         PC+k+1         None         1/2           BRCC         k         Branch if Carry Cleared         if (C = 0) then PC         ←         PC+k+1         None         1/2           BRC         k         Branch if Lower         if (C = 0) then PC         ←         PC+k+1         None         1/2           BRMI         k         Branch if Minus         if (N = 0) then PC         ←         PC+k+1         None         1/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SBRS      | Rr, b    | Skip if Bit in Register Set         | if (Rr(b) = 1) PC        | <b>←</b> | PC + 2 or 3 | None        | 1/2/3                |

| BRBS         s, k         Branch if Status Flag Set         if (SREG(s) = 1) then PC         ←         PC + k+1         None         1/2           BRBC         s, k         Branch if Status Flag Cleared         if (SREG(s) = 0) then PC         ←         PC + k+1         None         1/2           BREO         k         Branch if Equal         if (Z = 1) then PC         ←         PC + k+1         None         1/2           BRNE         k         Branch if Carry Set         if (Z = 0) then PC         ←         PC + k+1         None         1/2           BRCC         k         Branch if Carry Cleared         if (C = 0) then PC         ←         PC + k+1         None         1/2           BRSH         k         Branch if Same or Higher         if (C = 0) then PC         ←         PC + k+1         None         1/2           BRUD         k         Branch if Lower         if (C = 0) then PC         ←         PC + k+1         None         1/2           BRMI         k         Branch if Minus         if (N = 0) then PC         ←         PC + k+1         None         1/2           BRPL         k         Branch if Drus         if (N = V = 0) then PC         ←         PC + k+1         None         1/2           BRS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SBIC      | A, b     | Skip if Bit in I/O Register Cleared | if (I/O(A,b) = 0) PC     | <b>←</b> | PC + 2 or 3 | None        | 2/3/4                |

| BRBC         s, k         Branch if Status Flag Cleared         if (SREG(s) = 0) then PC         ←         PC + k + 1         None         1 / 2           BREQ         k         Branch if Equal         if (Z = 1) then PC         ←         PC + k + 1         None         1 / 2           BRNE         k         Branch if Not Equal         if (Z = 0) then PC         ←         PC + k + 1         None         1 / 2           BRCS         k         Branch if Carry Set         if (C = 0) then PC         ←         PC + k + 1         None         1 / 2           BRCC         k         Branch if Carry Cleared         if (C = 0) then PC         ←         PC + k + 1         None         1 / 2           BRSH         k         Branch if Same or Higher         if (C = 0) then PC         ←         PC + k + 1         None         1 / 2           BRLD         k         Branch if Same or Higher         if (C = 0) then PC         ←         PC + k + 1         None         1 / 2           BRLD         k         Branch if Lower         if (C = 0) then PC         ←         PC + k + 1         None         1 / 2           BRMI         k         Branch if Plus         if (N = 0) then PC         ←         PC + k + 1         None         1 / 2 <td>SBIS</td> <td>A, b</td> <td>Skip if Bit in I/O Register Set</td> <td>If (I/O(A,b) =1) PC</td> <td><b>←</b></td> <td>PC + 2 or 3</td> <td>None</td> <td>2/3/4</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SBIS      | A, b     | Skip if Bit in I/O Register Set     | If (I/O(A,b) =1) PC      | <b>←</b> | PC + 2 or 3 | None        | 2/3/4                |

| BREQ         k         Branch if Equal         if (Z = 1) then PC         ←         PC + k + 1         None         1/2           BRNE         k         Branch if Not Equal         if (Z = 0) then PC         ←         PC + k + 1         None         1/2           BRCS         k         Branch if Carry Set         if (C = 0) then PC         ←         PC + k + 1         None         1/2           BRCC         k         Branch if Carry Cleared         if (C = 0) then PC         ←         PC + k + 1         None         1/2           BRSH         k         Branch if Same or Higher         if (C = 0) then PC         ←         PC + k + 1         None         1/2           BRU         k         Branch if Lower         if (C = 1) then PC         ←         PC + k + 1         None         1/2           BRMI         k         Branch if Minus         if (N = 1) then PC         ←         PC + k + 1         None         1/2           BRPL         k         Branch if Greater or Equal, Signed         if (N = 0) then PC         ←         PC + k + 1         None         1/2           BRLT         k         Branch if Greater or Equal, Signed         if (N = 0) then PC         ←         PC + k + 1         None         1/2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BRBS      | s, k     | Branch if Status Flag Set           | if (SREG(s) = 1) then PC | <b>←</b> | PC + k + 1  | None        | 1/2                  |

| BRNE         k         Branch if Not Equal         if (Z = 0) then PC         ← PC + k + 1         None         1/2           BRCS         k         Branch if Carry Set         if (C = 1) then PC         ← PC + k + 1         None         1/2           BRCC         k         Branch if Carry Cleared         if (C = 0) then PC         ← PC + k + 1         None         1/2           BRSH         k         Branch if Same or Higher         if (C = 0) then PC         ← PC + k + 1         None         1/2           BRLO         k         Branch if Lower         if (C = 1) then PC         ← PC + k + 1         None         1/2           BRMI         k         Branch if Minus         if (N = 1) then PC         ← PC + k + 1         None         1/2           BRPL         k         Branch if Jess or Law Signed         if (N = 0) then PC         ← PC + k + 1         None         1/2           BRGE         k         Branch if Less Than, Signed         if (N ⊕ V = 0) then PC         ← PC + k + 1         None         1/2           BRLT         k         Branch if Half Carry Flag Set         if (H = 1) then PC         ← PC + k + 1         None         1/2           BRTS         k         Branch if T Flag Cleared         if (T = 0) then PC         ← PC + k + 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BRBC      | s, k     | Branch if Status Flag Cleared       | if (SREG(s) = 0) then PC | <b>←</b> | PC + k + 1  | None        | 1/2                  |

| BRCS         k         Branch if Carry Set         if (C = 1) then PC         ←         PC + k + 1         None         1 / 2           BRCC         k         Branch if Carry Cleared         if (C = 0) then PC         ←         PC + k + 1         None         1 / 2           BRSH         k         Branch if Same or Higher         if (C = 0) then PC         ←         PC + k + 1         None         1 / 2           BRLO         k         Branch if Lower         if (C = 1) then PC         ←         PC + k + 1         None         1 / 2           BRMI         k         Branch if Minus         if (N = 1) then PC         ←         PC + k + 1         None         1 / 2           BRPL         k         Branch if Plus         if (N = 0) then PC         ←         PC + k + 1         None         1 / 2           BRGE         k         Branch if Greater or Equal, Signed         if (N = 0) then PC         ←         PC + k + 1         None         1 / 2           BRLT         k         Branch if Less Than, Signed         if (N = 0) then PC         ←         PC + k + 1         None         1 / 2           BRHS         k         Branch if Half Carry Flag Set         if (H = 1) then PC         ←         PC + k + 1         None         1 / 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | BREQ      | k        | Branch if Equal                     | if (Z = 1) then PC       | <b>←</b> | PC + k + 1  | None        | 1/2                  |

| BRCC         k         Branch if Carry Cleared         if (C = 0) then PC         ←         PC + k + 1         None         1 / 2           BRSH         k         Branch if Same or Higher         if (C = 0) then PC         ←         PC + k + 1         None         1 / 2           BRLO         k         Branch if Lower         if (C = 1) then PC         ←         PC + k + 1         None         1 / 2           BRMI         k         Branch if Minus         if (N = 1) then PC         ←         PC + k + 1         None         1 / 2           BRPL         k         Branch if Plus         if (N = 0) then PC         ←         PC + k + 1         None         1 / 2           BRGE         k         Branch if Greater or Equal, Signed         if (N = 0) then PC         ←         PC + k + 1         None         1 / 2           BRLT         k         Branch if Less Than, Signed         if (N = 0) then PC         ←         PC + k + 1         None         1 / 2           BRHS         k         Branch if Half Carry Flag Set         if (H = 1) then PC         ←         PC + k + 1         None         1 / 2           BRTS         k         Branch if T Flag Cleared         if (T = 0) then PC         ←         PC + k + 1         None         1 / 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BRNE      | k        | Branch if Not Equal                 | if (Z = 0) then PC       | <b>←</b> | PC + k + 1  | None        | 1/2                  |

| BRSH         k         Branch if Same or Higher         if (C = 0) then PC         ←         PC+k+1         None         1/2           BRLO         k         Branch if Lower         if (C = 1) then PC         ←         PC+k+1         None         1/2           BRMI         k         Branch if Minus         if (N = 1) then PC         ←         PC+k+1         None         1/2           BRPL         k         Branch if Plus         if (N = 0) then PC         ←         PC+k+1         None         1/2           BRGE         k         Branch if Greater or Equal, Signed         if (N ⊕ V = 0) then PC         ←         PC+k+1         None         1/2           BRLT         k         Branch if Less Than, Signed         if (N ⊕ V = 1) then PC         ←         PC+k+1         None         1/2           BRHS         k         Branch if Half Carry Flag Set         if (H = 1) then PC         ←         PC+k+1         None         1/2           BRTS         k         Branch if T Flag Set         if (T = 1) then PC         ←         PC+k+1         None         1/2           BRTC         k         Branch if Overflow Flag is Set         if (Y = 1) then PC         ←         PC+k+1         None         1/2           BRVS </td <td>BRCS</td> <td>k</td> <td>Branch if Carry Set</td> <td>if (C = 1) then PC</td> <td><b>←</b></td> <td>PC + k + 1</td> <td>None</td> <td>1/2</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | BRCS      | k        | Branch if Carry Set                 | if (C = 1) then PC       | <b>←</b> | PC + k + 1  | None        | 1/2                  |

| BRLO         k         Branch if Lower         if (C = 1) then PC         ←         PC + k + 1         None         1 / 2           BRMI         k         Branch if Minus         if (N = 1) then PC         ←         PC + k + 1         None         1 / 2           BRPL         k         Branch if Plus         if (N = 0) then PC         ←         PC + k + 1         None         1 / 2           BRGE         k         Branch if Greater or Equal, Signed         if (N ⊕ V = 0) then PC         ←         PC + k + 1         None         1 / 2           BRLT         k         Branch if Less Than, Signed         if (N ⊕ V = 1) then PC         ←         PC + k + 1         None         1 / 2           BRHS         k         Branch if Half Carry Flag Set         if (H = 1) then PC         ←         PC + k + 1         None         1 / 2           BRTS         k         Branch if T Flag Set         if (T = 1) then PC         ←         PC + k + 1         None         1 / 2           BRTC         k         Branch if T Flag Cleared         if (T = 0) then PC         ←         PC + k + 1         None         1 / 2           BRVS         k         Branch if Overflow Flag is Set         if (V = 0) then PC         ←         PC + k + 1         None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | BRCC      | k        | Branch if Carry Cleared             | if (C = 0) then PC       | <b>←</b> | PC + k + 1  | None        | 1/2                  |

| BRMI         k         Branch if Minus         if (N = 1) then PC         ←         PC + k + 1         None         1/2           BRPL         k         Branch if Plus         if (N ⊕ V = 0) then PC         ←         PC + k + 1         None         1/2           BRGE         k         Branch if Greater or Equal, Signed         if (N ⊕ V = 0) then PC         ←         PC + k + 1         None         1/2           BRLT         k         Branch if Less Than, Signed         if (N ⊕ V = 1) then PC         ←         PC + k + 1         None         1/2           BRHS         k         Branch if Half Carry Flag Set         if (H = 1) then PC         ←         PC + k + 1         None         1/2           BRTS         k         Branch if T Flag Set         if (T = 0) then PC         ←         PC + k + 1         None         1/2           BRTC         k         Branch if T Flag Cleared         if (T = 0) then PC         ←         PC + k + 1         None         1/2           BRVS         k         Branch if Overflow Flag is Set         if (V = 1) then PC         ←         PC + k + 1         None         1/2           BRVC         k         Branch if Interrupt Enabled         if (I = 0) then PC         ←         PC + k + 1         None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | BRSH      | k        | Branch if Same or Higher            | if (C = 0) then PC       | <b>←</b> | PC + k + 1  | None        | 1/2                  |

| BRPL         k         Branch if Plus         if (N = 0) then PC         ←         PC + k + 1         None         1/2           BRGE         k         Branch if Greater or Equal, Signed         if (N ⊕ V = 0) then PC         ←         PC + k + 1         None         1/2           BRLT         k         Branch if Less Than, Signed         if (N ⊕ V = 1) then PC         ←         PC + k + 1         None         1/2           BRHS         k         Branch if Half Carry Flag Set         if (H = 1) then PC         ←         PC + k + 1         None         1/2           BRTS         k         Branch if T Flag Set         if (T = 0) then PC         ←         PC + k + 1         None         1/2           BRTC         k         Branch if T Flag Cleared         if (T = 0) then PC         ←         PC + k + 1         None         1/2           BRVS         k         Branch if Overflow Flag is Set         if (V = 0) then PC         ←         PC + k + 1         None         1/2           BRVC         k         Branch if Interrupt Enabled         if (V = 0) then PC         ←         PC + k + 1         None         1/2           BRID         k         Branch if Interrupt Disabled         if (I = 0) then PC         ←         PC + k + 1         None <td>BRLO</td> <td>k</td> <td>Branch if Lower</td> <td>if (C = 1) then PC</td> <td><b>←</b></td> <td>PC + k + 1</td> <td>None</td> <td>1/2</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | BRLO      | k        | Branch if Lower                     | if (C = 1) then PC       | <b>←</b> | PC + k + 1  | None        | 1/2                  |

| BRGE         k         Branch if Greater or Equal, Signed         if (N ⊕ V= 0) then PC         ←         PC + k + 1         None         1/2           BRLT         k         Branch if Less Than, Signed         if (N ⊕ V= 1) then PC         ←         PC + k + 1         None         1/2           BRHS         k         Branch if Half Carry Flag Set         if (H = 1) then PC         ←         PC + k + 1         None         1/2           BRHS         k         Branch if Half Carry Flag Cleared         if (H = 0) then PC         ←         PC + k + 1         None         1/2           BRTS         k         Branch if T Flag Set         if (T = 1) then PC         ←         PC + k + 1         None         1/2           BRTC         k         Branch if Overflow Flag is Set         if (Y = 0) then PC         ←         PC + k + 1         None         1/2           BRVC         k         Branch if Overflow Flag is Cleared         if (V = 0) then PC         ←         PC + k + 1         None         1/2           BRIE         k         Branch if Interrupt Disabled         if (I = 1) then PC         ←         PC + k + 1         None         1/2           BRID         k         Branch if Interrupt Disabled         if (I = 0) then PC         ←         PC + k                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BRMI      | k        | Branch if Minus                     | if (N = 1) then PC       | <b>←</b> | PC + k + 1  | None        | 1/2                  |

| BRLT         k         Branch if Less Than, Signed         if (N ⊕ V= 1) then PC         ←         PC + k + 1         None         1/2           BRHS         k         Branch if Half Carry Flag Set         if (H = 1) then PC         ←         PC + k + 1         None         1/2           BRHC         k         Branch if Half Carry Flag Cleared         if (H = 0) then PC         ←         PC + k + 1         None         1/2           BRTS         k         Branch if T Flag Set         if (T = 1) then PC         ←         PC + k + 1         None         1/2           BRTC         k         Branch if T Flag Cleared         if (T = 0) then PC         ←         PC + k + 1         None         1/2           BRVS         k         Branch if Overflow Flag is Set         if (V = 1) then PC         ←         PC + k + 1         None         1/2           BRVC         k         Branch if Interrupt Enabled         if (V = 0) then PC         ←         PC + k + 1         None         1/2           BRID         k         Branch if Interrupt Disabled         if (I = 0) then PC         ←         PC + k + 1         None         1/2           Data Transfer Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BRPL      | k        | Branch if Plus                      | if (N = 0) then PC       | <b>←</b> | PC + k + 1  | None        | 1/2                  |

| BRHS         k         Branch if Half Carry Flag Set         if (H = 1) then PC         ←         PC + k + 1         None         1/2           BRHC         k         Branch if Half Carry Flag Cleared         if (H = 0) then PC         ←         PC + k + 1         None         1/2           BRTS         k         Branch if T Flag Set         if (T = 1) then PC         ←         PC + k + 1         None         1/2           BRTC         k         Branch if T Flag Cleared         if (T = 0) then PC         ←         PC + k + 1         None         1/2           BRVS         k         Branch if Overflow Flag is Set         if (V = 1) then PC         ←         PC + k + 1         None         1/2           BRVC         k         Branch if Interrupt Enabled         if (V = 0) then PC         ←         PC + k + 1         None         1/2           BRIE         k         Branch if Interrupt Disabled         if (I = 0) then PC         ←         PC + k + 1         None         1/2           Data Transfer Instructions           MOV         Rd, Rr         Copy Register         Rd         ←         Rr         None         1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | BRGE      | k        | Branch if Greater or Equal, Signed  | if (N ⊕ V= 0) then PC    | <b>←</b> | PC + k + 1  | None        | 1/2                  |