Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | AVR                                                         |

| Core Size                  | 8/16-Bit                                                    |

| Speed                      | 32MHz                                                       |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                  |

| Number of I/O              | 78                                                          |

| Program Memory Size        | 64KB (32K x 16)                                             |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | 2K x 8                                                      |

| RAM Size                   | 4K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                 |

| Data Converters            | A/D 16x12b; D/A 4x12b                                       |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 100-VFBGA                                                   |

| Supplier Device Package    | 100-VFBGA (7x7)                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/atxmega64a1-c7ur |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

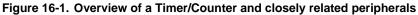

# 1. Ordering Information

| Ordering Code     | Flash (B)  | E <sup>2</sup> | SRAM | Speed (MHz) | Power Supply | Package <sup>(1)(2)(3)</sup> | Temp         |

|-------------------|------------|----------------|------|-------------|--------------|------------------------------|--------------|

| ATxmega128A1-AU   | 128K + 8K  | 2 KB           | 8 KB |             |              |                              |              |

| ATxmega128A1-AUR  | 1200 + 00  |                |      | 100.4       |              |                              |              |

| ATxmega64A1-AU    | 64K + 4K   | 2 KB           | 4 KB |             |              | 100A                         |              |

| ATxmega64A1-AUR   | 04N + 4N   | 2 ND           | 4 ND |             |              |                              |              |

| ATxmega128A1-CU   | 128K + 8K  | 2 KB           | 8 KB |             | 1.6 - 3.6V   | 100C1                        |              |

| ATxmega128A1CUR   | 120N + ON  | 2 10           | 0 ND | 32          |              |                              | -40°C - 85°C |

| ATxmega64A1-CU    | 64K + 4K   | 2 KB           | 4 KB |             |              |                              |              |

| ATxmega64A1-CUR   | 041 + 41   | 2 10           | 4 ND |             |              |                              |              |

| ATxmega128A1-C7U  | 128K + 8K  | 2 KB           | 8 KB |             |              |                              |              |

| ATxmega128A1-C7UR | 1200 + 00  | 2 ND           | 0 ND |             |              | 100C2                        |              |

| ATxmega64A1-C7U   | 64K + 4K   | 2 KB           | 4 KB |             |              |                              |              |

| ATxmega64A1-C7UR  | 0411 7 411 |                |      |             |              |                              |              |

Notes: 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information.

2. Pb-free packaging, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green.

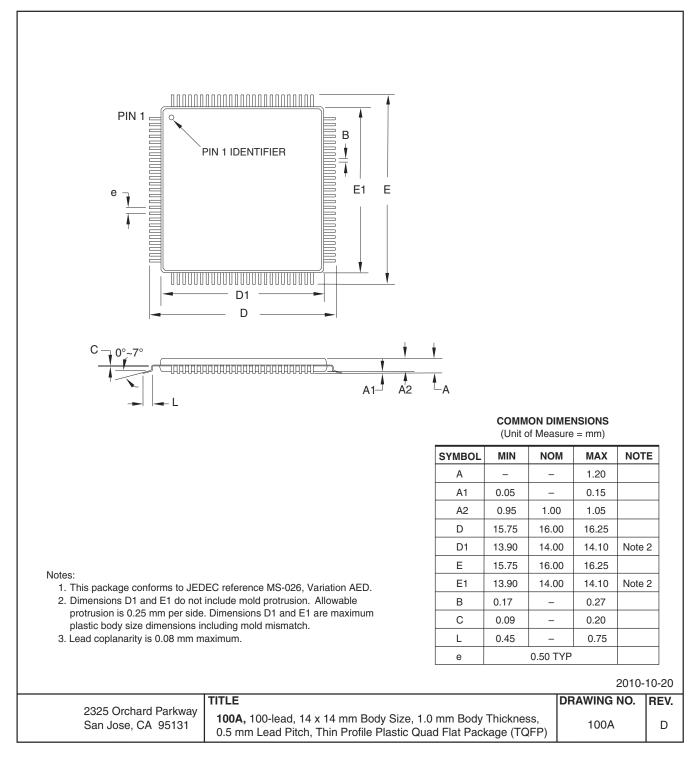

3. For packaging information, see "Packaging information" on page 70.

|       | Package Type                                                                                  |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------|--|--|--|--|--|

| 100A  | 100-lead, 14 x 14 x 1.0mm, 0.5mm lead pitch, thin profile plastic quad flat package (TQFP)    |  |  |  |  |  |

| 100C1 | 100-ball, 9 x 9 x 1.2mm body, ball pitch 0.88mm, chip ball grid array (CBGA)                  |  |  |  |  |  |

| 100C2 | 100-ball, 7 x 7 x 1.0mm body, ball pitch 0.65mm, very thin fine-pitch ball grid array (VFBGA) |  |  |  |  |  |

# **Typical Applications**

| Industrial control | Climate control            | Low power battery applications |

|--------------------|----------------------------|--------------------------------|

| Factory automation | RF and ZigBee <sup>®</sup> | Power tools                    |

| Building control   | Sensor control             | HVAC                           |

| Board control      | Optical                    | Utility metering               |

| White goods        | Medical applications       |                                |

# 7. AVR CPU

## 7.1 Features

- 8/16-bit high performance AVR RISC Architecture

- 138 instructions

- Hardware multiplier

- 32x8-bit registers directly connected to the ALU

- Stack in SRAM

- Stack Pointer accessible in I/O memory space

- Direct addressing of up to 16M Bytes of program and data memory

- True 16/24-bit access to 16/24-bit I/O registers

- Support for 8-, 16- and 32-bit Arithmetic

- Configuration Change Protection of system critical features

## 7.2 Overview

All Atmel AVR XMEGA devices use the 8/16-bit AVR CPU. The main function of the CPU is to execute the code and perform all calculations. The CPU is able to access memories, perform calculations, control peripherals, and execute the program in the flash memory. Interrupt handling is described in a separate section, refer to "Interrupts and Programmable Multilevel Interrupt Controller" on page 29.

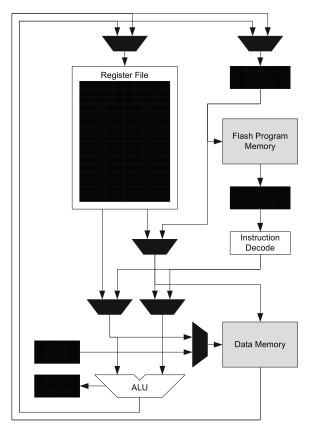

## 7.3 Architectural Overview

In order to maximize performance and parallelism, the AVR CPU uses a Harvard architecture with separate memories and buses for program and data. Instructions in the program memory are executed with single-level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This enables instructions to be executed on every clock cycle. For details of all AVR instructions, refer to http://www.atmel.com/avr.

Figure 7-1. Block diagram of the AVR CPU architecture.

The arithmetic logic unit (ALU) supports arithmetic and logic operations between registers or between a constant and a register. Single-register operations can also be executed in the ALU. After an arithmetic operation, the status register is updated to reflect information about the result of the operation.

The ALU is directly connected to the fast-access register file. The 32 x 8-bit general purpose working registers all have single clock cycle access time allowing single-cycle arithmetic logic unit (ALU) operation between registers or between a register and an immediate. Six of the 32 registers can be used as three 16-bit address pointers for program and data space addressing, enabling efficient address calculations.

The memory spaces are linear. The data memory space and the program memory space are two different memory spaces.

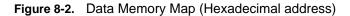

The data memory space is divided into I/O registers, SRAM, and external RAM. In addition, the EEPROM can be memory mapped in the data memory.

All I/O status and control registers reside in the lowest 4KB addresses of the data memory. This is referred to as the I/O memory space. The lowest 64 addresses can be accessed directly, or as the data space locations from 0x00 to 0x3F. The rest is the extended I/O memory space, ranging from 0x0040 to 0x0FFF. I/O registers here must be accessed as data space locations using load (LD/LDS/LDD) and store (ST/STS/STD) instructions.

The SRAM holds data. Code execution from SRAM is not supported. It can easily be accessed through the five different addressing modes supported in the AVR architecture. The first SRAM address is 0x2000.

Data addresses 0x1000 to 0x1FFF are reserved for memory mapping of EEPROM.

The program memory is divided in two sections, the application program section and the boot program section. Both sections have dedicated lock bits for write and read/write protection. The SPM instruction that is used for self-programming of the application flash memory must reside in the boot program section. The application section contains an application table section with separate lock bits for write and read/write protection. The application table section can be used for safe storing of nonvolatile data in the program memory.

## 8.6 EEPROM

XMEGA AU devices have EEPROM for nonvolatile data storage. It is either addressable in a separate data space (default) or memory mapped and accessed in normal data space. The EEPROM supports both byte and page access. Memory mapped EEPROM allows highly efficient EEPROM reading and EEPROM buffer loading. When doing this, EEPROM is accessible using load and store instructions. Memory mapped EEPROM will always start at hexadecimal address 0x1000.

## 8.7 I/O Memory

The status and configuration registers for peripherals and modules, including the CPU, are addressable through I/O memory locations. All I/O locations can be accessed by the load (LD/LDS/LDD) and store (ST/STS/STD) instructions, which is used to transfer data between the 32 registers in the register file and the I/O memory. The IN and OUT instructions can address I/O memory locations in the range 0x00 - 0x3F directly. In the address range 0x00 - 0x1F, single- cycle instructions for manipulation and checking of individual bits are available.

The I/O memory address for all peripherals and modules in XMEGA A1U is shown in the "Peripheral Module Address Map" on page 62.

#### 8.7.1 General Purpose I/O Registers

The lowest 16 I/O memory addresses are reserved as general purpose I/O registers. These registers can be used for storing global variables and flags, as they are directly bit-accessible using the SBI, CBI, SBIS, and SBIC instructions.

### 8.8 External Memory

Four ports can be used for external memory, supporting external SRAM, SDRAM, and memory mapped peripherals such as LCD displays. Refer to "EBI – External Bus Interface" on page 47. The external memory address space will always start at the end of internal SRAM.

### 8.9 Data Memory and Bus Arbitration

Since the data memory is organized as four separate sets of memories, the different bus masters (CPU, DMA controller read and DMA controller write, etc.) can access different memory sections at the same time.

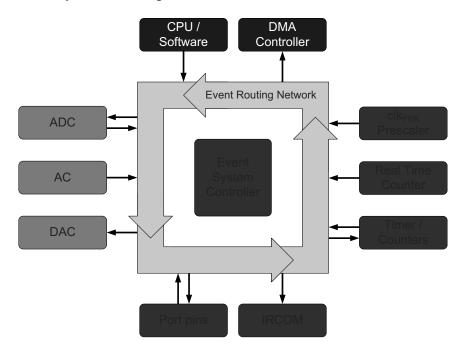

Figure 10-1. Event system block diagram.

he event routing network consists of eight software-configurable multiplexers that control how events are routed and used. These are called event channels, and allow for up to eight parallel event routing configurations. The maximum routing latency is two peripheral clock cycles. The event system works in both active mode and idle sleep mode.

# 13.5 WDT - Watchdog Timer

#### 13.5.1 Features

- Issues a device reset if the timer is not reset before its timeout period

- Asynchronous operation from dedicated oscillator

- 1kHz output of the 32kHz ultra low power oscillator

- 11 selectable timeout periods, from 8ms to 8s

- Two operation modes:

- Normal mode

- Window mode

- Configuration lock to prevent unwanted changes

## 13.6 Overview

The watchdog timer (WDT) is a system function for monitoring correct program operation. It makes it possible to recover from error situations such as runaway or deadlocked code. The WDT is a timer, configured to a predefined timeout period, and is constantly running when enabled. If the WDT is not reset within the timeout period, it will issue a microcontroller reset. The WDT is reset by executing the WDR (watchdog timer reset) instruction from the application code.

The window mode makes it possible to define a time slot or window inside the total timeout period during which WDT must be reset. If the WDT is reset outside this window, either too early or too late, a system reset will be issued. Compared to the normal mode, this can also catch situations where a code error causes constant WDR execution.

The WDT will run in active mode and all sleep modes, if enabled. It is asynchronous, runs from a CPU-independent clock source, and will continue to operate to issue a system reset even if the main clocks fail.

The configuration change protection mechanism ensures that the WDT settings cannot be changed by accident. For increased safety, a fuse for locking the WDT settings is also available.

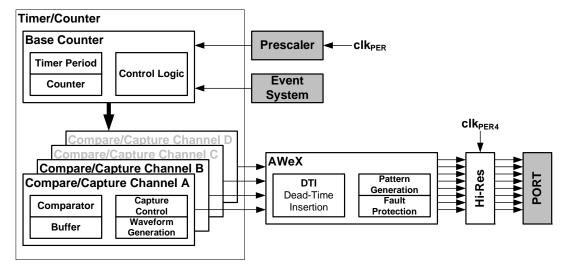

The high-resolution (hi-res) extension can be used to increase the waveform output resolution by four or eight times by using an internal clock source running up to four times faster than the peripheral clock. See "Hi-Res - High Resolution Extension" on page 39 for more details.

PORTC, PORTD, PORTE and PORTF each has one Timer/Counter 0 and one Timer/Counter1. Notation of these Timer/Counters are TCC0 (Time/Counter C0), TCC1, TCD0, TCD1, TCE0, TCE1, TCF0, and TCF1, respectively.

# 18. Hi-Res - High Resolution Extension

## 18.1 Features

- Increases Waveform Generator resolution by 2-bits (4x)

- Supports Frequency, single- and dual-slope PWM operation

- Supports the AWeX when this is enabled and used for the same Timer/Counter

### 18.2 Overview

TThe high-resolution (hi-res) extension can be used to increase the resolution of the waveform generation output from a timer/counter by four or eight. It can be used for a timer/counter doing frequency, single-slope PWM, or dual-slope PWM generation. It can also be used with the AWeX if this is used for the same timer/counter.

The hi-res extension uses the peripheral 4x clock (ClkPER4). The system clock prescalers must be configured so the peripheral 4x clock frequency is four times higher than the peripheral and CPU clock frequency when the hi-res extension is enabled.

There are four hi-res extensions that each can be enabled for each timer/counters pair on PORTC, PORTD, PORTE and PORTF. The notation of these peripherals are HIRESC, HIRESD, HIRESE and HIRESF, respectively.

# 26. ADC - 12-bit Analog to Digital Converter

### 26.1 Features

- Two ADCs with 12-bit resolution

- 2Msps sample rate for each ADC

- Signed and unsigned conversions

- 4 result registers with individual input channel control for each ADC

- 8 single ended inputs for each ADC

- 8x4 differential inputs for each ADC

- 4 internal inputs:

- Integrated Temperature Sensor

- DAC Output

- VCC voltage divided by 10

- Bandgap voltage

- Software selectable gain of 2, 4, 8, 16, 32 or 64

- Software selectable resolution of 8- or 12-bit.

- Internal or External Reference selection

- Event triggered conversion for accurate timing

- DMA transfer of conversion results

- Interrupt/Event on compare result

### 26.2 Overview

XMEGA A1 devices have two Analog to Digital Converters (ADC), see Figure 26-1 on page 49. The two ADC modules can be operated simultaneously, individually or synchronized.

The ADC converts analog voltages to digital values. The ADC has 12-bit resolution and is capable of converting up to 2 million samples per second. The input selection is flexible, and both single-ended and differential measurements can be done. For differential measurements an optional gain stage is available to increase the dynamic range. In addition several internal signal inputs are available. The ADC can provide both signed and unsigned results.

This is a pipeline ADC. A pipeline ADC consists of several consecutive stages, where each stage convert one part of the result. The pipeline design enables high sample rate at low clock speeds, and remove limitations on samples speed versus propagation delay. This also means that a new analog voltage can be sampled and a new ADC measurement started while other ADC measurements are ongoing.

ADC measurements can either be started by application software or an incoming event from another peripheral in the device. Four different result registers with individual input selection (MUX selection) are provided to make it easier for the application to keep track of the data. Each result register and MUX selection pair is referred to as an ADC Channel. It is possible to use DMA to move ADC results directly to memory or peripherals when conversions are done.

Both internal and external analog reference voltages can be used. An accurate internal 1.0V reference is available.

An integrated temperature sensor is available and the output from this can be measured with the ADC. The output from the DAC, VCC/10 and the Bandgap voltage can also be measured by the ADC.

# 32. Instruction Set Summary

| Mnemonics | Operands | Description                              | Operation                                             |        |                                          | Flags       | #Clocks |

|-----------|----------|------------------------------------------|-------------------------------------------------------|--------|------------------------------------------|-------------|---------|

|           |          | Arithmetic                               | and Logic Instructions                                |        |                                          |             |         |

| ADD       | Rd, Rr   | Add without Carry                        | Rd                                                    | ←      | Rd + Rr                                  | Z,C,N,V,S,H | 1       |

| ADC       | Rd, Rr   | Add with Carry                           | Rd                                                    | ←      | Rd + Rr + C                              | Z,C,N,V,S,H | 1       |

| ADIW      | Rd, K    | Add Immediate to Word                    | Rd                                                    | ~      | Rd + 1:Rd + K                            | Z,C,N,V,S   | 2       |

| SUB       | Rd, Rr   | Subtract without Carry                   | Rd                                                    | ~      | Rd - Rr                                  | Z,C,N,V,S,H | 1       |

| SUBI      | Rd, K    | Subtract Immediate                       | Rd                                                    | ←      | Rd - K                                   | Z,C,N,V,S,H | 1       |

| SBC       | Rd, Rr   | Subtract with Carry                      | Rd                                                    | ~      | Rd - Rr - C                              | Z,C,N,V,S,H | 1       |

| SBCI      | Rd, K    | Subtract Immediate with Carry            | Rd                                                    | ←      | Rd - K - C                               | Z,C,N,V,S,H | 1       |

| SBIW      | Rd, K    | Subtract Immediate from Word             | Rd + 1:Rd                                             | ~      | Rd + 1:Rd - K                            | Z,C,N,V,S   | 2       |

| AND       | Rd, Rr   | Logical AND                              | Rd                                                    | ←      | Rd ● Rr                                  | Z,N,V,S     | 1       |

| ANDI      | Rd, K    | Logical AND with Immediate               | Rd                                                    | ~      | Rd • K                                   | Z,N,V,S     | 1       |

| OR        | Rd, Rr   | Logical OR                               | Rd                                                    | ←      | Rd v Rr                                  | Z,N,V,S     | 1       |

| ORI       | Rd, K    | Logical OR with Immediate                | Rd                                                    | ~      | Rd v K                                   | Z,N,V,S     | 1       |

| EOR       | Rd, Rr   | Exclusive OR                             | Rd                                                    | ←      | Rd ⊕ Rr                                  | Z,N,V,S     | 1       |

| СОМ       | Rd       | One's Complement                         | Rd                                                    | ~      | \$FF - Rd                                | Z,C,N,V,S   | 1       |

| NEG       | Rd       | Two's Complement                         | Rd                                                    | ←      | \$00 - Rd                                | Z,C,N,V,S,H | 1       |

| SBR       | Rd,K     | Set Bit(s) in Register                   | Rd                                                    | ←      | Rd v K                                   | Z,N,V,S     | 1       |

| CBR       | Rd,K     | Clear Bit(s) in Register                 | Rd                                                    | ←      | Rd ● (\$FFh - K)                         | Z,N,V,S     | 1       |

| INC       | Rd       | Increment                                | Rd                                                    | ~      | Rd + 1                                   | Z,N,V,S     | 1       |

| DEC       | Rd       | Decrement                                | Rd                                                    | ~      | Rd - 1                                   | Z,N,V,S     | 1       |

| TST       | Rd       | Test for Zero or Minus                   | Rd                                                    | ~      | Rd • Rd                                  | Z,N,V,S     | 1       |

| CLR       | Rd       | Clear Register                           | Rd                                                    | ~      | Rd ⊕ Rd                                  | Z,N,V,S     | 1       |

| SER       | Rd       | Set Register                             | Rd                                                    | ~      | \$FF                                     | None        | 1       |

| MUL       | Rd,Rr    | Multiply Unsigned                        | R1:R0                                                 | ←      | Rd x Rr (UU)                             | Z,C         | 2       |

| MULS      | Rd,Rr    | Multiply Signed                          | R1:R0                                                 | ←      | Rd x Rr (SS)                             | Z,C         | 2       |

| MULSU     | Rd,Rr    | Multiply Signed with Unsigned            | R1:R0                                                 | ~      | Rd x Rr (SU)                             | Z,C         | 2       |

| FMUL      | Rd,Rr    | Fractional Multiply Unsigned             | R1:R0                                                 | ~      | Rd x Rr<<1 (UU)                          | Z,C         | 2       |

| FMULS     | Rd,Rr    | Fractional Multiply Signed               | R1:R0                                                 | ←      | Rd x Rr<<1 (SS)                          | Z,C         | 2       |

| FMULSU    | Rd,Rr    | Fractional Multiply Signed with Unsigned | R1:R0                                                 | ~      | Rd x Rr<<1 (SU)                          | Z,C         | 2       |

| DES       | К        | Data Encryption                          | if (H = 0) then R15:R0<br>else if (H = 1) then R15:R0 | ←<br>← | Encrypt(R15:R0, K)<br>Decrypt(R15:R0, K) |             | 1/2     |

|           |          | Bran                                     | ch Instructions                                       |        |                                          |             |         |

| RJMP      | k        | Relative Jump                            | PC                                                    | ~      | PC + k + 1                               | None        | 2       |

| IJMP      |          | Indirect Jump to (Z)                     | PC(15:0)<br>PC(21:16)                                 | ←<br>← | Z,<br>0                                  | None        | 2       |

| EIJMP     |          | Extended Indirect Jump to (Z)            | PC(15:0)<br>PC(21:16)                                 | ←<br>← | Z,<br>EIND                               | None        | 2       |

| JMP       | k        | Jump                                     | PC                                                    | ~      | k                                        | None        | 3       |

|           |          |                                          |                                                       |        |                                          |             |         |

| Mnemonics | Operands | Description                         | Operation                    |        |             | Flags       | #Clocks              |

|-----------|----------|-------------------------------------|------------------------------|--------|-------------|-------------|----------------------|

| RCALL     | k        | Relative Call Subroutine            | PC                           | ←      | PC + k + 1  | None        | 2 / 3 <sup>(1)</sup> |

| ICALL     |          | Indirect Call to (Z)                | PC(15:0)<br>PC(21:16)        | ←<br>← | Z,<br>0     | None        | 2 / 3 <sup>(1)</sup> |

| EICALL    |          | Extended Indirect Call to (Z)       | PC(15:0)<br>PC(21:16)        | ←<br>← | Z,<br>EIND  | None        | 3(1)                 |

| CALL      | k        | call Subroutine                     | PC                           | ←      | k           | None        | 3 / 4 <sup>(1)</sup> |

| RET       |          | Subroutine Return                   | PC                           | ~      | STACK       | None        | 4 / 5 <sup>(1)</sup> |

| RETI      |          | Interrupt Return                    | PC                           | ←      | STACK       | I           | 4 / 5 <sup>(1)</sup> |

| CPSE      | Rd,Rr    | Compare, Skip if Equal              | if (Rd = Rr) PC              | ~      | PC + 2 or 3 | None        | 1/2/3                |

| СР        | Rd,Rr    | Compare                             | Rd - Rr                      |        |             | Z,C,N,V,S,H | 1                    |

| CPC       | Rd,Rr    | Compare with Carry                  | Rd - Rr - C                  |        |             | Z,C,N,V,S,H | 1                    |

| CPI       | Rd,K     | Compare with Immediate              | Rd - K                       |        |             | Z,C,N,V,S,H | 1                    |

| SBRC      | Rr, b    | Skip if Bit in Register Cleared     | if (Rr(b) = 0) PC            | ~      | PC + 2 or 3 | None        | 1/2/3                |

| SBRS      | Rr, b    | Skip if Bit in Register Set         | if (Rr(b) = 1) PC            | ←      | PC + 2 or 3 | None        | 1/2/3                |

| SBIC      | A, b     | Skip if Bit in I/O Register Cleared | if (I/O(A,b) = 0) PC         | ←      | PC + 2 or 3 | None        | 2/3/4                |

| SBIS      | A, b     | Skip if Bit in I/O Register Set     | If (I/O(A,b) =1) PC          | ←      | PC + 2 or 3 | None        | 2/3/4                |

| BRBS      | s, k     | Branch if Status Flag Set           | if (SREG(s) = 1) then PC     | ←      | PC + k + 1  | None        | 1/2                  |

| BRBC      | s, k     | Branch if Status Flag Cleared       | if (SREG(s) = 0) then PC     | ←      | PC + k + 1  | None        | 1/2                  |

| BREQ      | k        | Branch if Equal                     | if (Z = 1) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRNE      | k        | Branch if Not Equal                 | if (Z = 0) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRCS      | k        | Branch if Carry Set                 | if (C = 1) then PC           | ~      | PC + k + 1  | None        | 1/2                  |

| BRCC      | k        | Branch if Carry Cleared             | if (C = 0) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRSH      | k        | Branch if Same or Higher            | if (C = 0) then PC           | ~      | PC + k + 1  | None        | 1/2                  |

| BRLO      | k        | Branch if Lower                     | if (C = 1) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRMI      | k        | Branch if Minus                     | if (N = 1) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRPL      | k        | Branch if Plus                      | if (N = 0) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRGE      | k        | Branch if Greater or Equal, Signed  | if (N $\oplus$ V= 0) then PC | ~      | PC + k + 1  | None        | 1/2                  |

| BRLT      | k        | Branch if Less Than, Signed         | if (N $\oplus$ V= 1) then PC | ←      | PC + k + 1  | None        | 1/2                  |

| BRHS      | k        | Branch if Half Carry Flag Set       | if (H = 1) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRHC      | k        | Branch if Half Carry Flag Cleared   | if (H = 0) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRTS      | k        | Branch if T Flag Set                | if (T = 1) then PC           | ~      | PC + k + 1  | None        | 1/2                  |

| BRTC      | k        | Branch if T Flag Cleared            | if (T = 0) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRVS      | k        | Branch if Overflow Flag is Set      | if (V = 1) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRVC      | k        | Branch if Overflow Flag is Cleared  | if (V = 0) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRIE      | k        | Branch if Interrupt Enabled         | if (I = 1) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

| BRID      | k        | Branch if Interrupt Disabled        | if (I = 0) then PC           | ←      | PC + k + 1  | None        | 1/2                  |

|           |          | Data Tr                             | ansfer Instructions          |        |             |             |                      |

| MOV       | Rd, Rr   | Copy Register                       | Rd                           | ←      | Rr          | None        | 1                    |

| MOVW      | Rd, Rr   | Copy Register Pair                  | Rd+1:Rd                      | ←      | Rr+1:Rr     | None        | 1                    |

| Mnemonics | Operands | Description                                  | Operation             |                                                                                     |                         | Flags     | #Clocks          |

|-----------|----------|----------------------------------------------|-----------------------|-------------------------------------------------------------------------------------|-------------------------|-----------|------------------|

| SPM       | Z+       | Store Program Memory and Post-Increment by 2 | (RAMPZ:Z)<br>Z        | ←<br>←                                                                              | R1:R0,<br>Z + 2         | None      | -                |

| IN        | Rd, A    | In From I/O Location                         | Rd                    | ~                                                                                   | I/O(A)                  | None      | 1                |

| OUT       | A, Rr    | Out To I/O Location                          | I/O(A)                | ←                                                                                   | Rr                      | None      | 1                |

| PUSH      | Rr       | Push Register on Stack                       | STACK                 | ~                                                                                   | Rr                      | None      | 1 <sup>(1)</sup> |

| POP       | Rd       | Pop Register from Stack                      | Rd                    | ~                                                                                   | STACK                   | None      | 2(1)             |

|           | 1        | Bit and                                      | Bit-test Instructions |                                                                                     |                         |           |                  |

| LSL       | Rd       | Logical Shift Left                           | Rd(n+1)<br>Rd(0)<br>C | ↓<br>↓<br>↓                                                                         | Rd(n),<br>0,<br>Rd(7)   | Z,C,N,V,H | 1                |

| LSR       | Rd       | Logical Shift Right                          | Rd(n)<br>Rd(7)<br>C   | $\begin{array}{c} \downarrow \\ \downarrow \\ \downarrow \\ \downarrow \end{array}$ | Rd(n+1),<br>0,<br>Rd(0) | Z,C,N,V   | 1                |

| ROL       | Rd       | Rotate Left Through Carry                    | Rd(0)<br>Rd(n+1)<br>C | ↓ ↓<br>↓ ↓                                                                          | C,<br>Rd(n),<br>Rd(7)   | Z,C,N,V,H | 1                |

| ROR       | Rd       | Rotate Right Through Carry                   | Rd(7)<br>Rd(n)<br>C   | $\downarrow \uparrow \uparrow$                                                      | C,<br>Rd(n+1),<br>Rd(0) | Z,C,N,V   | 1                |

| ASR       | Rd       | Arithmetic Shift Right                       | Rd(n)                 | ~                                                                                   | Rd(n+1), n=06           | Z,C,N,V   | 1                |

| SWAP      | Rd       | Swap Nibbles                                 | Rd(30)                | $\leftrightarrow$                                                                   | Rd(74)                  | None      | 1                |

| BSET      | s        | Flag Set                                     | SREG(s)               | ~                                                                                   | 1                       | SREG(s)   | 1                |

| BCLR      | S        | Flag Clear                                   | SREG(s)               | ~                                                                                   | 0                       | SREG(s)   | 1                |

| SBI       | A, b     | Set Bit in I/O Register                      | I/O(A, b)             | ~                                                                                   | 1                       | None      | 1                |

| CBI       | A, b     | Clear Bit in I/O Register                    | I/O(A, b)             | ~                                                                                   | 0                       | None      | 1                |

| BST       | Rr, b    | Bit Store from Register to T                 | Т                     | ←                                                                                   | Rr(b)                   | Т         | 1                |

| BLD       | Rd, b    | Bit load from T to Register                  | Rd(b)                 | ~                                                                                   | т                       | None      | 1                |

| SEC       |          | Set Carry                                    | С                     | ←                                                                                   | 1                       | С         | 1                |

| CLC       |          | Clear Carry                                  | С                     | ~                                                                                   | 0                       | С         | 1                |

| SEN       |          | Set Negative Flag                            | N                     | ←                                                                                   | 1                       | N         | 1                |

| CLN       |          | Clear Negative Flag                          | N                     | ←                                                                                   | 0                       | N         | 1                |

| SEZ       |          | Set Zero Flag                                | Z                     | ~                                                                                   | 1                       | Z         | 1                |

| CLZ       |          | Clear Zero Flag                              | Z                     | ~                                                                                   | 0                       | Z         | 1                |

| SEI       |          | Global Interrupt Enable                      | I                     | ~                                                                                   | 1                       | I         | 1                |

| CLI       |          | Global Interrupt Disable                     | I                     | ~                                                                                   | 0                       | I         | 1                |

| SES       |          | Set Signed Test Flag                         | S                     | ←                                                                                   | 1                       | S         | 1                |

| CLS       |          | Clear Signed Test Flag                       | S                     | ←                                                                                   | 0                       | S         | 1                |

| SEV       |          | Set Two's Complement Overflow                | V                     | ~                                                                                   | 1                       | V         | 1                |

| CLV       |          | Clear Two's Complement Overflow              | V                     | ~                                                                                   | 0                       | V         | 1                |

| SET       |          | Set T in SREG                                | Т                     | ←                                                                                   | 1                       | Т         | 1                |

| CLT       |          | Clear T in SREG                              | т                     | ~                                                                                   | 0                       | т         | 1                |

| SEH       |          | Set Half Carry Flag in SREG                  | Н                     | ←                                                                                   | 1                       | н         | 1                |

| CLH       |          | Clear Half Carry Flag in SREG                | н                     | ←                                                                                   | 0                       | Н         | 1                |

| Mnemonics                | Operands | Description    | Operation                       | Flags | #Clocks |  |  |

|--------------------------|----------|----------------|---------------------------------|-------|---------|--|--|

| MCU Control Instructions |          |                |                                 |       |         |  |  |

| BREAK                    |          | Break          | (See specific descr. for BREAK) | None  | 1       |  |  |

| NOP                      |          | No Operation   |                                 | None  | 1       |  |  |

| SLEEP                    |          | Sleep          | (see specific descr. for Sleep) | None  | 1       |  |  |

| WDR                      |          | Watchdog Reset | (see specific descr. for WDR)   | None  | 1       |  |  |

Notes:

: 1. Cycle times for Data memory accesses assume internal memory accesses, and are not valid for accesses via the external RAM interface.

2. One extra cycle must be added when accessing Internal SRAM.

# 33. Packaging information

# 34.6 DAC Characteristics

| Symbol           | Parameter                  | Condition                  |                        | Min  | Тур                    | Max                   | Units |

|------------------|----------------------------|----------------------------|------------------------|------|------------------------|-----------------------|-------|

| INL              | Integral Non-Linearity     | V <sub>CC</sub> = 1.6-3.6V | VREF = Ext. ref        |      | 5                      |                       | LSB   |

| DNL              | Differential Neg Linearity | V - 1626V                  | VREF = Ext. ref        |      | 0.6                    | <±1                   | LSB   |

| DINL             | Differential Non-Linearity | V <sub>CC</sub> = 1.6-3.6V | VREF= AV <sub>CC</sub> |      | 0.6                    |                       |       |

| F <sub>clk</sub> | Conversion rate            |                            | I                      |      |                        | 1000                  | ksps  |

| AREF             | External reference voltage |                            |                        | 1.1  |                        | AV <sub>CC</sub> -0.6 | V     |

|                  | Reference input impedance  |                            |                        |      | >10                    |                       | MΩ    |

|                  | Max output voltage         | $R_{load}$ =100k $\Omega$  |                        |      | AV <sub>CC</sub> *0.98 |                       | V     |

|                  | Min output voltage         | $R_{load}$ =100k $\Omega$  |                        | 0.01 |                        | V                     |       |

## 34.7 Analog Comparator Characteristics

| Table 34-8. | Analog C | omparator | characteristics. |

|-------------|----------|-----------|------------------|

|-------------|----------|-----------|------------------|

| Symbol             | Parameter             | Condition                       | Condition |        | Тур | Max | Units |

|--------------------|-----------------------|---------------------------------|-----------|--------|-----|-----|-------|

| V <sub>off</sub>   | Input Offset Voltage  | V <sub>CC</sub> = 1.6 - 3.6V    |           |        | <±5 |     | mV    |

| l <sub>ik</sub>    | Input Leakage Current | V <sub>CC</sub> = 1.6 - 3.6V    |           | < 1000 |     | pА  |       |

| V <sub>hys1</sub>  | Hysteresis, No        | V <sub>CC</sub> = 1.6 - 3.6V    |           | 0      |     | mV  |       |

| V <sub>hys2</sub>  | Hysteresis, Small     | V <sub>CC</sub> = 1.6 - 3.6V    | mode = HS |        | 25  |     | mV    |

| V <sub>hys3</sub>  | Hysteresis, Large     | V <sub>CC</sub> = 1.6 - 3.6V    | mode = HS |        | 50  |     | mV    |

|                    |                       | V <sub>CC</sub> = 3.0V, T= 85°C | mode = HS |        |     | 100 |       |

| t <sub>delay</sub> | Propagation delay     | V <sub>CC</sub> = 1.6 - 3.6V    | mode = HS |        | 70  |     | ns    |

|                    |                       | V <sub>CC</sub> = 1.6 - 3.6V    | mode = LP |        | 140 |     |       |

## 34.8 Bandgap Characteristics

#### Table 34-9. Bandgap voltage characteristics.

| Symbol | Parameter            | Condition                   | Min               | Тур | Max | Units |

|--------|----------------------|-----------------------------|-------------------|-----|-----|-------|

|        | Bandgap startup time | As reference for ADC or DAC | 1 Clk_PER + 2.5µs |     |     | μs    |

|        | Bandgap voltage      |                             |                   | 1.1 |     | V     |

# 35.5 Pin Pull-up

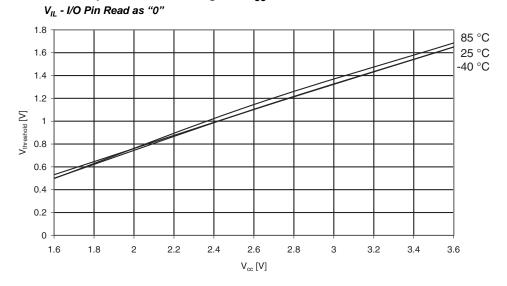

Figure 35-11.I/O Pin Input Threshold Voltage vs.  $\rm V_{\rm CC}$

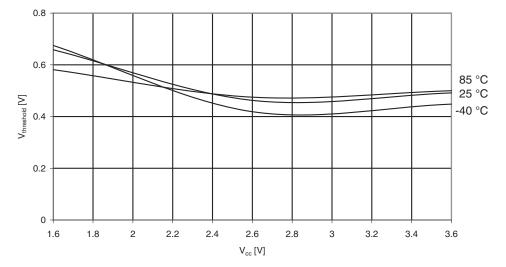

Figure 35-12.I/O Pin Input Hysteresis vs. V<sub>CC.</sub>

- TWI START condition at bus timeout will cause transaction to be dropped

- TWI Data Interrupt Flag erroneously read as set

- WDR instruction inside closed window will not issue reset

#### 1. Bandgap voltage input for the ACs cannot be changed when used for both ACs simultaneously

If the Bandgap voltage is selected as input for one Analog Comparator (AC) and then selected/deselected as input for another AC, the first comparator will be affected for up to 1  $\mu$ s and could potentially give a wrong comparison result.

#### Problem fix/Workaround

If the Bandgap is required for both ACs simultaneously, configure the input selection for both ACs before enabling any of them.

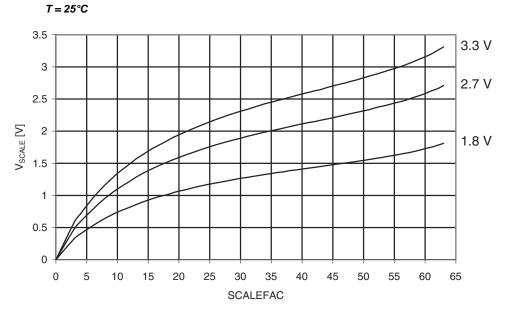

#### 2. VCC voltage scaler for AC is non-linear

The 6-bit VCC voltage scaler in the Analog Comparators is non-linear.

#### Figure 36-1. Analog Comparator Voltage Scaler vs. Scalefac

#### Problem fix/Workaround

Use external voltage input for the analog comparator if accurate voltage levels are needed

#### 3. The ADC has up to ±2 LSB inaccuracy

The ADC will have up to  $\pm 2$  LSB inaccuracy, visible as a saw-tooth pattern on the input voltage/ output value transfer function of the ADC. The inaccuracy increases with increasing voltage reference reaching  $\pm 2$  LSB with 3V reference.

#### 32. Accessing EBI address space with PREBI set will lock Bus Master

If EBI Power Reduction Bit is set while EBI is enabled, accessing external memory could result in bus hang-up, blocking all further access to all data memory.

#### Problem fix/Workaround

Ensure that EBI is disabled before setting EBI Power Reduction bit.

#### 33. RTC Counter value not correctly read after sleep

If the RTC is set to wake up the device on RTC Overflow and bit 0 of RTC CNT is identical to bit 0 of RTC PER as the device is entering sleep, the value in the RTC count register can not be read correctly within the first prescaled RTC clock cycle after wakeup. The value read will be the same as the value in the register when entering sleep.

The same applies if RTC Compare Match is used as wake-up source.

#### Problem fix/Workaround

Wait at least one prescaled RTC clock cycle before reading the RTC CNT value.

#### 34. Pending asynchronous RTC-interrupts will not wake up device

Asynchronous Interrupts from the Real-Time-Counter that is pending when the sleep instruction is executed, will be ignored until the device is woken from another source or the source triggers again.

#### Problem fix/Workaround

None.

#### 35. TWI, the minimum I<sup>2</sup>C SCL low time could be violated in Master Read mode

If the TWI is in Master Read mode and issues a Repeated Start on the bus, this will immediately release the SCL line even if one complete SCL low period has not passed. This means that the minimum SCL low time in the I2C specification could be violated.

#### Problem fix/Workaround

If this is a problem in the application, ensure in software that the Repeated Start is never issued before one SCL low time has passed.

#### 36. TWI address-mask feature is non-functional

The address-mask feature is non-functional, so the TWI can not perform hardware address match on more than one address.

#### Problem fix/Workaround

If the TWI must respond to multiple addresses, enable Promiscuous Mode for the TWI to respond to all address and implement the address-mask function in software.

# 36.2 ATxmega64A1 and ATxmega128A1 rev. G

- Bootloader Section in Flash is non-functional

- Bandgap voltage input for the ACs cannot be changed when used for both ACs simultaneously

- DAC is nonlinear and inaccurate when reference is above 2.4V

- ADC gain stage output range is limited to 2.4 V

- The ADC has up to ±2 LSB inaccuracy

- TWI, a general address call will match independent of the R/W-bit value

- TWI, the minimum I<sup>2</sup>C SCL low time could be violated in Master Read mode

- Setting HIRES PR bit makes PWM output unavailable

- EEPROM erase and write does not work with all System Clock sources

- BOD will be enabled after any reset

- Propagation delay analog Comparator increasing to 2 ms at -40°C

- Sampled BOD in Active mode will cause noise when bandgap is used as reference

- Default setting for SDRAM refresh period too low

- Flash Power Reduction Mode can not be enabled when entering sleep mode

- Enabling Analog Comparator B output will cause JTAG failure

- JTAG enable does not override Analog Comparator B output

- Bandgap measurement with the ADC is non-functional when V<sub>CC</sub> is below 2.7V

- DAC refresh may be blocked in S/H mode

- Inverted I/O enable does not affect Analog Comparator Output

- Both DFLLs and both oscillators has to be enabled for one to work

#### 1. Bootloader Section in Flash is non-functional

The Bootloader Section is non-functional, and bootloader or application code cannot reside in this part of the Flash.

#### Problem fix/Workaround

None, do not use the Bootloader Section.

#### 2. Bandgap voltage input for the ACs cannot be changed when used for both ACs simultaneously

If the Bandgap voltage is selected as input for one Analog Comparator (AC) and then selected/deselected as input for the another AC, the first comparator will be affected for up to 1 us and could potentially give a wrong comparison result.

#### Problem fix/Workaround

If the Bandgap is required for both ACs simultaneously, configure the input selection for both ACs before enabling any of them.

#### 3. DAC is nonlinear and inaccurate when reference is above 2.4V

Using the DAC with a reference voltage above 2.4V give inaccurate output when converting codes that give below 0.75V output:

• ±20 LSB for continuous mode