Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Active                                                     |

| Core Processor             | AVR                                                        |

| Core Size                  | 8/16-Bit                                                   |

| Speed                      | 32MHz                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                 |

| Number of I/O              | 78                                                         |

| Program Memory Size        | 64KB (32K x 16)                                            |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | 2K x 8                                                     |

| RAM Size                   | 4K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                |

| Data Converters            | A/D 16x12b; D/A 4x12b                                      |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                          |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 100-VFBGA                                                  |

| Supplier Device Package    | 100-VFBGA (7x7)                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/atxmega64a1-cur |

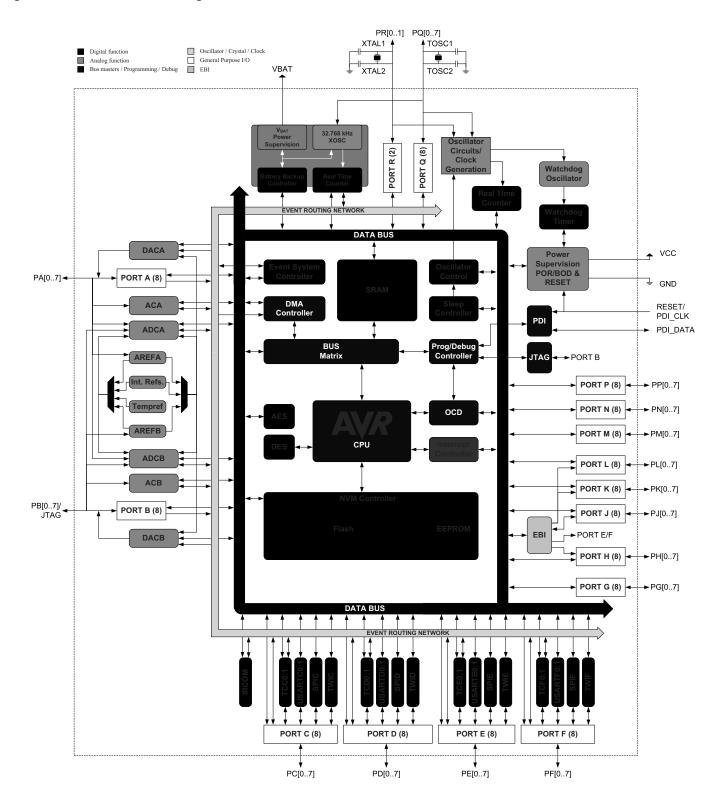

## 3.1 Block Diagram

Figure 3-1. XMEGA A1 Block Diagram

## 4. Resources

A comprehensive set of development tools, application notes and datasheets are available for download on http://www.atmel.com/avr.

## 4.1 Recommended reading

- XMEGA A Manual

- XMEGA A Application Notes

This device data sheet only contains part specific information and a short description of each peripheral and module. The XMEGA A Manual describes the modules and peripherals in depth. The XMEGA A application notes contain example code and show applied use of the modules and peripherals.

The XMEGA A Manual and Application Notes are available from http://www.atmel.com/avr.

# 5. Capacitive touch sensing

The Atmel QTouch library provides a simple to use solution to realize touch sensitive interfaces on most Atmel AVR microcontrollers. The patented charge-transfer signal acquisition offers robust sensing and includes fully debounced reporting of touch keys and includes Adjacent Key Suppression® (AKS®) technology for unambiguous detection of key events. The QTouch library includes support for the QTouch and QMatrix acquisition methods.

Touch sensing can be added to any application by linking the appropriate Atmel QTouch library for the AVR microcontroller. This is done by using a simple set of APIs to define the touch channels and sensors, and then calling the touch sensing API's to retrieve the channel information and determine the touch sensor states.

The QTouch library is FREE and downloadable from the Atmel website at the following location: www.atmel.com/qtouchlibrary. For implementation details and other information, refer to the QTouch library user guide - also available for download from the Atmel website.

## 6. Disclaimer

For devices that are not available yet, typical values contained in this datasheet are based on simulations and characterization of other AVR XMEGA microcontrollers manufactured on the same process technology. Min. and Max values will be available after the device is characterized.

Table 8-3. Number of Bytes and Pages in the EEPROM.

| Device       | EEPROM | Page Size | E2BYTE    | E2PAGE     | No of pages |

|--------------|--------|-----------|-----------|------------|-------------|

|              | Size   | bytes     |           |            |             |

| ATxmega64A1  | 2 KB   | 32        | ADDR[4:0] | ADDR[10:5] | 64          |

| ATxmega128A1 | 2 KB   | 32        | ADDR[4:0  | ADDR[10:5] | 64          |

#### 8.14.1 I/O Memory

All peripherals and modules are addressable through I/O memory locations in the data memory space. All I/O memory locations can be accessed by the Load (LD/LDS/LDD) and Store (ST/STS/STD) instructions, transferring data between the 32 general purpose registers in the CPU and the I/O Memory.

The IN and OUT instructions can address I/O memory locations in the range 0x00 - 0x3F directly.

I/O registers within the address range 0x00 - 0x1F are directly bit-accessible using the SBI and CBI instructions. The value of single bits can be checked by using the SBIS and SBIC instructions on these registers.

The I/O memory address for all peripherals and modules in XMEGA A1 is shown in the "Peripheral Module Address Map" on page 62.

#### 12.3.3 Power-save Mode

Power-save mode is identical to power down, with one exception. If the real-time counter (RTC) is enabled, it will keep running during sleep, and the device can also wake up from either an RTC overflow or compare match interrupt.

#### 12.3.4 Standby Mode

Standby mode is identical to power down, with the exception that the enabled system clock sources are kept running while the CPU, peripheral, and RTC clocks are stopped. This reduces the wake-up time.

## 12.3.5 Extended Standby Mode

Extended standby mode is identical to power-save mode, with the exception that the enabled system clock sources are kept running while the CPU and peripheral clocks are stopped. This reduces the wake-up time.

#### 13.4.2 Brownout Detection

The on-chip brownout detection (BOD) circuit monitors the  $V_{CC}$  level during operation by comparing it to a fixed, programmable level that is selected by the BODLEVEL fuses. If disabled, BOD is forced on at the lowest level during chip erase and when the PDI is enabled.

#### 13.4.3 External Reset

The external reset circuit is connected to the external  $\overline{RESET}$  pin. The external reset will trigger when the RESET pin is driven below the  $\overline{RESET}$  pin threshold voltage,  $V_{RST}$ , for longer than the minimum pulse period,  $t_{EXT}$ . The reset will be held as long as the pin is kept low. The  $\overline{RESET}$  pin includes an internal pull-up resistor.

#### 13.4.4 Watchdog Reset

The watchdog timer (WDT) is a system function for monitoring correct program operation. If the WDT is not reset from the software within a programmable timeout period, a watchdog reset will be given. The watchdog reset is active for one to two clock cycles of the 2MHz internal oscillator. For more details see "WDT - Watchdog Timer" on page 28.

#### 13.4.5 Software reset

The software reset makes it possible to issue a system reset from software by writing to the software reset bit in the reset control register. The reset will be issued within two CPU clock cycles after writing the bit. It is not possible to execute any instruction from when a software reset is requested until it is issued.

#### 13.4.6 Program and Debug Interface Reset

The program and debug interface reset contains a separate reset source that is used to reset the device during external programming and debugging. This reset source is accessible only from external debuggers and programmers.

## 13.5 WDT - Watchdog Timer

#### 13.5.1 Features

- Issues a device reset if the timer is not reset before its timeout period

- · Asynchronous operation from dedicated oscillator

- 1kHz output of the 32kHz ultra low power oscillator

- 11 selectable timeout periods, from 8ms to 8s

- Two operation modes:

- Normal mode

- Window mode

- Configuration lock to prevent unwanted changes

#### 13.6 Overview

The watchdog timer (WDT) is a system function for monitoring correct program operation. It makes it possible to recover from error situations such as runaway or deadlocked code. The WDT is a timer, configured to a predefined timeout period, and is constantly running when enabled. If the WDT is not reset within the timeout period, it will issue a microcontroller reset. The WDT is reset by executing the WDR (watchdog timer reset) instruction from the application code.

The window mode makes it possible to define a time slot or window inside the total timeout period during which WDT must be reset. If the WDT is reset outside this window, either too early or too late, a system reset will be issued. Compared to the normal mode, this can also catch situations where a code error causes constant WDR execution.

The WDT will run in active mode and all sleep modes, if enabled. It is asynchronous, runs from a CPU-independent clock source, and will continue to operate to issue a system reset even if the main clocks fail.

The configuration change protection mechanism ensures that the WDT settings cannot be changed by accident. For increased safety, a fuse for locking the WDT settings is also available.

## 21. SPI - Serial Peripheral Interface

## 21.1 Features

- Four identical SPI peripherals

- Full-duplex, three-wire synchronous data transfer

- Master or slave operation

- · Lsb first or msb first data transfer

- Eight programmable bit rates

- Interrupt flag at the end of transmission

- Write collision flag to indicate data collision

- Wake up from idle sleep mode

- Double speed master mode

## 21.2 Overview

The Serial Peripheral Interface (SPI) is a high-speed synchronous data transfer interface using three or four pins. It allows fast communication between an Atmel AVR XMEGA device and peripheral devices or between several microcontrollers. The SPI supports full-duplex communication.

A device connected to the bus must act as a master or slave. The master initiates and controls all data transactions. PORTC, PORTD, PORTE, and PORTF each has one SPI. Notation of these peripherals are SPIC, SPID, SPIE, and SPIF.

| PORT C | PIN# | INTERRUPT | TCC0 | AWEXC  | TCC1 | USARTC0 | USARTC1 | SPIC | TWIC | CLOCKOUT | EVENTOUT |

|--------|------|-----------|------|--------|------|---------|---------|------|------|----------|----------|

| РС3    | 18   | SYNC      | OC0D | OC0BHS |      | TXD0    |         |      |      |          |          |

| PC4    | 19   | SYNC      |      | OC0CLS | OC1A |         |         | SS   |      |          |          |

| PC5    | 20   | SYNC      |      | OC0CHS | OC1B |         | XCK1    | MOSI |      |          |          |

| PC6    | 21   | SYNC      |      | OC0DLS |      |         | RXD1    | MISO |      |          |          |

| PC7    | 22   | SYNC      |      | OC0DHS |      |         | TXD1    | SCK  |      | CLKOUT   | EVOUT    |

#### Table 30-4. Port D - Alternate functions.

| PORT D | PIN# | INTERRUPT  | TCD0 | TCD1 | USARTD0 | USARTD1 | SPID | TWID | CLOCKOUT | EVENTOUT |

|--------|------|------------|------|------|---------|---------|------|------|----------|----------|

| GND    | 23   |            |      |      |         |         |      |      |          |          |

| vcc    | 24   |            |      |      |         |         |      |      |          |          |

| PD0    | 25   | SYNC       | OC0A |      |         |         |      | SDA  |          |          |

| PD1    | 26   | SYNC       | OC0B |      | XCK0    |         |      | SCL  |          |          |

| PD2    | 27   | SYNC/ASYNC | OC0C |      | RXD0    |         |      |      |          |          |

| PD3    | 28   | SYNC       | OC0D |      | TXD0    |         |      |      |          |          |

| PD4    | 29   | SYNC       |      | OC1A |         |         | SS   |      |          |          |

| PD5    | 30   | SYNC       |      | OC1B |         | XCK1    | MOSI |      |          |          |

| PD6    | 31   | SYNC       |      |      |         | RXD1    | MISO |      |          |          |

| PD7    | 32   | SYNC       |      |      |         | TXD1    | SCK  |      | CLKOUT   | EVOUT    |

## Table 30-5. Port E - Alternate functions.

| PORT E | PIN# | INTERRUPT  | TCE0 | AWEXE  | TCE1 | USARTE0 | USARTE1 | SPIE | TWIE | CLOCKOUT | EVENTOUT |

|--------|------|------------|------|--------|------|---------|---------|------|------|----------|----------|

| GND    | 33   |            |      |        |      |         |         |      |      |          |          |

| vcc    | 34   |            |      |        |      |         |         |      |      |          |          |

| PE0    | 35   | SYNC       | OC0A | OC0ALS |      |         |         |      | SDA  |          |          |

| PE1    | 36   | SYNC       | OC0B | OC0AHS |      | XCK0    |         |      | SCL  |          |          |

| PE2    | 37   | SYNC/ASYNC | OC0C | OC0BLS |      | RXD0    |         |      |      |          |          |

| PE3    | 38   | SYNC       | OC0D | OC0BHS |      | TXD0    |         |      |      |          |          |

| PE4    | 39   | SYNC       |      | OC0CLS | OC1A |         |         | SS   |      |          |          |

| PE5    | 40   | SYNC       |      | OC0CHS | OC1B |         | XCK1    | MOSI |      |          |          |

| PE6    | 41   | SYNC       |      | OC0DLS | _    |         | RXD1    | MISO |      |          |          |

| PE7    | 42   | SYNC       |      | OC0DHS |      |         | TXD1    | SCK  |      | CLKOUT   | EVOUT    |

#### Table 30-6. Port F - Alternate functions.

| PORT F | PIN# | INTERRUPT | TCF0 | TCF1 | USARTF0 | USARTF1 | SPIF | TWIF |

|--------|------|-----------|------|------|---------|---------|------|------|

| GND    | 43   |           |      |      |         |         |      |      |

| vcc    | 44   |           |      |      |         |         |      |      |

| PF0    | 45   | SYNC      | OC0A |      |         |         |      | SDA  |

| Mnemonics | Operands | Description                                         | Operation                                  |            |                     | Flags | #Clocks             |

|-----------|----------|-----------------------------------------------------|--------------------------------------------|------------|---------------------|-------|---------------------|

| LDI       | Rd, K    | Load Immediate                                      | Rd                                         | <b>←</b>   | К                   | None  | 1                   |

| LDS       | Rd, k    | Load Direct from data space                         | Rd                                         | <b>←</b>   | (k)                 | None  | 2 <sup>(1)(2)</sup> |

| LD        | Rd, X    | Load Indirect                                       | Rd                                         | <b>←</b>   | (X)                 | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, X+   | Load Indirect and Post-Increment                    | Rd<br>X                                    | <b>← ←</b> | (X)<br>X + 1        | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, -X   | Load Indirect and Pre-Decrement                     | $X \leftarrow X - 1$ , $Rd \leftarrow (X)$ | <b>←</b>   | X - 1<br>(X)        | None  | 2 <sup>(1)(2)</sup> |

| LD        | Rd, Y    | Load Indirect                                       | $Rd \leftarrow (Y)$                        | <b>←</b>   | (Y)                 | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, Y+   | Load Indirect and Post-Increment                    | Rd<br>Y                                    | <b>←</b>   | (Y)<br>Y + 1        | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, -Y   | Load Indirect and Pre-Decrement                     | Y<br>Rd                                    | <b>←</b>   | Y - 1<br>(Y)        | None  | 2 <sup>(1)(2)</sup> |

| LDD       | Rd, Y+q  | Load Indirect with Displacement                     | Rd                                         | <b>←</b>   | (Y + q)             | None  | 2 <sup>(1)(2)</sup> |

| LD        | Rd, Z    | Load Indirect                                       | Rd                                         | <b>←</b>   | (Z)                 | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, Z+   | Load Indirect and Post-Increment                    | Rd<br>Z                                    | <b>←</b>   | (Z),<br>Z+1         | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, -Z   | Load Indirect and Pre-Decrement                     | Z<br>Rd                                    | <b>← ←</b> | Z - 1,<br>(Z)       | None  | 2 <sup>(1)(2)</sup> |

| LDD       | Rd, Z+q  | Load Indirect with Displacement                     | Rd                                         | <b>←</b>   | (Z + q)             | None  | 2 <sup>(1)(2)</sup> |

| STS       | k, Rr    | Store Direct to Data Space                          | (k)                                        | <b>←</b>   | Rd                  | None  | 2 <sup>(1)</sup>    |

| ST        | X, Rr    | Store Indirect                                      | (X)                                        | <b>←</b>   | Rr                  | None  | 1 <sup>(1)</sup>    |

| ST        | X+, Rr   | Store Indirect and Post-Increment                   | (X)<br>X                                   | <b>←</b>   | Rr,<br>X + 1        | None  | 1 <sup>(1)</sup>    |

| ST        | -X, Rr   | Store Indirect and Pre-Decrement                    | X<br>(X)                                   | <b>← ←</b> | X - 1,<br>Rr        | None  | 2 <sup>(1)</sup>    |

| ST        | Y, Rr    | Store Indirect                                      | (Y)                                        | <b>←</b>   | Rr                  | None  | 1 <sup>(1)</sup>    |

| ST        | Y+, Rr   | Store Indirect and Post-Increment                   | (Y)<br>Y                                   | <b>←</b>   | Rr,<br>Y + 1        | None  | 1 <sup>(1)</sup>    |

| ST        | -Y, Rr   | Store Indirect and Pre-Decrement                    | Y<br>(Y)                                   | <b>←</b>   | Y - 1,<br>Rr        | None  | 2 <sup>(1)</sup>    |

| STD       | Y+q, Rr  | Store Indirect with Displacement                    | (Y + q)                                    | <b>←</b>   | Rr                  | None  | 2 <sup>(1)</sup>    |

| ST        | Z, Rr    | Store Indirect                                      | (Z)                                        | <b>←</b>   | Rr                  | None  | 1 <sup>(1)</sup>    |

| ST        | Z+, Rr   | Store Indirect and Post-Increment                   | (Z)<br>Z                                   | <b>←</b>   | Rr<br>Z + 1         | None  | 1 <sup>(1)</sup>    |

| ST        | -Z, Rr   | Store Indirect and Pre-Decrement                    | Z                                          | <b>←</b>   | Z - 1               | None  | 2 <sup>(1)</sup>    |

| STD       | Z+q,Rr   | Store Indirect with Displacement                    | (Z + q)                                    | <b>←</b>   | Rr                  | None  | 2 <sup>(1)</sup>    |

| LPM       |          | Load Program Memory                                 | R0                                         | <b>←</b>   | (Z)                 | None  | 3                   |

| LPM       | Rd, Z    | Load Program Memory                                 | Rd                                         | <b>←</b>   | (Z)                 | None  | 3                   |

| LPM       | Rd, Z+   | Load Program Memory and Post-Increment              | Rd<br>Z                                    | <b>←</b>   | (Z),<br>Z + 1       | None  | 3                   |

| ELPM      |          | Extended Load Program Memory                        | R0                                         | <b>←</b>   | (RAMPZ:Z)           | None  | 3                   |

| ELPM      | Rd, Z    | Extended Load Program Memory                        | Rd                                         | <b>←</b>   | (RAMPZ:Z)           | None  | 3                   |

| ELPM      | Rd, Z+   | Extended Load Program Memory and Post-<br>Increment | Rd<br>Z                                    | <b>← ←</b> | (RAMPZ:Z),<br>Z + 1 | None  | 3                   |

| SPM       |          | Store Program Memory                                | (RAMPZ:Z)                                  | <b>←</b>   | R1:R0               | None  | -                   |

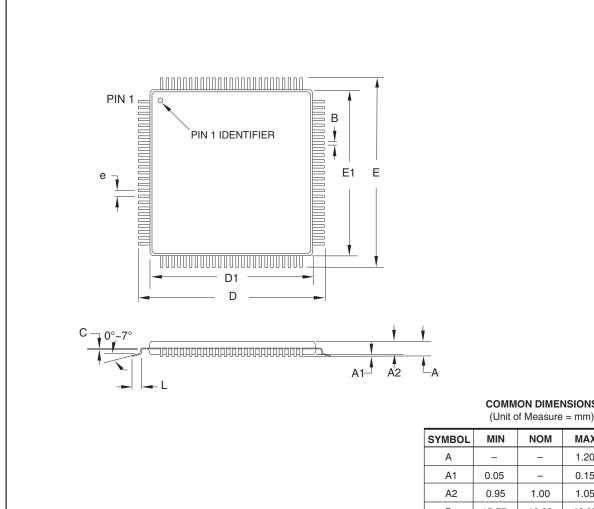

#### **Packaging information** 33.

#### 33.1 100A

- 1. This package conforms to JEDEC reference MS-026, Variation AED.

- 2. Dimensions D1 and E1 do not include mold protrusion. Allowable protrusion is 0.25 mm per side. Dimensions D1 and E1 are maximum plastic body size dimensions including mold mismatch.

- 3. Lead coplanarity is 0.08 mm maximum.

| COMMON      | DIMENSIONS |

|-------------|------------|

| /Linit of M | occure mm) |

| SYMBOL | MIN   | NOM      | MAX   | NOTE   |

|--------|-------|----------|-------|--------|

| А      | _     | _        | 1.20  |        |

| A1     | 0.05  | _        | 0.15  |        |

| A2     | 0.95  | 1.00     | 1.05  |        |

| D      | 15.75 | 16.00    | 16.25 |        |

| D1     | 13.90 | 14.00    | 14.10 | Note 2 |

| Е      | 15.75 | 16.00    | 16.25 |        |

| E1     | 13.90 | 14.00    | 14.10 | Note 2 |

| В      | 0.17  | _        | 0.27  |        |

| С      | 0.09  | _        | 0.20  |        |

| L      | 0.45  | _        | 0.75  |        |

| е      |       | 0.50 TYP |       |        |

2010-10-20

| 0005 0 1 1 1 1 1 1                         | TITLE                                                                                                                                 | DRAWING NO. | REV. |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------|------|

| 2325 Orchard Parkway<br>San Jose, CA 95131 | <b>100A</b> , 100-lead, 14 x 14 mm Body Size, 1.0 mm Body Thickness, 0.5 mm Lead Pitch, Thin Profile Plastic Quad Flat Package (TQFP) | 100A        | D    |

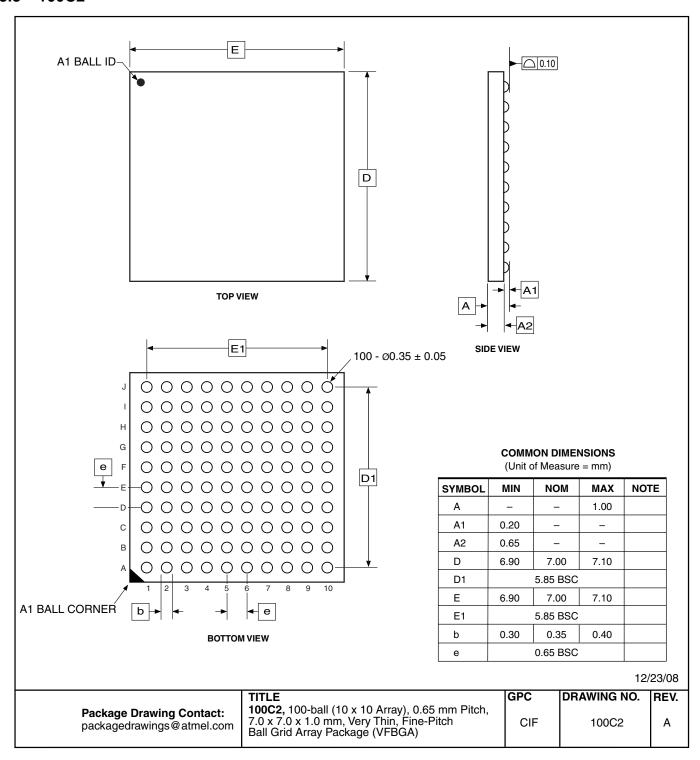

## 33.3 100C2

## **34.3 Speed**

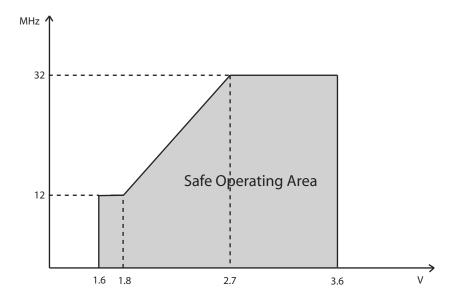

Table 34-2. Operating voltage and frequency.

| Symbol             | Parameter           | Condition              | Min | Тур | Max | Units |  |

|--------------------|---------------------|------------------------|-----|-----|-----|-------|--|

| Clk <sub>CPU</sub> | CPU clock frequency | V <sub>CC</sub> = 1.6V | 0   |     | 12  |       |  |

|                    |                     | V <sub>CC</sub> = 1.8V | 0   |     | 12  | MHz   |  |

|                    |                     | V <sub>CC</sub> = 2.7V | 0   |     | 32  |       |  |

|                    |                     | V <sub>CC</sub> = 3.6V | 0   |     | 32  |       |  |

The maximum CPU clock frequency of the XMEGA A1 devices is depending on  $V_{CC}$ . As shown in Figure 34-1 on page 75 the Frequency vs.  $V_{CC}$  curve is linear between 1.8V <  $V_{CC}$  < 2.7V.

Figure 34-1. Maximum Frequency vs. Vcc

## 34.6 DAC Characteristics

Table 34-7. DAC characteristics.

| Symbol           | Parameter                  | Condition                  |                        | Min | Тур                    | Max                   | Units |

|------------------|----------------------------|----------------------------|------------------------|-----|------------------------|-----------------------|-------|

| INL              | Integral Non-Linearity     | V <sub>CC</sub> = 1.6-3.6V | VREF = Ext. ref        |     | 5                      |                       | LSB   |

| DNL              | Differential Non-Linearity | V <sub>CC</sub> = 1.6-3.6V | VREF = Ext. ref        |     | 0.6                    | <±1                   | LSB   |

| DINL             | Differential Non-Linearity | V <sub>CC</sub> = 1.0-3.6V | VREF= AV <sub>CC</sub> |     | 0.6                    |                       | LOD   |

| F <sub>clk</sub> | Conversion rate            |                            |                        |     |                        | 1000                  | ksps  |

| AREF             | External reference voltage |                            |                        | 1.1 |                        | AV <sub>CC</sub> -0.6 | V     |

|                  | Reference input impedance  |                            |                        |     | >10                    |                       | ΜΩ    |

|                  | Max output voltage         | $R_{load}$ =100k $\Omega$  |                        |     | AV <sub>CC</sub> *0.98 |                       | V     |

|                  | Min output voltage         | R <sub>load</sub> =100kΩ   |                        |     | 0.01                   |                       | V     |

# 34.7 Analog Comparator Characteristics

Table 34-8. Analog Comparator characteristics.

| Symbol             | Parameter             | Condition                       |           | Min | Тур    | Max | Units |

|--------------------|-----------------------|---------------------------------|-----------|-----|--------|-----|-------|

| V <sub>off</sub>   | Input Offset Voltage  | V <sub>CC</sub> = 1.6 - 3.6V    |           |     | <±5    |     | mV    |

| I <sub>lk</sub>    | Input Leakage Current | V <sub>CC</sub> = 1.6 - 3.6V    |           |     | < 1000 |     | pA    |

| V <sub>hys1</sub>  | Hysteresis, No        | V <sub>CC</sub> = 1.6 - 3.6V    |           |     | 0      |     | mV    |

| V <sub>hys2</sub>  | Hysteresis, Small     | V <sub>CC</sub> = 1.6 - 3.6V    | mode = HS |     | 25     |     | mV    |

| V <sub>hys3</sub>  | Hysteresis, Large     | V <sub>CC</sub> = 1.6 - 3.6V    | mode = HS |     | 50     |     | mV    |

| t <sub>delay</sub> | Propagation delay     | V <sub>CC</sub> = 3.0V, T= 85°C | mode = HS |     |        | 100 |       |

|                    |                       | V <sub>CC</sub> = 1.6 - 3.6V    | mode = HS |     | 70     |     | ns    |

|                    |                       | V <sub>CC</sub> = 1.6 - 3.6V    | mode = LP |     | 140    |     |       |

# 34.8 Bandgap Characteristics

Table 34-9. Bandgap voltage characteristics.

| Symbol | Parameter            | Condition                   | Min               | Тур | Max | Units |

|--------|----------------------|-----------------------------|-------------------|-----|-----|-------|

|        | Bandgap startup time | As reference for ADC or DAC | 1 Clk_PER + 2.5μs |     | μs  |       |

|        | Bandgap voltage      |                             |                   | 1.1 |     | V     |

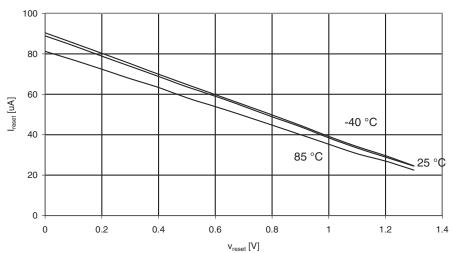

#### 35.5 Pin Pull-up

Figure 35-7. I/O Reset Pull-up Resistor Current vs. Reset Pin Voltage

$V_{CC} = 1.8V$

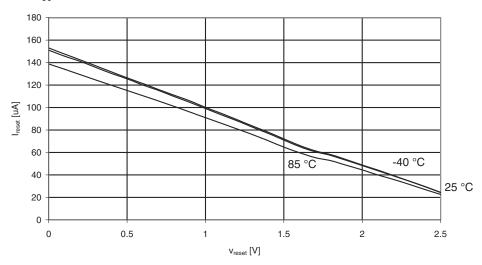

Figure 35-8. I/O Reset Pull-up Resistor Current vs. Reset Pin Voltage

$V_{CC}=3.0V$

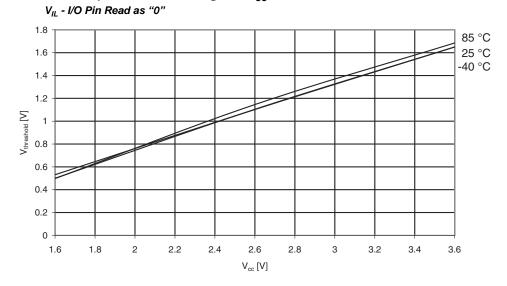

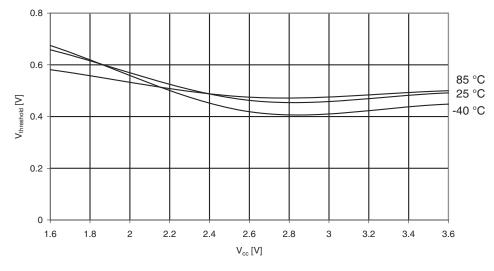

Figure 35-11.I/O Pin Input Threshold Voltage vs.  $V_{\rm CC}$

Figure 35-12.I/O Pin Input Hysteresis vs.  $V_{\rm CC.}$

#### Problem fix/Workaround

None, the actual ADC resolution will be reduced with up to ±2 LSB.

#### 4. ADC gain stage output range is limited to 2.4 V

The amplified output of the ADC gain stage will never go above 2.4 V, hence the differential input will only give correct output when below 2.4 V/gain. For the available gain settings, this gives a differential input range of:

2.4 V 1x gain: 2x gain: 1.2 V 4x gain: 0.6 V 8x gain: 300 mV 16x gain: 150 mV 32x 75 mV gain: 38 mV 64x gain:

#### Problem fix/Workaround

Keep the amplified voltage output from the ADC gain stage below 2.4 V in order to get a correct result, or keep ADC voltage reference below 2.4 V.

#### 5. Sampling speed limited to 500 ksps for supply voltage below 2.0V

The sampling frequency is limited to 500 ksps for supply voltage below 2.0V. At higher sampling rate the INL error will be several hundred LSB.

#### Problem fix/Workaround

None.

#### 6. ADC Event on compare match non-functional

ADC signalling event will be given at every conversion complete even if Interrupt mode (INTMODE) is set to BELOW or ABOVE.

#### Problem fix/Workaround

Enable and use interrupt on compare match when using the compare function.

#### 7. Bandgap measurement with the ADC is non-functional when VCC is below 2.7V

The ADC can not be used to do bandgap measurements when VCC is below 2.7V.

#### Problem fix/Workaround

None.

#### 8. Accuracy lost on first three samples after switching input to ADC gain stage

Due to memory effect in the ADC gain stage, the first three samples after changing input channel must be disregarded to achieve 12-bit accuracy.

#### Problem fix/Workaround

Run three ADC conversions and discard these results after changing input channels to ADC gain stage.

#### 9. The input difference between two succeeding ADC samples is limited by VREF

If the difference in input between two samples changes more than the size of the reference, the ADC will not be able to convert the data correctly. Two conversions will be required before the conversion is correct.

#### Problem fix/Workaround

Discard the first conversion if input is changed more than VREF, or ensure that the input never changes more then VREF.

#### 10. Increased noise when using internal 1.0V reference at low temperature

When operating at below 0°C and using internal 1.0V reference the RMS noise will be up 4 LSB, Peak-to-peak noise up to 25 LSB.

#### Problem fix/Workaround

Use averaging to remove noise.

#### 11. Configuration of PGM and CWCM not as described in XMEGA A Manual

Enabling Common Waveform Channel Mode will enable Pattern generation mode (PGM), but not Common Waveform Channel Mode.

Enabling Pattern Generation Mode (PGM) and not Common Waveform Channel Mode (CWCM) will enable both Pattern Generation Mode and Common Waveform Channel Mode.

#### Problem fix/Workaround

| PGM | СМСМ | Description           |

|-----|------|-----------------------|

| 0   | 0    | PGM and CWCM disabled |

| 0   | 1    | PGM enabled           |

| 1   | 0    | PGM and CWCM enabled  |

| 1   | 1    | PGM enabled           |

#### 12 PWM is not restarted properly after a fault in cycle-by-cycle mode

When the AWeX fault restore mode is set to cycle-by-cycle, the waveform output will not return to normal operation at first update after fault condition is no longer present.

#### Problem fix/Workaround

Do a write to any AWeX I/O register to re-enable the output.

#### 13. BOD will be enabled after any reset

If any reset source goes active, the BOD will be enabled and keep the device in reset if the VCC voltage is below the programmed BOD level. During Power-On Reset, reset will not be released until VCC is above the programmed BOD level even if the BOD is disabled.

#### Problem fix/Workaround

Do not set the BOD level higher than VCC even if the BOD is not used.

#### 14. BODACT fuse location is not correct

The fuses for enabling BOD in active mode (BODACT) are located at FUSEBYTE2, bit 2 and 3 and not in FUSEBYTE 5 as described in the XMEGA A Manual.

#### Problem fix/Workaround

Access the fuses in FUSEBYTE2.

#### 15. Sampled BOD in Active mode will cause noise when bandgap is used as reference

Using the BOD in sampled mode when the device is running in Active or Idle mode will add noise on the bandgap reference for ADC, DAC and Analog Comparator.

#### Problem fix/Workaround

If the bandgap is used as reference for either the ADC, DAC or Analog Comparator, the BOD must not be set in sampled mode.

#### 16. DAC has up to ±10 LSB noise in Sampled Mode

The DAC has noise of up to ±10 LSB in Sampled Mode for entire operation range.

#### Problem fix/Workaround

Use the DAC in continuous mode.

#### 17. DAC is nonlinear and inaccurate when reference is above 2.4V or VCC - 0.6V

Using the DAC with a reference voltage above 2.4V or VCC - 0.6V will give inaccurate output when converting codes that give below 0.75V output:

- ±10 LSB for continuous mode

- ±200 LSB for Sample and Hold mode

#### Problem fix/Workaround

None.

#### 37.9 8067G - 11/2008

- 1. Updated "Block Diagram" on page 6.

- 2. Updated feature list in "Memories" on page 12.

- 3. Updated "Programming and Debugging" on page 54.

- 4. Updated "Peripheral Module Address Map" on page 62. IRCOM has address 0x8F0.

- 5. Added "Electrical Characteristics" on page 73.

- 6. Added "Typical Characteristics" on page 82.

- 7. Added "ATxmega64A1and ATxmega128A1 rev. H" on page 96.

- 8. Updated "ATxmega64A1 and ATxmega128A1 rev. G" on page 107.

#### 37.10 8067F - 09/2008

- 1. Updated "Features" on page 1

- 2. Updated "Ordering Information" on page 2

- 3. Updated Figure 7-1 on page 11 and Figure 7-2 on page 11.

- 4. Updated Table 7-2 on page 15.

- 5. Updated "Features" on page 48 and "Overview" on page 48.

- 6. Removed "Interrupt Vector Summary" section from datasheet.

#### 37.11 8067E - 08/2008

- 1. Changed Figure 2-1's title to "Block diagram and pinout" on page 3.

- 2. Updated Figure 2-2 on page 4.

- 3. Updated Table 29-2 on page 51 and Table 29-3 on page 52.

#### 37.12 8067D - 07/2008

- 1. Updated "Ordering Information" on page 2.

- 2. Updated "Peripheral Module Address Map" on page 62.

- 3. Inserted "Interrupt Vector Summary" on page 56.