Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               |                                                                           |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 1.5KB (1K x 12)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 72 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 14-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c505-04-sl |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 GENERAL DESCRIPTION

The PIC16C505 from Microchip Technology is a lowcost, high-performance, 8-bit, fully static, EPROM/ ROM-based CMOS microcontroller. It employs a RISC architecture with only 33 single word/single cycle instructions. All instructions are single cycle (200  $\mu$ s) except for program branches, which take two cycles. The PIC16C505 delivers performance an order of magnitude higher than its competitors in the same price category. The 12-bit wide instructions are highly symmetrical resulting in a typical 2:1 code compression over other 8-bit microcontrollers in its class. The easy to use and easy to remember instruction set reduces development time significantly.

The PIC16C505 product is equipped with special features that reduce system cost and power requirements. The Power-On Reset (POR) and Device Reset Timer (DRT) eliminate the need for external reset circuitry. There are five oscillator configurations to choose from, including INTRC internal oscillator mode and the power-saving LP (Low Power) oscillator mode. Power saving SLEEP mode, Watchdog Timer and code protection features improve system cost, power and reliability.

The PIC16C505 is available in the cost-effective One-Time-Programmable (OTP) version, which is suitable for production in any volume. The customer can take full advantage of Microchip's price leadership in OTP microcontrollers, while benefiting from the OTP's flexibility.

The PIC16C505 product is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a 'C' compiler, a low-cost development programmer and a full featured programmer. All the tools are supported on  $IBM^{\textcircled{B}}$  PC and compatible machines.

### 1.1 <u>Applications</u>

The PIC16C505 fits in applications ranging from personal care appliances and security systems to lowpower remote transmitters/receivers. The EPROM technology makes customizing application programs (transmitter codes, appliance settings, receiver frequencies, etc.) extremely fast and convenient. The small footprint packages, for through hole or surface mounting, make this microcontroller perfect for applications with space limitations. Low-cost, low-power, highperformance, ease of use and I/O flexibility make the PIC16C505 very versatile even in areas where no microcontroller use has been considered before (e.g., timer functions, replacement of "glue" logic and PLD's in larger systems, and coprocessor applications).

| TABLE 3-1: | PIC16C505 PINOUT DESCRIPTION |

|------------|------------------------------|

|------------|------------------------------|

| Name            | DIP<br>Pin # | SOIC<br>Pin # | l/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|--------------|---------------|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0             | 13           | 13            | I/O           | TTL/ST         | Bi-directional I/O port/ serial programming data. Can<br>be software programmed for internal weak pull-up and<br>wake-up from SLEEP on pin change. This buffer is a<br>Schmitt Trigger input when used in serial programming<br>mode.                                                                                                                                                                                             |

| RB1             | 12           | 12            | I/O           | TTL/ST         | Bi-directional I/O port/ serial programming clock. Can<br>be software programmed for internal weak pull-up and<br>wake-up from SLEEP on pin change. This buffer is a<br>Schmitt Trigger input when used in serial programming<br>mode.                                                                                                                                                                                            |

| RB2             | 11           | 11            | I/O           | TTL            | Bi-directional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                          |

| RB3/MCLR/Vpp    | 4            | 4             | Ι             | TTL/ST         | Input port/master clear (reset) input/programming volt-<br>age input. When configured as MCLR, this pin is an<br>active low reset to the device. Voltage on MCLR/VPP<br>must not exceed VDD during normal device operation.<br>Can be software programmed for internal weak pull-up<br>and wake-up from SLEEP on pin change. Weak pull-<br>up only when configured as RB3. ST when configured<br>as MCLR.                         |

| RB4/OSC2/CLKOUT | 3            | 3             | I/O           | TTL            | Bi-directional I/O port/oscillator crystal output. Con-<br>nections to crystal or resonator in crystal oscillator<br>mode (XT and LP modes only, RB4 in other modes).<br>Can be software programmed for internal weak pull-up<br>and wake-up from SLEEP on pin change. In EXTRC<br>and INTRC modes, the pin output can be configured to<br>CLKOUT, which has 1/4 the frequency of OSC1 and<br>denotes the instruction cycle rate. |

| RB5/OSC1/CLKIN  | 2            | 2             | I/O           | TTL/ST         | Bidirectional IO port/oscillator crystal input/external<br>clock source input (RB5 in Internal RC mode only,<br>OSC1 in all other oscillator modes). TTL input when<br>RB5, ST input in external RC oscillator mode.                                                                                                                                                                                                              |

| RC0             | 10           | 10            | I/O           | TTL            | Bi-directional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                          |

| RC1             | 9            | 9             | I/O           | TTL            | Bi-directional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                          |

| RC2             | 8            | 8             | I/O           | TTL            | Bi-directional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                          |

| RC3             | 7            | 7             | I/O           | TTL            | Bi-directional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                          |

| RC4             | 6            | 6             | I/O           | TTL            | Bi-directional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                          |

| RC5/T0CKI       | 5            | 5             | I/O           | ST             | Bi-directional I/O port. Can be configured as T0CKI.                                                                                                                                                                                                                                                                                                                                                                              |

| Vdd             | 1            | 1             | Р             | —              | Positive supply for logic and I/O pins                                                                                                                                                                                                                                                                                                                                                                                            |

| Vss             | 14           | 14            | Р             |                | Ground reference for logic and I/O pins                                                                                                                                                                                                                                                                                                                                                                                           |

Legend: I = input, O = output, I/O = input/output, P = power, — = not used, TTL = TTL input, ST = Schmitt Trigger input

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (Table 4-1). The Special Function Registers can be classified into two sets. The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

| Address            | Name   | Bit 7         | Bit 6        | Bit 5      | Bit 4       | Bit 3       | Bit 2        | Bit 1  | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets <sup>(2)</sup> |

|--------------------|--------|---------------|--------------|------------|-------------|-------------|--------------|--------|-------|-------------------------------|------------------------------------------------|

| 00h                | INDF   | Uses conte    | nts of FSF   | to addres  | s data me   | mory (not a | physical reg | ister) |       | xxxx xxxx                     | uuuu uuuu                                      |

| 01h                | TMR0   | 8-bit real-ti | me clock/c   | ounter     |             |             |              |        |       | xxxx xxxx                     | uuuu uuuu                                      |

| 02h <sup>(1)</sup> | PCL    | Low order     | B bits of PC | C          |             |             |              |        |       | 1111 1111                     | 1111 1111                                      |

| 03h                | STATUS | RBWUF         | _            | PAO        | TO          | PD          | Z            | DC     | С     | 0001 1xxx                     | q00q quuu <sup>(1)</sup>                       |

| 04h                | FSR    | Indirect dat  | a memory     | address p  | ointer      |             |              |        |       | 110x xxxx                     | 11uu uuuu                                      |

| 05h                | OSCCAL | CAL5          | CAL4         | CAL3       | CAL2        | CAL1        | CAL0         | _      | _     | 1000 00                       | uuuu uu                                        |

| N/A                | TRISB  | —             |              | I/O contro | l registers |             |              |        |       | 11 1111                       | 11 1111                                        |

| N/A                | TRISC  | _             |              | I/O contro | l registers |             |              |        |       | 11 1111                       | 11 1111                                        |

| N/A                | OPTION | RBWU          | RBPU         | TOCS       | TOSE        | PSA         | PS2          | PS1    | PS0   | 1111 1111                     | 1111 1111                                      |

| 06h                | PORTB  | —             |              | RB5        | RB4         | RB3         | RB2          | RB1    | RB0   | xx xxxx                       | uu uuuu                                        |

| 07h                | PORTC  | —             |              | RC5        | RC4         | RC3         | RC2          | RC1    | RC0   | xx xxxx                       | uu uuuu                                        |

### TABLE 4-1:SPECIAL FUNCTION REGISTER (SFR) SUMMARY

Legend: Shaded cells not used by Port Registers, read as '0', — = unimplemented, read as '0', x = unknown, u = unchanged, q = depends on condition.

Note 1: If reset was due to wake-up on pin change, then bit 7 = 1. All other rests will cause bit 7 = 0.

Note 2: Other (non-power-up) resets include external reset through MCLR, watchdog timer and wake-up on pin change reset.

### TABLE 5-1: SUMMARY OF PORT REGISTERS

| Address | Name   | Bit 7 | Bit 6 | Bit 5      | Bit 4                   | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other Resets |

|---------|--------|-------|-------|------------|-------------------------|-------|-------|-------|-------|-------------------------------|------------------------------|

| N/A     | TRISB  | —     | _     | I/O contro | l registers             |       |       |       |       | 11 1111                       | 11 1111                      |

| N/A     | TRISC  | —     | _     | I/O contro | l registers             |       |       |       |       | 11 1111                       | 11 1111                      |

| N/A     | OPTION | RBWU  | RBPU  | TOCS       | TOSE                    | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                    |

| 03h     | STATUS | RBWUF | _     | PAO        | PAO TO PD Z DC C        |       |       |       |       |                               | q00q quuu <sup>(1)</sup>     |

| 06h     | PORTB  | —     | —     | RB5        | RB5 RB4 RB3 RB2 RB1 RB0 |       |       |       |       |                               | uu uuuu                      |

| 07h     | PORTC  |       |       | RC5        | RC4                     | RC3   | RC2   | RC1   | RC0   | xx xxxx                       | uu uuuu                      |

Legend: Shaded cells not used by Port Registers, read as '0', — = unimplemented, read as '0', x = unknown, u = unchanged, q = depends on condition.

Note 1: If reset was due to wake-up on pin change, then bit 7 = 1. All other rests will cause bit 7 = 0.

#### 5.5 I/O Programming Considerations

#### 5.5.1 BI-DIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU, bit5 to be set and the PORTB value to be written to the output latches. If another bit of PORTB is used as a bidirectional I/O pin (say bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Example 5-1 shows the effect of two sequential read-modify-write instructions (e.g.,  ${\tt BCF}\,,~{\tt BSF},$  etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wiredand"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-1: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

; Initial PORTB Settings ; PORTB<5:3> Inputs ; PORTB<2:0> Outputs ; ; PORTB latch PORTB pins -----; BCF ;--01 -ppp --11 pppp PORTB, 5 BCF PORTB, 4 ;--10 -ppp --11 pppp MOVLW 007h ;

TRIS PORTB

; ;Note that the user may have expected the pin ;values to be --00 pppp. The 2nd BCF caused ;RB5 to be latched as the pin value (High).

;--10 -ppp

--11 pppp

#### 5.5.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-2). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction causes that file to be read into the CPU. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

NOTES:

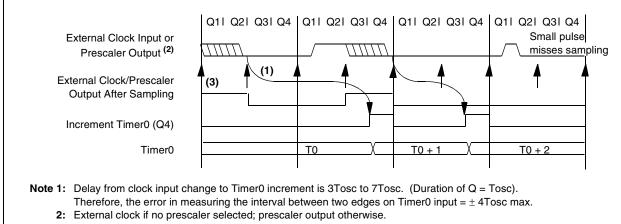

#### 6.1 Using Timer0 with an External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.1.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-4). Therefore, it is necessary for T0CKI to be high for at least 2T0sc (and a small RC delay of 20 ns) and low for at least 2T0sc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 6.1.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-4 shows the delay from the external clock edge to the timer incrementing.

#### FIGURE 6-4: TIMER0 TIMING WITH EXTERNAL CLOCK

**3:** The arrows indicate the points in time where sampling occurs.

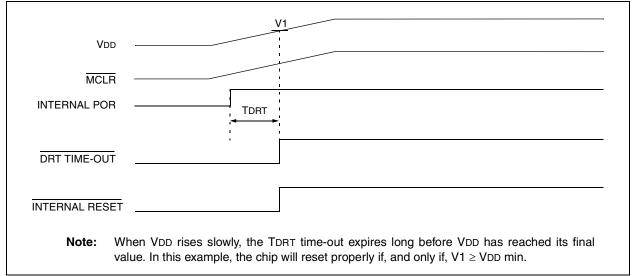

#### FIGURE 7-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): SLOW VDD RISE TIME

#### 7.5 Device Reset Timer (DRT)

In the PIC16C505, the DRT runs any time the device is powered up. DRT runs from RESET and varies based on oscillator selection and reset type (see Table 7-5).

The DRT operates on an internal RC oscillator. The processor is kept in RESET as long as the DRT is active. The DRT delay allows VDD to rise above VDD min. and for the oscillator to stabilize.

Oscillator circuits based on crystals or ceramic resonators require a certain time after power-up to establish a stable oscillation. The on-chip DRT keeps the device in a RESET condition for approximately 18 ms after MCLR has reached a logic high (VIHMCLR) level. Thus, programming RB3/MCLR/VPP as MCLR and using an external RC network connected to the MCLR input is not required in most cases, allowing for savings in cost-sensitive and/or space restricted applications, as well as allowing the use of the RB3/MCLR/VPP pin as a general purpose input.

The Device Reset time delay will vary from chip to chip due to VDD, temperature and process variation. See AC parameters for details.

The DRT will also be triggered upon a Watchdog Timer time-out. This is particularly important for applications using the WDT to wake from SLEEP mode automatically.

Reset sources are POR, MCLR, WDT time-out and Wake-up on pin change. (See Section 7.9.2, Notes 1, 2, and 3, page 37.)

#### 7.6 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the external RC oscillator of the RB5/OSC1/CLKIN pin and the internal 4 MHz oscillator. That means that the WDT will run even if the main processor clock has been stopped, for example, by execution of a SLEEP instruction. During normal operation or SLEEP, a WDT reset or wake-up reset generates a device RESET.

The  $\overline{\text{TO}}$  bit (STATUS<4>) will be cleared upon a Watchdog Timer reset.

The WDT can be permanently disabled by programming the configuration bit WDTE as a '0' (Section 7.1). Refer to the PIC16C505 Programming Specifications to determine how to access the configuration word.

TABLE 7-5: DRT (DEVICE RESET TIMER PERIOD)

| ,                           |                 |                      |  |  |  |  |  |

|-----------------------------|-----------------|----------------------|--|--|--|--|--|

| Oscillator<br>Configuration | POR Reset       | Subsequent<br>Resets |  |  |  |  |  |

| IntRC &<br>ExtRC            | 18 ms (typical) | 300 μs<br>(typical)  |  |  |  |  |  |

| HS, XT & LP                 | 18 ms (typical) | 18 ms (typical)      |  |  |  |  |  |

#### 7.7 <u>Time-Out Sequence, Power Down,</u> and Wake-up from SLEEP Status Bits (TO/PD/RBWUF)

The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$ , and RBWUF bits in the STATUS register can be tested to determine if a RESET condition has been caused by a power-up condition, a  $\overline{\text{MCLR}}$  or Watchdog Timer (WDT) reset.

| <b>TABLE 7-7:</b> | TO/PD/RBWUF STATUS |

|-------------------|--------------------|

|                   | AFTER RESET        |

| RBWUF | TO | PD | RESET caused by                     |  |  |  |  |

|-------|----|----|-------------------------------------|--|--|--|--|

| 0     | 0  | 0  | WDT wake-up from<br>SLEEP           |  |  |  |  |

| 0     | 0  | u  | WDT time-out (not from SLEEP)       |  |  |  |  |

| 0     | 1  | 0  | MCLR wake-up from<br>SLEEP          |  |  |  |  |

| 0     | 1  | 1  | Power-up                            |  |  |  |  |

| 0     | u  | u  | MCLR not during SLEEP               |  |  |  |  |

| 1     | 1  | 0  | Wake-up from SLEEP on<br>pin change |  |  |  |  |

Legend: u = unchanged

Note 1: The TO, PD, and RBWUF bits maintain their status (u) until a reset occurs. A low-pulse on the MCLR input does not change the TO, PD, and RBWUF status bits.

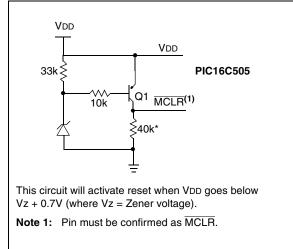

#### 7.8 Reset on Brown-Out

A brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a brown-out.

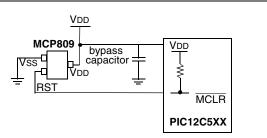

To reset PIC16C505 devices when a brown-out occurs, external brown-out protection circuits may be built, as shown in Figure 7-12 and Figure 7-13.

#### FIGURE 7-12: BROWN-OUT PROTECTION CIRCUIT 1

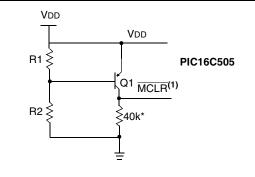

#### FIGURE 7-13: BROWN-OUT PROTECTION CIRCUIT 2

This brown-out circuit is less expensive, although less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \bullet \frac{R1}{R1 + R2} = 0.7V$$

**Note 1:** Pin must be confirmed as  $\overline{MCLR}$ .

#### FIGURE 7-14: BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. There are 7 different trip point selections to accommodate 5V to 3V systems.

| INCF                                                    | Increment f                                                                                                                                                            |  |  |  |  |  |  |  |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:                                                 | [label] INCF f,d                                                                                                                                                       |  |  |  |  |  |  |  |

| Operands:                                               | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                             |  |  |  |  |  |  |  |

| Operation:                                              | (f) + 1 $\rightarrow$ (dest)                                                                                                                                           |  |  |  |  |  |  |  |

| Status Affected:                                        | Z                                                                                                                                                                      |  |  |  |  |  |  |  |

| Encoding:                                               | 0010 10df ffff                                                                                                                                                         |  |  |  |  |  |  |  |

| Description:                                            | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in register<br>'f'. |  |  |  |  |  |  |  |

| Words:                                                  | 1                                                                                                                                                                      |  |  |  |  |  |  |  |

| Cycles:                                                 | 1                                                                                                                                                                      |  |  |  |  |  |  |  |

| Example:                                                | INCF CNT, 1                                                                                                                                                            |  |  |  |  |  |  |  |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0xFF<br>= 0                                                                                                                                                          |  |  |  |  |  |  |  |

|                     | Increment f, Skip if 0                                                                                                                                                 |  |  |  |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:             | [label] INCFSZ f,d                                                                                                                                                     |  |  |  |  |  |  |

| Operands:           | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                             |  |  |  |  |  |  |

| Operation:          | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                       |  |  |  |  |  |  |

| Status Affected:    | None                                                                                                                                                                   |  |  |  |  |  |  |

| Encoding:           | 0011 11df ffff                                                                                                                                                         |  |  |  |  |  |  |

| Description:        | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in register<br>'f'. |  |  |  |  |  |  |

|                     | If the result is 0, then the next<br>instruction, which is already<br>fetched, is discarded and a NOP is<br>executed instead making it a two<br>cycle instruction.     |  |  |  |  |  |  |

| Words:              | 1                                                                                                                                                                      |  |  |  |  |  |  |

| Cycles:             | 1(2)                                                                                                                                                                   |  |  |  |  |  |  |

| Example:            | HERE INCFSZ CNT, 1<br>GOTO LOOP                                                                                                                                        |  |  |  |  |  |  |

|                     | CONTINUE •                                                                                                                                                             |  |  |  |  |  |  |

|                     | uction                                                                                                                                                                 |  |  |  |  |  |  |

| Before Instru       |                                                                                                                                                                        |  |  |  |  |  |  |

| Before Instru<br>PC | = address (HERE)                                                                                                                                                       |  |  |  |  |  |  |

| RLF                                                           | Rotate Left f through Carry                                                                                                                                                                                        | RRF                                                           | Rotate Right f through Carry                                                                                                                                                                                        |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                       | [ <i>label</i> ] RLF f,d                                                                                                                                                                                           | Syntax:                                                       | [ <i>label</i> ] RRF f,d                                                                                                                                                                                            |

| Operands:                                                     | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                         | Operands:                                                     | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                                                      |

| Operation:                                                    | See description below                                                                                                                                                                                              | Operation:                                                    | See description below                                                                                                                                                                                               |

| Status Affected:                                              | С                                                                                                                                                                                                                  | Status Affected:                                              | С                                                                                                                                                                                                                   |

| Encoding:                                                     | 0011 01df ffff                                                                                                                                                                                                     | Encoding:                                                     | 0011 00df ffff                                                                                                                                                                                                      |

| Description:                                                  | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is stored back in regis-<br>ter 'f'. | Description:                                                  | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in reg-<br>ister 'f'. |

|                                                               | C register 'f'                                                                                                                                                                                                     |                                                               | C register 'f'                                                                                                                                                                                                      |

| Words:                                                        | 1                                                                                                                                                                                                                  | Words:                                                        | 1                                                                                                                                                                                                                   |

| Cycles:                                                       | 1                                                                                                                                                                                                                  | Cycles:                                                       | 1                                                                                                                                                                                                                   |

| Example:                                                      | RLF REG1,0                                                                                                                                                                                                         | Example:                                                      | RRF REG1,0                                                                                                                                                                                                          |

| Before Instru<br>REG1<br>C<br>After Instruc<br>REG1<br>W<br>C | = 1110 0110<br>= 0                                                                                                                                                                                                 | Before Instru<br>REG1<br>C<br>After Instruc<br>REG1<br>W<br>C | = 1110 0110<br>= 0                                                                                                                                                                                                  |

### 9.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 9.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

## 9.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

## 9.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 9.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

#### 10.3 DC CHARACTERISTICS:

#### PIC16C505-04 (Commercial, Industrial, Extended) PIC16C505-20(Commercial, Industrial, Extended) PIC16LC505-04 (Commercial, Industrial)

|        | I                                  | PIC16L                                                                                                                                                                                                                                                | .C505-04 | (Com   | mercial   | , Indu   | strial)                                 |  |  |  |  |

|--------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|-----------|----------|-----------------------------------------|--|--|--|--|

|        |                                    |                                                                                                                                                                                                                                                       |          |        |           |          | ss otherwise specified)                 |  |  |  |  |

|        |                                    | Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ (commercial)                                                                                                                                                                               |          |        |           |          |                                         |  |  |  |  |

| DC CHA | ARACTERISTICS                      | $\label{eq:constraint} \begin{array}{l} -40^\circ C \leq TA \leq +85^\circ C \mbox{ (industrial)} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ (extended)} \\ \end{array}$<br>Operating voltage VDD range as described in DC spec Section 10.1 and |          |        |           |          |                                         |  |  |  |  |

|        |                                    |                                                                                                                                                                                                                                                       |          |        |           |          |                                         |  |  |  |  |

|        |                                    | Section                                                                                                                                                                                                                                               |          | ו טט י | ange as c | lescribe | ed in DC spec Section 10.1 and          |  |  |  |  |

| Param  | Characteristic                     | Sym Min Typ† Max Units Conditions                                                                                                                                                                                                                     |          |        |           |          |                                         |  |  |  |  |

| No.    | onaraoteristic                     | Oyin                                                                                                                                                                                                                                                  |          | 1 YPI  | Max       | Onits    | Conditions                              |  |  |  |  |

|        | Input Low Voltage                  |                                                                                                                                                                                                                                                       |          |        |           |          |                                         |  |  |  |  |

|        | I/O ports                          | VIL                                                                                                                                                                                                                                                   |          |        |           |          |                                         |  |  |  |  |

| D030   | with TTL buffer                    | VIL                                                                                                                                                                                                                                                   | Vss      | _      | 0.8V      | v        | For all $4.5 \le VDD \le 5.5V$          |  |  |  |  |

| D030A  |                                    |                                                                                                                                                                                                                                                       | VSS      | _      | 0.15VDD   | -        | otherwise                               |  |  |  |  |

| D031   | with Schmitt Trigger buffer        |                                                                                                                                                                                                                                                       | VSS      | _      | 0.2VDD    | v        |                                         |  |  |  |  |

| D032   | MCLR, RC5/T0CKI                    |                                                                                                                                                                                                                                                       | VSS      | _      | 0.2VDD    | v        |                                         |  |  |  |  |

| DUUL   | (in EXTRC mode)                    |                                                                                                                                                                                                                                                       | ¥00      |        | 0.2000    | v        |                                         |  |  |  |  |

| D033   | OSC1 (in XT, HS and LP)            |                                                                                                                                                                                                                                                       | Vss      | _      | 0.3VDD    | v        | Note1                                   |  |  |  |  |

| 2000   | Input High Voltage                 |                                                                                                                                                                                                                                                       |          |        | 0.07.55   | -        |                                         |  |  |  |  |

|        | I/O ports                          | VIH                                                                                                                                                                                                                                                   |          | _      |           |          |                                         |  |  |  |  |

| D040   | with TTL buffer                    |                                                                                                                                                                                                                                                       | 2.0      | _      | Vdd       | v        | $4.5 \leq VDD \leq 5.5V$                |  |  |  |  |

| D040A  |                                    |                                                                                                                                                                                                                                                       | 0.25VDD  | _      | Vdd       | v        |                                         |  |  |  |  |

|        |                                    |                                                                                                                                                                                                                                                       | + 0.8VDD |        |           |          | otherwise                               |  |  |  |  |

| D041   | with Schmitt Trigger buffer        |                                                                                                                                                                                                                                                       | 0.8Vdd   | —      | Vdd       | V        | For entire VDD range                    |  |  |  |  |

| D042   | MCLR, RC5/T0CKI                    |                                                                                                                                                                                                                                                       | 0.8Vdd   | —      | Vdd       | V        |                                         |  |  |  |  |

| D042A  | OSC1 (XT, HS and LP)               |                                                                                                                                                                                                                                                       | 0.7Vdd   | —      | Vdd       | V        | Note1                                   |  |  |  |  |

| D043   | OSC1 (in EXTRC mode)               |                                                                                                                                                                                                                                                       | 0.9Vdd   | _      | Vdd       | V        |                                         |  |  |  |  |

| D070   | GPIO weak pull-up current (Note 4) | IPUR                                                                                                                                                                                                                                                  | 50       | 250    | 400       | μA       | VDD = 5V, VPIN = VSS                    |  |  |  |  |

|        | Input Leakage Current (Notes 2, 3) |                                                                                                                                                                                                                                                       |          |        |           |          |                                         |  |  |  |  |

| D060   | I/O ports                          | lı∟                                                                                                                                                                                                                                                   | —        | —      | ±1        | μA       | $Vss \leq VPIN \leq VDD$ , Pin at       |  |  |  |  |

|        |                                    |                                                                                                                                                                                                                                                       |          |        |           |          | hi-impedance                            |  |  |  |  |

| D061   | GP3/MCLRI (Note 5)                 |                                                                                                                                                                                                                                                       | —        | —      | ±30       | μΑ       | $Vss \le VPIN \le VDD$                  |  |  |  |  |

| D061A  | GP3/MCLRI (Note 6)                 |                                                                                                                                                                                                                                                       | —        | —      | ±5        | μΑ       | $Vss \le VPIN \le VDD$                  |  |  |  |  |

| D063   | OSC1                               |                                                                                                                                                                                                                                                       | —        | —      | ±5        | μΑ       | $Vss \leq VPIN \leq VDD, XT, HS and LP$ |  |  |  |  |

|        |                                    |                                                                                                                                                                                                                                                       |          |        |           |          | osc configuration                       |  |  |  |  |

|        | Output Low Voltage                 |                                                                                                                                                                                                                                                       |          |        |           |          |                                         |  |  |  |  |

| D080   | I/O ports/CLKOUT                   | VOL                                                                                                                                                                                                                                                   | —        | —      | 0.6       | V        | IOL = 8.5 mA, VDD = 4.5V,               |  |  |  |  |

|        |                                    |                                                                                                                                                                                                                                                       |          |        |           |          | –40°C to +85°C                          |  |  |  |  |

| D080A  |                                    |                                                                                                                                                                                                                                                       | —        | —      | 0.6       | V        | IOL = 7.0  mA,  VDD = 4.5 V,            |  |  |  |  |

| Dage   |                                    |                                                                                                                                                                                                                                                       |          |        |           |          | -40°C to +125°C                         |  |  |  |  |

| D083   | OSC2                               |                                                                                                                                                                                                                                                       | —        | -      | 0.6       | V        | IOL = 1.6  mA,  VDD = 4.5  V,           |  |  |  |  |

| Dacat  |                                    |                                                                                                                                                                                                                                                       |          |        | 0.0       |          | -40°C to +85°C                          |  |  |  |  |

| D083A  |                                    |                                                                                                                                                                                                                                                       | _        | -      | 0.6       | V        | IOL = 1.2  mA, VDD = 4.5V,              |  |  |  |  |

|        |                                    |                                                                                                                                                                                                                                                       |          |        |           |          | –40°C to +125°C                         |  |  |  |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C505 be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as coming out of the pin.

4: Does not include GP3. For GP3 see parameters D061 and D061A.

5: This spec. applies to GP3/MCLR configured as external MCLR and GP3/MCLR configured as input with internal pull-up enabled.

6: This spec. applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

| VDD (Volts) | Temperature (°C) | Min   | Тур    | Max  | Units |

|-------------|------------------|-------|--------|------|-------|

|             |                  | RB0/R | B1/RB4 |      |       |

| 2.5         | -40              | 38K   | 42K    | 63K  | W     |

|             | 25               | 42K   | 48K    | 63K  | W     |

|             | 85               | 42K   | 49K    | 63K  | W     |

|             | 125              | 50K   | 55K    | 63K  | W     |

| 5.5         | -40              | 15K   | 17K    | 20K  | W     |

|             | 25               | 18K   | 20K    | 23K  | W     |

|             | 85               | 19K   | 22K    | 25K  | W     |

|             | 125              | 22K   | 24K    | 28K  | W     |

|             |                  | R     | B3     |      |       |

| 2.5         | -40              | 285K  | 346K   | 417K | W     |

|             | 25               | 343K  | 414K   | 532K | W     |

|             | 85               | 368K  | 457K   | 532K | W     |

|             | 125              | 431K  | 504K   | 593K | W     |

| 5.5         | -40              | 247K  | 292K   | 360K | W     |

|             | 25               | 288K  | 341K   | 437K | W     |

|             | 85               | 306K  | 371K   | 448K | W     |

|             | 125              | 351K  | 407K   | 500K | W     |

# TABLE 10-1: PULL-UP RESISTOR RANGES - PIC16C505

\* These parameters are characterized but not tested.

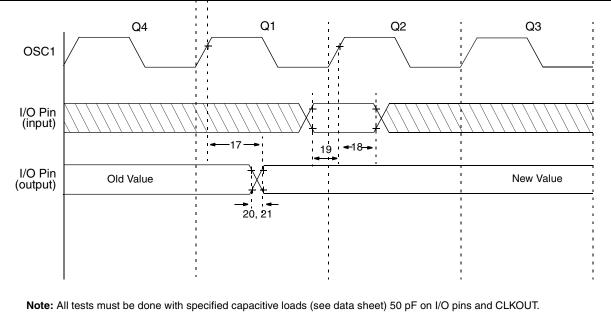

#### FIGURE 10-6: I/O TIMING - PIC16C505

| <b>TABLE 10-4:</b> | TIMING REQUIREMENTS - PIC16C505 |

|--------------------|---------------------------------|

|                    |                                 |

| AC Characteristics |          | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \ (commercial) \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \ (industrial) \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \ (extended) \\ \mbox{Operating Voltage VDD range is described in Section 10.1} \end{array}$ |     |                    |      |       |  |

|--------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|------|-------|--|

| Parameter<br>No.   | Sym      | Characteristic                                                                                                                                                                                                                                                                                                                                                              | Min | Typ <sup>(1)</sup> | Max  | Units |  |

| 17                 | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(2,3)</sup>                                                                                                                                                                                                                                                                                                             | —   | _                  | 100* | ns    |  |

| 18                 | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid<br>(I/O in hold time) <sup>(2)</sup>                                                                                                                                                                                                                                                                                     | TBD | —                  | _    | ns    |  |

| 19                 | TioV2osH | Port input valid to OSC1↑<br>(I/O in setup time)                                                                                                                                                                                                                                                                                                                            | TBD | —                  | _    | ns    |  |

| 20                 | TioR     | Port output rise time <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                        | —   | 10                 | 25** | ns    |  |

| 21                 | TioF     | Port output fall time <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                        | _   | 10                 | 25** | ns    |  |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: Measurements are taken in EXTRC mode.

**3:** See Figure 10-4 for loading conditions.

NOTES:

Example

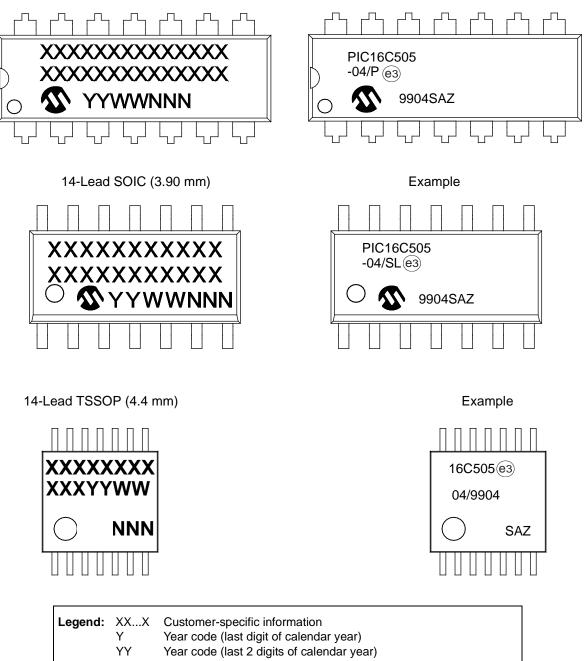

# 12.0 PACKAGING INFORMATION

## 12.1 Package Marking Information

14-Lead PDIP (300 mil)

|       | YY                                                                     | Year code (last 2 digits of calendar year)                               |  |  |  |

|-------|------------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|--|

|       | WW                                                                     | Week code (week of January 1 is week '01')                               |  |  |  |

|       | NNN                                                                    | Alphanumeric traceability code                                           |  |  |  |

|       | e3                                                                     | Pb-free JEDEC designator for Matte Tin (Sn)                              |  |  |  |

|       | *                                                                      | This package is Pb-free. The Pb-free JEDEC designator ((e3))             |  |  |  |

|       |                                                                        | can be found on the outer packaging for this package.                    |  |  |  |

|       |                                                                        |                                                                          |  |  |  |

| Note: | In the eve                                                             | ent the full Microchip part number cannot be marked on one line, it will |  |  |  |

|       | be carried over to the next line, thus limiting the number of availabl |                                                                          |  |  |  |

|       | characters for customer-specific information.                          |                                                                          |  |  |  |

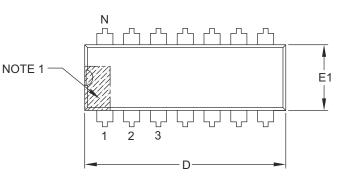

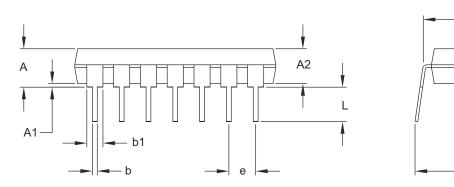

# 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Е

eВ

С

|                            | INCHES           |      |          |      |

|----------------------------|------------------|------|----------|------|

| Dimensior                  | Dimension Limits |      | NOM      | MAX  |

| Number of Pins             | Ν                | 14   |          |      |

| Pitch                      | е                |      | .100 BSC |      |

| Top to Seating Plane       | А                | —    | -        | .210 |

| Molded Package Thickness   | A2               | .115 | .130     | .195 |

| Base to Seating Plane      | A1               | .015 | -        | -    |

| Shoulder to Shoulder Width | E                | .290 | .310     | .325 |

| Molded Package Width       | E1               | .240 | .250     | .280 |

| Overall Length             | D                | .735 | .750     | .775 |

| Tip to Seating Plane       | L                | .115 | .130     | .150 |

| Lead Thickness             | С                | .008 | .010     | .015 |

| Upper Lead Width           | b1               | .045 | .060     | .070 |

| Lower Lead Width           | b                | .014 | .018     | .022 |

| Overall Row Spacing §      | eB               | -    | -        | .430 |

Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M. BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B

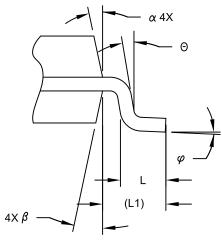

### 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

VIEW C

| Units                    |    | MILLIMETERS |          |      |

|--------------------------|----|-------------|----------|------|

| Dimension Limits         |    | MIN         | NOM      | MAX  |

| Number of Pins           | N  |             | 14       |      |

| Pitch                    | е  |             | 1.27 BSC |      |

| Overall Height           | Α  | -           | -        | 1.75 |

| Molded Package Thickness | A2 | 1.25        | -        | -    |

| Standoff §               | A1 | 0.10        | -        | 0.25 |

| Overall Width            | E  | 6.00 BSC    |          |      |

| Molded Package Width     | E1 | 3.90 BSC    |          |      |

| Overall Length           | D  | 8.65 BSC    |          |      |

| Chamfer (Optional)       | h  | 0.25        | -        | 0.50 |

| Foot Length              | L  | 0.40        | -        | 1.27 |

| Footprint                | L1 |             | 1.04 REF |      |

| Lead Angle               | Θ  | 0°          | -        | -    |

| Foot Angle               | φ  | 0°          | -        | 8°   |

| Lead Thickness           | С  | 0.10        | -        | 0.25 |

| Lead Width               | b  | 0.31        | -        | 0.51 |

| Mold Draft Angle Top     | α  | 5°          | -        | 15°  |

| Mold Draft Angle Bottom  | β  | 5°          | -        | 15°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065C Sheet 2 of 2

## INDEX

| Α                                              |        |

|------------------------------------------------|--------|

| ALU                                            | 7      |

| Applications                                   |        |

| Architectural Overview                         |        |

| Assembler                                      |        |

| MPASM Assembler                                |        |

| В                                              |        |

| -                                              |        |

| Block Diagram                                  |        |

| On-Chip Reset Circuit                          |        |

| Timer0<br>TMR0/WDT Prescaler                   |        |

|                                                |        |

| Watchdog Timer<br>Brown-Out Protection Circuit |        |

|                                                |        |

| C                                              |        |

| C Compilers                                    |        |

| MPLAB C18                                      | 52     |

| CAL0 bit                                       | 16     |

| CAL1 bit                                       | 16     |

| CAL2 bit                                       | 16     |

| CAL3 bit                                       | 16     |

| CALFST bit                                     | 16     |

| CALSLW bit                                     | 16     |

| Carry                                          |        |

| Clocking Scheme                                |        |

| Code Protection                                | 27, 37 |

| Configuration Bits                             |        |

| Configuration Word                             |        |

| Customer Change Notification Service           |        |

| Customer Notification Service                  |        |

| Customer Support                               | 85     |

| D                                              |        |

| DC and AC Characteristics                      | 69     |

| Development Support                            |        |

| Device Varieties                               |        |

| Digit Carry                                    |        |

| E                                              |        |

| -                                              |        |

| Errata                                         | 2      |

| F                                              |        |

| Family of Devices                              |        |

| PIC16C505                                      | 4      |

| FSR                                            | 18     |

| 1                                              |        |