Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | POR, WDT                                                                   |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 1.5KB (1K x 12)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 72 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

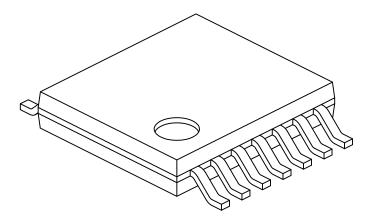

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 14-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c505-04i-sl |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 PIC16C505 DEVICE VARIETIES

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC16C505 Product Identification System at the back of this data sheet to specify the correct part number.

### 2.1 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility of frequent code updates or small volume applications.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

## 2.2 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program medium to high quantity units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

## 2.3 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service, where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry-code, password or ID number.

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (Table 4-1). The Special Function Registers can be classified into two sets. The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

| Address            | Name   | Bit 7                  | Bit 6      | Bit 5      | Bit 4       | Bit 3       | Bit 2        | Bit 1     | Bit 0     | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets <sup>(2)</sup> |

|--------------------|--------|------------------------|------------|------------|-------------|-------------|--------------|-----------|-----------|-------------------------------|------------------------------------------------|

| 00h                | INDF   | Uses conte             | nts of FSF | to addres  | s data me   | mory (not a | physical reg | ister)    |           | xxxx xxxx                     | uuuu uuuu                                      |

| 01h                | TMR0   | 8-bit real-ti          | me clock/c | ounter     |             |             |              |           |           | xxxx xxxx                     | uuuu uuuu                                      |

| 02h <sup>(1)</sup> | PCL    | Low order 8 bits of PC |            |            |             |             |              | 1111 1111 | 1111 1111 |                               |                                                |

| 03h                | STATUS | RBWUF                  | _          | PAO        | TO          | PD          | Z            | DC        | С         | 0001 1xxx                     | q00q quuu <sup>(1)</sup>                       |

| 04h                | FSR    | Indirect dat           | a memory   | address p  | ointer      |             |              |           |           | 110x xxxx                     | 11uu uuuu                                      |

| 05h                | OSCCAL | CAL5                   | CAL4       | CAL3       | CAL2        | CAL1        | CAL0         | _         | _         | 1000 00                       | uuuu uu                                        |

| N/A                | TRISB  | —                      |            | I/O contro | l registers |             |              |           |           | 11 1111                       | 11 1111                                        |

| N/A                | TRISC  | _                      |            | I/O contro | l registers |             |              |           |           | 11 1111                       | 11 1111                                        |

| N/A                | OPTION | RBWU                   | RBPU       | TOCS       | TOSE        | PSA         | PS2          | PS1       | PS0       | 1111 1111                     | 1111 1111                                      |

| 06h                | PORTB  | —                      |            | RB5        | RB4         | RB3         | RB2          | RB1       | RB0       | xx xxxx                       | uu uuuu                                        |

| 07h                | PORTC  | —                      |            | RC5        | RC4         | RC3         | RC2          | RC1       | RC0       | xx xxxx                       | uu uuuu                                        |

## TABLE 4-1:SPECIAL FUNCTION REGISTER (SFR) SUMMARY

Legend: Shaded cells not used by Port Registers, read as '0', — = unimplemented, read as '0', x = unknown, u = unchanged, q = depends on condition.

Note 1: If reset was due to wake-up on pin change, then bit 7 = 1. All other rests will cause bit 7 = 0.

Note 2: Other (non-power-up) resets include external reset through MCLR, watchdog timer and wake-up on pin change reset.

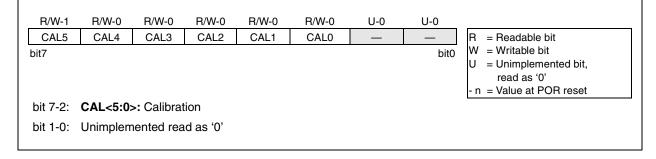

## 4.5 OSCCAL Register

The Oscillator Calibration (OSCCAL) register is used to calibrate the internal 4 MHz oscillator. It contains six bits for calibration

| Note: | Please note that erasing the device will       |

|-------|------------------------------------------------|

|       | also erase the pre-programmed internal         |

|       | calibration value for the internal oscillator. |

|       | The calibration value must be read prior to    |

|       | erasing the part, so it can be repro-          |

|       | grammed correctly later.                       |

After you move in the calibration constant, do not change the value. See Section 7.2.5

## REGISTER 4-3: OSCCAL REGISTER (ADDRESS 05h) PIC16C505

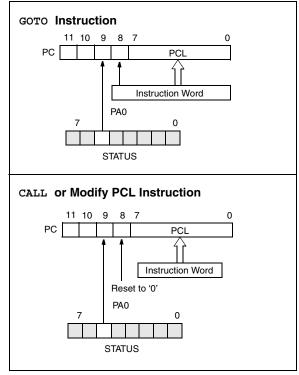

### 4.6 Program Counter

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one every instruction cycle, unless an instruction changes the PC.

For a GOTO instruction, bits 8:0 of the PC are provided by the GOTO instruction word. The PC Latch (PCL) is mapped to PC<7:0>. Bit 5 of the STATUS register provides page information to bit 9 of the PC (Figure 4-3).

For a CALL instruction, or any instruction where the PCL is the destination, bits 7:0 of the PC again are provided by the instruction word. However, PC<8> does not come from the instruction word, but is always cleared (Figure 4-3).

Instructions where the PCL is the destination, or Modify PCL instructions, include MOVWF PC, ADDWF PC, and BSF PC, 5.

**Note:** Because PC<8> is cleared in the CALL instruction or any Modify PCL instruction, all subroutine calls or computed jumps are limited to the first 256 locations of any program memory page (512 words long).

### FIGURE 4-3: LOADING OF PC BRANCH INSTRUCTIONS -PIC16C505

#### 4.6.1 EFFECTS OF RESET

The Program Counter is set upon a RESET, which means that the PC addresses the last location in the last page (i.e., the oscillator calibration instruction.) After executing MOVLW XX, the PC will roll over to location 00h and begin executing user code.

The STATUS register page preselect bits are cleared upon a RESET, which means that page 0 is pre-selected.

Therefore, upon a RESET, a GOTO instruction will automatically cause the program to jump to page 0 until the value of the page bits is altered.

# 4.7 <u>Stack</u>

PIC16C505 devices have a 12-bit wide hardware push/pop stack.

A CALL instruction will push the current value of stack 1 into stack 2 and then push the current program counter value, incremented by one, into stack level 1. If more than two sequential CALL's are executed, only the most recent two return addresses are stored.

A RETLW instruction will pop the contents of stack level 1 into the program counter and then copy stack level 2 contents into level 1. If more than two sequential RETLW's are executed, the stack will be filled with the address previously stored in level 2. Note that the W register will be loaded with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

Note 1: There are no STATUS bits to indicate stack overflows or stack underflow conditions.

Note 2: There are no instructions mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETLW, and instructions.

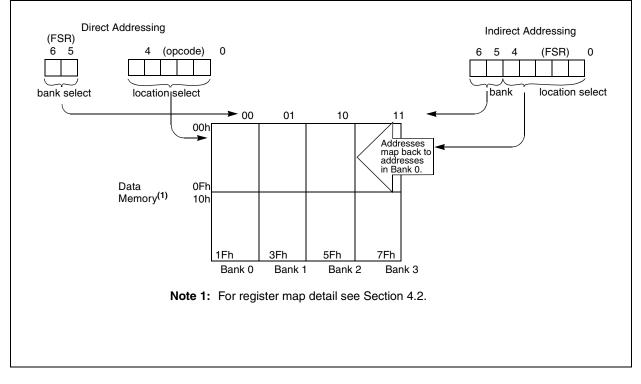

#### 4.8 Indirect Data Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

## EXAMPLE 4-1: INDIRECT ADDRESSING

- Register file 07 contains the value 10h

- Register file 08 contains the value 0Ah

- · Load the value 07 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 08)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 10h-1Fh using indirect addressing is shown in Example 4-2.

## FIGURE 4-4: DIRECT/INDIRECT ADDRESSING

#### EXAMPLE 4-2: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

|          | movlw<br>movwf | 0x10<br>FSR | ;initialize pointer<br>; to RAM |

|----------|----------------|-------------|---------------------------------|

| NEXT     | clrf           | INDF        | clear INDF register;            |

|          | incf           | FSR,F       | ;inc pointer                    |

|          | btfsc          | FSR,4       | ;all done?                      |

|          | goto           | NEXT        | ;NO, clear next                 |

| CONTINUE |                |             |                                 |

|          | :              |             | ;YES, continue                  |

|          | :              |             |                                 |

The FSR is a 5-bit wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

The device uses FSR<6:5> to select between banks 0:3.

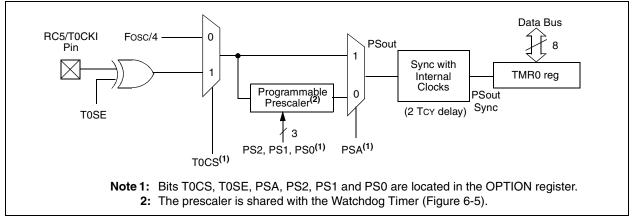

# 6.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the TOCS bit (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.1.

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. Section 6.2 details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 6-1.

## FIGURE 6-1: TIMER0 BLOCK DIAGRAM

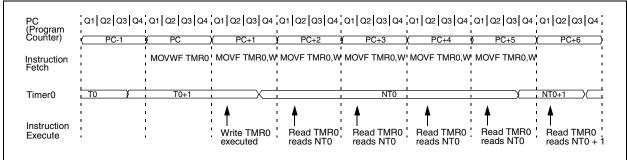

# FIGURE 6-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

| (Program<br>Counter)    | ( PC-1      | X PC        | ( PC+1      | PC+2        | PC+3        | ( PC+4 )    | PC+5 (      | PC+6      |

|-------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-----------|

| nstruction<br>Fetch     | 1<br>1<br>1 | MOVWF TMR0  | MOVF TMR0,W |           |

| Timer0                  |             | Τ0+1 χ      | T0+2 X      |             | NTO         |             | NT0+1 )     | NT0+2     |

| Instruction<br>Executed | 1<br>1<br>1 | 1<br>1<br>1 | Write TMR0  | Read TMR0   | Read TMR0   | Read TMR0   | Read TMR0   | Read TMR0 |

### FIGURE 6-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6                                  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0     | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|--------|----------|----------------------------------------|-------|-------|-------|-------|-----------|-----------|-------------------------------|---------------------------------|

| 01h     | TMR0   | Timer0 - | Timer0 - 8-bit real-time clock/counter |       |       |       |       | xxxx xxxx | uuuu uuuu |                               |                                 |

| N/A     | OPTION | RBWU     | RBPU                                   | TOCS  | T0SE  | PSA   | PS2   | PS1       | PS0       | 1111 1111                     | 1111 1111                       |

| N/A     | TRISC  | —        | _                                      | RC5   | RC4   | RC3   | RC2   | RC1       | RC0       | 11 1111                       | 11 1111                         |

Legend: Shaded cells not used by Timer0, - = unimplemented, x = unknown, u = unchanged.

| <b>TABLE 7-3:</b> | <b>RESET CONDITIONS FOR REGISTERS</b> |

|-------------------|---------------------------------------|

|-------------------|---------------------------------------|

| Register | Address | Power-on Reset | MCLR Reset<br>WDT time-out<br>Wake-up on Pin Change |

|----------|---------|----------------|-----------------------------------------------------|

| W        | —       | वववव वववव (1)  | वववव वववव(1)                                        |

| INDF     | 00h     | xxxx xxxx      | uuuu uuuu                                           |

| TMR0     | 01h     | xxxx xxxx      | uuuu uuuu                                           |

| PC       | 02h     | 1111 1111      | 1111 1111                                           |

| STATUS   | 03h     | 0001 1xxx      | q00q quuu <sup>(2,3)</sup>                          |

| FSR      | 04h     | 110x xxxx      | 11uu uuuu                                           |

| OSCCAL   | 05h     | 1000 00        | uuuu uu                                             |

| PORTB    | 06h     | xx xxxxx       | uu uuuu                                             |

| PORTC    | 07h     | xx xxxxx       | uu uuuu                                             |

| OPTION   | —       | 1111 1111      | 1111 1111                                           |

| TRISB    | —       | 11 1111        | 11 1111                                             |

| TRISC    | —       | 11 1111        | 11 1111                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: Bits <7:2> of W register contain oscillator calibration values due to MOVLW XX instruction at top of memory.

**Note 2:** See Table 7-7 for reset value for specific conditions.

**Note 3:** If reset was due to wake-up on pin change, then bit 7 = 1. All other resets will cause bit 7 = 0.

## TABLE 7-4: RESET CONDITION FOR SPECIAL REGISTERS

|                                    | STATUS Addr: 03h | PCL Addr: 02h |

|------------------------------------|------------------|---------------|

| Power on reset                     | 0001 1xxx        | 1111 1111     |

| MCLR reset during normal operation | 000u uuuu        | 1111 1111     |

| MCLR reset during SLEEP            | 0001 0uuu        | 1111 1111     |

| WDT reset during SLEEP             | 0000 Ouuu        | 1111 1111     |

| WDT reset normal operation         | 0000 uuuu        | 1111 1111     |

| Wake-up from SLEEP on pin change   | 1001 Ouuu        | 1111 1111     |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0'.

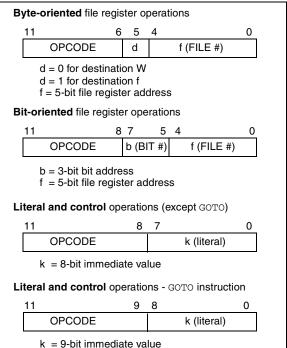

# 8.0 INSTRUCTION SET SUMMARY

Each PIC16C505 instruction is a 12-bit word divided into an OPCODE, which specifies the instruction type, and one or more operands which further specify the operation of the instruction. The PIC16C505 instruction set summary in Table 8-2 groups the instructions into byte-oriented, bit-oriented, and literal and control operations. Table 8-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator is used to specify which one of the 32 file registers is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8 or 9-bit constant or literal value.

#### TABLE 8-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| x             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is<br>the recommended form of use for compatibility<br>with all Microchip software tools. |

| d             | Destination select;<br>d = 0 (store result in W)<br>d = 1 (store result in file register 'f')<br>Default is d = 1                                                              |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| WDT           | Watchdog Timer Counter                                                                                                                                                         |

| TO            | Time-Out bit                                                                                                                                                                   |

| PD            | Power-Down bit                                                                                                                                                                 |

| dest          | Destination, either the W register or the specified register file location                                                                                                     |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| <>            | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

All instructions are executed within a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Figure 8-1 shows the three general formats that the instructions can have. All examples in the figure use the following format to represent a hexadecimal number:

0xhhh

where 'h' signifies a hexadecimal digit.

# FIGURE 8-1: GENERAL FORMAT FOR INSTRUCTIONS

<sup>© 1999-2012</sup> Microchip Technology Inc.

| ADDWF                                                           | Add W and f                                                                                                                                                                       |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                                         | [ label ] ADDWF f,d                                                                                                                                                               |

| Operands:                                                       | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                                                  |

| Operation:                                                      | $(W) + (f) \to (dest)$                                                                                                                                                            |

| Status Affected:                                                | C, DC, Z                                                                                                                                                                          |

| Encoding:                                                       | 0001 11df ffff                                                                                                                                                                    |

| Description:                                                    | Add the contents of the W register<br>and register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>'1', the result is stored back in reg-<br>ister 'f'. |

| Words:                                                          | 1                                                                                                                                                                                 |

| Cycles:                                                         | 1                                                                                                                                                                                 |

| Example:                                                        | ADDWF FSR, 0                                                                                                                                                                      |

| Before Instru<br>W =<br>FSR =<br>After Instruct<br>W =<br>FSR = | 0x17<br>0xC2<br>tion<br>0xD9                                                                                                                                                      |

| ANDLW                 | And literal with W                                                                                                    |      |      |  |  |  |  |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------|------|------|--|--|--|--|--|

| Syntax:               | [label] ANDLW k                                                                                                       |      |      |  |  |  |  |  |

| Operands:             | $0 \le k \le 255$                                                                                                     |      |      |  |  |  |  |  |

| Operation:            | (W).AND. (k) $\rightarrow$ (W)                                                                                        |      |      |  |  |  |  |  |

| Status Affected:      | Z                                                                                                                     |      |      |  |  |  |  |  |

| Encoding:             | 1110                                                                                                                  | kkkk | kkkk |  |  |  |  |  |

| Description:          | The contents of the W register a<br>AND'ed with the eight-bit literal 'I<br>The result is placed in the W reg<br>ter. |      |      |  |  |  |  |  |

| Words:                | 1                                                                                                                     |      |      |  |  |  |  |  |

| Cycles:               | 1                                                                                                                     |      |      |  |  |  |  |  |

| Example:              | ANDLW                                                                                                                 | 0x5F |      |  |  |  |  |  |

| Before Instru<br>W =  | oxA3                                                                                                                  |      |      |  |  |  |  |  |

| After Instruct<br>W = | ion<br>0x03                                                                                                           |      |      |  |  |  |  |  |

| ANDWF                                                           | AND W with f                                                                                                                                                                            |  |  |  |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                                         | [label] ANDWF f,d                                                                                                                                                                       |  |  |  |

| Operands:                                                       | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                                                        |  |  |  |

| Operation:                                                      | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                      |  |  |  |

| Status Affected:                                                | Z                                                                                                                                                                                       |  |  |  |

| Encoding:                                                       | 0001 01df ffff                                                                                                                                                                          |  |  |  |

| Description:                                                    | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is 0, the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back in<br>register 'f'. |  |  |  |

| Words:                                                          | 1                                                                                                                                                                                       |  |  |  |

| Cycles:                                                         | 1                                                                                                                                                                                       |  |  |  |

| Example:                                                        | ANDWF FSR, 1                                                                                                                                                                            |  |  |  |

| Before Instru<br>W =<br>FSR =<br>After Instruct<br>W =<br>FSR = | 0x17<br>0xC2<br>iion<br>0x17                                                                                                                                                            |  |  |  |

| BCF                                   | Bit Clear               | r f                                                                |           |    |  |

|---------------------------------------|-------------------------|--------------------------------------------------------------------|-----------|----|--|

| Syntax:                               | [label]                 | BCF f,t                                                            | )         |    |  |

| Operands:                             |                         | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |           |    |  |

| Operation:                            | $0 \rightarrow (f < b)$ | >)                                                                 |           |    |  |

| Status Affected:                      | None                    |                                                                    |           |    |  |

| Encoding:                             | 0100                    | bbbf                                                               | ffff      |    |  |

| Description:                          | Bit 'b' in r            | egister 'f'                                                        | is cleare | d. |  |

| Words:                                | 1                       |                                                                    |           |    |  |

| Cycles:                               | 1                       |                                                                    |           |    |  |

| Example:                              | BCF                     | FLAG_REG                                                           | 5, 7      |    |  |

| Before Instruction<br>FLAG_REG = 0xC7 |                         |                                                                    |           |    |  |

| After Instruc<br>FLAG_R               | tion<br>EG = 0x47       | 7                                                                  |           |    |  |

| COMF                       | Complement f                                                                                                                                                              |  |  |  |  |  |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                    | [ label ] COMF f,d                                                                                                                                                        |  |  |  |  |  |

| Operands:                  | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                |  |  |  |  |  |

| Operation:                 | $(\overline{f}) \rightarrow (dest)$                                                                                                                                       |  |  |  |  |  |

| Status Affected:           | Z                                                                                                                                                                         |  |  |  |  |  |

| Encoding:                  | 0010 01df ffff                                                                                                                                                            |  |  |  |  |  |

| Description:               | The contents of register 'f' are<br>complemented. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>1, the result is stored back in regis-<br>ter 'f'. |  |  |  |  |  |

| Words:                     | 1                                                                                                                                                                         |  |  |  |  |  |

| Cycles:                    | 1                                                                                                                                                                         |  |  |  |  |  |

| Example:                   | COMF REG1,0                                                                                                                                                               |  |  |  |  |  |

| Before Instru<br>REG1      | uction<br>= 0x13                                                                                                                                                          |  |  |  |  |  |

| After Instruc<br>REG1<br>W | tion<br>= 0x13<br>= 0xEC                                                                                                                                                  |  |  |  |  |  |

| DECF                       | Decrement f                                                                                                                                                               |  |  |  |  |  |

| Syntax:                    | [label] DECF f,d                                                                                                                                                          |  |  |  |  |  |

| Operands:                  | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                                          |  |  |  |  |  |

| Operation:                                  | $(f) - 1 \rightarrow (dest)$                                                                                                                  |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Status Affected:                            | Z                                                                                                                                             |

| Encoding:                                   | 0000 11df ffff                                                                                                                                |

| Description:                                | Decrement register 'f'. If 'd' is 0, the<br>result is stored in the W register. If<br>'d' is 1, the result is stored back in<br>register 'f'. |

| Words:                                      | 1                                                                                                                                             |

| Cycles:                                     | 1                                                                                                                                             |

| Example:                                    | DECF CNT, 1                                                                                                                                   |

| Before Instru<br>CNT<br>Z<br>After Instruct | = 0x01<br>= 0                                                                                                                                 |

| CNT<br>Z                                    | = 0x00<br>= 1                                                                                                                                 |

| DECFSZ                                               | Decrement f, Skip if 0                                                                                                                                                                     |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                              | [label] DECFSZ f,d                                                                                                                                                                         |

| Operands:                                            | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                                          |

| Operation:                                           | (f) $-1 \rightarrow d$ ; skip if result = 0                                                                                                                                                |

| Status Affected:                                     | None                                                                                                                                                                                       |

| Encoding:                                            | 0010 11df ffff                                                                                                                                                                             |

| Description:                                         | The contents of register 'f' are dec-<br>remented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in register<br>'f'.                   |

|                                                      | If the result is 0, the next instruc-<br>tion, which is already fetched, is<br>discarded and a NOP is executed<br>instead making it a two cycle<br>instruction.                            |

| Words:                                               | 1                                                                                                                                                                                          |

| Cycles:                                              | 1(2)                                                                                                                                                                                       |

| Example:                                             | HERE DECFSZ CNT, 1<br>GOTO LOOP                                                                                                                                                            |

|                                                      | CONTINUE •                                                                                                                                                                                 |

| Before Instru<br>PC                                  | uction<br>= address (HERE)                                                                                                                                                                 |

| After Instruc<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC | tion<br>= CNT - 1;<br>= 0,<br>= address (CONTINUE);<br>≠ 0,<br>= address (HERE+1)                                                                                                          |

| GOTO                                                 | Unconditional Branch                                                                                                                                                                       |

| Syntax:                                              | [ <i>label</i> ] GOTO k                                                                                                                                                                    |

| Operands:                                            | $0 \le k \le 511$                                                                                                                                                                          |

| Operation:                                           | $k \rightarrow PC < 8:0>;$<br>STATUS <6:5> $\rightarrow PC < 10:9>$                                                                                                                        |

| Status Affected:                                     | None                                                                                                                                                                                       |

| Encoding:                                            | 101k kkkk kkkk                                                                                                                                                                             |

| Description:                                         | GOTO is an unconditional branch.<br>The 9-bit immediate value is<br>loaded into PC bits <8:0>. The<br>upper bits of PC are loaded from<br>STATUS<6:5>. GOTO is a two cycle<br>instruction. |

| Words:                                               | 1                                                                                                                                                                                          |

| Cycles:                                              | 2                                                                                                                                                                                          |

| Example:                                             | GOTO THERE                                                                                                                                                                                 |

| After Instruc<br>PC =                                | tion<br>address (THERE)                                                                                                                                                                    |

| IORLW                                               | Inclusive OR literal with W                                                                                                 |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                             | [ <i>label</i> ] IORLW k                                                                                                    |  |  |  |  |

| Operands:                                           | $0 \le k \le 255$                                                                                                           |  |  |  |  |

| Operation:                                          | (W) .OR. (k) $\rightarrow$ (W)                                                                                              |  |  |  |  |

| Status Affected:                                    | Z                                                                                                                           |  |  |  |  |

| Encoding:                                           | 1101 kkkk kkkk                                                                                                              |  |  |  |  |

| Description:                                        | The contents of the W register are<br>OR'ed with the eight bit literal 'k'.<br>The result is placed in the W regis-<br>ter. |  |  |  |  |

| Words:                                              | 1                                                                                                                           |  |  |  |  |

| Cycles:                                             | 1                                                                                                                           |  |  |  |  |

| Example:                                            | IORLW 0x35                                                                                                                  |  |  |  |  |

| Before Instruction<br>W = 0x9A<br>After Instruction |                                                                                                                             |  |  |  |  |

| W =<br>Z =                                          | 0xBF<br>0                                                                                                                   |  |  |  |  |

| IORWF                             | Inclusive OR W with f                                                                                                                                                   |  |  |  |  |  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                           | [ label ] IORWF f,d                                                                                                                                                     |  |  |  |  |  |

| Operands:                         | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                              |  |  |  |  |  |

| Operation:                        | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                                        |  |  |  |  |  |

| Status Affected:                  | Z                                                                                                                                                                       |  |  |  |  |  |

| Encoding:                         | 0001 00df ffff                                                                                                                                                          |  |  |  |  |  |

| Description:                      | Inclusive OR the W register with<br>register 'f'. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in register<br>'f'. |  |  |  |  |  |

| Words:                            | 1                                                                                                                                                                       |  |  |  |  |  |

| Cycles:                           | 1                                                                                                                                                                       |  |  |  |  |  |

| Example:                          | IORWF RESULT, 0                                                                                                                                                         |  |  |  |  |  |

| Before Instru<br>RESULT<br>W      |                                                                                                                                                                         |  |  |  |  |  |

| After Instruc<br>RESULT<br>W<br>Z |                                                                                                                                                                         |  |  |  |  |  |

| MOVF                 | Move f                                                                                                                                                                                                                                                      |  |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:              | [label] MOVF f,d                                                                                                                                                                                                                                            |  |  |  |  |

| Operands:            | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                  |  |  |  |  |

| Operation:           | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                    |  |  |  |  |

| Status Affected:     | Z                                                                                                                                                                                                                                                           |  |  |  |  |

| Encoding:            | 0010 00df ffff                                                                                                                                                                                                                                              |  |  |  |  |

| Description:         | The contents of register 'f' are<br>moved to destination 'd'. If 'd' is 0,<br>destination is the W register. If 'd'<br>is 1, the destination is file register<br>'f'. 'd' = 1 is useful as a test of a file<br>register since status flag Z is<br>affected. |  |  |  |  |

| Words:               | 1                                                                                                                                                                                                                                                           |  |  |  |  |

| Cycles:              | 1                                                                                                                                                                                                                                                           |  |  |  |  |

| Example:             | MOVF FSR, 0                                                                                                                                                                                                                                                 |  |  |  |  |

| After Instruc<br>W = | tion<br>value in FSR register                                                                                                                                                                                                                               |  |  |  |  |

| MOVLW                 | Move Literal to W                    |            |            |  |  |

|-----------------------|--------------------------------------|------------|------------|--|--|

| Syntax:               | [ label ]                            | MOVLW      | k          |  |  |

| Operands:             | $0 \le k \le 25$                     | 55         |            |  |  |

| Operation:            | $k \to (W)$                          |            |            |  |  |

| Status Affected:      | None                                 |            |            |  |  |

| Encoding:             | 1100                                 | kkkk       | kkkk       |  |  |

| Description:          | The eight<br>the W reg<br>will asser | gister. Th | ie don't c |  |  |

| Words:                | 1                                    |            |            |  |  |

| Cycles:               | 1                                    |            |            |  |  |

| Example:              | MOVLW                                | 0x5A       |            |  |  |

| After Instruct<br>W = | ion<br>0x5A                          |            |            |  |  |

# 9.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 9.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 9.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 9.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

### 10.3 DC CHARACTERISTICS:

#### PIC16C505-04 (Commercial, Industrial, Extended) PIC16C505-20(Commercial, Industrial, Extended) PIC16LC505-04 (Commercial, Industrial)

|        | I                                  | PIC16L                                          | .C505-04    | (Com   | mercial   | , Indu   | strial)                                            |

|--------|------------------------------------|-------------------------------------------------|-------------|--------|-----------|----------|----------------------------------------------------|

|        |                                    |                                                 |             |        |           |          | ss otherwise specified)                            |

|        |                                    | Operati                                         | ing tempera | ature  |           |          | +70°C (commercial)                                 |

| DC CHA | ARACTERISTICS                      |                                                 |             |        |           |          | 85°C (industrial)                                  |

|        |                                    | Oporati                                         | ing voltage | Voor   |           |          | 125°C (extended)<br>ed in DC spec Section 10.1 and |

|        |                                    |                                                 |             | ו טט י | ange as c | lescribe | ed in DC spec Section 10.1 and                     |

| Param  | Characteristic                     | Section 10.3. Sym Min Typ† Max Units Conditions |             |        |           |          |                                                    |

| No.    | onaraoteristic                     | Oyin                                            |             | 1 YPI  | Max       | Onits    | Conditions                                         |

|        | Input Low Voltage                  |                                                 |             |        |           |          |                                                    |

|        | I/O ports                          | VIL                                             |             |        |           |          |                                                    |

| D030   | with TTL buffer                    | VIL                                             | Vss         | _      | 0.8V      | v        | For all $4.5 \le VDD \le 5.5V$                     |

| D030A  |                                    |                                                 | VSS         | _      | 0.15VDD   | -        | otherwise                                          |

| D031   | with Schmitt Trigger buffer        |                                                 | VSS         | _      | 0.2VDD    | v        |                                                    |

| D032   | MCLR, RC5/T0CKI                    |                                                 | VSS         | _      | 0.2VDD    | v        |                                                    |

| DUUL   | (in EXTRC mode)                    |                                                 | ¥00         |        | 0.2000    | v        |                                                    |

| D033   | OSC1 (in XT, HS and LP)            |                                                 | Vss         | _      | 0.3VDD    | v        | Note1                                              |

| 2000   | Input High Voltage                 |                                                 |             |        | 0.07.55   | -        |                                                    |

|        | I/O ports                          | VIH                                             |             | _      |           |          |                                                    |

| D040   | with TTL buffer                    |                                                 | 2.0         | _      | Vdd       | v        | $4.5 \leq VDD \leq 5.5V$                           |

| D040A  |                                    |                                                 | 0.25VDD     | _      | Vdd       | v        |                                                    |

|        |                                    |                                                 | + 0.8VDD    |        |           |          | otherwise                                          |

| D041   | with Schmitt Trigger buffer        |                                                 | 0.8Vdd      | —      | Vdd       | v        | For entire VDD range                               |

| D042   | MCLR, RC5/T0CKI                    |                                                 | 0.8Vdd      | —      | Vdd       | V        |                                                    |

| D042A  | OSC1 (XT, HS and LP)               |                                                 | 0.7Vdd      | —      | Vdd       | V        | Note1                                              |

| D043   | OSC1 (in EXTRC mode)               |                                                 | 0.9Vdd      | _      | Vdd       | V        |                                                    |

| D070   | GPIO weak pull-up current (Note 4) | IPUR                                            | 50          | 250    | 400       | μA       | VDD = 5V, VPIN = VSS                               |

|        | Input Leakage Current (Notes 2, 3) |                                                 |             |        |           |          |                                                    |

| D060   | I/O ports                          | lı∟                                             | —           | —      | ±1        | μA       | $Vss \leq VPIN \leq VDD$ , Pin at                  |

|        |                                    |                                                 |             |        |           |          | hi-impedance                                       |

| D061   | GP3/MCLRI (Note 5)                 |                                                 | —           | —      | ±30       | μΑ       | $Vss \le VPIN \le VDD$                             |

| D061A  | GP3/MCLRI (Note 6)                 |                                                 | —           | —      | ±5        | μΑ       | $Vss \le VPIN \le VDD$                             |

| D063   | OSC1                               |                                                 | —           | —      | ±5        | μΑ       | $Vss \leq VPIN \leq VDD, XT, HS and LP$            |

|        |                                    |                                                 |             |        |           |          | osc configuration                                  |

|        | Output Low Voltage                 |                                                 |             |        |           |          |                                                    |

| D080   | I/O ports/CLKOUT                   | Vol                                             | —           | —      | 0.6       | V        | IOL = 8.5 mA, VDD = 4.5V,                          |

|        |                                    |                                                 |             |        |           |          | –40°C to +85°C                                     |

| D080A  |                                    |                                                 | —           | —      | 0.6       | V        | IOL = 7.0  mA,  VDD = 4.5 V,                       |

| Dage   |                                    |                                                 |             |        |           |          | -40°C to +125°C                                    |

| D083   | OSC2                               |                                                 | —           | -      | 0.6       | V        | IOL = 1.6  mA,  VDD = 4.5  V,                      |

| Dacat  |                                    |                                                 |             |        | 0.0       |          | -40°C to +85°C                                     |

| D083A  |                                    |                                                 | _           | -      | 0.6       | V        | IOL = 1.2  mA, VDD = 4.5V,                         |

|        |                                    |                                                 |             |        |           |          | –40°C to +125°C                                    |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C505 be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as coming out of the pin.

4: Does not include GP3. For GP3 see parameters D061 and D061A.

5: This spec. applies to GP3/MCLR configured as external MCLR and GP3/MCLR configured as input with internal pull-up enabled.

6: This spec. applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

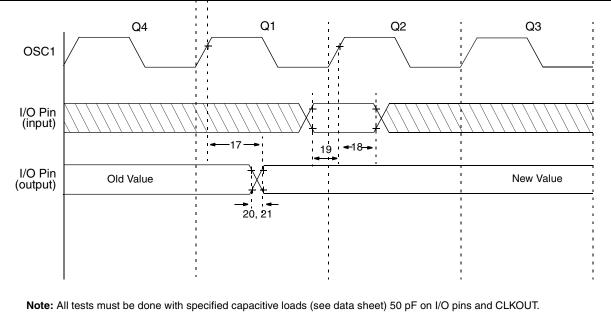

## FIGURE 10-6: I/O TIMING - PIC16C505

| <b>TABLE 10-4:</b> | TIMING REQUIREMENTS - PIC16C505 |

|--------------------|---------------------------------|

|                    |                                 |

| AC Charae        | cteristics | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                    | C (commerci<br>C (industrial)<br>°C (extended | al) |      |       |

|------------------|------------|-----------------------------------------------------------------------------------------|-----------------------------------------------|-----|------|-------|

| Parameter<br>No. | Sym        | Characteristic Min Typ <sup>(1)</sup> Max U                                             |                                               |     |      | Units |

| 17               | TosH2ioV   | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid <sup>(2,3)</sup>                         | —                                             | _   | 100* | ns    |

| 18               | TosH2iol   | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid<br>(I/O in hold time) <sup>(2)</sup> | TBD                                           | —   | _    | ns    |

| 19               | TioV2osH   | Port input valid to OSC1↑<br>(I/O in setup time)                                        | TBD                                           | —   | _    | ns    |

| 20               | TioR       | Port output rise time <sup>(3)</sup>                                                    | —                                             | 10  | 25** | ns    |

| 21               | TioF       | Port output fall time <sup>(3)</sup>                                                    | _                                             | 10  | 25** | ns    |

\* These parameters are characterized but not tested.

\*\* These parameters are design targets and are not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: Measurements are taken in EXTRC mode.

**3:** See Figure 10-4 for loading conditions.

NOTES:

# 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units | MILLIMETERS |      |      |

|--------------------------|-------|-------------|------|------|

| Dimension Limits         |       | MIN         | NOM  | MAX  |

| Number of Pins           | N     | 14          |      |      |

| Pitch                    | е     | 0.65 BSC    |      |      |

| Overall Height           | Α     | -           | -    | 1.20 |

| Molded Package Thickness | A2    | 0.80        | 1.00 | 1.05 |

| Standoff                 | A1    | 0.05        | -    | 0.15 |

| Overall Width            | E     | 6.40 BSC    |      |      |

| Molded Package Width     | E1    | 4.30        | 4.40 | 4.50 |

| Molded Package Length    | D     | 4.90        | 5.00 | 5.10 |

| Foot Length              | L     | 0.45        | 0.60 | 0.75 |

| Footprint                | (L1)  | 1.00 REF    |      |      |

| Foot Angle               | φ     | 0°          | -    | 8°   |

| Lead Thickness           | С     | 0.09        | -    | 0.20 |

| Lead Width               | b     | 0.19        | -    | 0.30 |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-087C Sheet 2 of 2

# 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

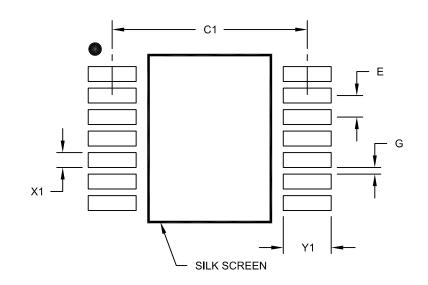

# RECOMMENDED LAND PATTERN

|                          | Units | Units MILLIMETERS |          | S    |  |

|--------------------------|-------|-------------------|----------|------|--|

| Dimension Limits         |       | MIN               | NOM      | MAX  |  |

| Contact Pitch            | E     |                   | 0.65 BSC |      |  |

| Contact Pad Spacing      | C1    |                   | 5.90     |      |  |

| Contact Pad Width (X14)  | X1    |                   |          | 0.45 |  |

| Contact Pad Length (X14) | Y1    |                   |          | 1.45 |  |

| Distance Between Pads    | G     | 0.20              |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2087A

# W

| Wake-up from SLEEP         |    |

|----------------------------|----|

| Watchdog Timer (WDT)       |    |

| Period                     | 35 |

| Programming Considerations |    |

| WWW Address                |    |

| WWW, On-Line Support       | 2  |

| Z                          |    |

| Zero bit                   | 7  |

# THE MICROCHIP WEB SITE