### Microchip Technology - PIC16C505-20I/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 1.5KB (1K x 12)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 72 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            |                                                                           |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 14-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c505-20i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

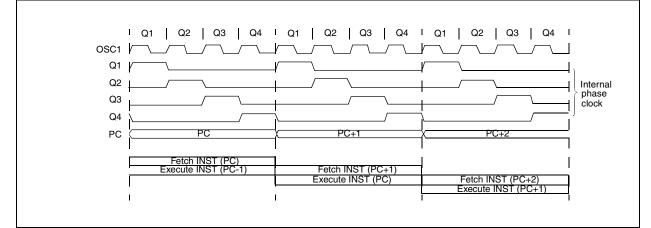

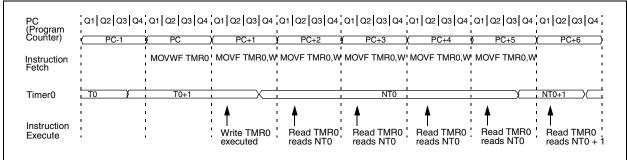

### 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter is incremented every Q1, and the instruction is fetched from program memory and latched into the instruction register in Q4. It is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2 and Example 3-1.

### 3.2 Instruction Flow/Pipelining

An Instruction cycle consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in cycle Q1. This instruction is then decoded and executed during the Q2, Q3 and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

### EXAMPLE 3-1: INSTRUCTION PIPELINE FLOW

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral functions to control the operation of the device (Table 4-1). The Special Function Registers can be classified into two sets. The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section for each peripheral feature.

| Address            | Name   | Bit 7                                                                 | Bit 6                  | Bit 5      | Bit 4       | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets <sup>(2)</sup> |

|--------------------|--------|-----------------------------------------------------------------------|------------------------|------------|-------------|-------|-------|-------|-------|-------------------------------|------------------------------------------------|

| 00h                | INDF   | Uses contents of FSR to address data memory (not a physical register) |                        |            |             |       |       |       |       | xxxx xxxx                     | uuuu uuuu                                      |

| 01h                | TMR0   | 8-bit real-ti                                                         | me clock/c             | ounter     |             |       |       |       |       | xxxx xxxx                     | uuuu uuuu                                      |

| 02h <sup>(1)</sup> | PCL    | Low order a                                                           | Low order 8 bits of PC |            |             |       |       |       |       | 1111 1111                     | 1111 1111                                      |

| 03h                | STATUS | RBWUF                                                                 | _                      | PAO        | TO          | PD    | Z     | DC    | С     | 0001 1xxx                     | q00q quuu <sup>(1)</sup>                       |

| 04h                | FSR    | Indirect dat                                                          | a memory               | address p  | ointer      |       |       |       |       | 110x xxxx                     | 11uu uuuu                                      |

| 05h                | OSCCAL | CAL5                                                                  | CAL4                   | CAL3       | CAL2        | CAL1  | CAL0  | _     | _     | 1000 00                       | uuuu uu                                        |

| N/A                | TRISB  | —                                                                     |                        | I/O contro | l registers |       |       |       |       | 11 1111                       | 11 1111                                        |

| N/A                | TRISC  | —                                                                     |                        | I/O contro | l registers |       |       |       |       | 11 1111                       | 11 1111                                        |

| N/A                | OPTION | RBWU                                                                  | RBPU                   | TOCS       | TOSE        | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                                      |

| 06h                | PORTB  | —                                                                     |                        | RB5        | RB4         | RB3   | RB2   | RB1   | RB0   | xx xxxx                       | uu uuuu                                        |

| 07h                | PORTC  | —                                                                     |                        | RC5        | RC4         | RC3   | RC2   | RC1   | RC0   | xx xxxx                       | uu uuuu                                        |

### TABLE 4-1:SPECIAL FUNCTION REGISTER (SFR) SUMMARY

Legend: Shaded cells not used by Port Registers, read as '0', — = unimplemented, read as '0', x = unknown, u = unchanged, q = depends on condition.

Note 1: If reset was due to wake-up on pin change, then bit 7 = 1. All other rests will cause bit 7 = 0.

Note 2: Other (non-power-up) resets include external reset through MCLR, watchdog timer and wake-up on pin change reset.

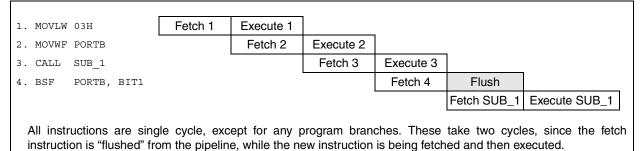

### 6.0 TIMER0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the TOCS bit (OPTION<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the T0CS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin T0CKI. The T0SE bit (OPTION<4>) determines the source edge. Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.1.

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4,..., 1:256 are selectable. Section 6.2 details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 6-1.

### FIGURE 6-1: TIMER0 BLOCK DIAGRAM

### FIGURE 6-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

| (Program<br>Counter)    | ( PC-1      | X PC        | ( PC+1      | PC+2        | PC+3        | ( PC+4 )    | PC+5 (      | PC+6      |

|-------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-----------|

| nstruction<br>Fetch     | 1<br>1<br>1 | MOVWF TMR0  | MOVF TMR0,W |           |

| Timer0                  |             | Τ0+1 χ      | T0+2 X      |             | NTO         |             | NT0+1 )     | NT0+2     |

| Instruction<br>Executed | 1<br>1<br>1 | 1<br>1<br>1 | Write TMR0  | Read TMR0   | Read TMR0   | Read TMR0   | Read TMR0   | Read TMR0 |

### FIGURE 6-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6      | Bit 5     | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|--------|----------|------------|-----------|----------|-------|-------|-------|-------|-------------------------------|---------------------------------|

| 01h     | TMR0   | Timer0 - | 8-bit real | -time clo | ck/count | ter   |       |       |       | xxxx xxxx                     | uuuu uuuu                       |

| N/A     | OPTION | RBWU     | RBPU       | TOCS      | T0SE     | PSA   | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

| N/A     | TRISC  | —        | _          | RC5       | RC4      | RC3   | RC2   | RC1   | RC0   | 11 1111                       | 11 1111                         |

Legend: Shaded cells not used by Timer0, - = unimplemented, x = unknown, u = unchanged.

#### 7.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

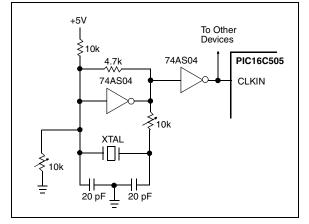

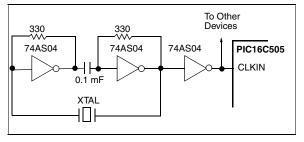

Either a prepackaged oscillator or a simple oscillator circuit with TTL gates can be used as an external crystal oscillator circuit. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with parallel resonance, or one with series resonance.

Figure 7-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This circuit could be used for external oscillator designs.

### FIGURE 7-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

Figure 7-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330  $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

### FIGURE 7-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

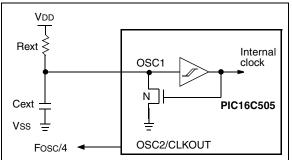

### 7.2.4 EXTERNAL RC OSCILLATOR

For timing insensitive applications, the RC device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used.

Figure 7-5 shows how the R/C combination is connected to the PIC16C505. For Rext values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high Rext values (e.g., 1 M $\Omega$ ) the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend keeping Rext between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

The Electrical Specifications section shows RC frequency variation from part to part due to normal process variation. The variation is larger for larger values of R (since leakage current variation will affect RC frequency more for large R) and for smaller values of C (since variation of input capacitance will affect RC frequency more).

Also, see the Electrical Specifications section for variation of oscillator frequency due to VDD for given Rext/Cext values, as well as frequency variation due to operating temperature for given R, C and VDD values.

## FIGURE 7-5: EXTERNAL RC OSCILLATOR MODE

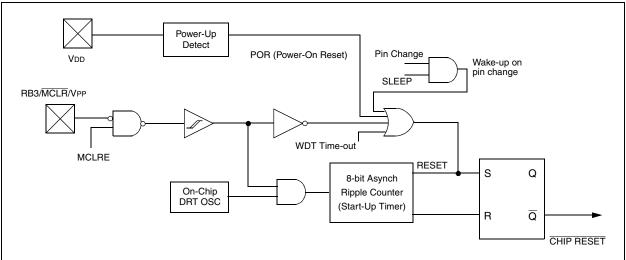

FIGURE 7-7: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

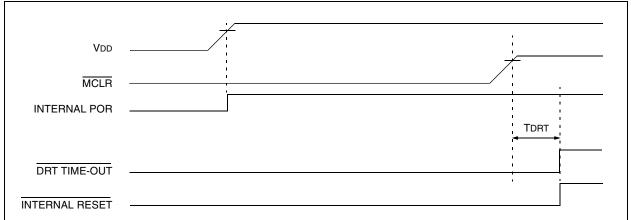

FIGURE 7-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR PULLED LOW)

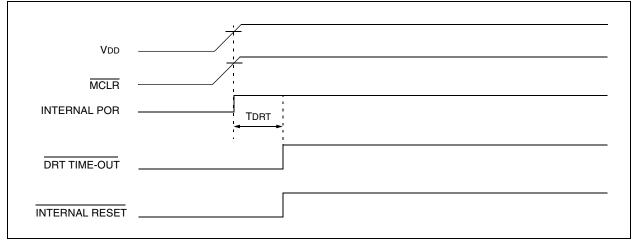

FIGURE 7-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): FAST VDD RISE TIME

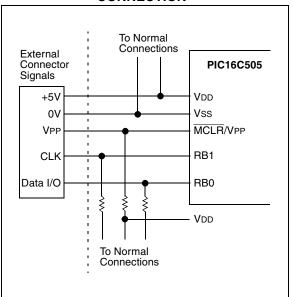

### 7.12 In-Circuit Serial Programming

The PIC16C505 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding the RB1 and RB0 pins low while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIHH (see programming specification). RB1 becomes the programming clock and RB0 becomes the programming data. Both RB1 and RB0 are Schmitt Trigger inputs in this mode.

After reset, a 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C505 Programming Specifications.

A typical in-circuit serial programming connection is shown in Figure 7-15.

#### FIGURE 7-15: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

| ADDWF                                                           | Add W and f                                                                                                                                                                       |  |  |  |  |  |  |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                                         | [ label ] ADDWF f,d                                                                                                                                                               |  |  |  |  |  |  |

| Operands:                                                       | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                                                  |  |  |  |  |  |  |

| Operation:                                                      | $(W) + (f) \to (dest)$                                                                                                                                                            |  |  |  |  |  |  |

| Status Affected:                                                | C, DC, Z                                                                                                                                                                          |  |  |  |  |  |  |

| Encoding:                                                       | 0001 11df ffff                                                                                                                                                                    |  |  |  |  |  |  |

| Description:                                                    | Add the contents of the W register<br>and register 'f'. If 'd' is 0, the result<br>is stored in the W register. If 'd' is<br>'1', the result is stored back in reg-<br>ister 'f'. |  |  |  |  |  |  |

| Words:                                                          | 1                                                                                                                                                                                 |  |  |  |  |  |  |

| Cycles:                                                         | 1                                                                                                                                                                                 |  |  |  |  |  |  |

| Example:                                                        | ADDWF FSR, 0                                                                                                                                                                      |  |  |  |  |  |  |

| Before Instru<br>W =<br>FSR =<br>After Instruct<br>W =<br>FSR = | 0x17<br>0xC2<br>tion<br>0xD9                                                                                                                                                      |  |  |  |  |  |  |

| ANDLW                 | And liter                              | al with W  | v            |           |  |  |  |

|-----------------------|----------------------------------------|------------|--------------|-----------|--|--|--|

| Syntax:               | [ <i>label</i> ] ANDLW k               |            |              |           |  |  |  |

| Operands:             | $0 \le k \le 255$                      |            |              |           |  |  |  |

| Operation:            | (W).AND. (k) $\rightarrow$ (W)         |            |              |           |  |  |  |

| Status Affected:      | Z                                      |            |              |           |  |  |  |

| Encoding:             | 1110                                   | kkkk       | kkkk         |           |  |  |  |

| Description:          | The conte<br>AND'ed v<br>The resulter. | vith the e | ight-bit lit | eral 'k'. |  |  |  |

| Words:                | 1                                      |            |              |           |  |  |  |

| Cycles:               | 1                                      |            |              |           |  |  |  |

| Example:              | ANDLW                                  | 0x5F       |              |           |  |  |  |

| Before Instru<br>W =  | oxA3                                   |            |              |           |  |  |  |

| After Instruct<br>W = | ion<br>0x03                            |            |              |           |  |  |  |

| ANDWF                                                           | AND W with f                                                                                                                                                                            |  |  |  |  |  |  |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                                         | [label] ANDWF f,d                                                                                                                                                                       |  |  |  |  |  |  |

| Operands:                                                       | $\begin{array}{l} 0 \leq f \leq 31 \\ d \in [0,1] \end{array}$                                                                                                                          |  |  |  |  |  |  |

| Operation:                                                      | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                                                      |  |  |  |  |  |  |

| Status Affected:                                                | Z                                                                                                                                                                                       |  |  |  |  |  |  |

| Encoding:                                                       | 0001 01df ffff                                                                                                                                                                          |  |  |  |  |  |  |

| Description:                                                    | The contents of the W register are<br>AND'ed with register 'f'. If 'd' is 0, the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back in<br>register 'f'. |  |  |  |  |  |  |

| Words:                                                          | 1                                                                                                                                                                                       |  |  |  |  |  |  |

| Cycles:                                                         | 1                                                                                                                                                                                       |  |  |  |  |  |  |

| Example:                                                        | ANDWF FSR, 1                                                                                                                                                                            |  |  |  |  |  |  |

| Before Instru<br>W =<br>FSR =<br>After Instruct<br>W =<br>FSR = | 0x17<br>0xC2<br>iion<br>0x17                                                                                                                                                            |  |  |  |  |  |  |

| BCF                     | Bit Clear                                                          | r f            |           |    |  |  |  |  |

|-------------------------|--------------------------------------------------------------------|----------------|-----------|----|--|--|--|--|

| Syntax:                 | [label]                                                            | BCF f,t        | )         |    |  |  |  |  |

| Operands:               | $\begin{array}{l} 0 \leq f \leq 31 \\ 0 \leq b \leq 7 \end{array}$ |                |           |    |  |  |  |  |

| Operation:              | $0 \rightarrow (f < b >)$                                          |                |           |    |  |  |  |  |

| Status Affected:        | None                                                               |                |           |    |  |  |  |  |

| Encoding:               | 0100                                                               | 0100 bbbf ffff |           |    |  |  |  |  |

| Description:            | Bit 'b' in r                                                       | egister 'f'    | is cleare | d. |  |  |  |  |

| Words:                  | 1                                                                  |                |           |    |  |  |  |  |

| Cycles:                 | 1                                                                  |                |           |    |  |  |  |  |

| Example:                | BCF                                                                | FLAG_REG       | 5, 7      |    |  |  |  |  |

| 20.0.0                  | Before Instruction<br>FLAG_REG = 0xC7                              |                |           |    |  |  |  |  |

| After Instruc<br>FLAG_R | tion<br>EG = 0x47                                                  | 7              |           |    |  |  |  |  |

| INCF                                                    | Increment f                                                                                                                                                            |  |  |  |  |  |  |  |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:                                                 | [label] INCF f,d                                                                                                                                                       |  |  |  |  |  |  |  |

| Operands:                                               | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                             |  |  |  |  |  |  |  |

| Operation:                                              | (f) + 1 $\rightarrow$ (dest)                                                                                                                                           |  |  |  |  |  |  |  |

| Status Affected:                                        | Z                                                                                                                                                                      |  |  |  |  |  |  |  |

| Encoding:                                               | 0010 10df ffff                                                                                                                                                         |  |  |  |  |  |  |  |

| Description:                                            | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1,<br>the result is placed back in register<br>'f'. |  |  |  |  |  |  |  |

| Words:                                                  | 1                                                                                                                                                                      |  |  |  |  |  |  |  |

| Cycles:                                                 | 1                                                                                                                                                                      |  |  |  |  |  |  |  |

| Example:                                                | INCF CNT, 1                                                                                                                                                            |  |  |  |  |  |  |  |

| Before Instru<br>CNT<br>Z<br>After Instruct<br>CNT<br>Z | = 0xFF<br>= 0                                                                                                                                                          |  |  |  |  |  |  |  |

|                     | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:             | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Operands:           | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Operation:          | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Status Affected:    | None                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Encoding:           | 0011 11df ffff                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Description:        | The contents of register 'f' are<br>incremented. If 'd' is 0, the result i<br>placed in the W register. If 'd' is 1<br>the result is placed back in register<br>'f'.<br>If the result is 0, then the next<br>instruction, which is already<br>fetched, is discarded and a NOP is<br>executed instead making it a two<br>cycle instruction. |  |  |  |  |  |

|                     |                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Words:              | 1                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Cycles:             | 1(2)                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Example:            | HERE INCFSZ CNT, 1<br>GOTO LOOP                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                     | CONTINUE •                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                     | uction                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Before Instru       |                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Before Instru<br>PC | = address (HERE)                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

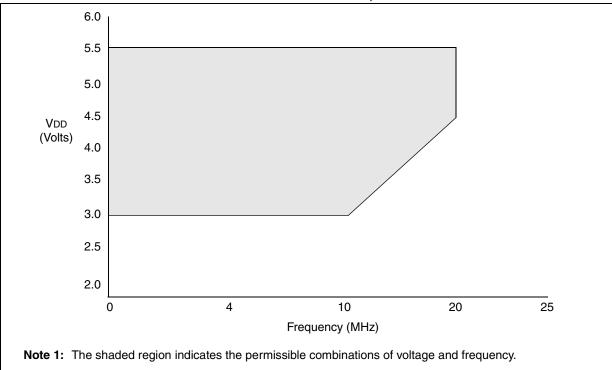

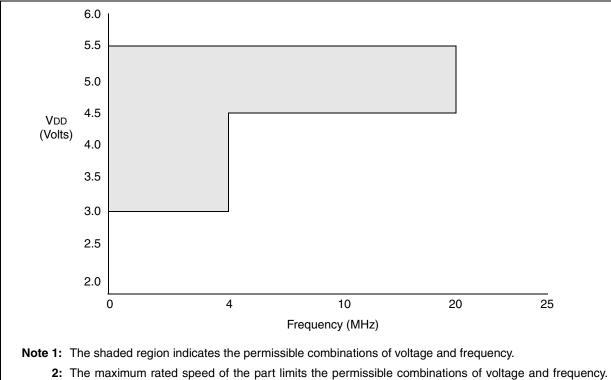

**2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

Please reference the Product Identification System section for the maximum rated speed of the parts.

### 10.3 DC CHARACTERISTICS:

### PIC16C505-04 (Commercial, Industrial, Extended) PIC16C505-20(Commercial, Industrial, Extended) PIC16LC505-04 (Commercial, Industrial)

|        | I                                  | PIC16L  | .C505-04    | (Com   | mercial   | , Indu     | strial)                                            |

|--------|------------------------------------|---------|-------------|--------|-----------|------------|----------------------------------------------------|

|        |                                    |         |             |        |           |            | ss otherwise specified)                            |

|        |                                    | Operati | ing tempera | ature  |           |            | +70°C (commercial)                                 |

| DC CHA | ARACTERISTICS                      |         |             |        |           |            | 85°C (industrial)                                  |

|        |                                    | Oporati | ing voltage | Voor   |           |            | 125°C (extended)<br>ed in DC spec Section 10.1 and |

|        |                                    | Section |             | י טט י | ange as c | lescribe   | ed in DC spec Section 10.1 and                     |

| Param  | Characteristic                     | Section | Min         | Typt   | Max       | Conditions |                                                    |

| No.    | onaraoteristic                     | Oyin    |             | 1 YPI  | Max       | Units      | Conditions                                         |

|        | Input Low Voltage                  |         |             |        |           |            |                                                    |

|        | I/O ports                          | VIL     |             |        |           |            |                                                    |

| D030   | with TTL buffer                    | VIL     | Vss         | _      | 0.8V      | v          | For all $4.5 \le VDD \le 5.5V$                     |

| D030A  |                                    |         | VSS         | _      | 0.15VDD   | -          | otherwise                                          |

| D031   | with Schmitt Trigger buffer        |         | VSS         | _      | 0.2VDD    | v          |                                                    |

| D032   | MCLR, RC5/T0CKI                    |         | VSS         | _      | 0.2VDD    | v          |                                                    |

| DUUL   | (in EXTRC mode)                    |         | ¥00         |        | 0.2000    | v          |                                                    |

| D033   | OSC1 (in XT, HS and LP)            |         | Vss         | _      | 0.3VDD    | v          | Note1                                              |

| 2000   | Input High Voltage                 |         |             |        | 0.0755    | -          |                                                    |

|        | I/O ports                          | VIH     |             | _      |           |            |                                                    |

| D040   | with TTL buffer                    |         | 2.0         | _      | Vdd       | v          | $4.5 \leq VDD \leq 5.5V$                           |

| D040A  |                                    |         | 0.25VDD     | _      | Vdd       | v          |                                                    |

|        |                                    |         | + 0.8VDD    |        |           |            | otherwise                                          |

| D041   | with Schmitt Trigger buffer        |         | 0.8Vdd      | —      | Vdd       | v          | For entire VDD range                               |

| D042   | MCLR, RC5/T0CKI                    |         | 0.8Vdd      | —      | Vdd       | V          |                                                    |

| D042A  | OSC1 (XT, HS and LP)               |         | 0.7Vdd      | —      | Vdd       | V          | Note1                                              |

| D043   | OSC1 (in EXTRC mode)               |         | 0.9Vdd      | _      | Vdd       | V          |                                                    |

| D070   | GPIO weak pull-up current (Note 4) | IPUR    | 50          | 250    | 400       | μA         | VDD = 5V, VPIN = VSS                               |

|        | Input Leakage Current (Notes 2, 3) |         |             |        |           |            |                                                    |

| D060   | I/O ports                          | lı∟     | —           | —      | ±1        | μA         | $Vss \leq VPIN \leq VDD$ , Pin at                  |

|        |                                    |         |             |        |           |            | hi-impedance                                       |

| D061   | GP3/MCLRI (Note 5)                 |         | —           | —      | ±30       | μΑ         | $Vss \le VPIN \le VDD$                             |

| D061A  | GP3/MCLRI (Note 6)                 |         | —           | —      | ±5        | μΑ         | $Vss \le VPIN \le VDD$                             |

| D063   | OSC1                               |         | —           | —      | ±5        | μΑ         | $Vss \leq VPIN \leq VDD, XT, HS and LP$            |

|        |                                    |         |             |        |           |            | osc configuration                                  |

|        | Output Low Voltage                 |         |             |        |           |            |                                                    |

| D080   | I/O ports/CLKOUT                   | VOL     | —           | —      | 0.6       | V          | IOL = 8.5 mA, VDD = 4.5V,                          |

|        |                                    |         |             |        |           |            | –40°C to +85°C                                     |

| D080A  |                                    |         | —           | —      | 0.6       | V          | IOL = 7.0  mA,  VDD = 4.5 V,                       |

| Dage   |                                    |         |             |        |           |            | -40°C to +125°C                                    |

| D083   | OSC2                               |         | —           | -      | 0.6       | V          | IOL = 1.6  mA,  VDD = 4.5  V,                      |

| Dacat  |                                    |         |             |        | 0.0       |            | -40°C to +85°C                                     |

| D083A  |                                    |         | _           | -      | 0.6       | V          | IOL = 1.2  mA, VDD = 4.5V,                         |

|        |                                    |         |             |        |           |            | –40°C to +125°C                                    |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In EXTRC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C505 be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as coming out of the pin.

4: Does not include GP3. For GP3 see parameters D061 and D061A.

5: This spec. applies to GP3/MCLR configured as external MCLR and GP3/MCLR configured as input with internal pull-up enabled.

6: This spec. applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

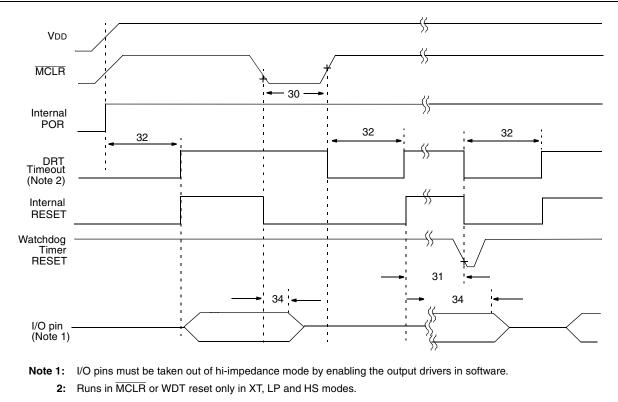

### FIGURE 10-7: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER TIMING - PIC16C505

### TABLE 10-5: RESET, WATCHDOG TIMER, AND DEVICE RESET TIMER - PIC16C505

| AC Charac        | teristics | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ (commercial)} \\ & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (industrial)} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ (extended)} \\ \mbox{Operating Voltage VDD range is described in Section 10.1} \end{array}$ |       |                    |       |       |                          |  |  |

|------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|-------|-------|--------------------------|--|--|

| Parameter<br>No. | Sym       | Characteristic                                                                                                                                                                                                                                                                                                                                                                                    | Min   | Typ <sup>(1)</sup> | Мах   | Units | Conditions               |  |  |

| 30               | TmcL      | MCLR Pulse Width (low)                                                                                                                                                                                                                                                                                                                                                                            | 2000* |                    | —     | ns    | VDD = 5.0 V              |  |  |

| 31               | Twdt      | Watchdog Timer Time-out Period<br>(No Prescaler)                                                                                                                                                                                                                                                                                                                                                  | 9*    | 18*                | 30*   | ms    | VDD = 5.0 V (Commercial) |  |  |

| 32               | Tdrt      | Device Reset Timer Period(2)                                                                                                                                                                                                                                                                                                                                                                      | 9*    | 18*                | 30*   | ms    | VDD = 5.0 V (Commercial) |  |  |

| 34               | Tioz      | I/O Hi-impedance from MCLR Low                                                                                                                                                                                                                                                                                                                                                                    | _     | _                  | 2000* | ns    |                          |  |  |

\* These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### TABLE 10-6: DRT (DEVICE RESET TIMER PERIOD - PIC16C505

| Oscillator Configuration | POR Reset       | Subsequent Resets |

|--------------------------|-----------------|-------------------|

| IntRC & ExtRC            | 18 ms (typical) | 300 μs (typical)  |

| XT, HS & LP              | 18 ms (typical) | 18 ms (typical)   |

NOTES:

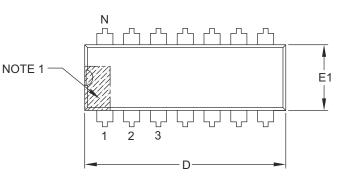

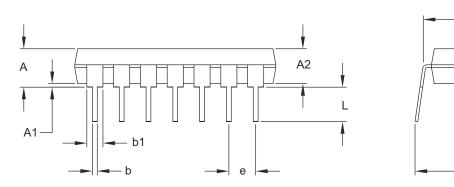

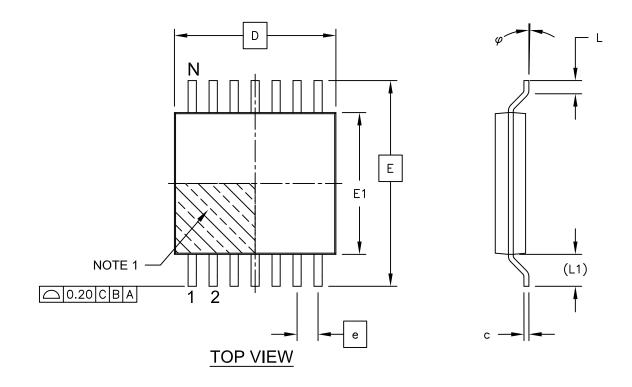

### 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Е

eВ

С

|                            | Units    |          | INCHES |      |

|----------------------------|----------|----------|--------|------|

| Dimensior                  | n Limits | MIN      | NOM    | MAX  |

| Number of Pins             | Ν        |          | 14     |      |

| Pitch                      | е        | .100 BSC |        |      |

| Top to Seating Plane       | А        | —        | -      | .210 |

| Molded Package Thickness   | A2       | .115     | .130   | .195 |

| Base to Seating Plane      | A1       | .015     | -      | -    |

| Shoulder to Shoulder Width | E        | .290     | .310   | .325 |

| Molded Package Width       | E1       | .240     | .250   | .280 |

| Overall Length             | D        | .735     | .750   | .775 |

| Tip to Seating Plane       | L        | .115     | .130   | .150 |

| Lead Thickness             | С        | .008     | .010   | .015 |

| Upper Lead Width           | b1       | .045     | .060   | .070 |

| Lower Lead Width           | b        | .014     | .018   | .022 |

| Overall Row Spacing §      | eB       | -        | -      | .430 |

Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M. BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B

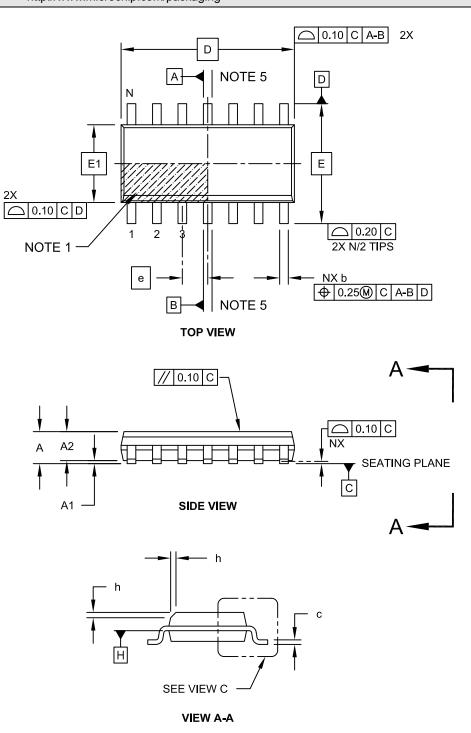

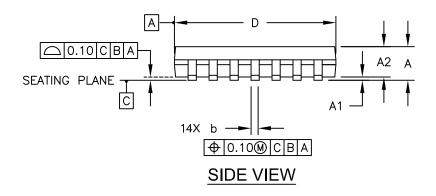

### 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-065C Sheet 1 of 2

### 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

VIEW C

|                          | Units | MILLIMETERS |          | S    |

|--------------------------|-------|-------------|----------|------|

| Dimension Lir            | nits  | MIN         | NOM      | MAX  |

| Number of Pins           | N     |             | 14       |      |

| Pitch                    | е     | 1.27 BSC    |          |      |

| Overall Height           | Α     | -           | -        | 1.75 |

| Molded Package Thickness | A2    | 1.25        | -        | -    |

| Standoff §               | A1    | 0.10        | -        | 0.25 |

| Overall Width            | E     |             | 6.00 BSC |      |

| Molded Package Width     | E1    | 3.90 BSC    |          |      |

| Overall Length           | D     |             | 8.65 BSC |      |

| Chamfer (Optional)       | h     | 0.25        | -        | 0.50 |

| Foot Length              | L     | 0.40        | -        | 1.27 |

| Footprint                | L1    |             | 1.04 REF |      |

| Lead Angle               | Θ     | 0°          | -        | -    |

| Foot Angle               | φ     | 0°          | -        | 8°   |

| Lead Thickness           | С     | 0.10        | -        | 0.25 |

| Lead Width               | b     | 0.31        | -        | 0.51 |

| Mold Draft Angle Top     | α     | 5°          | -        | 15°  |

| Mold Draft Angle Bottom  | β     | 5°          | -        | 15°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065C Sheet 2 of 2

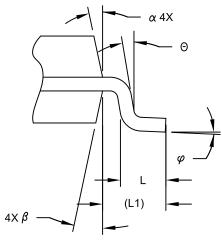

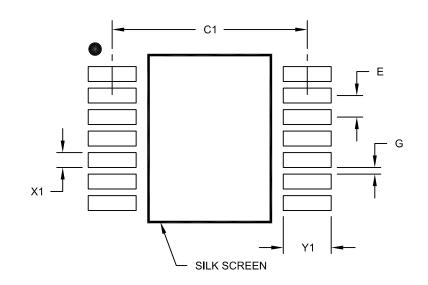

### 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-087C Sheet 1 of 2

### 14-Lead Plastic Thin Shrink Small Outline (ST) - 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                          | Units     | MILLIMETERS |          |      |

|--------------------------|-----------|-------------|----------|------|

| Dimensio                 | on Limits | MIN         | NOM      | MAX  |

| Contact Pitch            | E         |             | 0.65 BSC |      |

| Contact Pad Spacing      | C1        |             | 5.90     |      |

| Contact Pad Width (X14)  | X1        |             |          | 0.45 |

| Contact Pad Length (X14) | Y1        |             |          | 1.45 |

| Distance Between Pads    | G         | 0.20        |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2087A

# PIC18F66K80 FAMILY

NOTES:

### W

| Wake-up from SLEEP         |    |

|----------------------------|----|

| Watchdog Timer (WDT)       |    |

| Period                     | 35 |

| Programming Considerations |    |

| WWW Address                |    |

| WWW, On-Line Support       | 2  |

| Z                          |    |

| Zero bit                   | 7  |